摘要:在软硬件的开发阶段中,测试结果直接关系到这个软硬件能否顺利进行调试应用。其中,硬件的测试往往容易受外界因素的影响,如环境、计算机设备等,可以通过一些仿真软件来避免外界环境的影响,但是其测试速度比较慢,不利于硬件的开发进度。面对这一难题,文章从FPGA 的软硬件协同测试角度出发,利用PC 机和测试硬件设备的特点,进行FPGA 的软硬件协同测试的设计,努力实现FPGA 的软硬件协调测试系统在软硬件的测试和分析中的应用。

FPGA是现场可编程门阵列,是集成电路的一个新型门类,具有高度的灵活性、可现场定义相关数据存储容的能力、可反复改写程序等特点。在不久的将来,FPGA 将在很大程度上取代标准的数字集成电路,从而引起电子数据系统在设计方式上的变革,使其朝着集成电路的方向发展。目前,我国在计算机应用领域方面对基于FPGA 的软硬件协同测试的设计是比较重视的。

FPGA主要依赖于集成电路的发展,采用FPGA的数字化硬件设备,在图像处理中的优势越来越突出。每一个新的计算机软硬件产生,都必须经过测试,合格后才能正式投入使用。由此可见测试对于计算机软硬件设计开发的重要性。

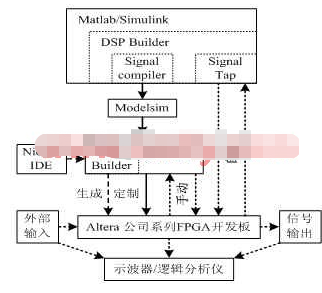

1 系统框架设计

系统框架设计是整个系统设计的整体概念,在这个过程中设计者需要对整个软硬件协同测试系统进行全局把握,明确其系统设计目的,并运用软硬件协同测试原理,结合软硬件协同测试的影响因素,PC 机与测试系统通信的设计及实时数据传输通道的设计来构建其系统设计框架。

1.1 软硬件协同测试原理

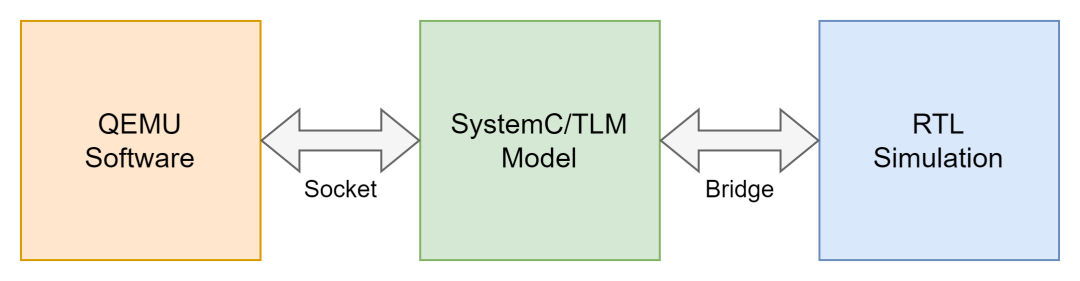

软硬件协同测试是通过对PC机进行模拟的设备输入、输出,来实现对硬件设备电路的测试。软硬件协同测试避免了PC 机在仿真过程中花费时间长的问题,充分利用了PC 机的系统资源,同时又发挥了硬件设备在电路工作过程中的高效,为硬件设备的测试提供了实时、高效的测试环境。

基于FPGA 的软硬件协同测试是将PC 机与待测试硬件设备相连接,能够将PC 机的资源充分利用,同时也能将硬件设备的高效工作速度发挥出来,可以实现实时、高效的双向数据传输,并能广泛地应用于各种硬件设备的开发测试与分析。用户在进行硬件设备的测试过程中,可以根据自身的需求,对单向传输通道或是双向传输通道进行选择。

1.2 软硬件协同测试的影响因素

在进行软硬件协同测试过程中,需要对能够影响其测试结果的相关因素进行分析,尽可能地减少或是避免其影响因素对测试结果造成偏差。

1.2.1 测试系统与待测试硬件设备之间的接口方式

待测试硬件设备的接口一般不是固定不变的,具体的接口方式主要根据其硬件设备的使用对象而有所不同,如数据线的接口与主从控制的接口就有所不同,若为了方便软硬件协同测试的进行,需要对测试硬件设备的接口进行相关的改进,使待测试硬件设备的接口标准化。

1.2.2 PC 机与测试系统的传输速度

在对待测试硬件设备进行实时测试过程中,待测试硬件设备的数据传输速度起到决定性作用。据相关资料显示,通常情况下,电视信号的数据量所要求的传输频率是28Mbps,软硬件协同测试过程中PC 机与待测试硬件设备之间的传输频率必须在100 Mbps 以上,才能够保证数据在PC 机与待测试硬件设备之间进行实时传输。

1.2.3 双向数据的实时传输

测试系统是模拟的待测试硬件设备在正常环境下的工作情况。所以,待测硬件设备的数据输入、输出等实时传输是对测试系统的最基本要求,也是保证硬件设备进行测试结果的真实性。PC 机的数据传输与待测试硬件设备有所不同,前者的通信模式通常是不定时的、突发的,后者往往是连续的、不间断的,因此,在实现数据的双向实时传输的过程中,测试系统对PC 机的设计存在着很大的改进空间。

1.3 PC 机与测试系统通信的设计

通常使用的USB、PCI 等数据接口可以保障PC 机与硬件设备测试系统之间的传输速度在100Mbps 以上。其中, PCI数据接口的传输数率比较高,但是不方便拔插,仅在一些计算机专业领域使用;USB数据接口的使用比较方便,是目前最普遍的数据接口。在硬件设备测试过程中,可以利用USB 数据接口的统一方便使用、即插即用、成本低廉等优点,将USB 作为其测试系统的数据接口。用户在对硬件设备进行检测时,只需要将外设同PC 机以外的总线进行连接,PC 机就可以对USB 数据接口的设备进行自动识别安装。目前使用的USB2.0的最大传输速度是480Mbps,可以满足PC机与硬件设备测试系统之间的传输速度需求。同时,USB 数据接口可以简化测试系统的相关设计方案,方便用户操作,节省测试成本。

1.4 实时数据传输通道的设计

待测试硬件设备的数据输入、输出是两个完全独立的实时通信,而USB 数据接口的通信模式是突发性的。数据传输方式的不统一,容易造成数据包在传输过程中的丢失。使用USB数据接口就需要解决传输方式不同而导致数据在传输过程中的丢失,保证设备之间进行数据实时传输和对输出数据的结果进行运算。

2 控制电路设计

软硬件协同测试的主要原理是对电路进行控制,以达到其测试的目的。本文以FPGA 为控制器、参与硬件设备测试系统与USB 数据接口的控制芯相关协议为例,来进行相关设计。其设计的出发点是根据待测试硬件设备的不同,设计出与之相适应的数据接口电路。

在整个设计过程中,SDRAM 的控制器功能主要是通过FPGA来实现的,主要包括SDRA控制器通过识读、存储数据、读取等操作所获取的信号、数据,来实现数据的双向传输通道。

2.1 请求发生器

SDRA控制器在每接收到8 个单位的数据后,就会向服务器发出一个关于写的请求;每识读出8 个单位的数据后,就会向相应的服务器发出一个关于读的请求。SDRA 的四个缓存分别用于两对控制器发出的读写请求。

SDRA 控制器的构造框架:USB 数据接口通过数据通道对请求发生器、刷新计数器进行控制,当信号发生器向请求发生器在两个以上请求时,仲裁器就根据SDRA决定运行的先后顺序。

2.2 仲裁器

在请求发生器产生两个及其以上的请求时,仲裁器会根据优先级别来决定SDRA 执行请求的先后顺序,并将其反馈到请求发生器上。仲裁器的功能是保证数据传输通道的畅通。

2.3 有限状态机

SDRA 控制的具体操作过程:状态接收器在收到有关读、写命令后会将其状态信息发送给信号发生器,进行相关数据的输入、输出。

目前使用最广泛的一种方式就是采用自动预充电的模式,主要步骤如下:(1)执行200 纳秒的空操作,来保障电源与时间信号的稳定性;(2)对SDRA 控制器中的区进行预充电操作;(3)执行至少两次刷新操作,保证仲裁器下达先后顺序指令的正确性。

2.4 信号发生器

根据SDRA 控制器的状态机来判断信号发生器的状态,并随之产生相应的SDRA 信号,包括CS、A、RAS 等。

2.5 数据通道

对FPGA 与待测硬件设备、USB 数据接口、控制芯片和SDRA 控制器的处理,主要是通过SDRA 数据缓存来实现的。

3 软硬件协同测试的实现

根据PC机与待测试硬件设备的优缺点,对硬件设备进行测试过程中的影响因素分析,为达到更加真实的测试结果,进行软硬件协同测试的相关结构组成部分的分析、测试过程中的各个部件的运行流程设计,形成了一个相对较准确、高效的测试环境。对于这样一个软硬件协同测试系统的最终实现,也需要经过向普通软硬件的产品生命周期,经过产品的设计、开发、测试、调试等一系列过程。

3.1 协同测试系统

在软硬件协同测试系统设计前期理念的前提下,对基于FPGA 的软硬件协同测试的设计成果应该进行相应的功能成果的验证。在计算机上面的相关软件环境下完成FPGA 的文件配置下载和安装后,形成一个软硬件协同测试环境,再进行相关顺序的步骤操作,同时,应该对其测试过程中的数据传输信号进行监控,以便与之前传统硬件设备测试结果进行对比,为基于FPGA的软硬件协同测试的实现创造有利的数据条件。

3.2 系统调试

按照设计目标,在实际的系统调试过程中,需要根据实际的调试结果进行相应的修改。

3.3 协同测试系统的验证

协同测试系统的功能的可行性包含两个方面的试验结果,一方面是协同测试系统功能在测试中的具体体现,另一方面是协同测试系统对于数据传输的速度的测定和分析。

协同测试系统功能在测试中的具体体现:基于FPGA 的软硬件协同测试通过了其内部的各个模块功能的设计,说明了协同测试系统设计完全符合其设计之初的功能期望。

协同测试系统对于数据传输的速度的测定和分析:只需要在FPGA 上运行非常短的时间就能够完成,表明在FPGA下的协同测试系统的初步设计构成,可以将硬件设备的高效工作速度发挥出来,可以实现实时、高效的双向数据传输,并能广泛地应用于各种硬件设备的开发测试与分析。

4 结语

随着计算机科学技术的发展,软硬件协同测试越来越受到重视和关注,也成为计算机领域的软硬件测试研究方向。基于FPGA 的软硬件协同测试在具体的系统测试过程中容易受到FPGA 容量的限制,因此,基于FPGA 的软硬件协同测试系统设计开发的重点在于其数据双向传输的速度。本文从FPGA 的软硬件协同测试的角度出发,根据PC机和测试硬件设备的特点和影响其测试的因素,进行FPGA 的软硬件协同测试原理设计、控制电路设计,并对软硬件协同测试系统测试、调试等运营结果进行研究分析,使其最终能够应用于各种软硬件设备的测试和分析中。

电子发烧友App

电子发烧友App

评论