讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2020-12-16 15:47:59 1693

1693

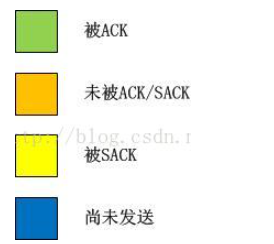

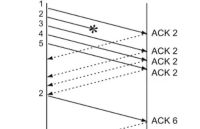

我一向觉得TCP拥塞控制算法太过复杂,而复杂的东西基本上就是用来装逼的垃圾,直到遇到了bbr。

2020-11-06 09:26:07 2484

2484

在win8.1 pc上使用Vivado 2014.1,MIG IP生成器在启动时收到Windows错误。相同的安装文件已加载到win7 pc上,MIG IP生成器运行正常。在Win8.1机器上,我

2018-12-07 11:18:46

MIG-250焊机图.pdf

2014-02-28 12:40:22

请帮忙。我通过MIG 2.3生成两个内存控制器。在合成报告中合成后,已经写了:粘合IOB的数量:560中的864 154%如何避免它?我使用Virtex-5和两个UDIMM。

2020-06-02 16:28:46

求助大神!!!FPGA对于DDR3读写,FPGA是virtex6系列配置MIG IP 核时,需要管脚分配1.原理图上dm是直接接地,管脚分配那里该怎么办2.系统时钟之类的管脚分配,是需要在原理图上找FPGA与DDR3之间的连线吗?还是?

2018-03-16 18:45:10

最近阿威也在玩MIG ,然后对我问了一大堆问题,主要针对MIG的时钟。后来发现自己理解得还是不够。这么一讨论更加清晰了,做个笔记吧。第一个时钟,也就是MIG 对DDR接口的时钟。因为我用的是ddr3

2019-05-21 07:21:10

TCP-2-10+

2023-03-28 13:15:03

TCP-2-10-75+

2023-03-29 21:36:21

TCP-2-10-75X+

2023-03-29 21:36:21

TCP-2-10X+

2023-03-29 21:36:21

TCP-2-33X+

2023-03-29 21:44:56

TCP-5027UB-DT

2023-03-29 22:34:34

TCP-5082UA-DT

2023-03-28 18:08:52

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

课题要求是用光电传感器控制ccd拍照我的想法是用光电开关(内含光电传感器)直接接24V继电器继电器开关串另外一个直流稳压5V电源电路控制CCD,是否可行?或者有什么其他的方法希望大家指导一下

2013-05-08 10:34:01

咖啡机光电式水位控制 的电路图。

2018-11-19 21:29:13

LT1084MIG-XX - 5 AMP POSITIVE VOLTAGE REGULATOR - Seme LAB

2022-11-04 17:22:44

大家好, 当我使用ML605 DDR3 MIG参考设计ml605_MIG_rdf0011_12.4时,它会在下面显示以下错误消息列表

2019-08-23 12:50:49

USR-TCP232-T2

2023-03-29 21:54:57

X76F101MIG-3.0 - Secure SerialFlash - IC MICROSYSTEMS

2022-11-04 17:22:44

嗨,大家好 我正在使用XUPV5 Virtex 5板,最近当我使用MIG创建DDR2内存控制器时,我意识到MIG创建的UCF文件与用户手册(我使用ML505的手册)不同,因为差分时钟的引脚根据

2019-08-21 10:24:03

有人用Xilinx ISE的mig生成ddr2,然后进行调试的吗?如果选择了内含pll,顶层时钟怎么连接

2014-09-15 19:14:41

在DDR2 MIG的使用时,想把DDR2封装成一个FIFO使用,但是有些问题不是太明白。在MIG的User Interface接口中,提供给控制器的数据是上升沿和下降沿的拼接,一个周期提供两个数据到

2015-03-29 18:41:43

振荡器和StateMachine的捕获来控制MIG,我使用的是LX9 Microboard。D0信号是我的状态机控制MIG的启用信号D1信号是StateMachine(WAIT)的返回D2是cmd_en

2019-07-23 14:46:25

里的例子,ddr正常。但实际是要使用user design文件夹下的.v文件,此时如果编写顶层读写控制程序对mig-39-2.v进行例化,应如何操作才能使用sim_tb_top.v仿真文件,(直接编写一个

2018-06-22 17:14:40

本帖最后由 elecfans跑堂 于 2015-9-14 09:21 编辑

最近在做FPGA板子用了两片16位的FPGA,在MIG中发现ODT 和CK CS等信号需要分别连接到FPGA。如下图,是我在MIG中设置的问题吗?还是xilinx DDR2 MIG就要求这么做?

2015-09-13 14:21:32

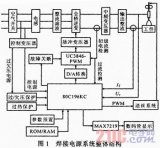

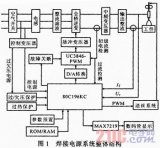

1. 文章研究主要问题双弧脉冲 MIG 焊是一种低能量输入焊接方法, 其原有的双电源供电系统结构复杂、协同控制困难、易受干扰。2. 结论提出了双弧脉冲 MIG 焊一体化专用电源的设计方案, 主弧和旁

2021-11-16 09:20:25

我可以使用mig生成ddr控制器(xc6vlx130t)吗?mig向导只支持ddr2和ddr3!

2020-06-12 07:32:48

如何使用MIG?我阅读了手册,但仍然有点困惑如何使用它来做到这一点。通过写一些地址并阅读一些地址并在地址上放置与地址相对应的指示灯来计划做一些较小的事情。

2020-08-04 10:51:22

该软件的版本是MIG2.1,ISE10.1.01。 FPGA是XC5VLX110T-1136,速度-1。我使用MIG2.1生成了DDR2内存控制器内核。首先,根据ML523用户指南中的DDR2引脚

2019-08-21 10:04:56

我在Kintex7 FPGA上使用MIG7控制器毁掉了对DDR3芯片的一些测试。在MIG7控制器内启用XADC模块。对于低于60℃的温度,每件事都可以。当温度达到60-65c时,我可以看到“app_rdy”信号变低并保持低电平直到FPGA重新编程。任何想法可能是错误的以及如何解决它?

2020-08-24 10:03:05

亲爱的先生Vivado:v2016.4装置:Artix-7我尝试在Vivado中使用MIG设计DDR3 SODIMM接口。但是,MIG只生成一对ddr_ck。我认为DDR3 SODIMM需要2对ddr_ck,如ddr_ck0和ddr_ck1。我该如何生成2对ddr_ck?谢谢。

2020-08-24 06:45:17

大家好,我最近经历了整整一周的时间,想知道如何在ZC706评估板上处理MIG。我的环境:ZC706评估板,带微米DDR3 SODIMM存储器(支持高达800MHz / 1,600 MT / s

2019-10-14 09:27:12

1. 文章研究主要问题在双弧脉冲熔化极惰性气体保护焊的过程中存主旁弧脉冲电流波形匹配以及耦合电弧稳定性的问题。2. 结论分析了双弧脉冲 MIG 焊的特点和控制要求,实现双弧脉冲 MIG 焊方法必须

2021-12-20 06:26:47

大家好,我用MIG 3.61生成DDR2内存控制器。在ISE 12.4中的映射期间,我有一个非常奇怪的错误,我不明白。错误:位置:864 - 不兼容的IOB被锁定到同一个存储区27冲突的IO标准

2020-06-11 11:52:56

嗨,我是jongbum。目前,MIG UltraScale DDR4支持最高2级。https://forums.xilinx.com/t5/Memory-Interfaces

2020-04-22 08:36:21

我有一段时间让恶意生成的内容工作。我是一个超级菜鸟,所以我认为这对我来说是一个非常普遍的过程,但我需要一只手学习如何克服困难。我想我来自编程,我希望MIG能够生成应该自己编译的库。但是,我发现事实

2019-08-06 07:54:35

存储器接口生成器(MIG)解决方案---Virtex-4 存储器接口和Virtex-II Pro存储器解决方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

大家好 我的问题是DDR3校准完成失败。调试结果:dbg_wrcal_err = 1,通过波形,我们可以看到写入模式不匹配。 我的问题是MIG IP Core配置中是否有任何参数可以调整它?或者我

2020-07-23 10:09:37

创建我放置Zynq PS和互连的设计,并将主引脚作为输出,以便在Artix中我使用Slave引脚作为输入进行另一种设计并通过AXI控制MIG ,来自Zynq?将Zynq项目导出到SDK时,如果找不到

2020-08-04 10:04:05

嗨,我正在尝试用我的设计生成带有MIG3.2的DDR3控制器,并修改example_design项目以适应我的电路板。在更改.ucf文件之前,实现成功。但在改变.ucfaccording我的设计后

2020-06-10 08:25:16

所以我在Vivado 2013.4中有一个使用MIG 7 IP模块的设计,它之前完成了合成和实现。我收到一条消息说合成和实现已经过时并决定再次运行它,据我所知,在此之前我没有改变项目中的任何内容

2020-04-06 15:47:46

求大神指导,我用的芯片是k7系列XC7K325TFFG676,内存是MT41K256M16HA,在vivado环境下通过AXI总线将MIG与microblaze相连,实现控制数据在DDR3的存读。差

2018-04-24 18:44:45

嗨,我有一个新的VCU108板。我正在尝试运行预定义的MIG测试,以便开始使用。我使用本指南作为参考。https://www.xilinx.com/support/documentation

2019-09-30 06:18:43

你好,先生,当我使用mig 7核心时,我遇到了这些错误(合成传递),[放置30-69]实例U_mig_7series_0 / u_mig_7series_0_mig

2020-08-24 09:15:36

请问光电开关如何控制步进电机正反转?

2021-10-14 08:31:50

DDR3的系统时钟?如何在MIG工具中使用NO BUFFER?clcok资源能实现这一目标吗?我已经尝试了,但它失败了。我注意到它在数据表中说系统时钟必须与mig相同,它是否重要?我很想知道如何将这个MRCC引入MMCM,PLL或BUFGDS,或其他类似的东西。谢谢。

2020-07-22 07:43:59

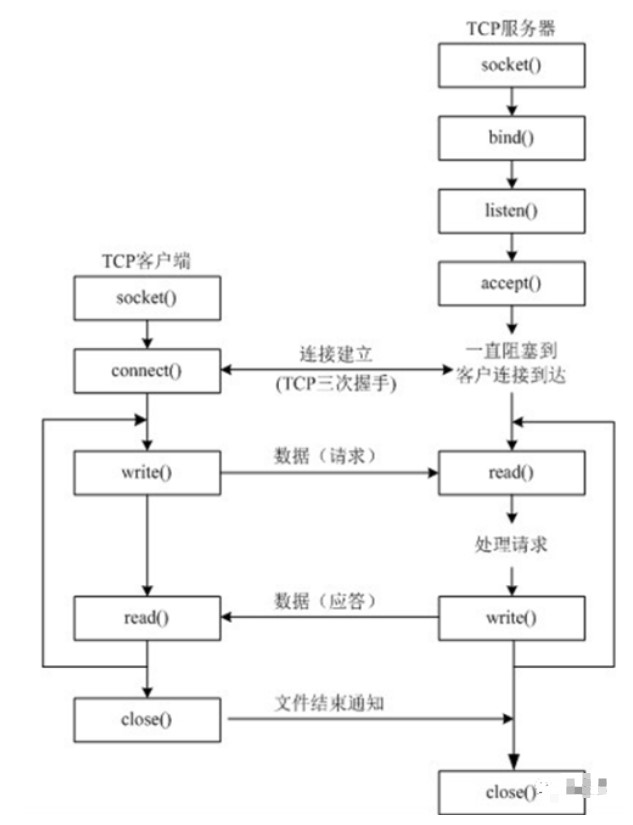

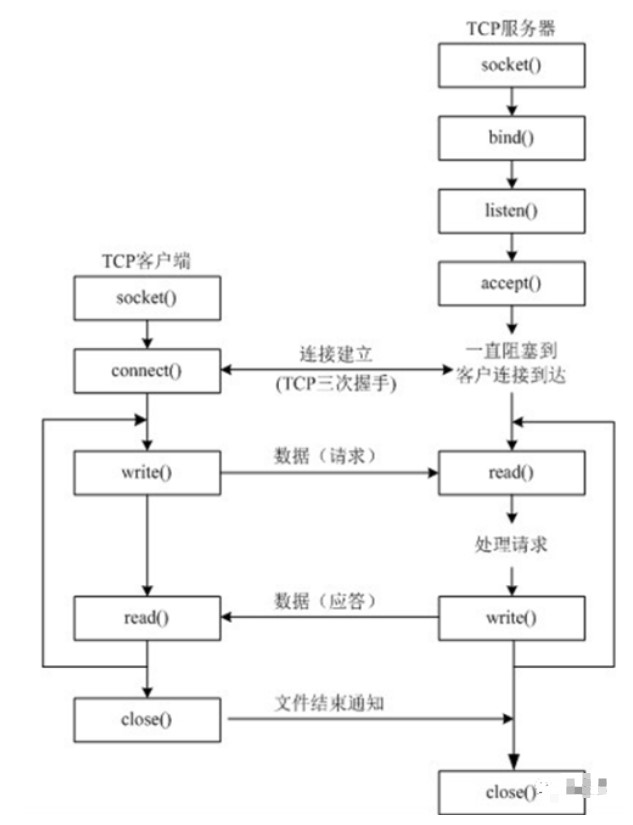

针对七自由度机械臂远程控制的需要,构建了基于TCP/IP 网络的控制系统。首先通过设计单片机系统实现本地端控制,然后运用WinSockets 类创建基于TCP/IP 的远程控制程序,使连接在Inte

2009-08-15 16:01:43 22

22 针对TCP 在高速网络中的缺陷,提出了改进的BIC TCP 拥塞控制算法。优化算法通过监控链路缓存的变化,调整探索可用带宽过程中的拥塞窗口增加值,当拥塞发生时将慢启动门限和拥

2009-09-17 10:18:17 15

15 TCP端到端等效噪声模型及拥塞控制方法研究:针对传统TCP拥塞控制协议在有线/无线混合网络中存在的问题,采用通信系统加性噪声分析方法和信道容量理论,将端到端链路背景流量等

2009-10-20 17:49:47 7

7 光电式液位开关和控制器

2009-12-16 15:15:40 20

20 随着互联网规模的增长,拥塞已经成为一个重要的研究热点。介绍了TCP 拥塞控制的四种基本算法。TCP 拥塞算法对这些基本算法进行组合,分析其不同的特点,并且通过建模对算法组

2009-12-25 15:14:29 20

20 本文针对30mm厚的7A52中厚板高强铝合金,进行了单丝单脉冲、复合脉冲和双丝Tandem MIG焊工艺的研究,并应用于生产中。

2009-12-26 15:06:57 9

9 研究了双脉冲MIG焊工艺对2219高强铝铜合金焊缝组织及性能的影响,通过正交试验确定了适合于2219铝铜合金焊接的最佳双脉冲MIG焊工艺参数。实验结果表明,采用上述工艺参数焊接,

2009-12-26 15:09:46 11

11

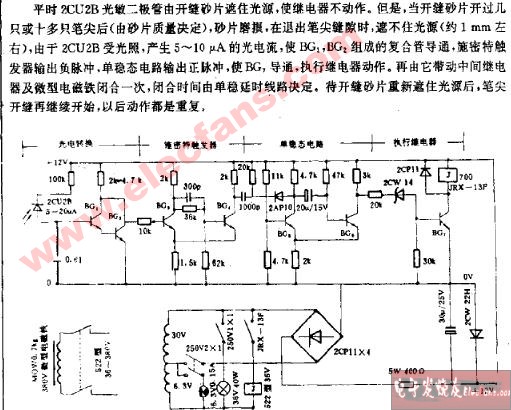

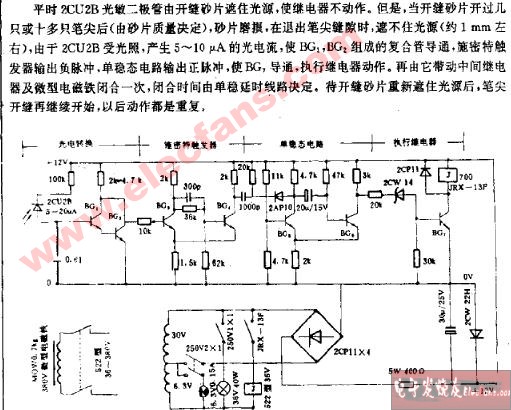

笔尖开缝控制的光电控制电路

2009-02-06 00:28:09 710

710

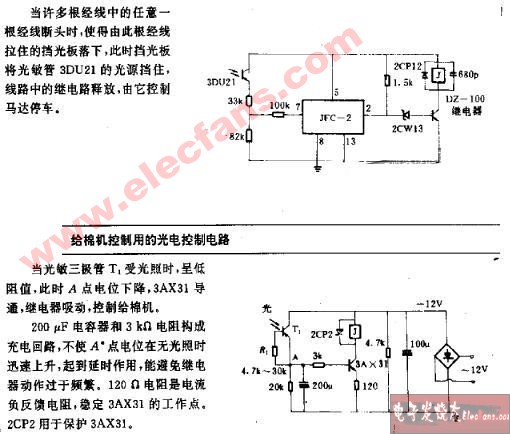

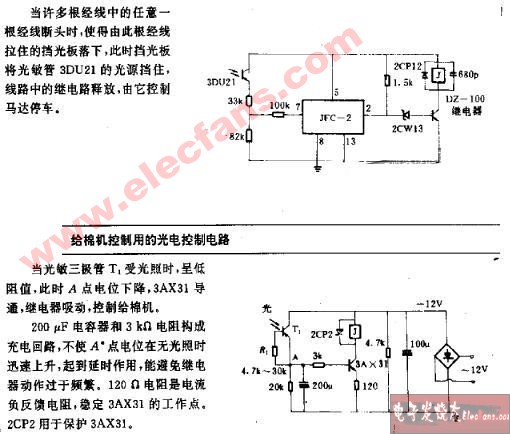

给棉机控制用的光电控制电路

2009-02-06 12:00:56 489

489

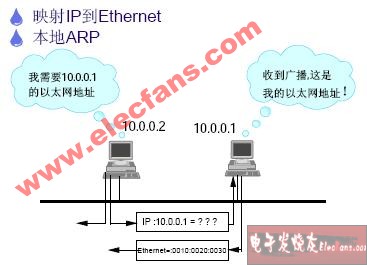

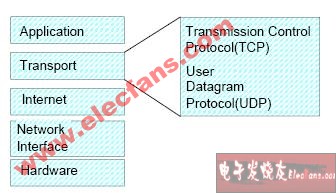

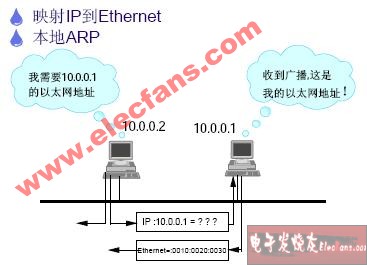

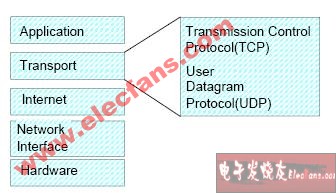

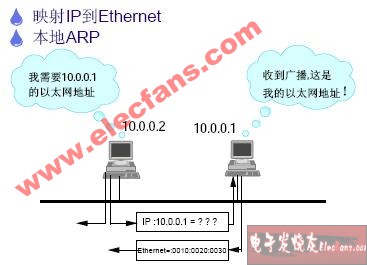

TCP/IP 传输层协议概揽

传输控制协议 TCP 是一个面向联接的协议,允许从一台

2009-06-09 21:51:51 732

732

TCP/IP传输层协议概揽

传输控制协议 TCP 是一个面向联接的协议,允许从一台

2009-06-09 21:52:31 869

869

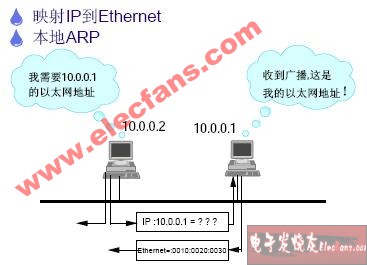

TCP/IP协议简介

TCP/IP传输层协议概揽

传输控制协议 TCP 是一

2009-06-09 23:07:31 1205

1205

什么是TCP

英文原义:Transmission Control Protocol

中文释义:(RFC-793)传输控制协议

注

2010-02-23 11:45:26 936

936 传输控制协议(TCP)/网络层协议是什么意思

传输控制协议(TCP)

TCP提供的是一种可靠的数据流服务。当传

2010-04-06 16:44:14 2688

2688 首先分析了面向控制应用TCP/IP协议的特点,随后阐述了两种针对专用控制网络的以太网网关实现方案,即MCU或DSP+以太网网络接口的TCP/IP实现。

2011-10-09 18:23:26 40

40 MIG 亚洲会议同时开启中国物联网企业的创新体验之旅

2015-08-05 11:34:34 910

910 经典款逆变气保焊MIG250一体机整机接线图。

2016-03-17 10:42:25 6

6 全数字脉冲MIG逆变焊接电源的研制,下来看看。

2016-03-30 14:37:55 22

22 TCP-IP详解卷2 TCP:传输控制协议,学习TCP很好的资料。欢迎下载。

2016-05-09 14:33:50 0

0 学习TCP-IP的很好的书。TCP-IP详解卷3。

2016-05-09 14:33:50 0

0 学习TCP-IP的很好的书。TCP-IP详解卷3。

2016-05-09 16:07:18 0

0 学习TCP-IP的很好的书。TCP-IP详解卷3。

2016-05-09 16:07:18 0

0 学习TCP-IP的很好的书。TCP-IP详解卷3。

2016-05-09 16:07:18 0

0 学习TCP-IP的很好的书。TCP-IP详解卷3。

2016-05-09 16:07:18 0

0 学习TCP-IP的很好的书。TCP-IP详解卷1。

2016-05-10 15:44:50 0

0 基于滑模控制的TCP网络自适应研究_冯卫华

2017-01-28 21:37:15 0

0 TCP( Transmlssion Control Protocol)处于Internet协议栈体系结构中的传输层,它采用确认重发和流量控制机制,为传输层提供了可靠的、面向连接的字节流服务。它的传输

2018-02-08 16:29:08 0

0 软开关型脉冲MIG焊接电源系统整体结构如图1所示,由主电路、控制电路、驱动电路3个主要部分组成。系统采用目前较为常用的AC/ DC/AC/DC的逆变模式,脉冲开关信号来自单片机给出的控制指令,经驱动和放大后,为功率开关管提供固定频率为20 kHz的高频脉冲开关信号。

2018-04-13 08:25:00 3169

3169

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。

2019-03-03 11:11:53 5644

5644

本文档的主要内容详细介绍的是MIG250 MOS管整机电路原理图免费下载。

2019-04-22 08:00:00 23

23 本文档的主要内容详细介绍的的是MIG-250单管IGBT整机电路原理图免费下载。

2019-04-22 08:00:00 31

31 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7391

7391

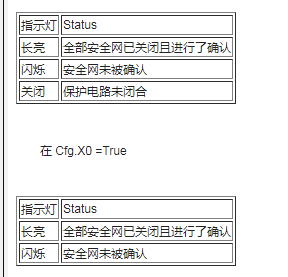

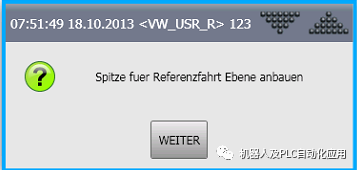

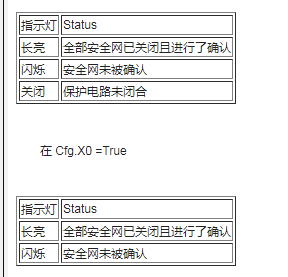

VASS标准中急停得接法与控制方法 1.硬线连接使用外部供电或者内部供电,双通道监控。 SIL3/PLe • 必须通过两个通道对传感器/编码器信号进行分析(“2 out

2020-12-23 16:48:35 3949

3949

其实不想用这个题目的,只因为TCP相关的东西比较吸引人的眼球,这篇文章的主题还是eBPF,而不是TCP。 用eBPF写TCP拥塞控制算法只是本文所讲内容的一个再平凡不过的例子。 先看两个问题,或者说

2020-12-26 09:44:14 1437

1437 VASS标准PLC工位时序控制要点

1.顺序块 顺序控制

2021-03-10 11:33:41 1854

1854 VASS标准中安全门的接法与控制方法

系统安全程序使用 : SFDOOR:安全门监视

2021-03-18 09:55:10 4204

4204

Profinet 诊断 操作页面包含以下功能范围: 显示所有 Profinet 参与者的状态信息和导航到 Profinet 详细诊断 Profinet I/O 拓扑 这一点VASS06的界面

2021-06-09 16:46:55 2707

2707 1. 文章研究主要问题双弧脉冲 MIG 焊是一种低能量输入焊接方法, 其原有的双电源供电系统结构复杂、协同控制困难、易受干扰。2. 结论提出了双弧脉冲 MIG 焊一体化专用电源的设计方案

2021-11-08 20:51:02 11

11 TCP(Transmission Control Protocol 传输控制协议)是一种面向连接(连接导向)的、可靠的、 基于IP的传输层协议。

2022-05-25 15:38:45 1330

1330

为了实现 VASS 标准中的预期功能范围,CPU 1517F至少需要固件版本 V2.5。

2022-07-15 10:50:01 1600

1600 传输控制协议(TCP,Transmission Control Protocol)是一种面向连接的、可靠的、基于字节流的传输层通信协议。

2022-08-19 09:17:23 2433

2433

VASS06由于PLC使用博途1500,博途1500,具有ProDiag功能,因此VASS06PLC的报警功能通过ProDiag来实现的!

2023-01-05 10:04:44 793

793 TCP(Transmission Control Protocol,传输控制协议),它是最常用传输层协议,也是最稳定传输层协议,很多上层应用都是依赖于TCP进程传输数据。

2023-02-14 10:26:23 2141

2141 之前有人发表论文说用chatGPT写了一个MCU 还流片了,一副很腻害的样子,在这个新闻的前几天我就在朋友圈里说了,用chatGPT写verilog代码还是有一段距离的。今天我就手把手教大家,如何把这段距离给走了。今天用我让chatGPT写MIG 控制器为例,一句代码都不想写。

2023-07-10 09:12:11 222

222

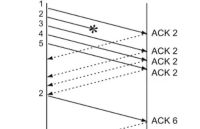

今天分享一篇文章,是关于 TCP 拥塞控制对数据延迟产生的影响的。作者在服务延迟变高之后进行抓包分析,结果发现时间花在了 TCP 本身的机制上面:客户端并不是将请求一股脑发送给服务端,而是只发送

2024-01-19 09:44:05 202

202

电子发烧友App

电子发烧友App

评论