高DV/DT开关区

图2和图4中,在VIN(或VOUT)与地之间的SW电压摆幅有高的dv/dt速率。这个结点上有丰富的高频噪声分量,是一个强大的EMI噪声源。为了尽量减小开关结点与其它噪声敏感走线之间的耦合电容,你可能会让SW铜箔面积尽可能小。但是,为了传导大的电感电流,并且为功率MOSFET管提供散热区,SW结点的PCB区域又不能够太小。一般建议在开关结点下布放一个接地铜箔区,提供额外的屏蔽。

如果设计中没有用于表面安装功率MOSFET与电感的散热器,则铜箔区必须有足够的散热面积。对于直流电压结点(如输入/输出电压与电源地),合理的方法是让铜箔区尽可能大。

多过孔有助于进一步降低热应力。要确定高dv/dt开关结点的合适铜箔区面积,就要在尽量减小dv/dt相关噪声与提供良好的MOSFET散热能力两者间做一个设计平衡。

功率焊盘形式

注意功率元件的焊盘形式,如低ESR电容、MOSFET、二极管和电感。图8a(略)和8b(略)分别给出了不合理和合理的功率元件焊盘形式。

对于去耦电容,正负极过孔应尽量互相靠近,以减少PCB的ESL.这对低ESL电容尤其有效。小容值低ESR的电容通常较贵,不正确的焊盘形式及不良走线都会降低它们的性能,从而增加整体成本。通常情况下,合理的焊盘形式能降低PCB噪声,减小热阻,并最大限度降低走线阻抗以及大电流元件的压降。

大电流功率元件布局时有一个常见的误区,那就是不正确地采用了热风焊盘(thermal relief),如图8a(略)所示。非必要情况下使用热风焊盘,会增加功率元件之间的互连阻抗,从而造成较大的功率损耗,降低小ESR电容的去耦效果。如果在布局时用过孔来传导大电流,要确保它们有充足的数量,以减少阻抗。此外,不要对这些过孔使用热风焊盘。

图9(略)是有多个板上电源的应用,这些电源共享相同的输入电压轨。当这些电源互相不同步时,就需要将输入电流走线隔离开来,以避免不同电源之间耦合公共阻抗噪声。每个电源拥有一个本地的输入去耦电容倒是不太关键。

对于一只PolyPhase单输出转换器,为每个相做一个对称布局有助于热应力的均衡。

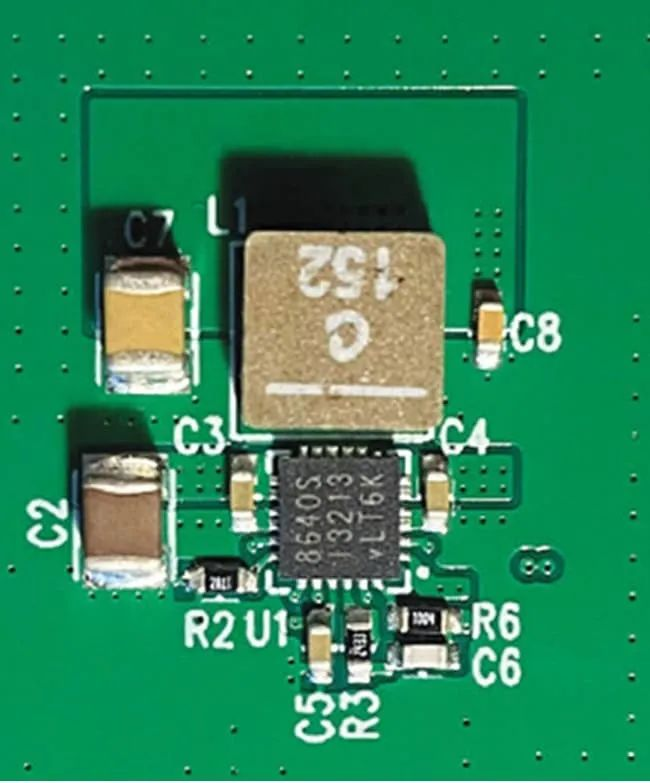

布局设计实例

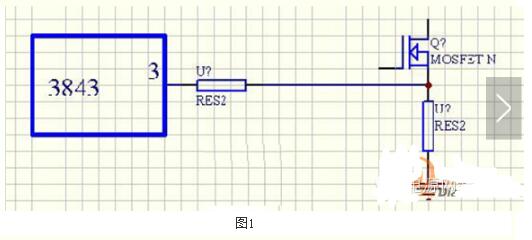

图10(略)是一个设计实例,它是一个3.5V~14V,最大输出1.2V/40A的双相同步降压转换器, 使用了LTC3855 PolyPhase电流模式步进降压控制器。在开始PCB布局前,一个好的习惯是在逻辑图上用不同颜色特别标示出大电流走线、高噪声的高dv/dt走线,以及敏感的小信号走线。这种图将有助于PCB设计者区分开各种走线。

图11(略)是这个1.2V/40A电源的功率元件层上的功率级布局例子。图中,QT是高侧控制MOSFET,QB是低侧同步FET.可选择增加QB的接地面积,以获得更多的输出电流。在功率元件层的下方,放了一个实心的电源地层。

控制电路布局

使控制电路远离高噪声的开关铜箔区。对降压转换器,好的办法是将控制电路置于靠近VOUT+端,而对升压转换器,控制电路则要靠近VIN+端,让功率走线承载连续电流。

如果空间允许,控制IC与功率MOSFET及电感(它们都是高噪声高热量元件)之间要有小的距离(0.5英寸~1英寸)。如果空间紧张,被迫将控制器置于靠近功率MOSFET与电感的位置,则要特别注意用地层或接地走线,将控制电路与功率元件隔离开来。

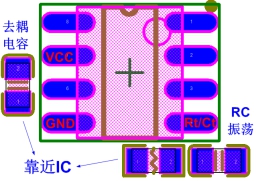

图12(略)是LTC3855电源的较好的隔离地方案,IC有外露的GND焊盘,应焊到PCB上,以尽量减少电气阻抗与热阻。几只关键去耦电容应紧挨着IC引脚。

控制电路应有一个不同于功率级地的独立信号(模拟)地。如果控制器IC上有独立的SGND(信号地)和PGND(功率地)引脚,则应分别布线。对于集成了MOSFET驱动器的控制IC,小信号部分的IC引脚应使用SGND.

信号地与功率地之间只需要一个连接点。合理方法是使信号地返回到功率地层的一个干净点。只在控制器IC下连接两种接地走线,就可以实现两种地。图12(略)给出了建议的LTC3855电源接地隔离法。在本例中,IC有一个外露的接地焊盘。此焊盘应焊到PCB上,以尽量减少电气阻抗与热阻。应在接地焊盘区放置多个过孔。

控制IC的去耦电容应靠近各自的引脚。为尽量减少连接阻抗,好的方法是将去耦电容直接接到引脚上,而不通过过孔。如图12(略)所示,应靠近置放去耦电容的LTC3855引脚是电流检测引脚Sense+/Sense-,补偿引脚ITH,信号地SGND,反馈分压器脚FB,IC VCC电压引脚INTVCC,以及功率地引脚PGND.

回路面积与串扰

两个或多个邻近导体可以产生容性耦合。一个导体上的高dv/dt会通过寄生电容,在另一个导体上耦合出电流。为减少功率级对控制电路的耦合噪声,高噪声的开关走线要远离敏感的小信号走线。如果可能的话,要将高噪声走线与敏感走线布放在不同的层,并用内部地层作为噪声屏蔽。

空间允许的话,控制IC要距离功率MOSFET和电感有一个小的距离(0.5英寸~1英寸),后者既有大噪声又发热。

LTC3855控制器上的FET驱动器TG、BG、SW和BOOST引脚都有高的dv/dt开关电压。连接到最敏感小信号结点的LTC3855引脚是:Sense+/Sense-、FB、ITH和SGND.如果布局时将敏感的信号走线靠近了高dv/dt结点,则必须在信号走线与高dv/dt走线之间插入接地线或接地层,以屏蔽噪声。

在布放栅极驱动信号时,采用短而宽的走线有助于尽量减小栅极驱动路径中的阻抗。在图13(略)中,布放的高FET驱动器走线TG与SW应有最小的回路面积,以尽量减小电感与高dv/dt噪声。同样,低FET驱动器走线BG要靠近一根PGND走线。

如果在BG走线下布放了一个PGND层,低FET的交流地返回电流将自动耦合到一个靠近BG走线的路径中。交流电流会流向它所发现的最小回路/阻抗。此时,低栅极驱动器不需要一个独立的PGND返回走线。最好的办法是尽量减少栅极驱动走线通过的层数量,这样可防止栅极噪声传播到其它层。

在所有小信号走线中,电流检测走线对噪声最为敏感。电流检测信号的波幅通常小于100mV,这与噪声的波幅相当。以LTC3855为例,Sense+/Sense-走线应以最小间距并行布放(Kelvin检测),以尽量减少拾取di/dt相关噪声的机会,如图14(略)所示。

另外,电流检测走线的滤波电阻与电容都应尽可能靠近IC引脚。当有噪声注入长的检测线时,这种结构的滤波效果最好。如果采用带R/C网络的电感DCR电流检测方式,则DCR检测电阻R应靠近电感,而DCR检测电容C则应靠近IC.

如果在走线到Sense-的返回路径上使用了一个过孔,则过孔不应接触到其它的内部VOUT+层。否则,过孔可能会传导大的VOUT+电流,所产生的压降可能破坏电流检测信号。要避免在高噪声开关结点(TG、BG、SW和BOOST走线)附近布放电流检测走线。如可能,在电流检测走线所在层与功率级走线层之间放置地层。

如果控制器IC有差分电压远程检测引脚,则要为正、负远程检测线采用独立的走线,同时也采用Kelvin检测连接。

走线宽度的选择

对具体的控制器引脚,电流水平和噪声敏感度都是唯一的,因此,必须为不同信号选择特定的走线宽度。通常情况下,小信号网络可以窄些,采用10mil~15mil宽度的走线。大电流网络(栅极驱动、VCC以及PGND)则应采用短而宽的走线。这些网络的走线建议至少为20mil宽。

电子发烧友App

电子发烧友App

评论