引言

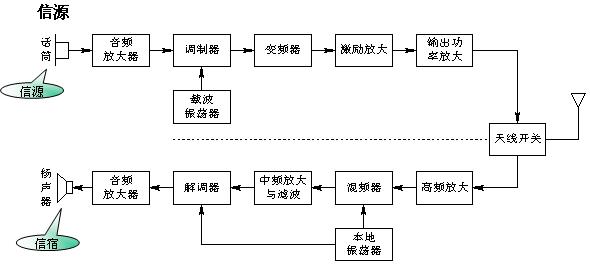

随着频率资源的日趋紧张,短距离无线通信按窄带化趋势发展。无线数传模块一般由微处理器和收发芯片组成,本文所设计的窄带数传模块的微处理器采用了STM32F103ZE芯片,收发芯片选用了TI公司新推出的CC1120,CC1120通过SPI串行总线协议与MCU相连接。同时,采用了可移植、可植入ROM、可裁剪、抢占式的实时多任务操作系统μC/OS—III作为软件平台。

1 系统硬件电路

1.1 CC1120的内部结构

CC1120是TI公司专为经济高效的无线系统在低功耗和低电压操作下,实现数据传输而设计的一款完全集成的单芯片无线收发器。该芯片主要应用于ISM(工业、科学和医疗)以及SRD(短程设备)频带。CC1120的主要特性有:体积小,超低功耗,可配置数据速率(1.2~200kbps),可编程控制输出功率(步长为0.5 dB,最高功率16 dBm),接收机灵敏度高(1.2 kbps数据速率下为123 dBm),还支持2FSK、2GFSK、4FSK、4GFSK、MSK、ASK、OOK及模拟FM多种调制方式等。

CC1120的内部结构框图如图1所示。CC1120具有一个低功耗IF接收机,低噪声放大器(LNA)将接收到的RF、信号放大,并在求积分(I和Q)过程中被降压转换至中频(IF)。在IF下,I/Q信号被ADC数字化。自动增益控制(AGC)、精确信道滤波和调制解调位/数据包同步均以数字方式完成。CC1120的发射器部分基于RF频率直接合成,频率合成器包括一个完全片上LC VCO和一个90°相位转换器,用来在接收模式下向降压转换混频器生成I和Q本振信号。一个4线SPI串行接口用于配置数据和缓冲区存取。数字基带包括了对信道配置、数据包处理以及数据缓冲的支持。

1.2 CC1120的配置特性

配置寄存器的读、写操作时序如图2所示。通过一个4线串行SPI兼容接口(SI、SO、SCLK和CSn)可对CC1120进行配置,该接口还可用于读取和写入缓冲数据。SPI接口上的所有数据传输均以最高位开始。

SPI接口上的所有事务均以一个报头字节作为开始,该字节包含一个R/W位、一个突发存取位(B)以及一个6位地址(A5~A0),报头字节帧格式如图3所示。在SPI总线上传输数据期间,CSn引脚必须保持低电平,否则传输就会被取消。拉低CSn电平时,在开始传输该报头字节以前,MCU必须等待,直到SO引脚变为低电平为止。这表明,芯片正在运行。除非芯片处在SLEEP或XOFF状态,否则SO引脚总会在CSn变为低电平以后立即变为低电平。

CC1120的寄存器空间主要作为CC1120的频率、数据速率、中频等大部分参数的配置。而扩展寄存器大部分为芯片配置辅助测试寄存器(只读),少部分为配置寄存器(可读写)。指令选通用于芯片状态切换和冲刷RX/TXFIFO。128字节TX FIFO和128字节RX FIFO均通过0x3F地址进行存取。当R/W位为0时,则TX FIFO被存取;当R/W位为1时,则RX FIFO被存取。其中,TXFIFO为只写,而RX FIFO为只读。寄存器地址映射如图4所示。

1.3 硬件连接关系

窄带无线数据传输系统的STM32F103ZE与无线收发芯片的硬件连接关系如图5所示。左侧为STM32F103ZE,它是一个32位、基于ARM Cort ex—M3内核的无线收发芯片。除了正常工作模式外,还支持睡眠、待机、停机工作模式,当所有外设都处于工作模式时消耗36 mA,待机时下降到2μA。CC1120内部集成的SPI接口的传输速率最高可达到18 Mbps。

右侧为无线收发芯片CC1120。CC1120的外部控制引脚主要有复位接口、SPI串行接口以及4个通用输出引脚GPIO0~GPIO3。其中,4个通用输出引脚在实际应用中,可以通过配置寄存器使它们为上层实时提供同步字或数据包收发状态等应用。在硬件平台上,CC1120的SPI串行接口(CSn、SCLK、SI、SO)分别连接到STM32F103ZE相应的4个SPI串行通信弓I脚(即SPI2_NSS、SPI2_SCLK、SPI2_MOSI、SPI2_ISO上)。通过这4根线,TM32F103ZE可以对CC1120进行参数配置、芯片状态切换以及RX/TX FIFO的读写。由于CC1120只有SPI从模式,因此TM32F103ZE采用SPI主模式。另外,本方案还采用了1个通用数字输出引脚GPIO0,用来实现数据包分组发送指示。同时,TM32F103ZE可以通过控制RESET引脚,复位无线收发芯片。

通信方式为SPI串行通信时,时钟源由STM32F103ZE提供,通过配置处理器寄存器,SPI的SCLK时钟频率为4.5 MHz。通过TM32F103ZE内部的8位移位寄存器,实现CC1120与STM32F103ZE的串行数据交换。CSn引脚主要用来控制数据通信的同步性,通信期间要始终保证CSn引脚的电平为低。但是,需要注意的是CC1120的CSn引脚的时序并未完全遵照SPI时序规范,因此,STM32F103ZE的SPI2_NSS引脚需要设置成普通GPIO接口模式,并采用软件控制方式。

2 软件平台

μC/OS—III实现了一个基于优先级调度的抢占式内核,并在这个内核之上提供了最基本的系统服务,例如信号量、邮箱、消息队列、内存管理、中断管理等,但它并不提供设备管理和文件系统管理。

信号量用于控制共享资源的访问,可用于中断服务子程序与任务间、任务与任务间的同步。本设计中采用信号量机制来管理两个共享资源,发送缓冲区和接收缓冲区。读任务、中断服务子程序和接收环形缓冲区之间的关系如图6所示。图中的共享资源为接收环形缓冲区,IN和OUT分别为入队和出队指针。当IN等于OUT时,则接收环形缓冲区为空,调用OSSemPend()阻塞读任务;当IN不等于OUT时,如果读任务被阻塞,则在中断服务子程序中调用OSSemPost()唤醒读任务。

3 CC1120驱动实现

本文参考了国内研究者提出的μC/OS下通用驱动框架模型,将CC1120驱动架构模型划分成上层访问抽象接口层、硬件设备驱动模块层和硬件设备接口操作层。其中,上层访问抽象接口层通过对硬件平台的抽象,可以在系统开发中向上层应用屏蔽硬件特征,从而实现软/硬件的分离;硬件设备驱动模块层是整个驱动框架的中间封装层,通过该层的封装,对上一层屏蔽了SPI硬件接口;而硬件设备接口操作层是实现对底层硬件SPI串行接口的功能操作,通过调用该层接口,可以实现CC1120提供的全部功能。

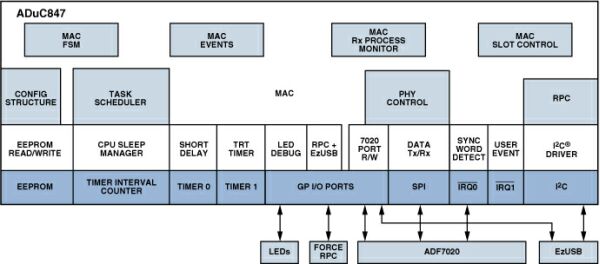

3.1 驱动体系结构

CC1120的驱动体系结构如图7所示。上层访问抽象接口层是驱动体系中的最高层,该模块主要实现了数据包发送与接收功能,并对无线收发芯片的状态进行控制和获取RSSI值。其中,perCC1120Init()接口主要完成CC1120的初始化、启动并配置芯片等功能;perCC1120Read()实现数据包的接收,以及对读缓冲区的管理;perCC1120Wrire()实现数据包的发送,以及对写缓冲区的管理;perCC1120Ioctl()实现了CC11 20的各个工作状态的切换(包括休眠和唤醒)和获取RSSI值。

硬件设备驱动模块层实现对上层访问抽象接口层操作,屏蔽了硬件SPI接口,提供了对CC1120的寄存器和FIFO的读写操作。其中,CC1120 SpiWriteReg()和CC1120SpiReadReg()分别提供了寄存器的写和读操作功能,屏蔽了8位和16位寄存器的区别;CC1120SpiWriteTxFifo()和CC1 120SpiReadRxFifo()提供了FIFO的连续写和读操作功能。

硬件设备接口操作层是对CC1120的硬件SPI接口的直接操作和软件表达,该层为整个驱动模块提供了SPI同步串行通信机制。其中,trx8 BitRegAccess()实现了8位寄存器的存取功能;trx16BitRegAccess()实现了16位寄存器的存取功能;trxSpiCmdStrobe()实现了芯片的指令选通功能,用于芯片工作状态切换。

本文结合CC1120驱动体系结构,简要介绍其主要功能,即数据包的收发。

应用层发送数据包之前,先调用perCC1120Ioctl()获取信道的RSSI值,当RSSI值低于信道忙碌的门限值时,则调用perCC1120Write()将需要发送的数据发送出去。perCC1120Write()的工作流程图如图8所示。本文使用了CC1120的通用GPIO0引脚,通过适当配置,该引脚电平会在发送或者接收完一个数据包时产生一个下降沿跳变。当上一包数据包发送完毕之后,GPIO0触发中断,STM32F103ZE进入中断处理程序,将会发送写缓冲区中的下一包数据包,直至发送缓冲区为空,再把CC1120置于空闲或休眠状态。

当上层不处于发送状态时,CC1120都将置于接收状态或增强型无线电唤醒状态,当接收到一个数据包时,GPIO0引脚产生一个下降沿中断,STM32F103ZE进入中断处理程序,调用CC1120SpiReadRxFifo(),从接收缓冲RXFIFO中读取数据包,并将其放入接收环形缓冲区中。如果接收环形缓冲区满时,将放弃当前接收到的数据包。上层通过调用perCC1120Read()接口读取接收到的数据包,当接收缓冲区为空时,将阻塞上层的读取进程。perCC1120Read()的工作流程图如图9所示。

3.2 CC1120的配置要点

(1)寄存器配置软件

针对CC1120的寄存器配置,TI公司提供了SmartRFStudio 7软件。通过这个软件可以对CC1120进行配置,以获得最佳寄存器设置以及性能和功能评估。配置软件根据用户输入的发射频率、晶振频率、符号速率等参数,生成相应的寄存器配置信息。

(2)数据包处理的硬件支持

CC1120内部支持的数据包处理方式有前导码、同步字、地址过滤、CRC、数据白化、状态字节、字节倒置等,同时,数据包长度类型支持固定长、可变长、无限长3种模式,可以通过手动配置PKT_CFG0~PKT_CFG2来实现。

(3)增强型无线电唤醒

在程序的实现过程中,当CC1120长时间没有接收到数据时,则开启增强型无线电唤醒功能(寄存器WOR_CFG0.RC_PD=0),并发送SWOR指令选通命令,将芯片工作状态切换到睡眠状态。CC1120将在MCU不干涉的前提下,周期性地从睡眠状态中唤醒并监听数据包的到来,从而降低系统的整体功耗。

(4)接收的信号强度指示

CC1120在接收状态下,能连续地从RSSI状态寄存器(RSSI0、RSSI1)中读取到RSSI值,直到检测到一个有效的同步字,其后RSSI读取值将被冻结。通过设置寄存器AGC_CFG1.AGC_SYNC_BEHAVIOR,可以解除RSSI值被冻结的状态。

(5)通用数字输出引脚(GPIO0~GPIO3)

在实际应用中,可以通过寄存器(IOCFG0~IOCFG3)配置,为上层实时提供信道或数据包状态等信息。本设计将寄存器IOCFG0的值设置为0x06,即利用了GPIO0引脚的电平跳变特点。当CC1120发送完或接收到一包数据包,触发MCU端口产生中断,并在中断服务程序中进行写入或读取缓冲区TX/RX FIFO等操作,使STM32F103ZE有更多时间处理其他事务或处于休眠状态,达到降低整个系统功耗的目的。

结语

基于μC/OS—III和CC1120的短距离窄带无线数传系统方案,可以实现低功耗、近距离、可靠的无线数据传输,具有成本低、可扩展性强、操作灵活简单的特点。通过对CC1120和STM32F103ZE进行适当的配置,硬件能在无数据收发的状态下,自动进入低功耗的睡眠或待机状态,可以大大降低硬件系统的整体功耗。大量测试结果表明,该窄带无线数据传输系统数据收发正常,整个系统运行稳定,具备RSSI检测、休眠唤醒等相关功能。

电子发烧友App

电子发烧友App

评论