摘 要: 针对传统固定监控架设成本高、监控有死角且需要布置的视频采集端个数太多的情况,提出一种基于ARM和FPGA相结合架构的移动视频监控系统及其软硬件实现方法,在减少视频采集端节点的前提下,能够全方位实时捕捉用户所需的信息。该系统由电机控制模块、视频采集模块和无线网络控制模块构成,实现了无线视频监控系统;基于Linux操作系统、Web服务器和视频编码器,实现了用户可以通过Internet远程查看目标现场的状况。

中国视频监控市场快速发展,数字监控逐步成为主流,网络化、个人化和智能化将是中国视频监控市场重要的发展趋势。但当前基于流媒体传输的技术对网络条件要求较高,不能大面积推广,固定监控成本太高。如何将视频监控与Interne相结合,使监控人员可以随时随地实施监控,是现代监控技术急需解决的问题。另一方面,目前视频监控系统采用的微控制器多是ARM9、ARM11等系列微控制器,ARM微控制器硬件外设出厂时已经固定,不利于用户进行硬件扩展和升级,而ARM和FPGA相结合的多芯片解决方案又会导致系统成本太高,同时还会造成系统资源的浪费,功耗太大。针对以上不足,本文提出了一种新的解决方案,采用Zynq系列处理器,芯片采用的是高性能Cortex-A9双核和FPGA相结合,ARM部分可以解决高清视频的处理问题,可编程逻辑FPGA部分可以升级和扩展硬件。

1 移动视频监控系统架构

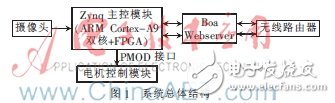

本设计的主控板为Digilent公司的ZedBoard开发板,主芯片Zynq7020结合高性能双核ARM Cortex-A9 MPCore处理系统和可编程逻辑于一体[1]。视频采集端位于移动小车之上,从而达到移动采集视频的目的。系统的设计主要包括ARM控制部分的设计和FPGA逻辑部分的设计。ARM部分主要用来运行操作系统和系统上的应用软件,如Web服务器Boa,视频编码器mjpg-streamer;FPGA部分主要用来扩展硬件资源,进行小车电机驱动部分PWM IP核的设计。系统总体结构框图如图1所示。各模块功能为:摄像头负责视频图像采集,Zynq主控模块负责ARM操作系统部分和FPGA逻辑资源部分,电机控制模块负责智能小车的运动,Boa Webserver负责网络的交互,无线路由器负责无线网络数据的收发。

系统上电之后,首先自动执行芯片内部固化的芯片初始化程序,然后执行第一阶段的启动加载器FSBL,使用比特流文件(PWM IP核设计生成的bit文件)对FPGA部分进行配置,待FPGA配置完成后,开始执行U-boot引导程序,启动Linux操作系统[2]。系统启动完成后,智能小车通过无线路由器产生无线信号,用户在另一端就可以通过网络来连接智能小车终端,实施视频监控。用户和系统的交互实现如图2所示。

本文主要介绍电机控制部分的设计,具体包括电机控制部分硬件电路的设计,FPGA部分PWM IP核的设计,Linux操作系统PWM驱动程序的设计。

2 电机控制部分的设计

2.1 电机控制部分硬件电路的设计

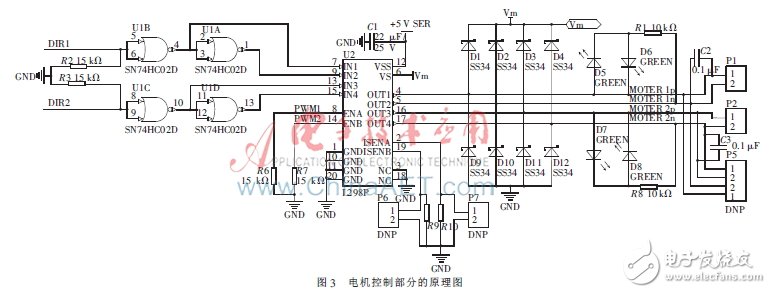

该模块主要由L298P双H桥直流电机驱动芯片实现。由于一个L298P芯片可以驱动两个直流电机,小车有4个车轮,因此需要两块L298P芯片[3]。同时,为了减少使用的FPGA I/O引脚数量,在原理图设计中采用了四二输入或非门芯片SN74HC02D,这样用两个I/O引脚就可以控制L298P的4个输入端。DIR1、DIR2、PWM1、PWM2通过Zedboard的PMOD接口与FPGA相连。原理图如图3所示,图中IN1、IN2、IN3、IN4为输入信号,ENA、ENB为使能信号。ENA控制IN1、IN2的输入使能,ENB控制IN3、IN4的输入使能。当ENA为1,DIR1为1时(也就是IN1为0,IN2为1时),P1接口上的电动机正转;当ENA为1,DIR1为0时(也就是IN1为1,IN2为0时),P1接口上的电动机反转;当ENA为0时,P1接口上的电动机停止。与P2口连接的电动机原理同上。

2.2 FPGA部分PWM IP核的设计

Xilinx嵌入式系统部分的设计由其公司推出的EDK(Embedded Development Kit)开发套件实现,EDK具有完成嵌入式系统设计的一整套工具,即:硬件设计工具XPS(Xilinx Platform Studio)和软件设计工具SDK(Xilinx Software Development Kit),硬件设计步骤如下:(1)设置新工程路径;

(2)自定义IP配置外设;

(3)建立UCF文件;

(4)bit流的生成[4]。自定义IP的部分主要实现电机的正转,反转和停止控制。关键VerilogHDL代码如下:

case(state)

//电机停止

′NOP:{pwm_left,pwm_right}<={7′d0,7′d0};

′GOING://电机正向旋转

begin

if(dis_value>31)

{pwm_left,pwm_right,dir_lself,dir_rself}

<={7′d100,7′d100,1′d0,1′d0};

else

{pwm_left,pwm_right,dir_lself,dir_rself}<=

{{dis_value[4:0],2′b0},{dis_value[4:0],2′b0},1′d1,1′d1};

end

′RETURN://电机反向旋转

begin

if(dir_value==3′b010)

{pwm_left,pwm_right,dir_lself,dir_rself}<={7′d80,7′d80,1′d1,1′d0};

else

{pwm_left,pwm_right,dir_lself,dir_rself}<={7′d80,7′d80,1′b0,1′b1};

end

endcase

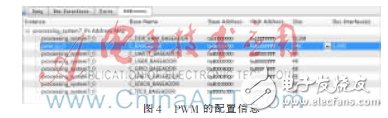

在本设计中,对电机的控制,传输的数据量较小,只需要添加一个低速的AXI4-Lite总线设备PWM模块来控制PMOD接口就可以实现硬件设备之间通信,其中AXI4-Lite的全局时ACLK设置为100 MHz,PWM模块分配的起始物理地址为0x6CA00000,空间大小为64 KB,PWM配置信息如图4所示。

2.3 Linux下电机驱动部分的设计

由于远端传输是在Linux系统下TCP/IP协议实现的,因此,编写Linux下的IP驱动,应用程序就可以通过Linux的标准接口访问FPGA的PMOD接口设备。本设计编写的是字符型设备驱动程序,包含设备加载、设备卸载以及文件操作函数。PWM模块加载时系统调用module_init(pwm_init)宏实现模块的初始化操作,在本系统中pwm_init()函数主要完成以下工作:(1)内核注册字符型设备驱动;(2)创建PWM设备类;(3)利用PWM设备类创建设备;(4)将PWM模块物理地址映射到虚拟地址上[5]。部分关键代码如下所示:

//XPS分配的物理地址

#define PWM_MOUDLE_PHY_ADDR 0x6CA00000

//注册驱动

pwm_driver_major=register_chrdev(0,DEVICE_NAME,&pwm_driver_fops);

pwm_driver_class=class_create(THIS_MODULE,"

pwm_driver");//创建设备类

pwm_driver_device=device_create(pwm_driver_class,NULL,MKDEV(pwm_driver_major,0),NULL,"pwm_device");

//利用设备类创建设备

//将PWM IP物理地址映射为虚拟地址

pwm_fre_addr=(unsignedlong)ioremap(PWM_MOUDLE_ PHY_ADDR,sizeof(u32));

初始化工作结束,但是仅有初始化函数,设备仍然无法工作,还需要有实现频率和占空比的调节机制。控制PWM的频率函数如下所示:

static ssize_t sys_pwm_frequency_set(struct device*dev, struct device_attribute*attr,const char*buf,size_t count)

{

long value=0;

int i;

frequency=0;

//修改频率之前,关闭PWM模块

outl(value,pwm_fre_addr);

//将写入pwm_frequency中的字符串转化为整数

for(i=0;i100000000)value=100000000;

value=100000000/frequency;

//将计数值写入到PWM模块的pwm_fre_addr寄存器中

outl(value,pwm_fre_addr);

return count;

}

控制PWM占空比的函数和控制PWM频率的函数一样。

3 实验结果及测试

系统的主控制板为Zedboard开发板,上电启动后,无线路由器会发布一个SSID为Tp_Link_5C90的无线网络,可以通过任何可以上网的设备连接这个网络。在浏览器中输入网址:192.168.1.100,就会登录到移动视频监控的网页上,通过界面的按钮控制视频终端的运行。

本文设计采用Xilinx All Programmable芯片Zynq作为主控CPU,FPGA部分可以实现逻辑扩展和功能补充。例如:自定义通信协议、IP核,同时还可以利用Xilinx的部分可重配置技术升级硬件系统,易于后期扩展和硬件升级;ARM部分采用的是性能较高的Cortex-A9双核,使得对高清晰视频的处理较为流畅,而且系统整体功能也比较稳定。相比于传统的模拟监控,数字视频处理技术提高了图像的质量和监控效率。

设计中采用软硬件协同设计的方法,即:在整个系统及定义的基础上,同时对软硬件进行设计和协调,其中包括软硬件的划分(哪些功能使用软件完成,哪些功能使用硬件完成)、软硬件系统的开发与联合调试,降低了开发风险,缩短了开发周期。

参考文献

[1] Xilinx Inc. UG585, Zynq-7000 All Programmable SoC Technical Reference Mannual[Z]. 2013.

[2] Xilinx Inc. UG873, Zynq-7000 All Programmable SoC: Concepts, Tools and Techniques[Z]. 2013:12-35,40-53.

[3] 王芳芳,张欢.基于Zynq平台的动态智能家居系统的设计[J].软件,2013,34(8):98-100.

[4] 胡典荣,郭春生.基于ZedBoard的SPI和以太网传输设计[J].杭州电子科技大学学报,2013,33(5):126-129.

[5] 陆佳华,江舟,马岷.嵌入式系统软硬件协同设计指南:基于Xilinx Zynq[M].北京:机械工业出版社,2013.

电子发烧友App

电子发烧友App

评论