三星内部认为当前NAND Flash供应价格过低,计划从今年四季度开始调涨NAND Flash产品的合约价格,涨幅预计在10%以上。

2023-10-10 17:15:37 554

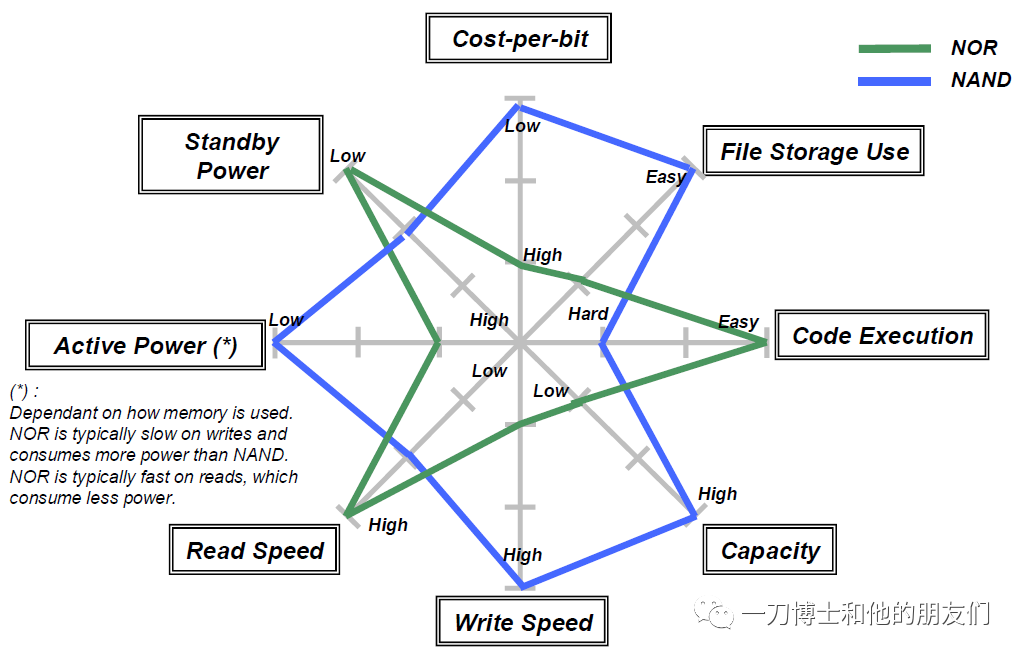

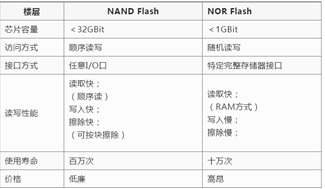

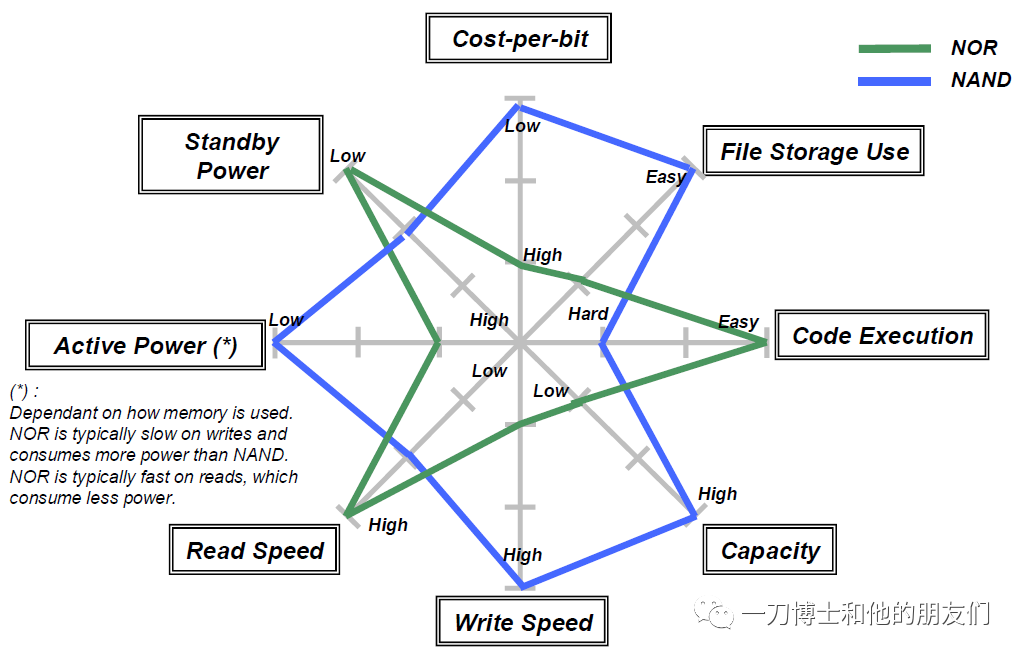

554 目前,NOR FLASH和NAND FLASH是市场上主要的非易失性闪存技术,但是据我了解,还是有很多工程师分不清NAND FLASH与NOR FLASH。

2023-10-01 14:05:00 58

58

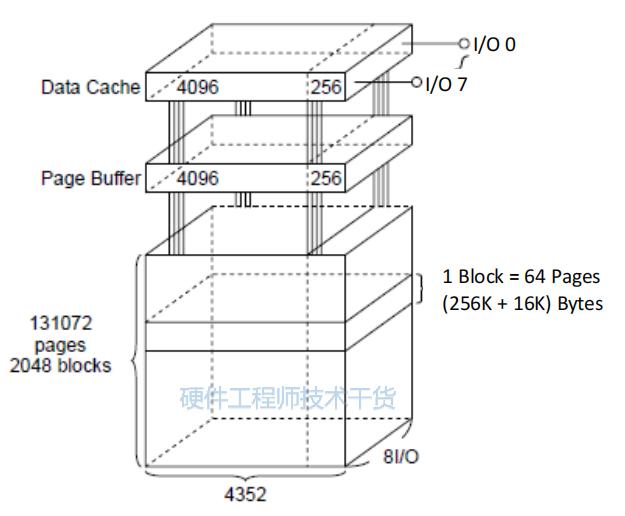

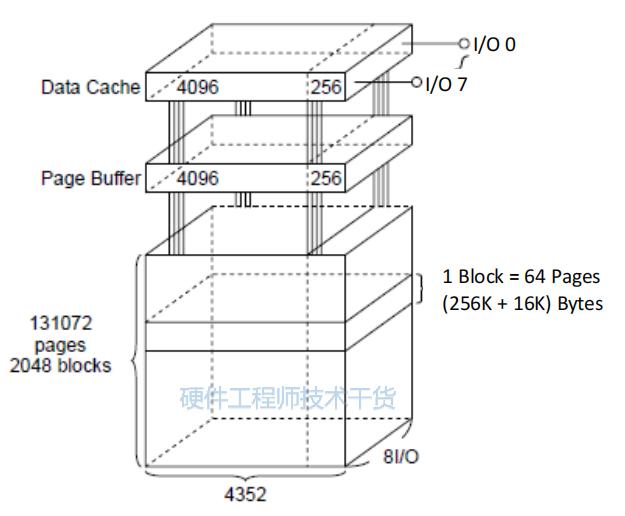

在上一篇文章中为大家介绍了NAND Flash的工作原理和自身的特性(点击查看 ),本次文章将继续为大家带来关于NAND Flash的内容。 一、NAND Flash 的容量结构 从访问NAND

2023-09-22 18:10:02 270

270

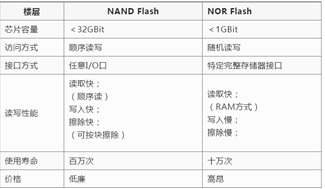

NAND Flash 和NOR Flash 的差别在哪儿呢?从字面意思上看, NAND = not AND(与非),NOR = not OR(或非),也有可能是NMOS AND/OR。同为非挥发

2023-09-11 16:59:23 343

343

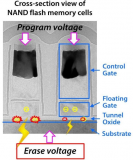

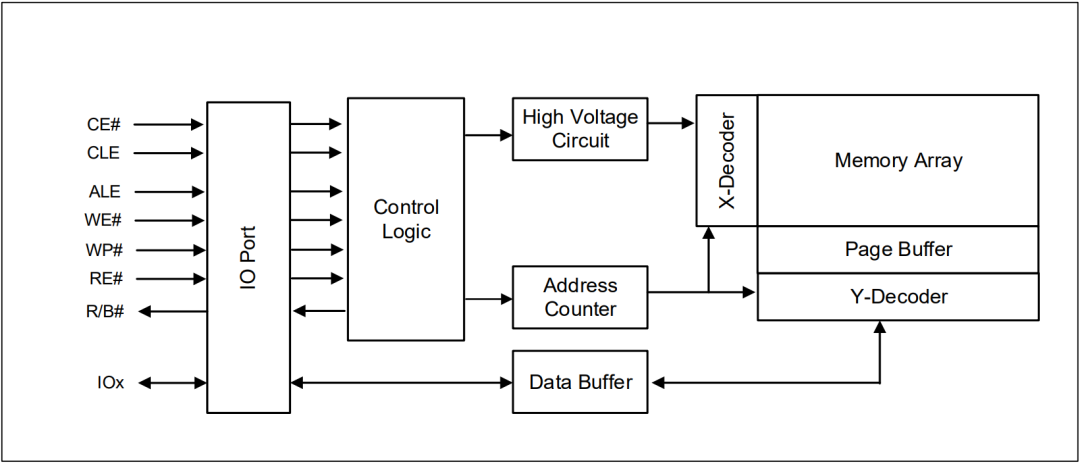

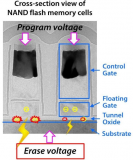

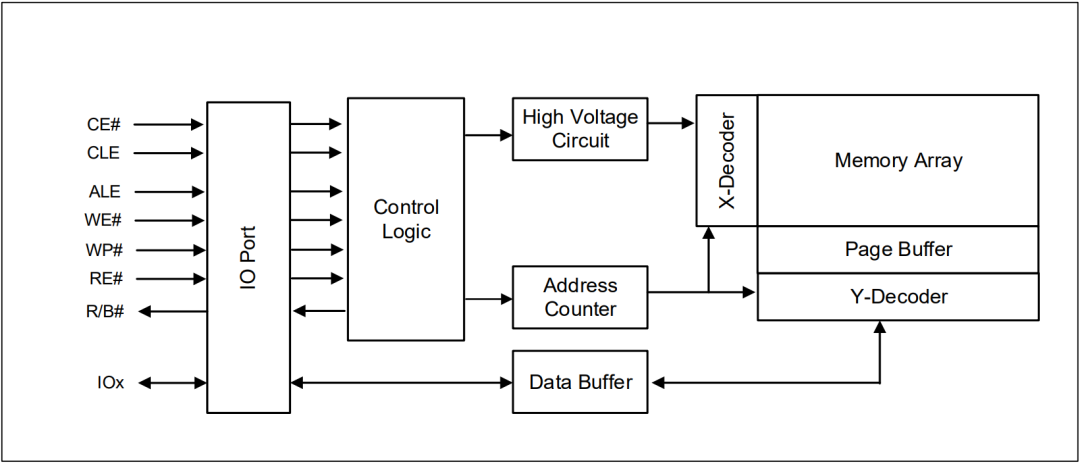

NAND Flash是一种非易失存储器,也就是掉电不丢失类型,现在我们常见的存储设备基本都是NAND Flash,比如U盘、固态硬盘,手机存储等等,电脑传统硬盘除外。

2023-09-11 14:48:23 200

200

Nand Flash存储器是Flash存储器的一种,其内部采用非线性宏单元模式,为固态大容量内存的实现提供了高性价比、高性能的解决方案。Nand Flash存储器具有容量较大、改写速度快等优点

2023-09-05 18:10:01 333

333 ;但是由于该MCU没有USB接口,为了缩短数据上传的时间,计划加一个 nand flash 控制器(通常控制器都带USB接口),专门用来读取nand flash 中的数据,写flash 不要求高速。这样

2013-09-24 14:09:37

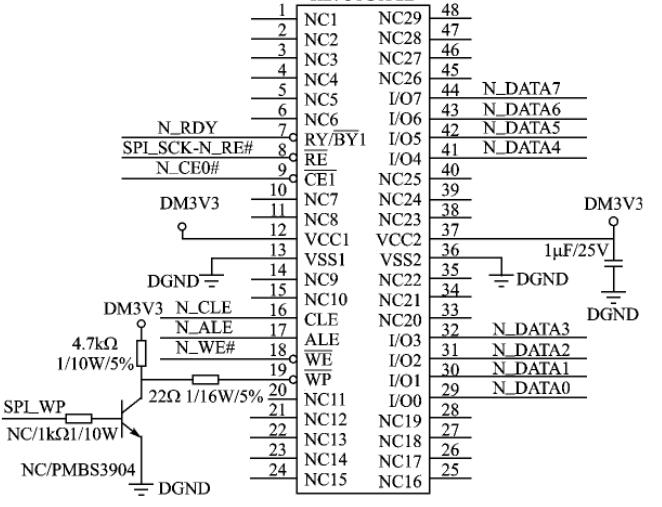

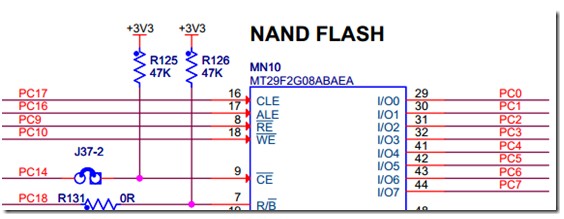

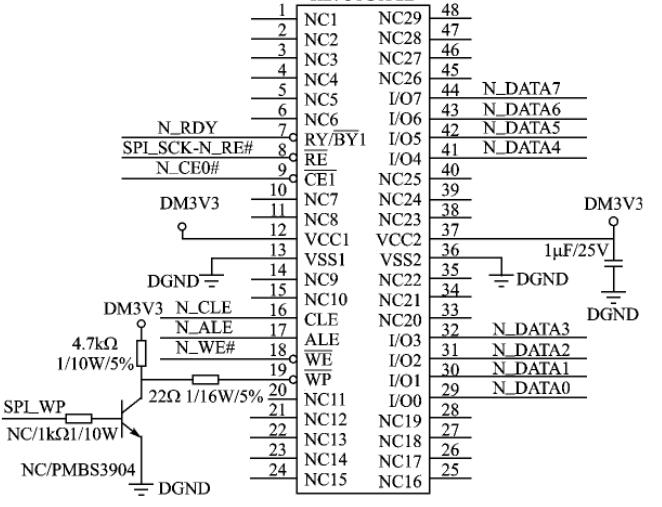

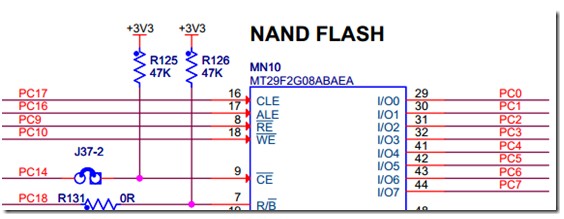

引言:并行Nand Flash是中等容量存储方案的理想选择,相比于SPI Nand Flash,性能更优,但体积较大,使用并没有后者广泛,多使用在嵌入式,物联网,工业等领域。

2023-08-11 15:50:13 330

330

非易失性存储元件有很多种,如EPROM、EEPROM、NOR FLASH和NAND FLASH,前两者已经基本被淘汰了,因此我仅关注后两者

2023-06-29 09:06:05 1071

1071

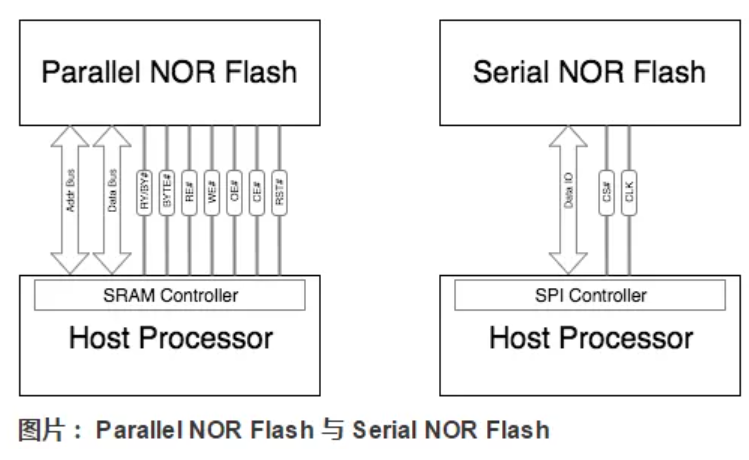

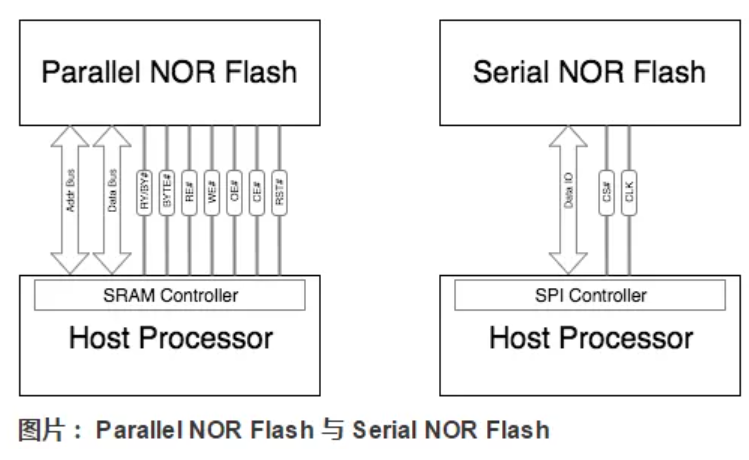

在嵌入式系统领域,作为存储设备的NOR Flash和NAND Flash,大家应该不陌生。早期NOR Flash的接口是并行口的形式,也就是把数据线,地址线并排设置在IC的管脚中。但是由于不同容量

2023-03-06 09:49:17 3901

3901 从SD卡、手机、平板等消费级产品到数据中心企业级场景,NAND Flash凭借其高性能、大容量、低功耗以及低成本等特性大受欢迎,是目前应用最为广泛的半导体非易失存储介质。为了满足业务场景越来越严苛的性能要求,人们想了许多方法来提升基于NAND Flash的系统性能,具体可分为以下几类。

2023-01-14 11:22:20 2172

2172 FLASH芯片分为Nor Flash和Nand Flash,Nor Flash容量小有独立的地址线,用于存储较小的程序代码如引导代码和程序参数,NAND FLASH容量大地址总线共用一组引线,Nand Flash用来安装操作系统存放应用程序及用户数据 像IOS,Linux Andriod

2022-02-10 10:11:45 31

31 在设计使用NAND FLASH的系统时选择适当的特性平衡非常重要。闪存控制器还必须足够灵活以进行适当的权衡。选择正确的闪存控制器对于确保...

2022-01-25 20:00:55 2

2 Flash Memory是一种非易失性的存储器。在嵌入式系统中通常用于存放系统、应用和数据等。在PC系统中,则主要用在固态硬盘以及主板BIOS中。绝大部分的U盘、SDCard等移动存储设备也都是

2022-01-25 17:25:12 58275

58275

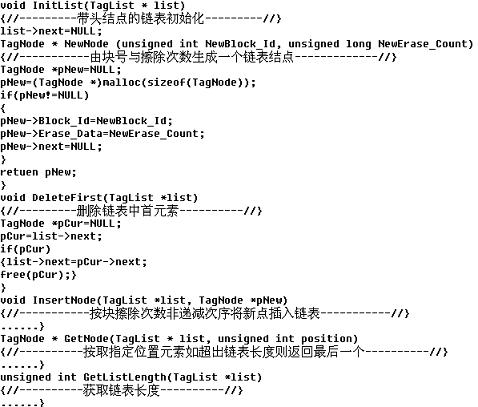

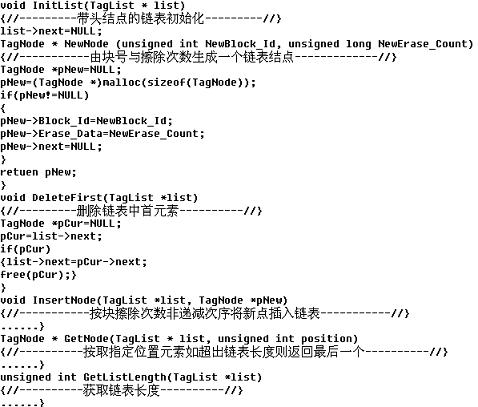

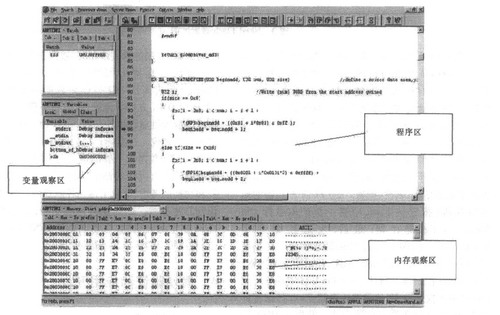

本文章主要讲解了nand_flash初始化的方法,如何读取nand_flash上的数据

2021-12-22 19:04:46 15

15 1、NOR flashNOR flash数据线和地址线分开,可以实现ram一样的随机寻址功能,可以读取任何一个字节。但是擦除仍要按块来擦。2、NAND flashNAND flash数据线和地址线

2021-12-02 12:21:06 28

28 1.SPI Nand Flash简介SPI Nand Flash顾名思义就是串行接口的Nand Flash,它和普通并行的Nand Flash相似,比如:SLC Nand Flash。2.SPI

2021-12-02 10:51:17 33

33 flash本身功率有关。如nand、nor flash。nand flash中的存储颗粒也有技术差异,如slc、mlc。这些东西是内部封装起来的用于存储的内核,对外编程的接口还需要一个外部控制器。我们买到的flash芯片,其实是内部的flash存储颗粒+外部封装的控制器来构成的。即,对外是外部控制器,对内是

2021-12-01 19:51:17 21

21 Flash在我们生活中无处不在,比如:U盘、固态硬盘、SD卡、内存卡等。 同时,在单片机开发过程中也会遇到各种各样的Flash,比如:SPI Flash、Nor Flash、 Nand Falsh等

2021-10-09 15:01:55 4507

4507 BCH编解码器在NAND Flash主控中的研究与优化实现(嵌入式开发培训哪家好)-该文档为BCH编解码器在NAND Flash主控中的研究与优化实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-08-04 10:43:36 18

18 Nand Flash文件系统解决方案(嵌入式开发一般考什么证书)-ST提供适用于SLC的NFTL(NAND Flash Translation Layer)和FAT类文件系统来解决NAND Flash存储的问题。

2021-07-30 10:41:29 9

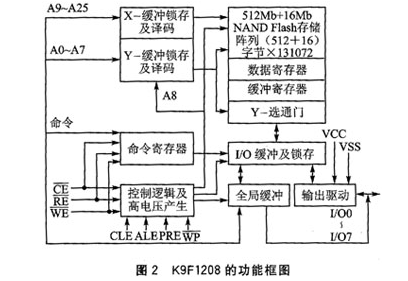

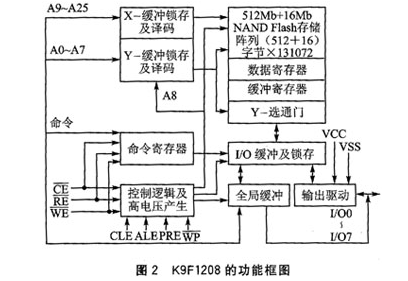

9 以Samsung NAND Flash器件K9F1208为例,对比NAND Flash和NOR Flash的异同;介绍大容量NAND Flash在uPSD3234A增强型单片机系统中的应

2021-06-03 18:01:48 2864

2864

移动电话的功能日益丰富,其对系统中数据存储容量的需求正在快速增长。 NAND Flash具有速度快、密度大、成本低等特点,在各种数码产品中得到了广泛 应用,在各种片上系统芯片中(SOC)集成NAND

2021-03-29 10:07:08 19

19 阐述在BCH编解码器在NAND Flash主控中的研究与优化。

2021-03-17 13:50:50 24

24 ,随着5G相关应用等的大举发力,5G基站中NOR FLASH占尽优势,而相关配套产品和生态产品中,NAND FLASH又频繁

2020-11-28 11:38:27 2880

2880

Nand flash是flash存储器的其中一种,Nand flash其内部采用非线性宏单元模式以及为固态大容量内存的实现提供了廉价有效的解决方案。NAND FLASH存储器具有容量较大和改写速度快

2020-11-03 16:12:08 3601

3601

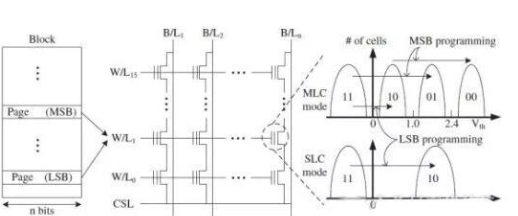

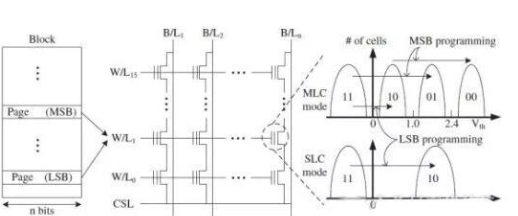

NAND闪存结构NAND Flash的内部组织是由块和页构成。每个块包含多个页

2020-07-22 11:56:26 5003

5003

三星在该工厂主要量产用于智能手机,PC,服务器等领域作为数据处理设备使用的 Nand Flash 记忆芯片。值得注意的是,通过垂直结构堆叠电路提高储存容量的 3D Nand Flash 芯片便在此生产。

2020-03-20 16:03:57 477

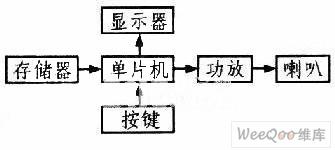

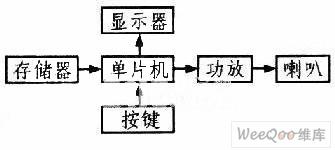

477 目前在技术上,声音的存储大都使用大容量的NAND Flash,但一般按照文件系统的方式存储,这对学生有一定的难度。本声音播放器的声音文件采用非文件方式存储在NAND Flash中,这样在不需要太多

2018-12-31 11:29:00 2719

2719

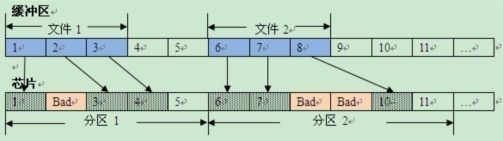

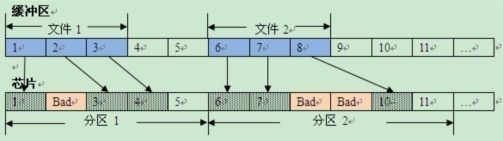

NAND Flash的容量较大。整片Flash分为若干个块(Block),每个Block分为若干个页(Page)。在每个页中,除了数据区域,也包含若干“多余”的区域,用来进行ECC等操作。在进行擦除操作是,基本单位是“块”;而编程的基本单位是“页”。

2018-12-11 15:47:20 13350

13350

坏块是出厂就有的,还是后来使用产生的,这个表叫做 坏块表(BBT,Bad Block Table)。在Linux内核MTD架构下的Nand Flash驱动,和Uboot中Nand Flash驱动中,在

2018-06-05 15:11:27 1669

1669 受NAND Flash的挤压,NOR Flash的市场占有率非常的低,但后续缺口却一直没有补上,因此NOR Flash供需变得极度的紧张,缺货状况恐怕到明年上半年都不会缓解。中芯长电采购NOR Flash测试设备,能缓解存储器缺货现状?

2017-12-14 16:34:17 1167

1167 Hynix NAND flash型号指南

2017-10-24 14:09:29 25

25 中得到广泛的应用。NAND Flash相对于NOR Flash具有更小的体积、更快的写入速度、更多次的可擦除次数以及更低廉的价格而得到了迅速发展。大容量的NAND Flash特别适合现在数码设备中大

2017-10-19 11:32:52 7

7 Nand Flash存储器是Flash存储器的一种,为固态大容量内存的实现提供了廉价有效的解决方案。NAND存储器具有容量较大,改写速度快等优点,适用于大量数据的存储,如嵌入式产品中包括数码相机、记忆卡、体积小巧的U盘等。

2017-10-10 10:54:11 23778

23778

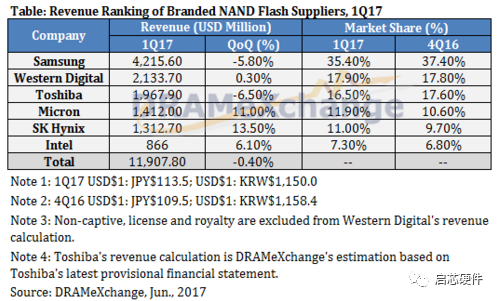

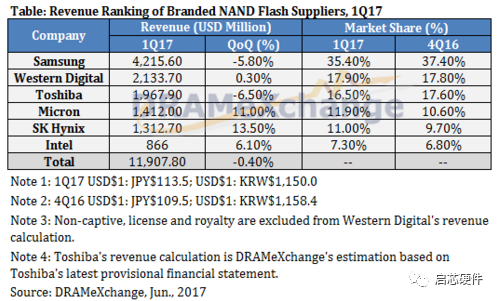

市调机构集邦科技预期,今年储存型快闪存储器(NAND Flash)整年都将维持供应吃紧的情况,NAND Flash厂商业绩可望逐季攀高。

2017-03-08 10:11:39 519

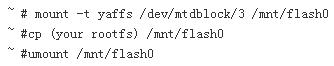

519 创龙固化Linux系统到NAND FLASH步骤。

2016-11-14 17:33:11 2

2 Allwinner Technology Nand Flash Support List—全志科技NAND Flash支持列表。

2016-09-26 16:31:14 2

2 NAND_Flash结构与驱动分析NAND_Flash结构与驱动分析NAND_Flash结构与驱动分析

2016-03-17 14:14:01 37

37 本文提出了 一种 NAND Flash 在 WINCE. net 系统中的应用方案设计。首先介绍了 NAND Flash 原理及与 NO R Flash的区别 接着介绍了 系统硬件设计方案

2016-03-14 16:01:23 2

2 研究机构TrendForce表示,随着清华紫光投资NAND Flash储存相关公司的脚步加快,以及中国半导体业者在NAND Flash产业链的布局日趋完整,中国业者在NAND Flash产业地位也越来越关键。

2015-11-11 09:03:54 405

405 NAND Flash存储器在移动设备应用市场的需求趋缓。根据IHS初步统计资料显示,受到品牌厂与网络厂商大举推出云端储存服务影响,第三季智能手机与平板设备内建NAND Flash存储器的需求已开始减少。

2013-11-26 11:16:17 1141

1141

NAND Flash需求主要集中在智慧型手机、云端储存大型资料库用的固态硬碟(SSD)上。2013年智慧型手机、平板电脑对于NAND Flash晶片用量倍数增加,加上云端运算商机,市场对第3季NAND Flash市场看法偏向吃紧,晶片价格维持高档。

2013-07-05 10:13:44 2960

2960 2012-07-07 00:14:45 15

15 基于NAND Flash的存储系统的设计首先要解决坏块问题。由于NAND Flash自身存在固有坏块并在擦除和编程中又随机产生坏块,因此为了提高设备的可靠性应该将这两种操作分散在闪存不同的块

2011-04-25 11:10:10 1293

1293

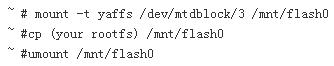

目前,针对NOR Flash设计的文件系统JFFS/JFFS2在嵌入式系统中已得到广泛的应用;随着NAND作为大容量存储介质的普及,基于NAND闪存的文件系统YAFFS(Yet Another Flash File System)正逐渐被

2010-09-01 10:10:03 993

993

Nand+Flash存储管理在DSP系统中的实现

Nand Flash作为一种安全、快速的存储体,因其具有体积小、容量大、成本低、掉电数 据不丢失等一系列优点,已

2010-04-12 13:42:17 1091

1091

一种在片上系统中实现Nand Flash控制器的方法

摘要:Nand Flash以其优越的特性和更高的性价比,在现代数码产品中得到了广泛的应用。在片上系统芯片中集成Na

2010-01-12 10:15:28 798

798

Nand Flash 因其体积小、容量大、成本低、掉电数据不丢失等一系列优点已经在嵌入式系统中得以广泛应用,然而,由于Flash 读写存储的编程特点以及其生产工艺与使用过程中坏块

2009-12-23 15:59:09 14

14 本文实现了大容量 NAND FLASH 在MSP430 嵌入式系统中的应用,阐述了NANDFLASH 的使用方法,重点介绍了硬件电路设计和软件设计,满足了系统微体积、低功耗的要求。

2009-09-14 16:42:24 21

21 由于Nand Flash 写之前需要擦除且使用寿命有限,为了提高Nand Flash 的使用寿命,需要对Nand Flash 存储块进行均衡管理。本文研究了ZLG/FFS,针对其不足,并根据ZLG/FFS设计了一个新的FF

2009-08-11 08:10:24 17

17 NAND Flash以其大容量、低价格等优势迅速成为嵌入式系统存储的新宠,因此其上的文件系统研究也日益广泛。本文简要介绍了常用的NAND Flash文件系统YAFFS,并针对YAFFS在均匀损耗和

2009-03-29 15:15:11 1227

1227

NAND Flash的驱动程序设计方案

以三星公司K9F2808UOB为例,设计了NAND Flash与S3C2410的接口电路,介绍了NAND Flash在ARM嵌入式系统中的设计与实

2009-03-29 15:07:30 1462

1462

NAND Flash SLC MLC技术分析什么是SLC?

SLC英文全称(Single Level Cell——SLC)即单层式储存 。主要由三星、海力士、美光、东芝等使用。

S

2008-07-17 10:07:27 1364

1364

正在加载...

电子发烧友App

电子发烧友App

评论