LED(Light-emitting diode)由于寿命长、能耗低等优点被广泛地应用于指示、显示等领域。可靠性、稳定性及高出光率是LED取代现有照明光源必须考虑的因素。封装工艺是影响LED功能作用的主要因素之一,封装工艺关键工序有装架、压焊、封装。由于封装工艺本身的原因,导致LED封装过程中存在诸多缺陷(如重复焊接、芯片电极氧化等),统计数据显示[1-2]:焊接系统的失效占整个半导体失效模式的比例是25%~30%,在国内[3],由于受到设备和产量的双重限制,多数生产厂家采用人工焊接的方法,焊接系统不合格占不合格总数的40%以上。从使用角度分析,LED封装过程中产生的缺陷,虽然使用初期并不影响其光电性能,但在以后的使用过程中会逐渐暴露出来并导致器件失效。在LED的某些应用领域,如高精密航天器材,其潜在的缺陷比那些立即出现致命性失效的缺陷危害更大。因此,如何在封装过程中实现对LED芯片的检测、阻断存在缺陷的LED进入后序封装工序,从而降低生产成本、提高产品的质量、避免使用存在缺陷的LED造成重大损失就成为LED封装行业急需解决的难题。

目前,LED产业的检测技术主要集中于封装前晶片级的检测[4-5]及封装完成后的成品级检测[6-7],而国内针对封装过程中LED的检测技术尚不成熟。本文在LED芯片非接触检测方法的基础上[8-9],在LED引脚式封装过程中,利用p-n结光生伏特效应,分析了封装缺陷对光照射LED芯片在引线支架中产生的回路光电流的影响,采用电磁感应定律测量该回路光电流,实现LED封装过程中芯片质量及封装缺陷的检测。

1理论分析

1.1 p-n结的光生伏特效应[m]根据p-n结光生伏特效应,光生电流IL表示为:

式中,A为p-n结面积,q是电子电量,Ln、Lp分别为电子和空穴的扩散长度,J表示以光子数计算的平均光强,α为p-n结材料的吸收系数,β是量子产额,即每吸收一个光子产生的电子一空穴对数。

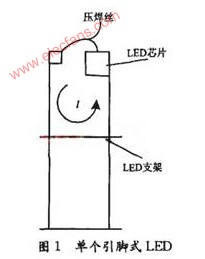

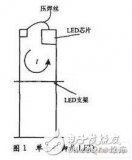

在LED引脚式封装过程中,每个LED芯片是被固定在引线支架上的,LED芯片通过压焊金丝(铝丝)与引线支架形成了闭合回路,如图1。若忽略引线支架电阻,LED支架回路光电流等于芯片光生电流IL。可见,当p-n结材料和掺杂浓度一定时,支架回路光电流与光照强度I成正比。

1.2封装缺陷机理

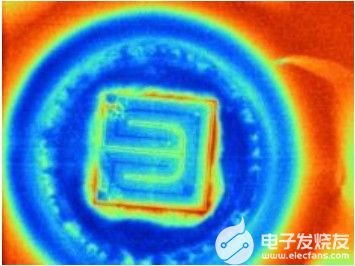

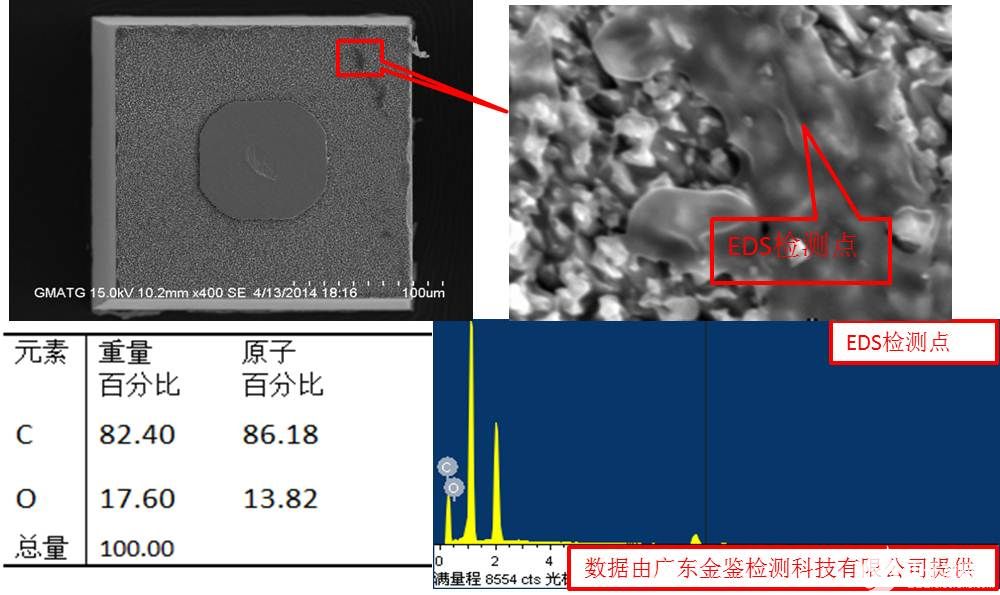

LED芯片受到腐蚀因素影响或沾染油污时,在芯片电极表面生成一层非金属膜,产生封装缺陷[11]。电极表面存在非金属膜层的LED芯片压焊工序后,焊接处形成金属一介质-金属结构,也称为隧道结。当一定强度的光照射在LED芯片上,若LED芯片失效,支架回路无光电流流过若非金属膜层足够厚,只有极少数电子可以隧穿膜层势垒,LED支架回路也无光电流流过;若非金属膜层较薄,由于LED芯片光生电流在隧道结两侧形成电场,电子主要以场致发射的方式隧穿膜层,流过单位面积膜层的电流可表示为[12]。

其中q为电子电量,m为电子质量,矗为普朗克常数,vx、vy、vz分别是电子在x、y、z方向的隧穿速度,T(x)为电子的隧穿概率。又任意势垒的电子隧穿概率可表示为[13]

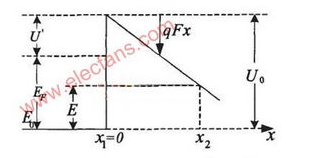

其中jin、jout。分别是进入膜层和穿过膜层的电流密度,x指向为芯片电极表面到压焊点,为膜层中z方向任意点的势垒,E是垂直芯片电极表面速度为vx电子的能量。

图2为在电场f’作用‘F芯片电极表面的势垒图,其中EF为费米能级,U为电子发射势垒。由图2,若芯片电极表面为突变结,其值为U0,光生电流在隧道结两侧形成的电场强度为F,电极表面以外的势垒为U0- qFx。取芯片电极导带底为参考能级E0(x=0),因而有x<0处,U(x)=0;x>0处,U(x)=U0- qFx,根据条件U(x)=E=U0- qFx2式中d为膜层厚度,V为膜层隧道结两侧电压。当LED芯片发生光生伏特效应时,由式(7)可知,流过芯片电极表面非金属膜层的电流受到膜层厚度的影响,随着膜层增厚,流过膜层的电流减小,流过LED支架回路的光电流也将减小。

综上所述,引脚式LED支架回路光电流的有无或大小可以反映封装工艺中LED芯片的功能状态及芯片电极与引线支架的电气连接情况,因此,可以通过检测LED支架回路光电流达到检测引脚式封装工艺中芯片功能状态和封装缺陷。

1.3封装缺陷的检测方法

完成压焊工序后,LED处于闭合短路状态,直接导出回路电流进行检测不可行。虽然支架回路有一定电阻,但光生电流只有微安量级,因而支架回路中的压降非常小,用一般的电压测量方法难度较大,而且接触式检测会引入接触电阻,影响检测的准确性。因此,考虑用非接触式的电流检测方法。根据法拉第电磁感应定律,利用引脚式LED自身特征,检测时将带磁芯线圈中磁芯的一端插入图1所示闭合回路z中,LED支架回路作为一级绕组,带磁芯线圈作为次级绕组,并在线圈的两端并联上电容C,与线圈L组成LC谐振回路。以交变的光激励LED芯片时,支架回路中产生交变电流,交流载流回路会在周围空间产生交变磁场,次级线圈交变磁场则在次级线圈中产生感生电动势。若交变光频率与LC谐振回路频率相等时,LC回路发生共振,此时次级线圈两端感生电动势最大。因此,可以通过检测次级线圈两端感生电动势间接达到检测支架回路光电流的目的,实现对封装工艺中芯片功能状况及焊接质量的检测。

LC谐振回路中,线圈中磁芯起到增强磁感应强度B的作用,从而增加检测信号幅值。又线圈中磁芯的有效磁导率与相对磁导率间关系可表示为[14]:

式中,μe磁芯的有效磁导率,胁为磁芯的相对磁导率,μr为磁芯的有效磁路长度,名为非闭合气隙长度。

由式(8)可以看出,影响有效磁导率胁从而影响磁感应强度B的参数有:

①磁芯材料的相对磁导率胁。与所选软磁磁芯材料有关(软磁材料初始相对磁导率一般大于1000),当磁芯材料选定后,其相对磁导率为确定值。

②磁芯的有效长度le、非闭合气隙长度lg,它们由磁芯的结构决定。微弱电流产生的磁场易受外界因素干扰,磁路越长,干扰越大,所以磁芯的有效长度宜短。

在磁芯材料确定的情况下,为了得到较大磁感应强度B,需改变线圈中磁芯的结构。若磁芯结构设计为环形,由式(8)知,磁感应强度B增大倍数理论上与磁芯的相对磁导率卢,大小相等,检测信号幅值将达到最大。与条形磁芯同种材质的u型磁芯上搭接一块条形磁芯就构成环形磁芯线圈,其搭接方式有两种,如图3示。

检测时将绕有线圈的U型磁芯的一端插入图1所示1闭合回路,感应LED支架回路中回路电流产生的交变磁通,再将条形磁芯搭接在U型磁芯上,使感应磁路闭合。由于搭接方式不同,两种搭接方式的磁芯线圈处在支架回路所产生的交变磁场中时,其搭接处磁路也将不同,用Ansoft MaxwELl软件仿真两种搭接方式的磁芯搭接处在交变磁场中的磁回路,结果如图4示

图4中(a)、(b)仿真结果对应于图3中(a)、(b)两种线圈磁芯搭接方式。比较两种线圈磁芯搭接处磁路仿真结果可以看出:①图3(a)示磁芯搭接处磁路在空气介质中的回路最短,所受磁阻最小,因此磁损耗也最小。②由于待测LED支架回路电流为微安量级,激起的磁场较小,易受空间电磁场的干扰,图3(b)示磁芯搭接处磁路暴露在空气介质中较多,受干扰的几率较大。由上述分析,图3(a)磁芯搭接方式较优,可以增强信号检测端抑制干扰能力,增加检测信号幅值,一定程度上提高光激励检测信号信噪比,进而提高缺陷检测精度。

2实验及分析

2.1实验

为了比较条形磁芯线圈与环形磁芯线圈对封装缺陷检测精度的影响,现分别使用条形磁芯线圈和图3(a)示环形磁芯线圈进行实验。磁芯材料为PC40,其初始相对磁导率约为2300,条形磁芯的外形几何尺寸为1.6minx3.2ram×20mm,线圈匝数为300匝;环形磁芯横截面尺寸为1.6mm×3.2mm,其有效磁路长度约等于条形磁芯,线圈匝数为300匝。实验中激励光源为一种超高亮度贴片式白光LED,激励光源用占空比为50%的方波信号驱动,方波信号可由一系列正弦变化的信号叠加而成,使其基频与谐振回路的工作频率相同,即LC谐振回路实现了对方波信号的选频,所以穿过线圈磁通链的变化率就是方波基频信号的变化率;检测对象分别是GaP材料12mil黄色焊接质量合格的LED和焊接过程中芯片电极有非金属膜的LED。从线圈两端输出的信号经放大、滤波、峰值检波后见图5。实验中放大器的放大倍数为103倍。

2.2结果分析

本文介绍的LED芯片封装缺陷检测方法是通过检测LED支架回路光电流间接实现的。由图5可以看出,支架回路光电流激发的磁场在不同磁芯结构线圈两端感生电动势大小不同;不同磁芯结构线圈,检测信号的信噪比差异较大。具体表现为:

①焊接质量合格的LED,实验检测值与理论计算值相吻合。图5(a)为使用条形线圈磁芯的实验结果,封装工艺中焊接质量合格的LED,信号检测端产生的光激励信号经放大、滤波、峰值检波后幅值约为60mV。选12mil黄色LED芯片进行理论值计算,芯片面积A=0.3mm×0.3mm,取β=0.5当单位时间内单位面积被半导体材料吸收的平均光强(以光子数计)为5.45×1021个/m2s时,由式(1)可计算出光生电流约为42μA。由毕奥-萨伐尔定理、叠加定理及法拉第电磁感应定律,可求得12mil黄色LED芯片在信号检测端感生电动势幅值约为63mV,去除实验误差和计算误差,理论值和实验值较好地吻合。

②对于环形结构磁芯线圈,实验值较理论值小。根据式(8),对于条形结构磁芯线圈,假设磁芯有效磁路长度le=100lg,此时有效磁导率μe≈100。若磁芯改为环形,则非闭合气隙长度lg≈0,此时有效磁导率μe≈μr=2300,由理论计算可知,12mil黄色焊接质量合格LED在信号检测端感生电动势幅值约为1.4V;由图5(b)知,实验得到信号值约为220mV,实验值远小于理论值。上述计算是在理想情况下进行的,在实际实验过程中,环形磁芯线圈是由U形磁芯和条形磁芯搭接而成的,搭接处气隙lg仍然存在,因而磁路不可能完全闭合,由式(8)知,气隙对有效磁导率影响很大,所以有效磁导率仍小于相对磁导率,因此,实验值远小于理论值。

③不同磁芯结构均可实现LED封装缺陷的检测,但检测信号的信噪比差异较大。由图5可以看出,虽然实验中磁芯线圈采用不同结构,对于焊接质量合格的LED,其光激励检测信号均明显大于封装过程中芯片电极表面存在非金属膜的LED光激励检测信号,通过比较两者检测信号幅值的大小,可将封装过程中芯片电极表面存在非金属膜的LED捡出。对图5(a),实验使用的线圈中磁芯为条形结构,存在气隙lg,磁感应强度B增强倍数为有效磁导率μe,同时检测信号易受外界干扰,因而检测信号幅值较小且存在较大的检测噪声,使得两种芯片光激励信号信噪比都较小,给后端信号处理带来难度,影响封装缺陷检测的精确度。将线圈中磁芯搭接成环形后构成闭合磁回路,磁感应强度B得到有效增强,磁损耗较小,受到空间电磁场的干扰相对也较小,所以检测信号信噪比得到显著改善。

④不同磁芯结构影响谐振回路的工作频率。实验过程中,LC谐振回路的电容C相等,环形磁芯的有效磁导率大于条形磁芯的有效磁导率,因而环形磁芯线圈的电感L大于条形磁芯线圈的电感,所以其谐振回路的谐振频率较小;从图5可以看出,条形磁芯线圈构成的谐振回路的谐振频率约为9.75kHz,而环形磁芯线圈构成的谐振回路的谐振频率约为7.33kHz。

⑤理论分析和实验结果分析可得,该方法对LED支架回路电流具有较高的检测精度,通过检测支架回路电流激起的磁场在线圈两端感生出电动势的大小,并与焊接质量合格的LED的检测信号进行比较,实现对封装过程中存在封装缺陷的LED进行检测。

3结论

针对引脚式LED芯片封装过程中存在的封装缺陷问题,基于p-n结的光生伏特效应,利用电子隧穿效应分析了一种封装缺陷对LED性能的影响。理论分析表明,当LED芯片电极表面存在非金属膜层时,流过LED支架回路的光电流小于光生电流,随着膜层厚度的增加,回路光电流逐渐减小,其检测信号减小。通过非接触法检测待测LED光激励信号并与焊接合格的LED光激励信号进行比较,实现对引脚式封装LED芯片在压焊工序中/后的功能状态及封装缺陷的检测。分析了影响检测精度的因素。用焊接合格与芯片电极表面存在非金属膜的12mil黄LED样品进行实验,结果表明,该方法可以检测LED支架回路微安量级光生电流信号,并具有较高的信噪比,检测结果能实现对焊接质量合格与芯片失效或存在封装缺陷的LED的区分,达到对LED芯片在压焊工序中/后的功能状态及封装缺陷检测的目的,从而降低LED生产成本、提高产品质量、避免使用存在缺陷的LED造成重大损失。

电子发烧友App

电子发烧友App

评论