了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应? 锁相环(PLL)是一种广泛应用于数字通信、计算机网络、无线传输等领域的重要电路。PLL主要用于时钟恢复、频率合成、时钟同步等领域

2023-10-23 10:10:20 44

44 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 99

99 数据库数据恢复-数据库文件被删除/分区被格式化的SQL SERVER数据恢复方案

2023-09-21 14:34:08 151

151 用FPGA的锁相环PLL给外围芯片提供时钟 FPGA锁相环PLL(Phase-Locked Loop)是一种广泛使用的时钟管理电路,可以对输入时钟信号进行精确控制和提高稳定性,以满足各种应用场景下

2023-09-02 15:12:34 351

351 德国GMC-I集团高美测仪可以提供全面的功率测试仪器方案,用户可以根据自己的特殊应用量身定制所需的测量仪器。这样高性价比的解决方案同样能很好地达到用户的要求,不需要去折衷接受低精度或者大材小用。

2023-09-01 17:24:52 166

166

电子发烧友网站提供《Brocade结构视觉技术在灾难恢复方面的优势.pdf》资料免费下载

2023-08-30 11:29:52 0

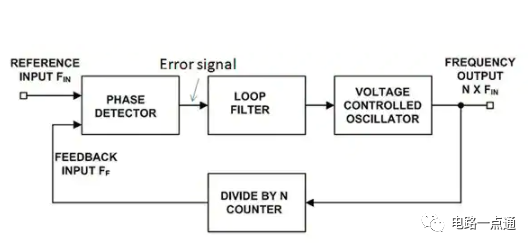

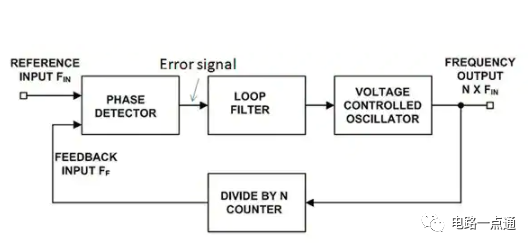

0 本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对PLL操作有基本的了解。

2023-07-10 10:22:24 425

425

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。因此,在包括无线电接收器和测试

2023-07-10 09:57:19 1262

1262

汽车电子测试测量解决方案 局域网测试解决方案动力系统测试解决方案数字分析解决方案数字RF测试解决方案 汽车设计提供的突破性解决方案.rar

2009-11-26 16:33:22

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 478

478

Linux误删除及误格式化的数据恢复方案针对的文件系统。

2022-11-23 11:34:23 1416

1416 【施工方案】送风机轴磨损在线修复方案

2022-10-18 15:44:34 0

0 电子发烧友网站提供《Compact系列CPLD时钟资源(Clock/PLL)用户指南 .pdf》资料免费下载

2022-09-26 10:03:33 1

1 外部晶振+内部时钟震荡器+内部PLL +内部分频器产生时钟,性能高一点的MCU基本都采用这种方案。

2022-08-31 18:04:08 682

682 石油钻井设备主轴磨损的修复方案

2022-06-17 15:01:20 0

0 干燥机轴承位在线快速修复方案

2022-05-25 17:02:15 3

3 机器人程序在运行过程中,可能会因为人为操作或报警的原因而发生程序中断。本文就机器人程序中断与相应的恢复方式进行简单介绍。

2022-03-21 10:11:03 3086

3086 SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52:25 5330

5330 的传输和接收至关重要。

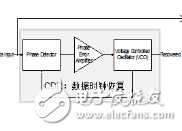

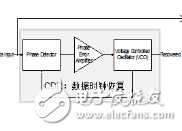

CDR电路原理

时钟恢复的目的是跟踪上发送端的时钟漂移和一部分抖动,以确保正确的数据采样。时钟恢复电路(CDR:Clock Data Recovery)一般都是通过PLL(...

2022-02-11 15:05:26 8

8 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

2022-02-09 10:43:43 6

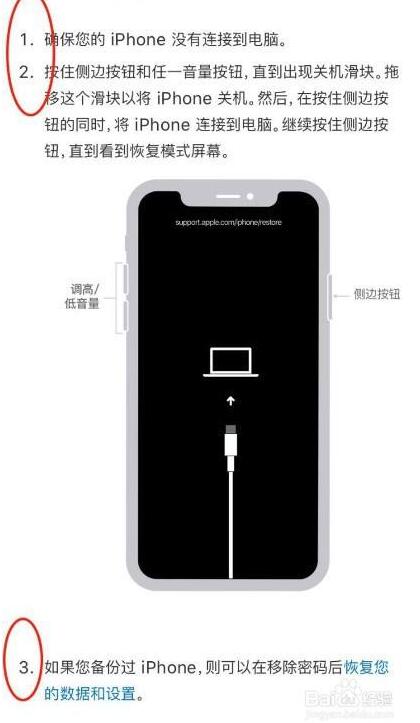

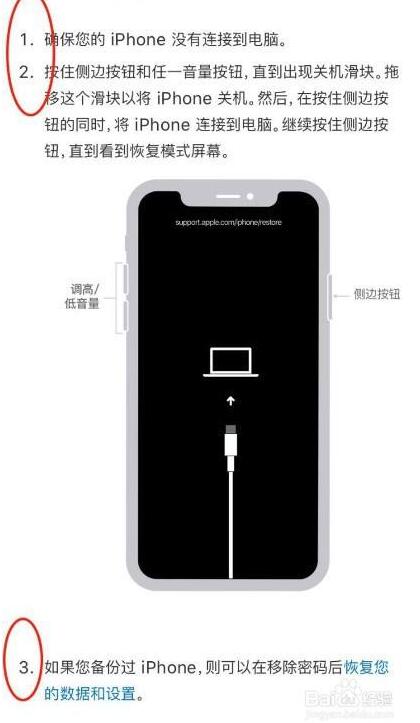

6 iphone已停用多久能恢复好?iphone已停用的恢复方法如下.

2021-09-18 09:40:59 38252

38252

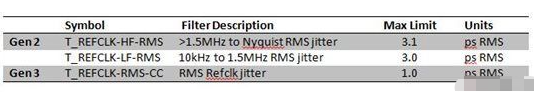

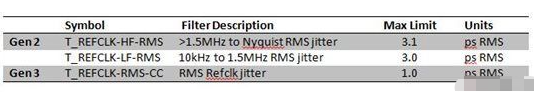

PCIe 参考时钟 (RefClk) 规范可针对 3 种不同架构定义,分别是:数据时钟、独立 RefClk 以及通用 RefClk。每个架构都具有特定的滤波器函数。在接收器时钟数据恢复输入端出

2021-06-28 16:49:48 1943

1943

PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 21

21 电子发烧友网为你提供时钟恢复方式的选择资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-05 08:40:15 18

18 AN-910: 在ADAV801和ADAV803上恢复DIR PLL运行

2021-03-21 08:33:25 5

5 Cyclone FPGA 具有锁相环(PLL)和全局时钟网络,提供完整的时钟管理方案。Cyclone PLL 具有时钟倍频和分频、相位偏移、可编程 占空比和外部时钟输出,进行系统级的时钟管理和偏移

2021-01-15 14:38:00 24

24 你会担心STM32时钟PLL各参数配错吗?

2020-03-01 13:35:13 2885

2885 苹果通讯录恢复方法

2019-08-26 16:38:36 3195

3195 本视频主要详细介绍了数据恢复方法有哪些,分别是硬盘数据恢复、硬盘物理故障、U盘数据恢复、Unix数据恢复。

2019-02-23 11:28:18 6747

6747 DCA/DCA-J主机描述83496A多速率电时钟恢复(CR)模块可凭借从50 Mb/s到13.5 Gb/s的连续无带调谐、超低剩余抖动和Golden PLL(锁相环)操作等特性为波形分析提取时钟。它提供

2018-09-25 11:43:14 143

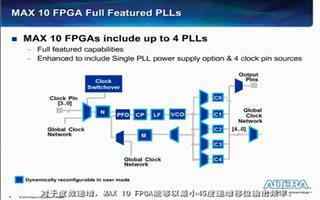

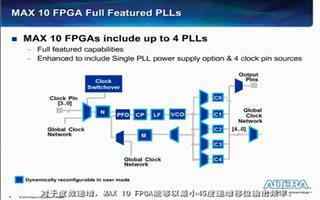

143 MAX 10 FPGA PLL和时钟培训,此次培训涉及到器件系列的时钟特性和选项。有20个全局时钟网络,全局CLK输入引脚数量也可以加倍,用作通用IO引脚。并且采用动态用户控制进行各种选择和电源控制,构建鲁棒的时钟网络源。它所有4个PLL都是全功能的。

2018-06-20 08:00:00 2107

2107

文中基于2.5 GB/s的高速型数据收发器模型,采用SMIC 0.18 um双半速率CMOS时钟进行数据的恢复处理。设计CMOS时钟主要包含:提供数据恢复所需等相位间隔参考时钟的1.25 GHz

2018-04-09 11:04:02 2

2 对大停电后机组和负荷的协调恢复的方案优化方法进行了研究。针对已有机组恢复的研究往往忽略了同一电厂不同机组对电网恢复过程贡献不同的不足,建立了考虑重要负荷恢复的机组分层协调恢复方案优化数学模型。将待

2018-03-20 17:04:55 0

0 当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17:00 5767

5767

本文档内容介绍了基于汽车雷达测试测量解决方案,供参考

2018-02-27 15:32:17 31

31 ;其次,结合多线程并发处理思想,提出并行实例恢复方法,对改进的实例恢复模型进行并发处理;最后,由于采用回滚段进行undo日志管理,可以实现undo日志的正常数据化管理,提前结束实例恢复。通过进行TPC-C基准测试,并行实例恢复

2017-12-20 16:35:56 0

0 在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟,然后将此时钟作为SERDES的参考时钟。

2017-11-18 12:08:49 5272

5272

随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试、野外

2017-11-18 06:28:42 1160

1160

该小区所有邻区向该小区切换的KPI指标判断是否为休眠小区,基站自动对OMC回复的休眠小区进行恢复工作。并且基于该方案进行实际的组网测试,测试结果表明该方案能够有效检测出睡眠小区并恢复小区功能。

2017-11-16 17:36:09 4

4 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2017-11-16 01:01:29 20403

20403

PLL(锁相环)是SoC(系统单芯片)中常见的模拟电路。几乎所有时钟速率高于30MHz的SoC都会用一只PLL作频率合成。不过,世上并不存在一种“万能”的PLL。各种器件都有其频率、功率、面积、性能和功能范围。

2017-09-07 18:43:27 9

9 这是一款专业的苹果手机删除照片恢复软件,支持通过设备扫描恢复,通过iTunes备份恢复和通过iCloud备份恢复三种恢复方式全面找回丢失的数据。那么,下面小编就给大家展示下具体怎么去操作这款软件。

2017-08-12 23:24:47 1661

1661

一种基于FPGA的微波时钟恢复的设计与实现_张丽

2017-03-04 18:11:24 1

1 Oracle数据库非归档模式重做日志恢复方法_王超

2017-02-28 20:38:20 0

0 普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54:11 6597

6597

汽车电子测试测量解决方案

2016-12-25 00:16:43 4

4 Tektronix产品选购指南_测试和测量解决方案

2016-08-16 19:37:49 11

11 光学发射机发送波形一致性测试要求中包括需要新的参考接收机及采用标准时钟恢复单元,其中参考接收机要有严格控制的频响及19.34GHz的3 dB带宽,时钟恢复单元要有10 MHz PLL环路带宽及

2011-08-08 16:46:40 1353

1353 Si5374和Si5375是业界第一款集成了四个独立高性能锁相回路(PLL)的单芯片时钟IC,它所提供的PLL集成是其它竞争解决方案的两倍,抖动则低了40%。

2011-05-18 09:39:47 2126

2126

摘 要:提出了一种采用片内PLL实现实速扫描测试的方案。在该方案中,移入测试向量时使用测试仪提供的时钟,激励施加和响应捕获采用片内PLL生成的高速时钟,从而降低了实速扫

2010-10-11 11:19:02 33

33 Cisco常见路由器密码和版本恢复方法探讨

摘要:本文对CISCO公司的一些常见路由器的密码恢复进行了探讨和总结,同时描述了对路

2010-04-01 11:15:06 327

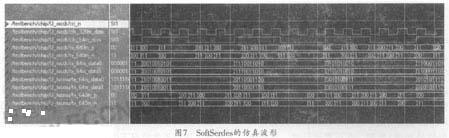

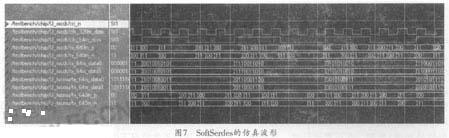

327 基于FPGA的SoftSerdes设计与实现

0 引言

在高速源同步应用中,时钟数据恢复是基本的方法。最普遍的时钟恢复方法是利用数字时钟模块(DCM)

2009-12-28 09:23:40 879

879

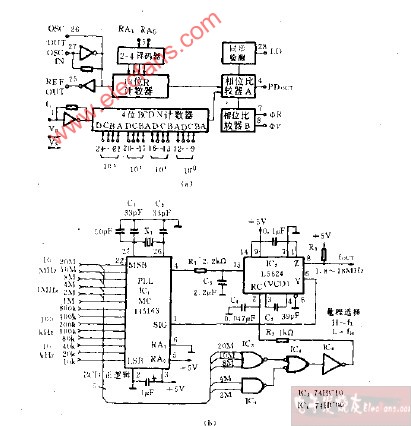

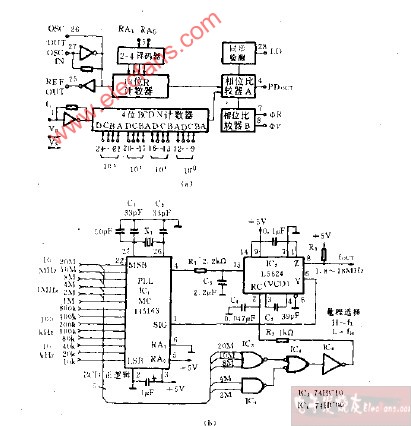

针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

36 基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3352

3352

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1424

1424

PLL合成器方式时钟脉冲振荡电路图

2009-07-16 11:19:18 425

425

HFAN-04.5.5评估电源噪声抑制比对PLL时钟合成器的影响

Characterizing Power-Supply Noise Rejection in PLL Clock

2009-06-19 07:35:38 50

50 本文主要设计了基于相位控制技术的时钟恢复系统的PLL 锁相环路。分别对各单元电路结构——鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器进行设计。采用2.5V,0.25μm

2009-06-01 15:51:53 53

53 精密参考时钟在时钟与数据恢复电路中的应用

2009-05-04 13:36:44 35

35 采用一种新的时钟增强方案并配合双区折射率耦合激光器实现非归零码信号的全光时钟恢复,通过数学仿真研究了此时钟恢复系统在64 Gb/s非归零码系统中的性能表现。仿真结果表

2009-03-04 10:38:27 19

19

电子发烧友App

电子发烧友App

评论