0、引言

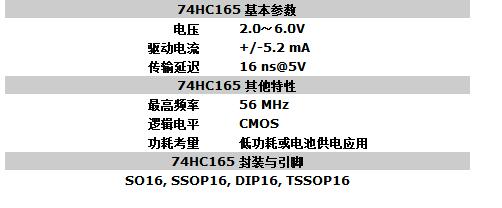

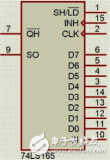

74HC165是一款高速CMOS移位寄存器,电压为2.0~6.0V,驱动电流为+/-5.2mA。74HC165引脚兼容TTL(LSTTL)系列(定义于JEDEC标准№.7A)。

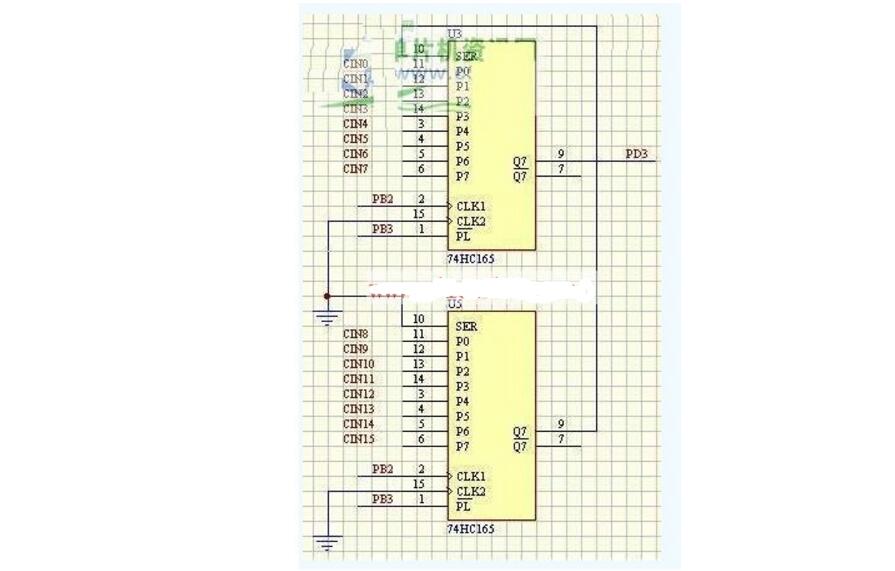

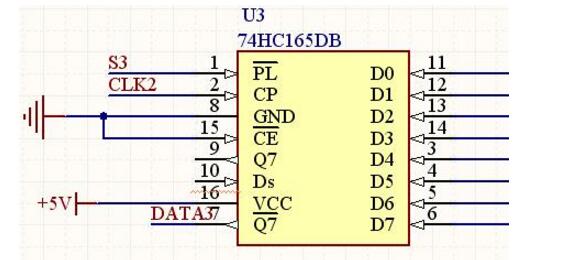

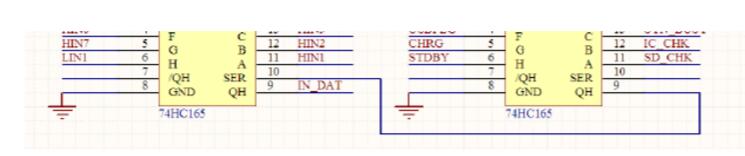

74HC165是8位并行输入串行输出移位寄存器,可在末级得到互斥的串行输出(Q0和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0→Q1→Q2,等等)。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。只有在CP为高时,才允许CE由低转高。在PL上升沿来临之前,CP或者CE应当置高,以防止数据在PL的活动状态发生位移。

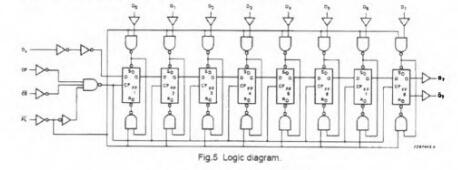

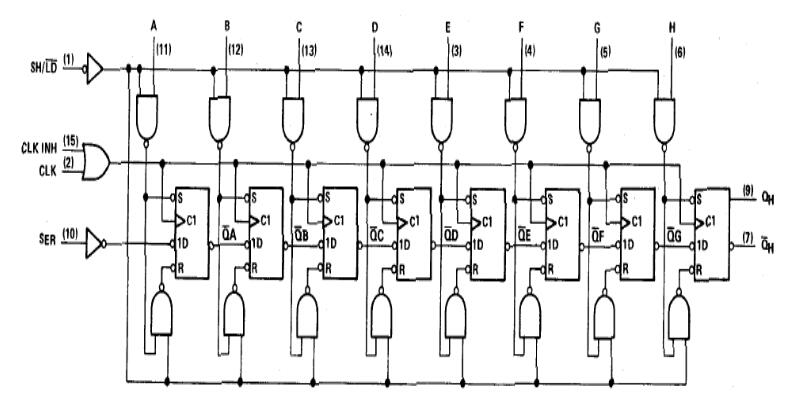

图174HC165逻辑图

单片机的开漏口输出高电平时,需要上拉电阻,否则无法输出高电平,同时为了提高抗干扰能力还要接一个瓷片电容进行滤波。

1、现象描述

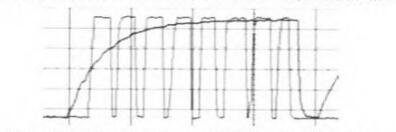

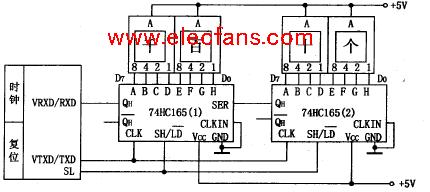

74HC165的数据装载口上拉一个10K欧姆的电阻(R160)到5V,串联一个510Ω(R260)的限流电阻和滤波电容102(C69)到单片机开漏口。通过计算RC充电时间,R=R160+R260=10510Ω,C=C69=1000PF,充电电压为5V,算出充电时间为42.04us。实际测量的充电时间为42us左右,同计算的时间基本一致。(若为推挽输出口控制PL脚,充电时只通过R260=510Ω和电容C69=1000PF,充电时间约为2.04us)。如图2,时钟口波形为脉冲数较多的,数据装载口为脉冲数较少的,可知数据装载口还没有完全达到高电平时,就有了移位脉冲,导致移位失效,数据读取错误。

图2C为102时74HC165数据装载口和时钟口波形

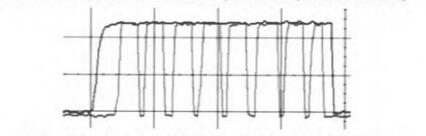

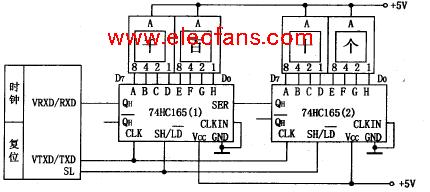

若电容C改为101时,通过计算和实际测量,得到充电时间为4.204us,充电速度快了十倍,如下图3。数据装载口变为可靠的高电平后,才有移位时钟脉冲,移位成功,数据读取成功。

图3C为101时74HC165数据装载口和时钟口波形

2、原因分析

74HC165是一个8位移位寄存器(并行输入、互补串行输出),当移位/置入控制端PL为低电平时,并行数据A-H(D0-D7)被置入寄存器,而与时钟(CP)及串行数据(Ds)均无关。当PL为高电平时,并行置数功能被禁止。要特别注意,移位时,PL为低电平时,移位无效。PL为高电平时,才能移位。当PL为高电平,而且CE为低电平时,与非门的输出完全由CP控制。当PL为低电平时,虽然CE为低电平,但是与非门的输出固定为高电平,不论CP电平如何变化,与非门的输出始终固定为高电平。所以,显然只有CE低电平去使能CP脉冲是不够的,同时PL也为高电平才能使CP脉冲有效。如图1中的D触发器1。

2.1PL为高电平时,由于SD和RD连接的与非门,有一个管脚连接PL的非门,是低电平,故SD(直接置1端)和RD(直接清零端)都是高电平,不影响电路工作。所以每次CP的上升沿,D端数据会移动到Q端,并且锁存起来。

2.2PL为低电平时,由于SD和RD连接的与非门有一个管脚连接PL的非门,是高电平,故SD(直接置1端)和RD(直接清零端)的状态都完全根据D0决定。当D0为1时,SD为0(低电平有效),RD为1,故Q1直接置1。当D0为0时,SD为1,RD为0(低电平有效),故Q1直接清0。这就是数据装载的原理。同时,由于PL为低电平时,CP被与非门无效了,所以每次CP的上升沿,D端数据不会移动到Q端。

3、结论

若PL的高电平不可靠时,会出现移位失败的问题,从而导致数据读取错误。要使CP的移位有效,提前必须使CE为可靠低电平且PL为可靠的高电平。当开漏口控制PL引脚时,务必注意查看由低电平到高电平的波形,是否提前于CP的上升沿。若变为高电平以后,才有CP上升沿,则没有问题;若还没有完全变为高电平,此时CP上升沿出现,则有可能移位不成功。

电子发烧友App

电子发烧友App

评论