什么是奇偶校验电路?奇偶校验器是时序逻辑电路吗? 奇偶校验电路是一种数字电路,在数据传输过程中用于检测数据是否发生错误。在每个数据字节(通常是8位)的最高位添加一位(偶校验)或两位(奇校验)进行校验

2023-10-17 16:16:02 97

97 时序逻辑电路的特点是输出信号不仅与电路的输入有关,还与电路原来的状态有关。

2023-09-17 16:22:32 836

836

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 441

441

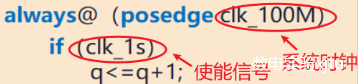

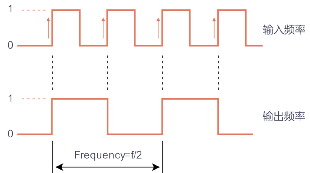

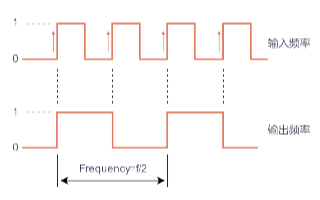

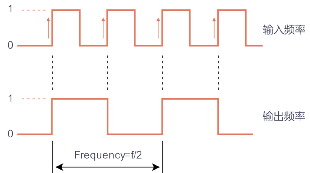

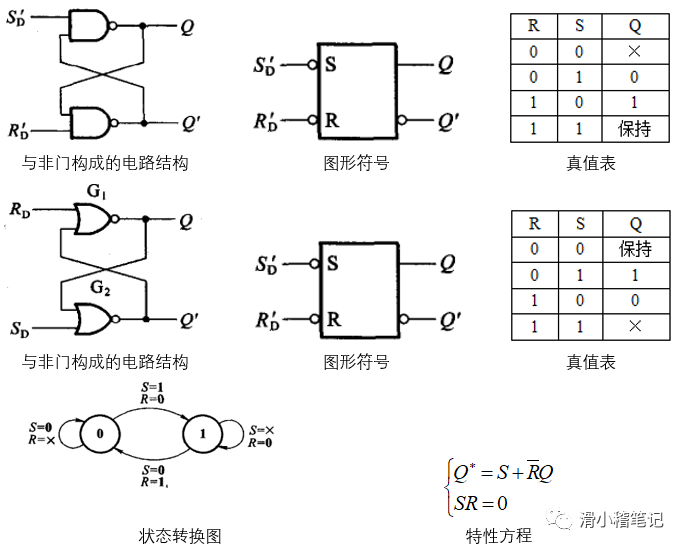

和单片机一样,FPGA开发板上也都会配有晶振用来生成板载时钟。前一篇我们提到了小脚丫的固定板载时钟频率为12MHz,这个频率实际上就是作为我们的时间参考基准。

2023-06-20 17:02:21 531

531

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 830

830

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 680

680

组合逻辑最大的缺点就是会存在竞争冒险,使用时序逻辑就可以极大地避免这种问题,从而使系统更加稳定。

2023-05-22 15:30:24 484

484

时序逻辑电路会复杂很多,强烈推荐mooc上华中科技大学的数字电路与逻辑设计,是我看过讲得最清楚的数电课。

2023-05-14 15:11:33 1093

1093

时序逻辑电路的设计实验1 进一步强化EDA仿真软件的使用;2 掌握利用MSI

2009-03-19 15:10:18

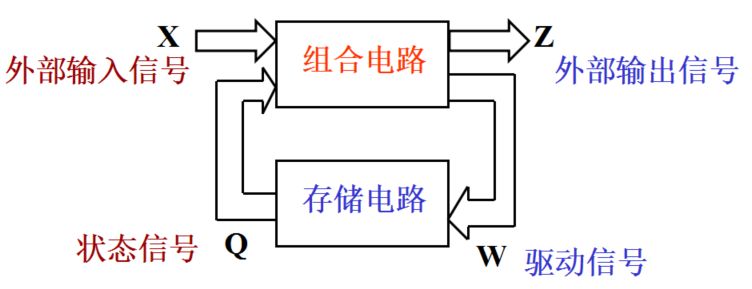

电路在任何时候的输出稳定值,不仅与该时刻的输入信号有关,而且与该时刻以前的电路状态有关; 电路结构具有反馈回路。

2023-03-16 15:42:39 517

517

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 2914

2914

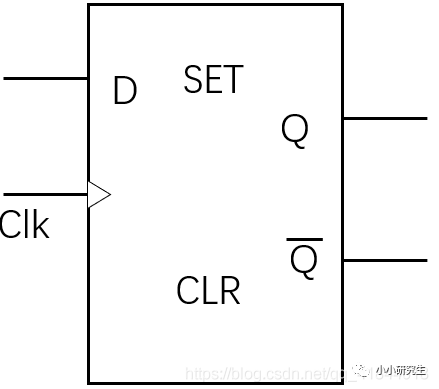

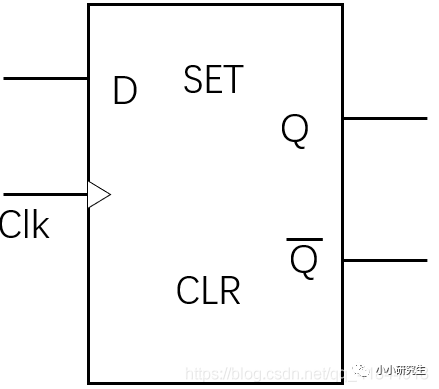

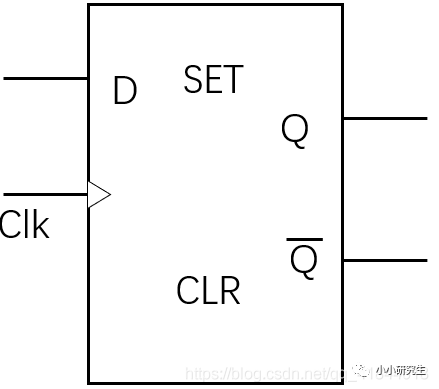

所谓寄存器,是用于寄存一组二进制代码的结构,被广泛地用于各类数字系统和数字计算机中,由于一个触发器只能存储1位二进制代码,所以用N个触发器组成的寄存器可以储存一组N位二进制代码,对于寄存器中的触发器只要求他们具有置1和清0的功能,故任一触发器均可组成寄存器。

2023-03-02 10:17:26 1554

1554

时序逻辑电路的精华——计数器

2022-12-29 09:23:56 748

748 时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

2022-12-05 14:49:30 6

6 在进行MCU开发时,有时需要用到一些简单的数字逻辑电路,LPC804与LPC55XX系列集成了PLU(Programmable Logic Unit),即可编程逻辑单元,可创建小型组合与时序逻辑电路,降低成本。

2022-12-01 09:17:42 823

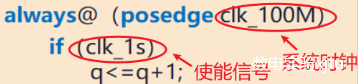

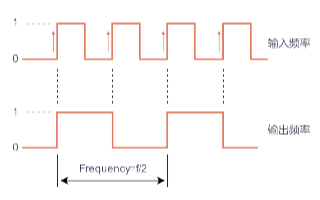

823 和单片机一样,FPGA开发板上也都会配有晶振用来生成板载时钟。前一篇我们提到了小脚丫的固定板载时钟频率为12MHz,这个频率实际上就是作为我们的时间参考基准。正如歌里唱的那样: 嘀嗒嘀嗒嘀嗒嘀嗒 时针它不停在转动 因此,小脚丫只要在通电之后,它的内部时钟就会每隔83.8ns滴答一次。这个时间真的很快,连光速还没来得及跑出小区大门就被掐断了。那么问题来了:如果在某些应用场合中,我们不需要这么快的嘀嗒该怎么办?比如,我们想让

2021-01-06 17:02:34 8466

8466

了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,

2020-12-25 14:39:28 3607

3607

本文档的主要内容详细介绍的是时序逻辑电路的学习课件免费下载。时序逻辑:与时间先后顺序有关,不仅与当前因素有关,还与前一时刻因素有关,状态机是描述时序逻辑的数学模型

2020-11-17 17:12:00 18

18 本文档的主要内容详细介绍的是组合逻辑电路和时序逻辑电路的学习课件免费下载包括了:任务一 组合逻辑电路,任务二 编码器,任务三 译码器,任务四 集成触发器,任务五 寄存器,任务六 计数器。

2020-10-27 15:58:24 28

28 既然时序电路是有记忆功能地,那有几个概念必须是要清楚的:输入信号、输出信号、激励信号以及现态、次态及其转换关系。

2020-08-08 10:19:00 2015

2015

本文档的主要内容详细介绍的是模拟电路教程之时序逻辑电路的课件资料免费下载包括了:1 概述,2 时序逻辑电路的分析方法,3 若干常用的时序逻辑电路,4 时序逻辑电路的设计方法。

2020-06-22 08:00:00 13

13 掌握时序逻辑电路的设计方法及调试技巧,熟练掌握触发器的功能及应用,熟练掌握常用MSI时序逻辑芯片的功能及应用

2020-05-20 08:00:00 19

19 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2323

2323

本文档的主要内容详细介绍的是时序逻辑电路的学习教程课件免费下载包括了:1 双稳态触发器,2 寄存器,3 计数器,4 555定时器,5 数模和模数转换

2019-10-11 16:48:11 11

11 时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-09-29 07:00:00 1609

1609

将驱动方程代入相应触发器的特性方程中,便得到该触发器的次态方程。时序逻辑电路的状态方程由各触发器次态的逻辑表达式组成。

2019-02-28 14:06:14 22685

22685 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 60005

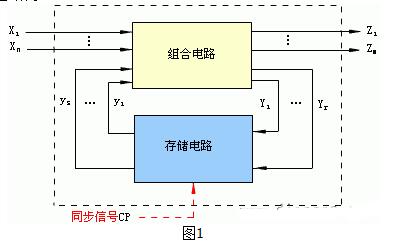

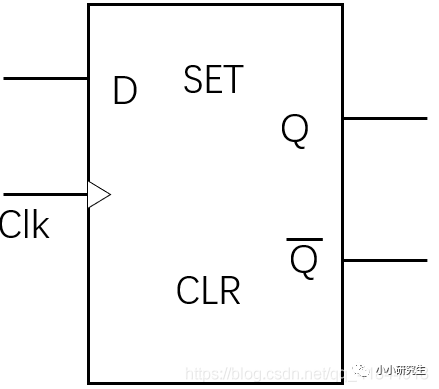

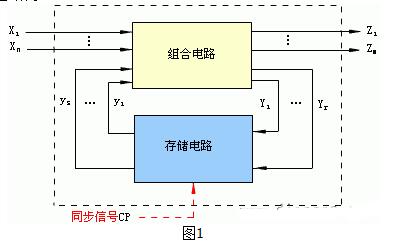

60005 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 48178

48178 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 29485

29485 时序逻辑电路的设计是分析的逆过程,其任务是根据实际逻辑问题的要求,设计出能实现给定逻辑功能的电路。

2019-02-22 08:00:00 8

8 本文档的主要内容详细介绍的是数字电路教程之时序逻辑电路课件的详细资料免费下载主要内容包括了:一 概述,二 时序逻辑电路的分析方法,三 若干常用的时序逻辑电路,四 时序逻辑电路的设计方法,五 时序逻辑电路中的竞争冒险现象

2018-12-28 08:00:00 9

9 本文档的主要内容详细介绍的是如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现。

2018-12-12 16:25:46 7

7 本文档的主要内容详细介绍的是数字电路基础教程之时序逻辑电路的详细资料概述。内容包括了:1.时序逻辑电路分析2.若干常用时序逻辑电路3.时序逻辑电路设计

2018-10-17 08:00:00 41

41 时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

2018-04-09 16:00:00 5279

5279

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 104785

104785

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 51593

51593

时序逻辑路是数字电路的一种,时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 19:19:25 61102

61102

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 120321

120321

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 89189

89189

2017-04-23 19:29:00 15

15 一种设计同步时序逻辑电路的新方法

2017-02-07 15:05:00 29

29 数字电子技术--时序逻辑电路

2016-12-12 22:07:22 1

1 数字电子技术-- 时序逻辑电路

2016-12-12 21:54:28 8

8 电子专业单片机相关知识学习教材资料之时序逻辑电路的分析与设计

2016-09-02 14:30:26 20

20 基础的电子类资料,电子工程师必备文档,快来下载学习吧。

2016-07-04 15:47:18 23

23 基础的电子类资料,电子工程师必备文档,快来下载学习吧。

2016-07-04 15:47:18 23

23 海南大学数字电子技术 (Digital Electronics Technology)课件

2016-06-07 10:41:41 10

10 内容包括:触发器同步计数器,异步计数器,寄存器,基础实验。

2016-04-29 11:28:59 9

9 主要讲了时序逻辑电路的相关知识,能够方便大家学习使用

2016-02-29 14:25:53 3

3 2013-05-02 15:09:20 83

83 2012-12-03 22:55:48 31

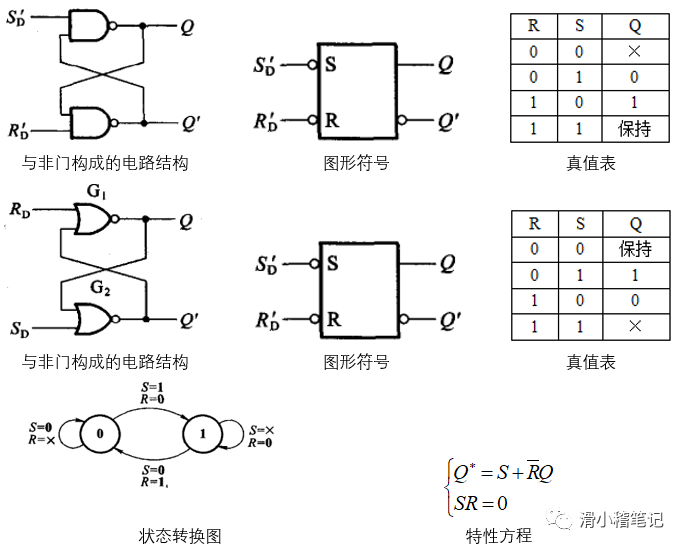

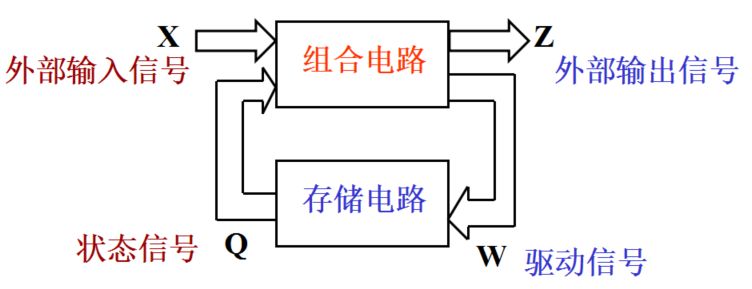

31 组合电路和时序电路是数字电路的两大类。门电路是组合电路的基本单元;触发器是时序电路的基本单元。

2010-08-29 11:29:04 67

67 一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 67

67 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 23

23 [T4.1] 图 T4.1 所示为由或非门构成的基本SR 锁存器,输入S、R 的约束条件是。(A)SR=0 (B)SR=1 (C)S+R=0 (D)S+R=1

2010-08-13 14:42:58 67

67 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 47

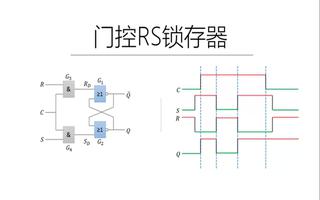

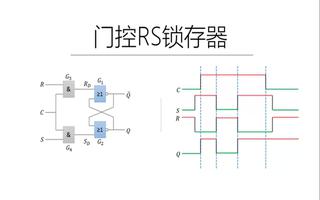

47 本章首先介绍能够存储1 位二值信号的基本单元电路锁存器和触发器。着重介绍各种锁存器和触发器的电路结构、工作原理、逻辑功能、特性及其描述方法。接着介绍时序逻辑电

2010-08-10 11:55:44 85

85 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则与它不同,其特点是:在任意时刻电路产生的稳定输出不仅与当前时刻的输入

2010-05-30 09:46:59 43

43 摘要:文章介绍了Multisim9仿真软件在数字电子技术中时序逻辑电路中的应用,从时序逻辑电路分析、计数器、寄存器等方面介绍了Multisim9仿真软件的优点,提出了Multisim9仿真软件的

2010-05-30 08:21:04 73

73 摘要:基于逻辑电路的设计中经常涉及到用卡诺图化简逻辑函数的过程,给出了利用次态卡诺图设计逻辑电路的方法及不同触发器的状态方程在次态卡诺图上的表示,并举例加以说

2010-05-25 09:41:28 13

13 摘要:通过实际例子,阐述了次态卡诺图在分析和设计时序逻辑电路中的使用方法。该方法的使用可以使时序逻辑电路的分析和设计得到一定的简化,过程中思路清晰,状态转换直

2010-04-28 10:03:10 21

21 时序逻辑电路实例解析

一、触发器 1、电位触发方式触发器

2010-04-15 13:46:25 4871

4871 Verilog HDL语言实现时序逻辑电路

在Verilog HDL语言中,时序逻辑电路使用always语句块来实现。例如,实现一个带有异步复位信号的D触发器

2010-02-08 11:46:43 4371

4371 时序逻辑电路的特点

在第三章所讨论的组合逻辑电路中,任一时刻的输出信号仅仅取决于该时刻的输入信号,而与电路原来

2009-09-30 18:19:22 9517

9517

异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 59

59 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 71

71 时序逻辑电路分析实例

例1 分析图所示电路的逻辑功能。设起始状态是

2009-04-07 23:20:25 4247

4247

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 7731

7731

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 3156

3156

第二十二讲 同步时序逻辑电路的分析方法

内容提要7.1 概述一、时序电路的定义二、电路构成三、分类:1 同步2 异

2009-03-30 16:26:17 4648

4648

时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 1 进一步强化EDA仿真软件的使用;2 掌握利用MSI、可编程器件设计时序逻辑电路的特点、方法;3 掌握时序逻辑电路的调试方法;4&

2009-03-18 20:06:31 47

47

正在加载...

电子发烧友App

电子发烧友App

评论