加法器是非常重要的,它不仅是其它复杂算术运算的基础,也是 CPU 中 ALU 的核心部件(全加器)。

2023-10-09 16:00:51 93

93

电子发烧友网站提供《加法合成器开源分享.zip》资料免费下载

2023-07-13 11:05:00 0

0 镜像加法器是一个经过改进的加法器电路,首先,它取消了进位反相门;

2023-07-07 14:20:50 413

413

电子发烧友网站提供《4位加法器的构建.zip》资料免费下载

2023-07-04 11:20:07 0

0 半加法器是一种执行二进制数相加的数字电路。它是最简单的数字加法器,您只需使用两个逻辑门即可构建一个;一个异或门和一个 AND 门。

2023-06-29 14:35:25 1320

1320

加法器可以是半加法器或全加法器。不同之处在于半加法器仅用于将两个 1 位二进制数相加,因此其总和只能从 0 到 2。为了提高这种性能,开发了FullAdder。它能够添加三个 1 位二进制数,实现从 0 到 3 的总和范围,可以用两个输出位 (“11”) 表示。

2023-06-29 14:27:35 1542

1542

同相加法器(又称为同相组合器、输入能量合成器、同相求和器)是一种电子电路器件,主要应用在通信、信号处理、调试和测量等领域。

2023-06-13 14:53:32 3644

3644

有关加法器的知识,加法器是用来做什么的,故名思义,加法器是为了实现加法的,它是一种产生数的和的装置,那么加法器的工作原理是什么,为什么要采用加法器,下面具体来看下。

2023-06-09 18:04:17 2245

2245 同相加法器(又称为同相组合器、输入能量合成器、同相求和器)是一种电子电路器件,主要应用在通信、信号处理、调试和测量等领域。

2023-06-06 17:21:13 570

570

指针的加法操作我们见过很多,但是减法操作遇到的好像很少。

2023-03-29 10:12:35 200

200 在之前的文章里,曾经多次提到过二进制加法的数字电路,这里详细说说它的细节。

2023-03-23 13:58:17 659

659

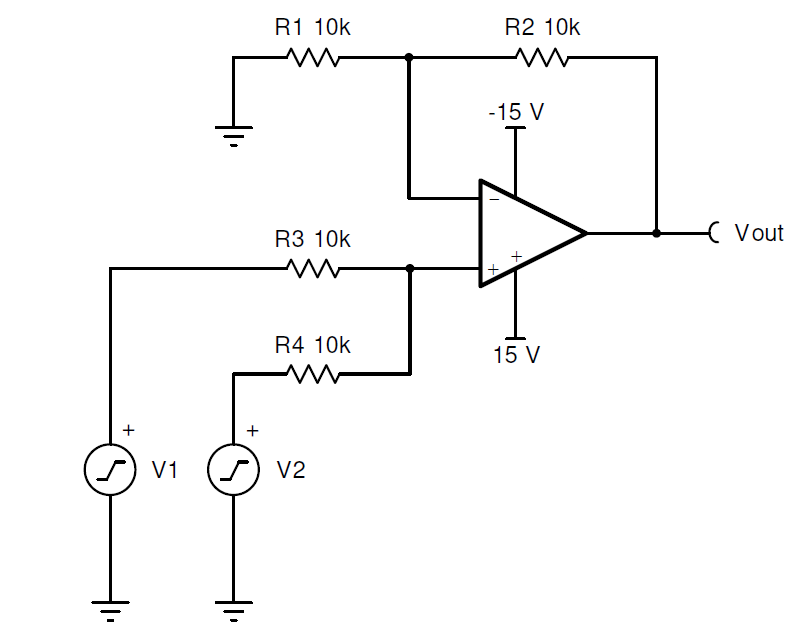

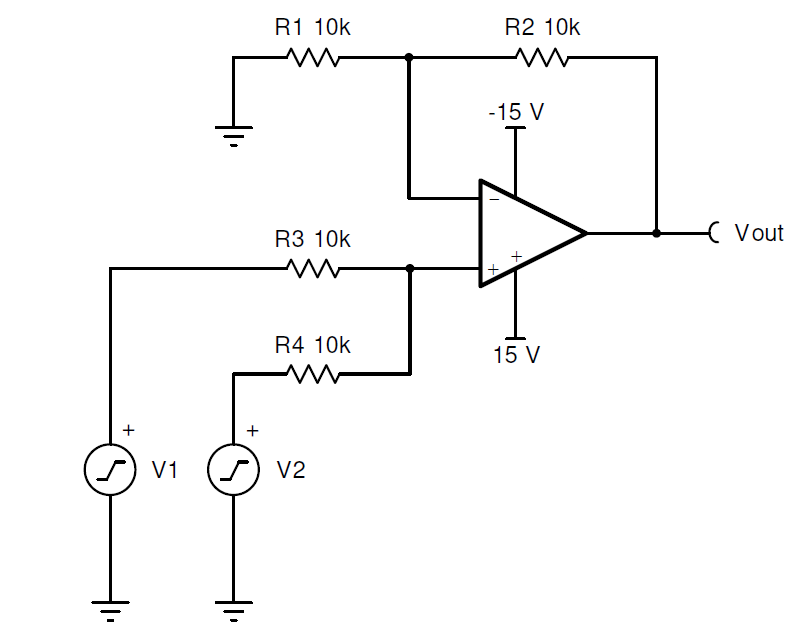

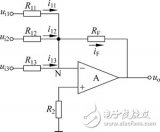

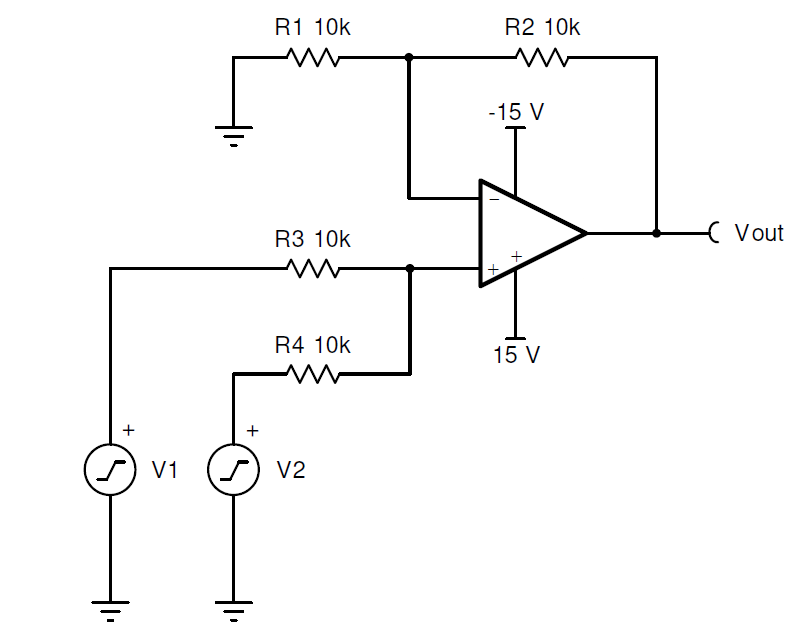

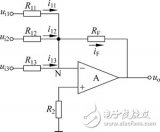

加法放大器的一般设计如以下电路所示。普通反相放大器电路在其反相输入端只有一个电压/输入。如果更多输入电压如图所示连接到反相输入端子,则结果输出将是所有施加的输入电压的总和,但是是反相的。

2023-01-08 10:40:32 1437

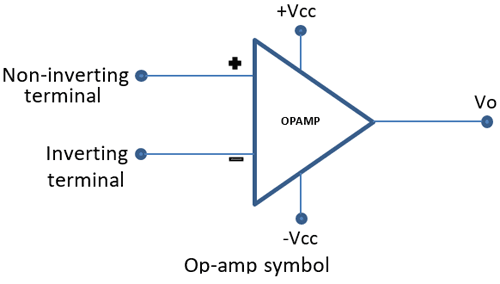

1437 运算放大器(Opamp)有许多有趣的应用,我们已经使用运算放大器创建了许多电路。今天我们将研究运算放大器的另一个应用,即添加两个或多个输入电压,该电路称为求和放大器或运算放大器加法器。在这里,我们将使用 LM358 运算放大器来演示加法器电路。

2022-11-11 15:29:29 7919

7919

一、 实验目的 1.了解二进制加法,加法计数器的工作过程。 2.学会计数器的调整及测试。

2022-10-20 11:49:44 2

2 运算放大器构成加法器 可以分为同相加法器和反相加法器

2022-08-05 17:17:38 19647

19647

行波进位加法器和超前进位加法器都是加法器,都是在逻辑电路中用作两个数相加的电路。我们再来回顾一下行波进位加法器。

2022-08-05 16:45:00 639

639

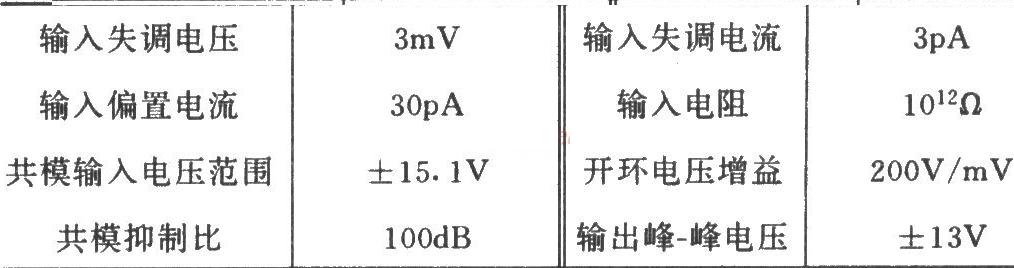

集成运算放大电路实验实验目的1. 了解集成运算放大器的特点。2. 掌握集成运算放大器在信号运算方面的应用。实验原理集成运算放大器按照输入方式可以分为同相、反相、差分三种接法,按照输入电压与输出电压的运算关系可以分为比例、加法、减法、积分、微分等,输入方式和运算关系组合起来,可以构成各种运算放大器。

2008-09-22 12:18:59

实验二、80C51汇编语言编程实验:编写3字节二进制加法子程序,并用主程序调用不同的加数和被加数来检测该子程序的正确性。需考虑有进位和无进位情况。 报价 200文章目录实验二、80C51汇编语言

2021-11-23 09:36:06 31

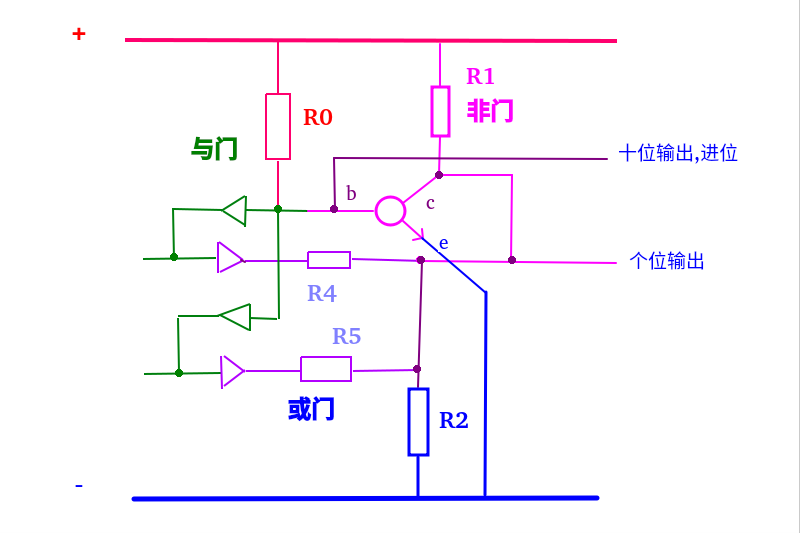

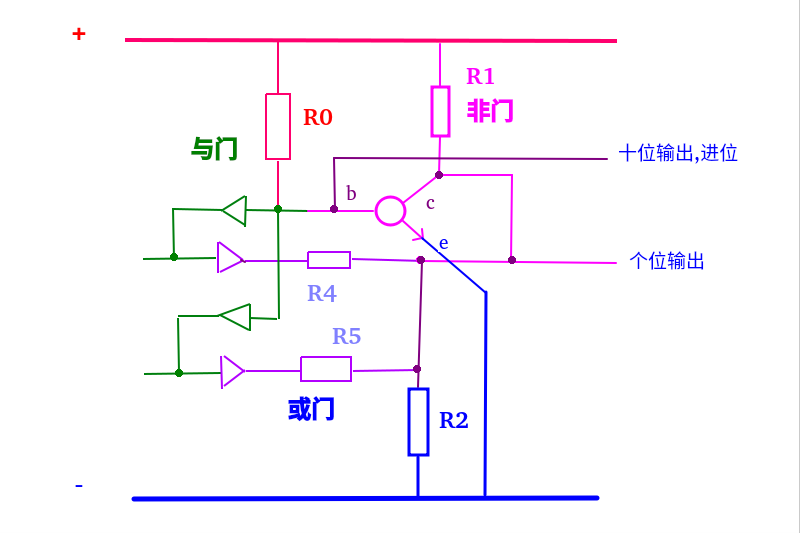

31 加法器的实现在解释这个半加法器之前,要明白计算机其实就是靠简单电路集成起来的复杂电路而已,而构成这些复杂电路最简单的逻辑电路就是“与”、“或”、“非”。而在他们的基础之上进行组合,...

2021-11-11 12:06:03 20

20 介绍各种加法器的Verilog代码和testbench。

2021-05-31 09:23:42 19

19 二进制加法 我已经忘了是什么时候学的加法了,应该是小学吧,先学10以内的,再学100以内的,然后不管多大的数都可以随便加了,算式很简单,就是逢10进1。 下面这个式子是一个万以内的加法: 相应

2021-04-29 11:06:03 4582

4582

本文档的主要内容详细介绍的是加法器产生数和的装置实验工程文件资料合集免费下载。

2021-03-08 15:22:19 3

3 verilog实现加法器,从底层的门级电路级到行为级,本文对其做出了相应的阐述。

2021-02-18 14:53:52 5005

5005

。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

2021-02-18 14:40:31 29303

29303

华为诺亚方舟实验室联合悉尼大学发布论文《Kernel Based Progressive Distillation for Adder Neural Networks》,提出了针对加法神经网...

2020-12-08 22:11:53 158

158 多位二进制减法器,是由加法电路构成的;在加法电路的基础上,减法与加法采用同一套电路,实现加减法共用。

2020-09-01 16:02:09 18552

18552

二进制加法器是半加器和全加法器形式的运算电路,用于将两个二进制数字加在一起.

2019-06-22 10:56:38 23032

23032

。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

2019-06-19 14:20:39 23685

23685

本文档的主要内容详细介绍的是模拟电路实验教程之基本运算电路的详细资料说明。一。实验目的1.掌握反相比例运算、同相比例运算、加法、减法运算电路的原理,设计方法及测试方法。2.能正确分析运算精度与运算电路中各元件参数之间的关系。

2019-05-27 17:26:51 22

22 4.1.3加法和减法运算电路

2019-04-18 06:03:00 14462

14462

加法器是数字系统中的基本逻辑器件。例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

2019-04-15 08:00:00 4

4 本文档的主要内容详细介绍的是反相加法器EWB电路仿真的详细资料免费下载。

2018-09-21 15:38:10 12

12 本文档的主要内容详细介绍的是4位加法器EWB电路仿真详细资料免费下载。

2018-09-19 16:25:53 24

24 一、什么是加法器加法器是为了实现加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半

2018-03-16 15:57:19 20303

20303

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2018-01-29 11:28:26 79946

79946

加法器是为了实现加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2018-01-29 10:49:50 30686

30686

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

2018-01-17 10:42:03 134108

134108

计算机所做的计算处理只有加法,有了加法就可以用加法计算除法,乘法,减法。而计算机所处理的数据也只是二进制数也就是0和1。下面简单阐述二进制加法机的构造原理,这是cpu计算单元的基本计算原理。

2017-11-13 15:22:25 5297

5297

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2017-08-16 12:06:45 16643

16643

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。减法电路是基本集成运放电路的一种,减法电路可以由反相加法电路构成,也可以由差分电路构成。基本集成运放电路有加、减、积分和微分等四种运算。一般是由集成运放外加反馈网络所构成的运算电路来实现。

2017-08-16 11:09:48 157219

157219

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2017-08-16 10:21:31 143816

143816

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。

2017-08-16 09:39:34 21204

21204

加法器是为了实现加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

2017-06-06 08:45:01 22064

22064

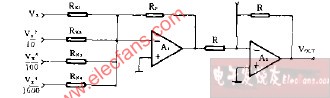

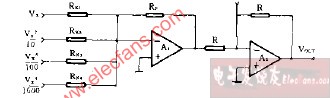

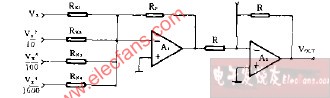

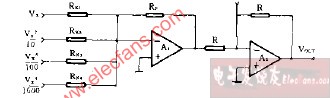

加法运算电路能实现多个模拟量的求和运算。图1所示为一个3个输入信号的反相加法运算电路。

2017-05-15 09:41:34 188724

188724

模拟电路实验--差动放大电路实验

2017-02-07 15:05:00 4

4 基于Skewtolerant Domino的新型高速加法器

2017-01-22 20:29:21 8

8 模拟电路实验--差动放大电路实验

2016-12-29 18:52:25 1

1 实验目的:

1.了解二进制加法,加法计数器的工作过程。

2.学会计数器的调整及测试。

2016-10-11 17:41:59 61

61 同相加法器输入阻抗高,输出阻抗低 反相加法器输入阻抗低,输出阻抗高.加法器是一种数位电路,其可进行数字的加法计算。当选用同相加法器时,如A输入信号时,因为是同相加法器,输入阻抗高,这样信号不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 54133

54133

二进制加法程序【C语言版】二进制加法程序【C语言版】二进制加法程序【C语言版】二进制加法程序【C语言版】

2015-12-29 11:03:51 4

4 二进制加法程序【汇编版】二进制加法程序【汇编版】二进制加法程序【汇编版】二进制加法程序【汇编版】

2015-12-29 11:02:06 3

3 为了缩短加法电路运行时间,提高FPGA运行效率,利用选择进位算法和差额分组算法用硬件电路实现32位加法器,差额分组中的加法单元是利用一种改进的超前进位算法实现,选择进位算

2013-09-18 14:32:05 33

33 实验五 全加器、译码器及数码显示电路 一、实验目的 1、掌握全加器逻辑功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段译码器和七段数码管显示十进制数的方法。 3、掌握

2012-07-16 23:01:22 37

37 浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计

2012-07-06 15:05:42 47

47 一、 实验目的 1.了解信号 运算放大电路 ,反相加法电路,减法电路,积分电路、三运放高共模抑制比放大工作原理,放大器性能。 2.通过实验,可以理论联系实际,增加学生对运算

2011-07-25 17:17:04 71

71 电子发烧友为您提供了运算放大加法器电路图!

2011-06-27 09:28:50 7614

7614

摘要:加法运算在计算机中是最基本的,也是最重要的运算。传统的快速加法器是使用超前进位加法器,但其存在着电路不规整,需要长线驱动等缺点。文章提出了采用二叉树法设

2010-05-19 09:57:06 62

62 加法电路

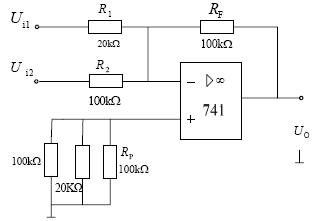

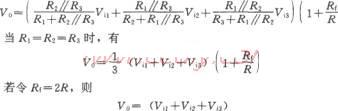

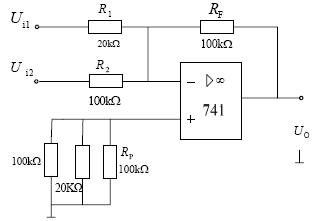

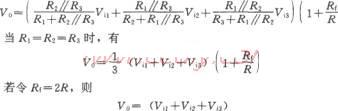

加法电路的输出电压UO是N个输入电压UI1,UI2...UIN的加权和,它的基本功能可以用数学表示式Y=A1*1+A2*2...+AN*N表示。如图5.4-1所示。

2010-04-23 15:49:32 21655

21655

计算机常用的组合逻辑电路:加法器

一、加法器

1.半加器: 不考虑进位输入时,两个数码X n和Y n相加称为半加。设半加和为H n ,则H n 的

2010-04-15 13:48:11 5885

5885 补码加法,补码加法计算原理 负数用补码表示后,可以和正数一样来处理。这样,运算器里只需要一个加法器就可以了,不必为了负数的加法运算,再配一个减

2010-04-13 11:41:28 16742

16742 十进制加法器,十进制加法器工作原理是什么?

十进制加法器可由BCD码(二-十进制码)来设计,它可以在二进制加法器的基础上加上适当的“校正”逻辑来实现,该校正逻

2010-04-13 10:58:41 12142

12142 加法器,加法器是什么意思

加法器 : 加法器是为了实现加法的。 即是产生数的和的装置。加数和被加数为输入,和数与

2010-03-08 16:48:58 4923

4923 PLD实验指导书:实验一 Maxplus2 软件的使用及设计流程4实验二 七段译码器的设计.9实验三 数码管扫描显示电路.11实验四 八位加法器的设计.....14实验五 抢答器的设计.16

2010-02-06 14:13:03 1

1

级数各项加法电路图

2009-07-20 12:14:18 515

515

级数各项加法电路图

2009-07-17 11:30:47 571

571

加法电路图

2009-07-08 11:44:02 847

847

图二所示为4位并行的BCD加法器电路。其中上面加法器的输入来自低一级的BCD数字。下

2009-03-28 16:35:54 11100

11100

电路实验课程简介 电路实验课程简介 实验教学日历 实验教学日历 实验评分标准和课程基本要求 实验评分标准和课程基本要求

2008-12-17 13:50:11 13

13

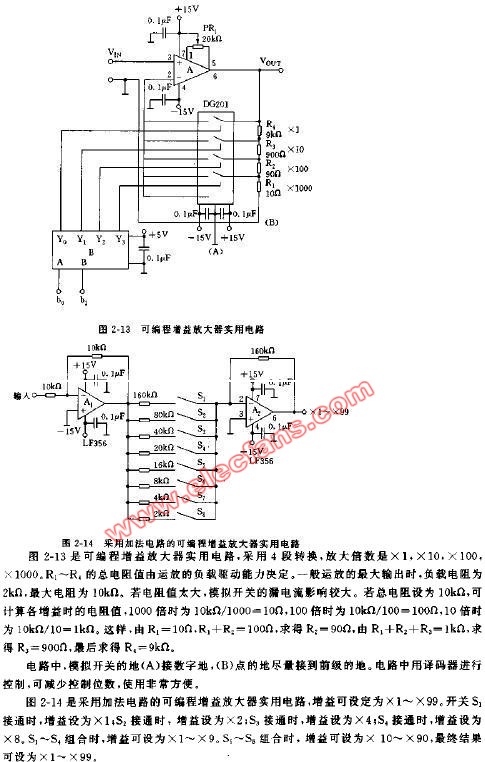

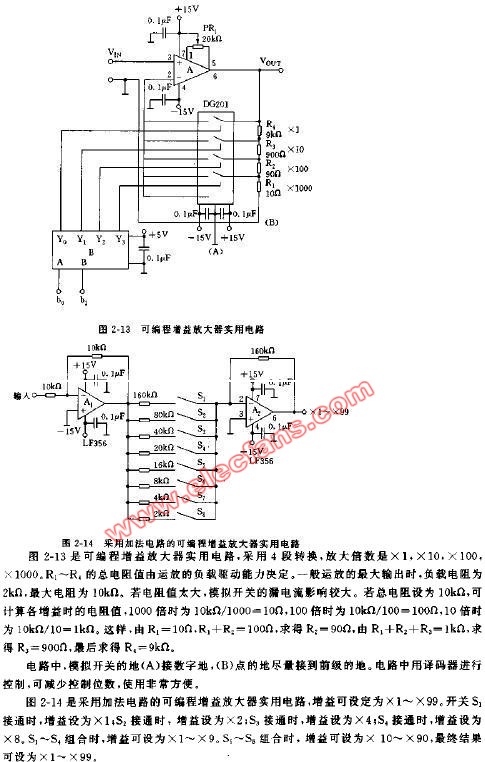

采用加法电路的可编程增益放大器电路

2008-12-17 01:41:12 642

642

加法运算放大器电路包含有

2008-09-27 17:33:18 26549

26549

模拟加法电路实际上有反相

2008-09-27 17:29:11 8653

8653

反相加法运算电路为若干个输入信号从集成运放的反相输入端引入,输出信号为它们反相按比例放大的代数和。

2008-09-22 11:44:29 2857

2857

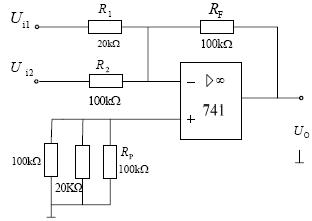

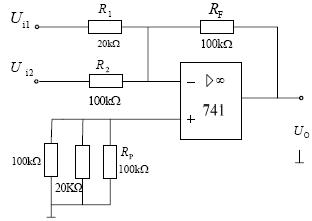

同相加法电路(由LF155组成的)

2008-01-21 14:16:11 4618

4618

正在加载...

电子发烧友App

电子发烧友App

评论