实验六 帧同步

一、实验目的

1. 掌握巴克码识别原理。

2. 掌握同步保护原理。

3. 掌握假同步、漏同步、捕捉态、维持态概念。

二、实验内容

1. 观察帧同步码无错误时帧同步器的维持态。

2. 观察帧同步码有一位错误时帧同步器的维持态和捕捉态。

3. 观察同步器的假同步现象和同步保护作用。

三、基本原理

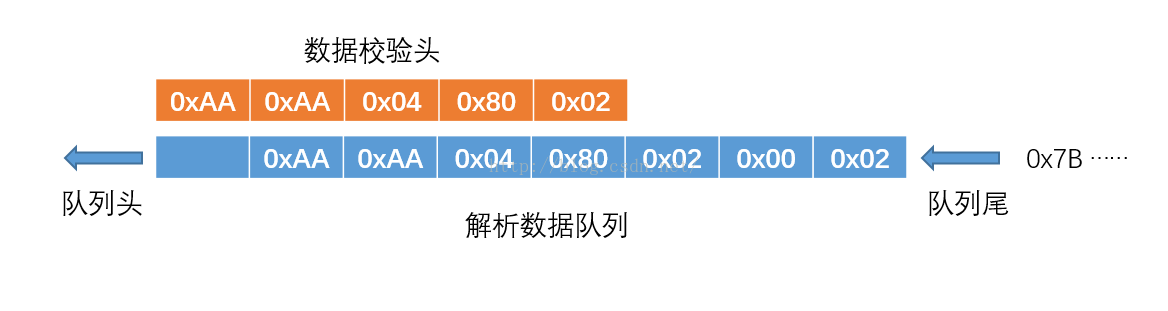

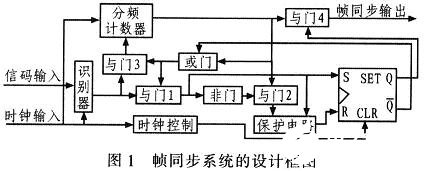

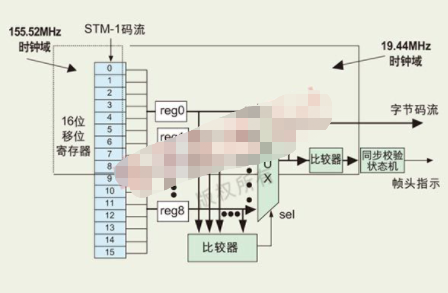

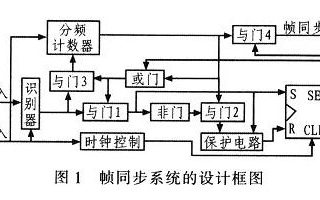

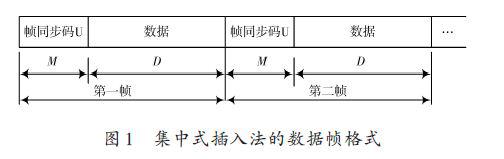

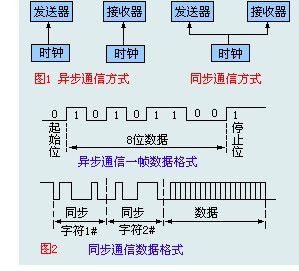

在时分复用通信系统中,为了正确地传输信息,必须在信息码流中插入一定数量的帧同步码,可以集中插入、也可以分散插入。本实验系统中帧同步识别码为7位巴克码,集中插入到每帧的第2至第8个码元位置上。帧同步模块的原理框图如图6-1所示,电原理图如图6-2所示(见附录),其内部只使用+5V电压。

本模块有以下测试点及输入输出点:

• S-IN 数字基带信号输入点(2个)

• BS-IN 位同步信号输入点(2个)

• GAL 巴克码识别器输出信号测试点

• ÷24 24分频器输出信号测试点

• TH 判决门限电平测试点

• FS 帧同步信号测试点

图6-1中各单元与电路板上元器件的对应关系如下:

• ÷24分频器 U60、U61:计数器4017;U58:C、U58:E:或门4071

• 移位寄存器 U50、U51:四位移位寄存器74175

• 相加器 U52:可编程逻辑器件GAL20V8

• 判决器 U53:可编程逻辑器件GAL20V8

• 单稳 U59:单稳态触发器4528

• 与门1 U56:A:与门7408

• 与门2 U56:C:与门4708

• 与门3 U56:D:与门7408

• 与门4 U56:B:与门7408

• 或门 U58:A:或门4071

• ÷3分频器 U54:计数器4017

• 触发器 U55:JK触发器4027

图6-1 帧同步模块原理框图

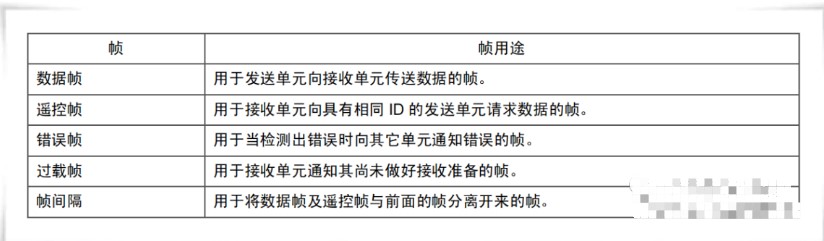

从总体上看,本模块可分为巴克码识别器及同步保护两部分。巴克码识别器包括移位寄存器、相加器和判决器,图6-1中的其余部分完成同步保护功能。

移位寄存器由两片74175组成,移位时钟信号是位同步信号。当7位巴克码全部进入移位寄存器时,U50的Q1、Q2、Q3、Q4及U51的Q2、Q3、Q4都为1,它们输入到相加器U52的数据输入端D0~D6,U52的输出端Y0、Y1、Y2都为1,表示输入端为7个1。若Y2Y1Y0=100时,表示输入端有4个1,依此类推,Y2Y1Y0的不同状态表示了U52输入端为1的个数。判决器U53有6个输入端。IN2、IN1、IN0分别与U52的Y2、Y1、Y0相连,L2、L1、L0与判决门限控制电压相连,L2、L1已设置为1,而L0由同步保护部分控制,可能为1也可能为0。在帧同步模块电路中有三个发光二极管指示灯P1、P2、P3与判决门限控制电压相对应,即从左到右与L2、L1、L0一一对应,灯亮对应1,灯熄对应0。判决电平测试点TH就是L0信号,它与最右边的指示灯P3状态相对应。当L2L1L0=111时门限为7,三个灯全亮,TH为高电平;当L2L1L0=110时门限为6,P1和P2亮,而P3熄,TH为低电平。当U52输入端为1的个数(即U53的IN2IN1IN0) 大于或等于判决门限于L2L1L0,识别器就会输出一个脉冲信号。

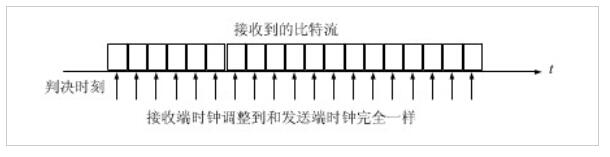

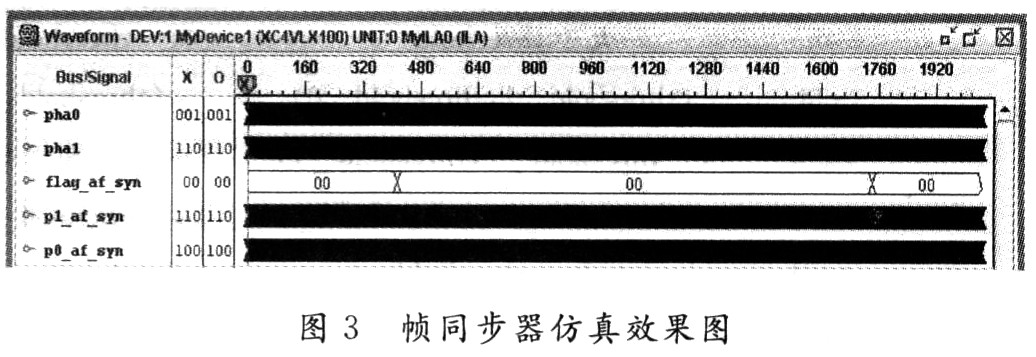

当基带信号里的帧同步码无错误时(七位全对),把位同步信号和数字基带信号输入给移位寄存器,识别器就会有帧同步识别信号GAL输出,各种信号波形及时序关系如图6-3所示,GAL信号的上升沿与最后一位帧同步码的结束时刻对齐。图中还给出了÷24信号及帧同步器最终输出的帧同步信号FS-OUT,FS-OUT的上升沿稍迟后于GAL的上升沿。

图6-3 帧同步器信号波形

÷24信号是将位同步信号进行24分频得到的,其周期与帧同步信号的周期相同(因为一帧24位是确定的),但其相位不一定符合要求。当识别器输出一个GAL脉冲信号时(即捕获到一组正确的帧同步码),在GAL信号和同步保护器的作用下,÷24电路置零,从而使输出的÷24信号下降沿与GAL信号的上升沿对齐。÷24信号再送给后级的单稳电路,单稳设置为下降沿触发,其输出信号的上升沿比÷24信号的下降沿稍有延迟。

同步器最终输出的帧同步信号FS是由同步保护器中的与门3对单稳输出的信号及状态触发器的Q端输出信号进行“与”运算得到的。

电路中同步保护器的作用是减小假同步和漏同步。

当无基带信号输入(或虽有基带信号输入但相加器输出低于门限值)时,识别器没有输出(即输出为0),与门1关闭、与门2打开,单稳输出信号通过与门2后输入到÷3电路,÷3电路的输出信号使状态触发器置“0”,从而关闭与门3,同步器无输出信号,此时Q的高电平把判决器的门限置为7(P3灯亮)、且关闭或门、打开与门1,同步器处于捕捉态。只要识别器输出一个GAL信号(因为判决门限比较高,这个GAL信号是正确的帧同步信号的概率很高),与门4就可以输出一个置零脉冲使÷24分频器置零,÷24分频器输出与GAL信号同频同相的的周期信号(见图6-3)。识别器输出的GAL脉冲信号通过与门1后使状态触发器置“1”,从而打开与门3,输出帧同步信号FS-OUT,同时使判决器门限降为6(P3灯熄)、打开或门、同步器进入维持状态。在维持状态下,因为判决门限较低,故识别器的漏识别概率减小,假识别概率增加。但假识别信号与单稳输出信号不同步,故与门1、与门4不输出假识别信号,从而使假识别信号不影响÷24电路的工作状态,与门3输出的仍是正确的帧同步信号。实验中可根据判决门限指示灯P3判断同步器处于何种状态,P3亮为捕捉态,P3熄为同步态。

在维持状态下,识别器也可能出现漏识别。但由于漏识别概率比较小,连续几帧出现漏识别的概率更小。只要识别器不连续出现三次漏识别,则÷3电路不输出脉冲信号,维持状态保持不变。若识别器连续出现三次漏识别,则÷3电路输出一个脉冲信号,使维持状态变为捕捉态,重新捕捉帧同步码。

不难看出,若识别器第一次输出的脉冲信号为假识别信号(即首次捕获到的是信息数据中与帧同步码完全相同的码元序列),则系统将进入错误的同步维持状态,由于本实验系统是连续传输以一帧为周期的周期信号,所以此状态将维持下去,但在实际的信息传输中不会连续传送这种周期信号,因此连续几帧都输出假识别信号的概率极小,所以这种错误的同步维持状态存在的时间是短暂的。

当然,同步保护器中的÷3电路的分频比也可以设置为其它值,此值越大,在维持状态下允许的识别器的漏识别概率也越大。

在维持态下对同步信号的保护措施称为前方保护,在捕捉态下的同步保护措施称后方保护。本同步器中捕捉态下的高门限属于后方保护措施之一,它可以减少假同步概率,当然还可以采取其它电路措施进行后方保护。低门限及÷3电路属于前方保护,它可以保护已建立起来的帧同步信号,避免识别器偶尔出现的漏识别造成帧同步器丢失帧同步信号即减少漏同步概率。同步器中的其它保护电路用来减少维持态下的假同步概率。

四、实验步骤

本实验使用数字信源单元及帧同步单元。

1、熟悉帧同步单元的工作原理,将信源单元的NRZ-OUT、BS-OUT分别与帧同步单元的S-IN、BS-IN对应相连,接通实验箱电源。

2、观察同步器的维持态(同步态)

将数字信源单元的K1(左边的8位微动开关)置于×111 0010状态 (110010为帧同步码,×是无定义位,可任意置“1”或置“0”),K2置为1000 0000状态、K3则置为全0状态,示波器CH1接信源单元的NRZ-OUT,CH2分别接帧同步单元的GAL、÷24、TH及FS,观察并纪录上述信号波形以及与NRZ-OUT的相位关系(注意:TH为0电平,帧同步模块的P3指示灯熄,P1、P2亮,表示识别门限为6)。使信源的帧同步码(注意是K1的第2位到第8位)中错一位,重新观察上述信号,此时GAL、÷24、TH、FS应不变。使信源帧同步码再错一位重作上述观察。(此时同步器应转入捕捉态,仅÷24波形不变,请根据原理框图分析思考此过程)。

3、观察同步器的捕捉态(失步态)

上步中电路已经由同步态变为捕捉态,示波器仍观察÷24信号,此时断开电源,再接通电源,可看到÷24波形的下降沿已不再对准第一个数据位(相位随机),观察其他信号可见TH为高电平,FS无输出。将信源K1从刚才错两位状态还原为仅错一位状态,观察÷24信号相位是否变化。再将信源K1还原为正确的帧同步码(×1110010) ,观察÷24信号相位是否变化。分析÷24信号相位变化原因,从而理解同步器从失步态转为同步态的过程。

4、观察识别器假识别现象及同步保护器的保护作用。

上步中同步器转为同步状态后,使信源单元的K2或K3中出现1110010状态(与1110010状态有一位不同的状态也可),示波器CH1接NRZ-OUT,CH2分别接GAL和FS,观察识别器假识别现象,理解同步保护电路的保护作用。

五、实验报告要求

1. 根据实验结果,画出同步器处于同步状态及失步状态时同步器各点波形。

2. 本实验中同步器由同步态转为捕捉态时÷24信号相位为什么不变?

3. 同步保护电路是如何使假识别信号不形成假同步信号的?

4. 试设计一个后方保护电路,使识别器连续两帧有信号输出且这两个识别脉冲的时间间隔为一帧时,同步器由失步态转为同步态。

电子发烧友App

电子发烧友App

评论