数据采集中毛刺的处理方法

2012年11月13日 15:56 来源:本站整理 作者:灰色天空 我要评论(0)

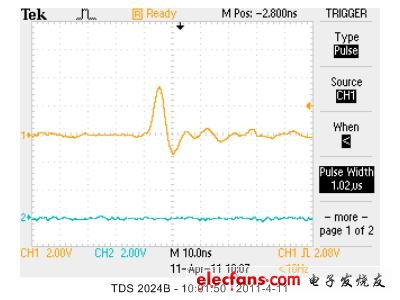

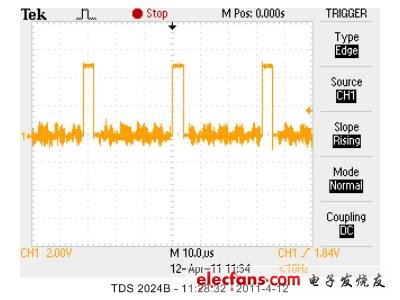

在采集一组并行接口信号时,发现接收到的数据非常不稳定。用示波器测量几个用于同步的控制信号,发现时不时的有毛刺产生。因为这些数据最终都是要显示在液晶屏上的,当示波器同时测量两个同步信号时,液晶屏的显示错位现象得到明显好转。示波器探头测量信号时相当于并联上一个pF级的电容,也能够一定程度上起到滤波的效果,因此可以断定同步信号的毛刺影响了数据的采集。其中一个同步信号如图1,两个有效高脉冲之间有很多毛刺,放大毛刺后如图2所示,大约维持10ns的高电平。

图1

图2

如何滤除这些毛刺呢?办法有两个,其一就是用纯粹硬件的办法,在信号进入FPGA之前进行滤波处理,串个电阻并个电容都可以,特权同学并了一个20pF电容后就能够把这些毛刺彻底滤干净,如图3所示。

图3

而还有一种“软”硬件滤波的方法。就如特权同学收录进<深入浅出玩转FPGA>一书中的博文<基于FPGA的跨时钟域信号处理——亚稳态>所谈到的,降低数据采集频率以及多次采集后逻辑处理都是一种思路。那这里特权同学给出一种多次采集处理的滤波方法和大家分享。

input ain; //输入信号

reg[3:0] ainr; //输入信号缓存

//输入信号打4拍

always @(posedge clk or negedge rst_n)

if(!rst_n) ainr <= 4‘d0;

else ainr <= {ainr[2:0],ain};

//输入信号上升沿检测,高电平有效

wire pos_ain = ~ainr[3] & ~ainr[2] & ainr[1] & ainr[0];

//通常只要两个信号就行,即wire pos_ain = ~ainr[2] & ainr[1] ;。

//这里用了4个信号就是多次采样滤波的效果

//输入信号下降沿检测,高电平有效

wire neg_ain = ainr[3] & ainr[2] & ~ainr[1] & ~ainr[0];

//通常只要两个信号就行,即wire neg_ain = ainr[2] & ~ainr[1] ;。

//这里用了4个信号就是多次采样滤波的效果

//若该输入信号主要关注其高脉冲,那么可以做以下滤波

wire high_ain = ainr[1] & ainr[0];

//两个信号相与通常可以滤除1个clk的毛刺,相应的,3个信号相与可以滤除2个clk的毛刺

//若该输入信号主要关注其低脉冲,那么可以做以下滤波

wire low_ain = ainr[1] | ainr[0];

上周热点文章排行榜

上周资料下载排行榜

创新实用技术专题

大家谈:华为能否撬开美国市场?

热评

- LM3S9B96开发板手册及原理图

- NI推出Single-Board RIO嵌入式介面

- STM32F103ZET6红牛电路图

- 高通发布全新设计DragonBoard板

- 3.15投诉:揭开天翼3G手机的“欺骗”

- 小米手机2工程机月底将上市

- 新款 Apple TV 将在3月8日出货

- protel99se正式汉化版免费下载

- matlab 7.0软件下载(免费破解版)

- hi3515海思原版原理图

博文

- 新学习单片机,决心转型技术宅

- 白岩松:青春该怎么过?不计后果的过

- 破解大学寝室的智能限电

- 关于学电子的女生那点事

- 当你累了,准备放弃时,看看这个吧!!!

- 十个学嵌入式的禁忌

- 电子信息专业到底该做些什么

- 大学那点事儿第二波:文科女生PK理科女生

- 菜鸟STM32初次制版

- iPhone5数据线芯片IC

用户评论

查看全部 条评论

查看全部 条评论>>