接口/时钟/PLL

电子发烧友网接口/时钟/PLL栏目提供pll锁相环,锁相环,锁相环电路,锁相环原理,数字锁相环等接口/时钟/PLL设计所需的所有最新行业新闻、产品信息及技术热点方案及介绍。详解配置控制器局域网络(CAN)位时序实现系统性能优化

隔离有利于提高鲁棒性,但同时也会增加发射和接收两个方向的传播延迟。必须使该延迟增加一倍,以支持两个节点参与仲裁。如果系统允许的传播延迟是固定的,在增加隔离措施之后,可以减...

2024-11-15 201

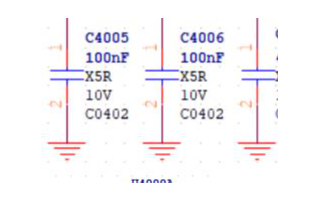

eMMC模块电路的PCB设计建议

eMMC电路简介 eMMC(Embedded Multi Media Card)是MMC协会订立、主要针对手机或平板电脑等产品的内嵌式存储器标准规格。 eMMC在封装中集成了一个控制器,提供标准接口并管理闪存。原理电路8位数据...

2023-08-17 44681

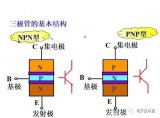

三极管开关电路驱动电阻如何选择

当三极管基极偏置电压小于PN结的导通电压,基极电流Ib=0时,集电极Ic和发射极Ie没电流(或只有微弱的弱电电流)通过,此时三极管失去了电流放大作用,我们称三极管工作在截止状态,...

2023-08-10 791

mcu需要考虑噪声的问题吗?如何降低微控制器系统中的噪声影响(2)

本篇我们将看看我们可能遇到的一些典型的噪声源。这些来源既可以是我们系统的外部,也可以是内部的。 外部噪声源 通常是系统可靠运行的最大威胁之一,我们必须在环境中管理许多噪声源...

2023-08-07 1159

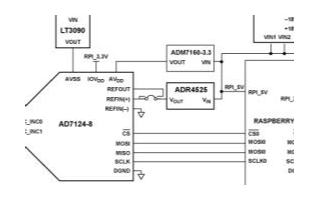

如何为逐次逼近型ADC设计可靠的数字接口?

逐次逼近型模数转换器(因其逐次逼近型寄存器而称为SAR ADC)广泛运用于要求最高18 位分辨率和最高5 MSPS 速率的应用中。其优势包括尺寸小、功耗低、无流水线延迟和易用。 主机处理器可以通...

2023-07-20 1209

模拟电子技术基础知识总结 模电经典电路与电路原理基础知识

01基尔霍夫定理的内容是什么? 基尔霍夫电流定律:在电路任一节点,流入、流出该节点电流的代数和为零。 基尔霍夫电压定律:在电路中的任一闭合电路,电压的代数和为零。 02戴维南...

2023-06-08 4732

TVS防护电路的典型应用

TVS(Transient Voltage Suppression)是一种限压保护器件,作用与压敏电阻很类似。也是利用器件的非线性特性将过电压钳位到一个较低的电压值实现对后级电路的保护。TVS管的主要参数有:反向击穿电...

2023-03-07 1801

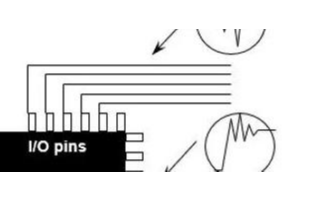

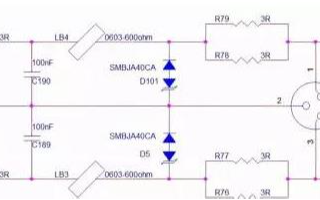

灵活的多通道混合信号模拟I/O电路构建指南

虽然世界继续更加数字化,计算能力和数字功能愈发关键,但测量环境和与实际器件交互的需求仍然是一种模拟功能。为了在数字和模拟域的边界运行,处理器必须包括混合信号输入/输出,并...

2023-02-18 1683

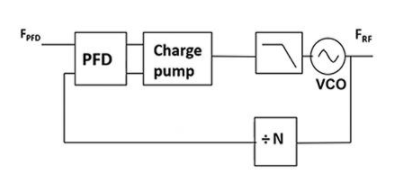

模拟锁相环和数字锁相环区别

模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精...

2023-02-15 4901

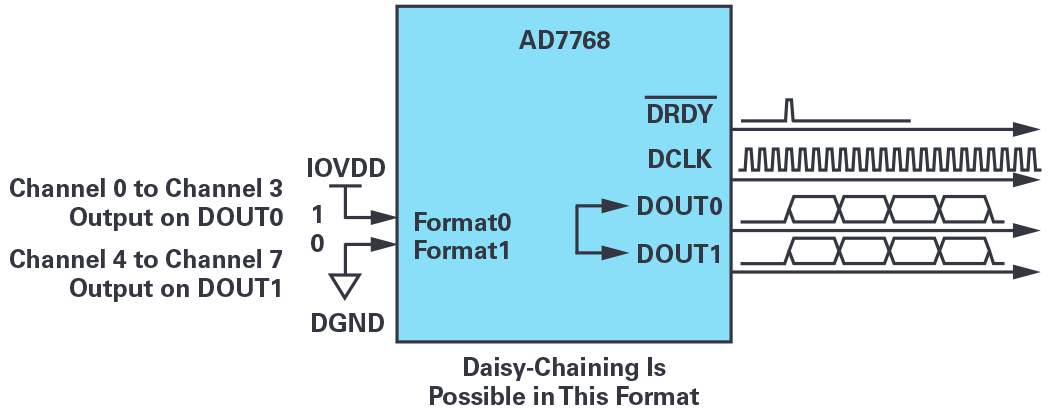

操纵MCU SPI接口以访问非标准SPI ADC

目前许多精密模数转换器 (ADC) 具有串行外设接口 (SPI) 或一些串行接口,用于与微控制器单元 (MCU)、DSP 或 FPGA 等控制器通信。控制器写入或读取ADC内部寄存器并读取转换代码。SPI因其简...

2023-02-15 4221

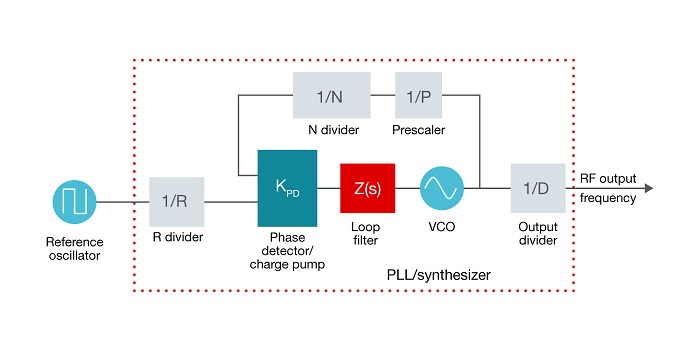

pll是什么意思_pll锁相环参数

PLL是指锁相环,是一种用于控制频率和相位的电路,它可以将一个输入信号的频率和相位转换成另一个输出信号的频率和相位,从而实现频率和相位的控制。...

2023-02-14 10364

pll锁相环版图设计注意

PLL锁相环版图设计时应注意以下几点:1)确定PLL的频率范围;2)确定PLL的控制电路;3)确定PLL的调节电路;4)确定PLL的输出电路;5)确定PLL的滤波电路;6)确定PLL的控制参数;7)确定PLL的...

2023-02-14 3234

几款常用的保护电路

鉴于电源电路存在一些不稳定因素,而设计用来防止此类不稳定因素影响电路效果的回路称作保护电路。在各类电子产品中,保护电路比比皆是,例如:过流保护、过压保护、过热保护、空载...

2023-02-11 1495

对比机电继电器 干簧管有哪些优势

磁簧开关(Reed Switch)也称之为干簧管,它是一个通过所施加的磁场操作的电开关。磁簧开关是由两片磁簧片(通常由铁和镍这两种金属所组成的) 密封在玻璃管内。 两片磁簧片呈重迭状况但中间...

2023-02-06 626

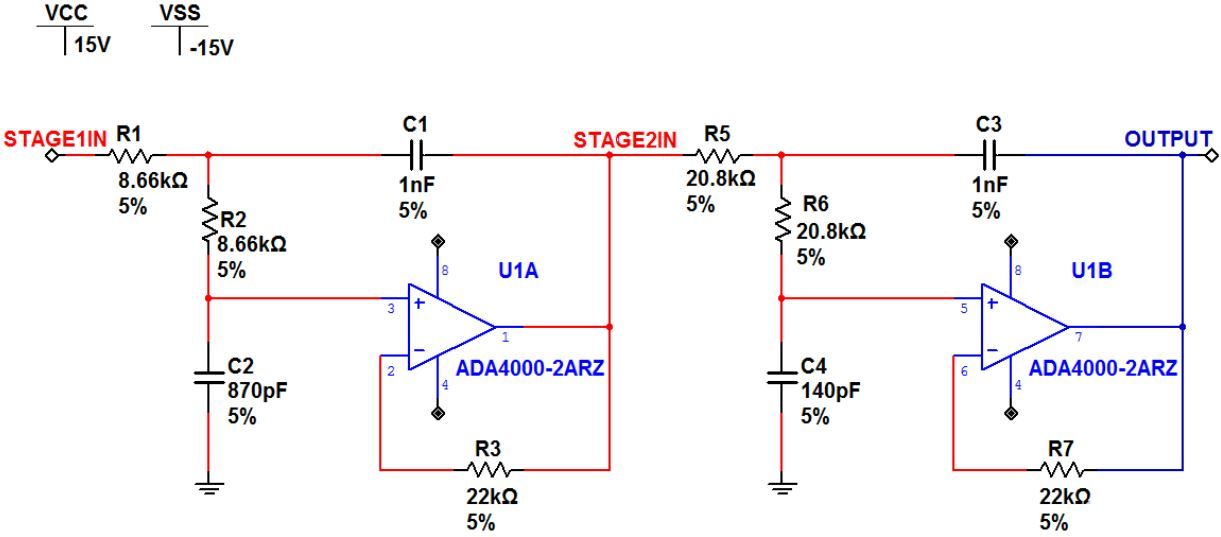

如何加快和改进滤波器设计的解决方法

许多半导体制造商提供工具,以帮助在初始规格阶段设计稳健的系统模块。例如,ADI公司(ADI)提供在线滤波器设计工具(参见参考文献1),可指导用户完成有源滤波器合成过程,并根据这些...

2023-01-29 2232

FPGA物理约束-网表约束CLOCK_DEDICATED_ROUTE

Vivado工具在编译时通常会自动识别设计中的时钟网络,并将其分配到专用的时钟布局布线资源中。...

2022-10-24 1815

jitter的关键术语和参数

时钟电路是芯片中最基础的电路,时钟电路性能的好坏关乎SoC中所有电路能否达到预期目标,例如:计算核(CPU/GPU/NPU)的主频,DDR的带宽,高速接口(PCIE)的带宽等。...

2022-10-12 6571

经典模拟电路有哪些类型?常见的模拟电路有哪些?

电子工程师大多平时需要和不同的电路接触,有些经典电路需要熟记,清楚这些电路图的作用,在工作中才能融会贯通。 电路一、差分放大电路 注意要点: 1、差分放大电路具有电路对称性...

2022-08-30 2568

SPI接口说明及原理

最基本的SPI通信就是一主一从,比如:一个STM32作为主机,一个W25Q16(SPI Flash)作为从机。还有两个MCU之间进行SPI通信等。...

2022-08-13 2833

如何从时序分析中排除跨时钟域路径?

要从时序分析删除一组路径,如果您确定这些路径不会影响时序性能(False 路径),可用FROM-TO 约束以及时序忽略 (TIG) 关键字。...

2022-08-02 911

传统 PLL 与平移环系统级封装技术

低噪声平移环的设计涉及众多电路块的实现,导致设计复杂,通常体积庞大,灵活性有限。此外,整个电路必须针对目标操作进行验证和特征化。...

2022-07-28 1076

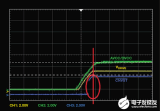

如何降低地弹噪声对单板信号完整性影响

本文结合某单板(下文中统一称M单板)FPGA调试过程中发现地弹噪声造成某重要时钟信号劣化从而导致单板业务丢包的故障,来谈下如何最大程度地降低地弹噪声对单板信号完整性影响。...

2022-07-27 817

带有时钟使能和同步清零的D触发器

每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。...

2022-07-22 3755

i.MXRT1170 的时钟架构

目前 i.MXRT1xxx 系列主要分为 i.MX RT10xx 和 i.MXRT11xx 两大分支。这两个分支的时钟系统设计是有一些差异的,不过总体来说,架构差别不大,我们以如下 i.MXRT1170 的时钟架构为例来具体介绍。...

2022-07-08 1009

PS和PL之间连接的技术

上面两种均采用内存映射控制方式,即 ARM 将用户自定义 IP 编入某一地址进行访问,读写时就像在读写自己的片内 RAM,编程也很方便,开发难度较低。代价就是资源占用过多,需要额外的读地...

2022-07-07 3617

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |