1 引言

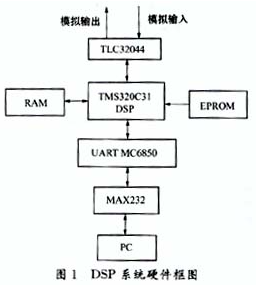

美国德州仪器公司(TI)的TMS320VC54XX系列DSP芯片与PC机实现异步通信通常有两种方法:第一种是使用通用I/O信号XF和BIO作为串口发送和接收信号,用软件逐位发送和接收数据,即软件异步通信方法,这种方法需要占用很多CPU时间,因此,只能在DSP不太忙、实时性要求不高的情况下采用;第二种是通过扩展异步通信芯片来实现高速串行通信,本文选用的就是此方法。

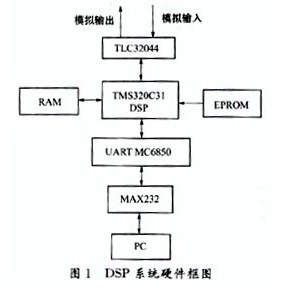

在笔者设计数字调幅广播系统中的基带处理子系统时,复用器与信道编码器之间的通信采用的是异步串行通讯方案。复用器则使用通用PC机来实现,信道编码器使用TI公司生产的DSP芯片TMS320VC5421来设计实现。

2 UART芯片TL16C752B简介[1]

2.1 主要特点

TL16C752B是TI公司推出的新型UART(Universal Asynchronous Receiver and Transmitter )收发器。该器件的主要特点如下:

●引脚和ST16C2550兼容,内置两套UART系统,可独立工作;

●工作时,最高波特率可以达到1.5Mbps(使用24MHz晶体时)或3Mbps(使用48MHz振荡器或时钟源时);

●具有64字节发送/接收FIFO(接收FIFO包含错误标志)。由于收、发FIFO的触发等级可通过软件编程实现,因而减少了CPU的中断次数;

●接收FIFO的启动和停止等级可以通过软件编程来实现;

●具有两种控制模式:其中软件流控制模式可通过编程Xon/Xoff字符来实现;而硬件流控制模式则可通过设置RTS和CTS引脚及相应的寄存器来实现;

●波特率可编程;

●可编程下列串行数据格式:

——5、6、7、8 四种字符;

——数据奇偶校验或者无校验;

——1、1.5、2bits 停止位;

●内部闭环。

2.2 TL16C752B的引脚功能

TL16C752B内含双UART,并自带64字节收发FIFO,可自动进行软件流和硬件流控制,最大波特率可达3Mbps。此外,TL16C752B还提供了其它一些增强功能,可通过设定EFR寄存器的相关位来实现。通过FIFO RDY 寄存器可读取TXRDY/RXRDY引脚的状态;而通过片内寄存器则可为使用者提供接收数据的错误识别、操作状态以及MODEM的接口控制信号。

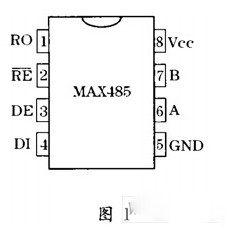

TL16C752B的引脚排列如图1所示,各主要引脚的功能如下:

A0~A2:地址线,通过这几个引脚以及读写信号IOR和IOW可以访问及设定片内寄存器?

D0~D7:双向8位数据线?

CSA、CSB:两套UART的片选信号?

TXA/RXA、TXB/RXB:分别表示所要发送和接收的数据端口?

INTA/INTB:中断信号?

RESET:芯片复位信号?

XIN/XOUT:时钟输入/输出信号。

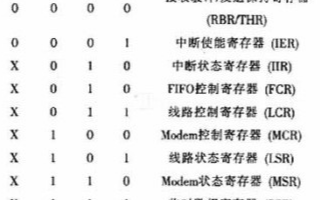

2.3 TL16C752B的内部寄存器

图2所示是TL16C752B的内部功能模块图,该器件内部共有20个寄存器,这些寄存器可分别用于实现通信参数的设置、对线路及MODEM状态的访问、数据的发送和接收以及中断管理等功能。其地址可分别通过A0~A2地址线和某些寄存器的特定位来确定,由于有些寄存器的地址是重叠的,所以还必须通过读/写信号加以区分。TL16C752B内部寄存器的映射如表1所列。表中:

“*” 表示仅当LCR的第7位为1时,访问DLL/DLH。

“** ”表示仅当LCR为0xBF时,访问EFR以及Xon1/2,Xoff1/2。

“+” 表示当EFR[4]为1,且MCR[6]为1时,访问TCR/TLR。

“++”表示当片选信号有效、MCR[2]为1且处于非闭环模式时,访问 FIFO RDY。

此外,对于MCR[7],只有当EFR[4]为1时才可以更改。在上述说明中,[]表示该寄存器的第几位。

表1 TL16C752B的内部寄存器映射表

| A[2] | A[1] | A[0] | 读 模 式 | 写 模 式 |

| 0 | 0 | 0 | 接收保持寄存器(RHR) | 发送保持寄存器(THR) |

| 0 | 0 | 1 | 中断使能寄存器(IER) | IER |

| 0 | 1 | 0 | 中断标示寄存器(IIR) | FIFO控制寄存器(FCR) |

| 0 | 1 | 1 | 线路控制寄存器(LCR) | LCR |

| 1 | 0 | 0 | MODEM控制寄存器(MCR) | MCR |

| 1 | 0 | 1 | 线路状态寄存器(LSR) | LSR |

| 1 | 1 | 0 | MODEM状态寄存器(MSR) | MSR |

| 1 | 1 | 1 | 临时寄存器(SPR) | SPR |

| 0 | 0 | 0 | *除数锁存低位(DLL) | DLL |

| 0 | 0 | 1 | *除数锁存高位(DLH) | DLH |

| 0 | 1 | 0 | **增强功能寄存器(EFR) | EFR |

| 1 | 0 | 0 | ** Xon-1字符值 | Xon-1字符值 |

| 1 | 0 | 1 | ** Xon-2字符值 | Xon-2字符值 |

| 1 | 1 | 0 | ** Xoff-1字符值 | Xoff-1字符值 |

| 1 | 1 | 1 | ** Xoff-2字符值 | Xoff-2字符值 |

| 1 | 1 | 1 | +传输控制寄存器(TCR) | TCR |

| 1 | 1 | 0 | +触发等级寄存器(TLR) | TLR |

| 1 | 1 | 1 | ++FOFO状态寄存器(FIFO RDY) | FIFO RDY |

2.4 TL16C752B工作流控制模式

TL16C752B有2种工作流控制模式:硬件流控制和软件流控制。使用前者可降低软件消耗,通过RTS和CTS引脚信号的硬件连接可自动控制串行数据流,从而提高系统的有效性;后者则通过使用可编程的Xon/Xoff字符来自动控制数据传输。本文主要介绍软件流控制模式。

软件流控制模式的使能可通过EFR和MCR这2个寄存器来实现。不同流模式的组合如表2所列(可通过设定EFR的低4位实现)。

表2 软件流控制模式

| EFR[3] | EFR[2] | EFR[1] | EFR[0] |

TX RX软件流控制组合模式 |

| 0 | 0 | X | X | 无发送流控制 |

| 1 | 0 | X | X | 发送Xon1,Xoff1 |

| 0 | 1 | X | X | 发送Xon2,Xoff2 |

| 1 | 1 | X | X | 发送Xon1,Xoff1;Xon2,Xoff2 |

| X | X | 0 | 0 | 无接收流控制 |

| X | X | 1 | 0 | 接收器比较Xon1,Xoff1 |

| X | X | 0 | 1 | 接收器比较Xon2,Xoff2 |

| 1 | 0 | 1 | 1 | 发送Xon1,Xoff1;接收器比较Xon1,Xoff1;Xon2,Xoff2 |

| 0 | 1 | 1 | 1 | 发送Xon2,X0ff2;接收器比较Xon1,Xoff1;Xon2,Xoff2 |

| 1 | 1 | 1 | 1 | 发送Xon1,Xoff1;Xon2,Xoff2;接收器比较Xon1,Xoff1;Xon2,Xoff2 |

| 0 | 0 | 1 | 1 | 无发送流控制;接收器比较Xon1,Xoff1;Xon2,Xoff2 |

具体工作流程(从接收的角度)为:接收时,若操作达到接收中断等级,则产生中断,但这时传输还在进行(这里假设中断有一定延时);而当RHR中的数据数目达到接收停止等级规定的数值时,接收端发送Xoff1/2,以通知发送端停止发送数据,这时接收端将读取RHR中的数据。当RHR中的数据数目降到接收启动等级规定的数值时,接收端发送Xon1/2,以通知发送端可以继续发送数据。

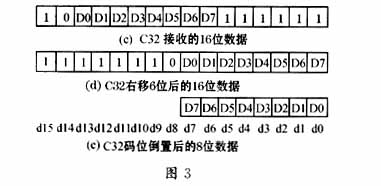

3 TL16C752B与PC的通信电路

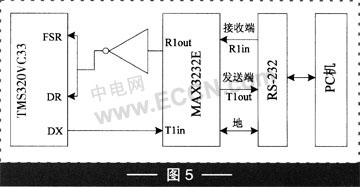

TL16C752B与PC的串行通信部分的硬件连接电路如图3所示。图中,地址线A0~A2、数据线D0~D7分别和DSP的地址总线A0~A2、外部数据线D0~D7直接相连,而选通信号CSA/CSB、读写信号IOR/IOW、复位信号RESET以及中断信号INTA/B则接入CPLD并由CPLD处理。同时DSP端的PS、DS、IS、IOSTRB、R/ W、MSTRB也同时接入CPLD以用于生成控制信号。电路中使用CPLD一方面可以对UART的地址灵活配置,另一方面也可以灵活生成UART的复位、选通和读写信号,从而增强系统的灵活性,方便系统调试。

由于PC端串口采用RS232电平标准,因此UART之后需要连接MAX3221以完成电平转换。TL16C752B的数据发送引脚和数据接收引脚分别与MAX3221的数据输入引脚和数据输出引脚连接。这里只使用一套UART来完成TL16C752B和PC的通信。数据收、发采用中断方式,UART_INTA通过CPLD和TMS320VC5421的外部中断INT0相连接。而3.072MHz晶振则连接到XIN和XOUT两引脚。波特率设定为38400,故DLL/DLH分别为06和00h。

具体调试时,可先从查询方式开始,若没有问题,再使用中断方式。

图3

4 TL16C752B和PC通信的软件编程

该系统的软件设计部分主要包括PC机程序、DSP初始化、TL16C752B初始化和数据发送/接收以及双方的通信协议等。下面介绍TL16C752B的初始化程序。

TL16C752B初始化程序主要包括以下几部分:

(1)波特率的设定;

(2)增强功能的使能及设置EFR的相关位;

(3)完成有关收、发FIFO的设定,主要是MCR/TCR/TLR 3个寄存器的设置;

(4)软件流控制模式使能以及Xon/Xoff字符的设置;

(5)传输数据格式设定,包括8位数据位、2位停止位、DMA传输模式1、偶校验、不使用强制校验模式、暂停控制位无效等;

(6)设置FIFO控制以及中断控制寄存器。

此外,在完成设置前,还应注意以下几点:

(1) 设定DLL和DLH前,LCR[7]应为1。

(2) 设定MCR前,EFR[4]应为1,LCR应为00h。地址相重叠的寄存器不能同时使能。

(3) 读写RHR和THR时,由于DSP的读写速度很快,故最好不要连续读写,而是在每读、写一次后延时一段时间,然后再进行下一次读写。

(4) 这里,DMA只是一个名称,而并非是 “直接存储器访问”。

TL16C752B的地址分配在I/O空间的0020h~0027h,读写通过PORTR和PORTW指令完成。TL16C752B初始化程序如下:

ini_uart_start:

;设置 baud rate=38400 ; divi-sor=0006h

stm #temp1_reg,ar1

nop

st #80h;*ar1 ;除数锁存使能 LCR=bfh

portw *ar1,#k_LCR_addr

st #k_DLL_value,*ar1

portw *ar1,#k_DLL_addr

st #k_DLH_value,*ar1

portw *ar1,#k_DLH_addr

;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

st #k_LCR_value?*ar1 ;LCR=bfh

portw *ar1,#k_LCR_addr

st #k1 EFR value?*ar1 ;增强功能使能

portw *ar1,#k_EFR_addr

st #0,*ar1 ;设定LCR= 0

portw *ar1?#k LCR addr

st #k_FCR_value,*ar1 ;设定FIFO控制寄存器

portw *ar1,#k_FCR_addr

st #k_MCR_value,*ar1 ;设定MCR/TCR/TLR寄存器

portw *ar1,#k_MCR_addr

st #k_TCR_value,*ar1

portw *ar1,#k_TCR_addr

st #k_TLR_value,*ar1

portw *ar1,#k_TLR_addr

st #k1_MCR_value,*ar1

portw *ar1,#k_MCR_addr

st #k_LCR_value,*ar1 ;为访问Xon/Xoff/EFR,LCR重设定为BFh

portw *ar1,#k_LCR_addr

st #k_Xoff1_value,*ar1 ;设置软件流控制

portw *ar1,#k_Xoff1_addr

st #k_Xon1_value,*ar1

portw *ar1,#k_Xon1_addr

st #k_Xoff2_value,*ar1

portw *ar1,#k_Xoff2_addr

st #k_Xon2_value,*ar1

portw *ar1,#k_Xon2_addr

st #k_EFR_value,*ar1 ;设置软件流控制组合方式

portw *ar1,#k_EFR_addr

st #k_LCR_dlatch_disable,*ar1

portw *ar1,#k_LCR_addr ;设定传输数据格式

st #k_IER_value,*ar1 ;设置中断

portw *ar1,#k_IER_addr

5 结束语

通过扩展串口完成TMS320VC5421与PC机串行通信硬件接口比较简单、数据传送距离远、使用经济。该电路及其软件经与微机的通信实验证明,在波特率为38400时,能够可靠地实现与PC机的通信。

电子发烧友App

电子发烧友App

评论