特权同学为大家介绍市面上最常见的Xilinx spartan-3的xc3s400的配置电路...

2013-05-31 14:07:33 3814

3814

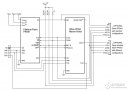

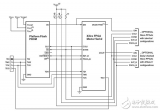

这里要列出一个市面上最常见的spartan-3的xc3s400的配置电路,所有spartan-3的FPGA配置电路的链接方式都是一样的。

2015-02-04 09:47:57 3259

3259

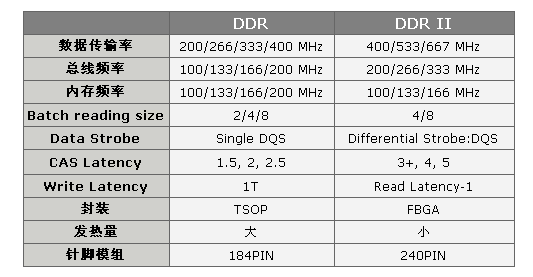

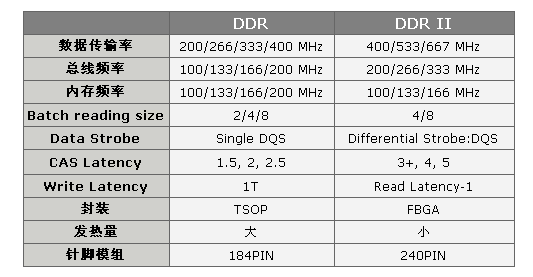

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2871

2871

DDR2 DDR3 dimm接口封装文件,金手指接口

2017-12-03 22:22:02

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

一般的FPGA的数据传输接送接口不都是用USB的么,我想用蓝牙无线的接口,想买响应的蓝牙模块,有没有能和Spartan-3 FPGA 系列 相匹配的蓝牙模块呢?

2019-08-14 16:33:55

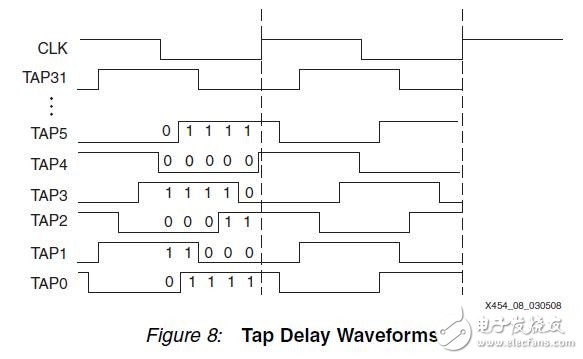

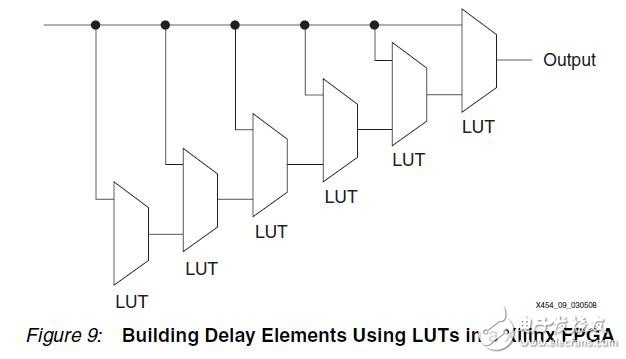

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA I/O结构中没有包含均衡功能,那么它与DDR3

2019-04-22 07:00:08

:图2:Spartan-7 FPGA同一bank连接1.8V SPI Flash和1.35V DDR3L虽然这不是一个标准的解决方案,只是限于有限的I/O资源,但是对于小型系统设计不失为一种好的方法。具体设计细节如器件选型、原理图、确定时钟频率等要求请参看官方文档`

2018-08-02 09:37:08

大家好!我有一个问题。我已经阅读了应用笔记XAPP486:7:1 Spartan-3E FPGA中的串行化速度高达666 Mbps和XAPP485:1:7 Spartan-3E FPGA中的串行化

2018-09-28 11:41:22

约束文件(XDC文件),它包含用于时序分析的“create_clock”和“set_input_jitter”约束。在ISE 14.7和Spartan-3 FPGA中,我可以使用称为“时钟向导”的IP来

2019-08-02 09:54:40

本帖最后由 lpc2292 于 2013-2-27 20:24 编辑

“部分 I: 用 Spartan-3 系列 FPGA 进行设计”第 1 章 “概述”第 2 章 “使用全局时钟资源”第 3

2013-02-27 20:20:10

与IP引脚接口时是否应该考虑特殊注意事项?或者将DDR SDRAM连接到Spartan 3E的具体要求是什么?到目前为止我的考虑: -Bank#需要具有相同的逻辑电平 - 需要考虑高速布局 - >

2019-05-10 13:59:37

求一DDR2接口设计代码

2013-04-24 10:00:36

大家好,什么是spartan 3a入门套件板中DDR2内存芯片的工作频率?谢谢,randeel。

2019-08-22 09:18:39

、DDR2、DDR3型SDRAM存储器,DDR系列的存储器都需要FPGA芯片有对应的硬件电路结构支持。对于Altera Cyclone IV系列的FPGA,其最高支持到DDR2存储器(不支持DDR3存储器

2016-12-30 20:05:09

1、从工作平率上说:首先接口就全部不同 电压不同 频率的计算方法不同 SDR的频率就是外频 133=133 DDR的频率就是外频的2倍 133=266 DDR2的频率就是外频的4倍 133=533

2014-12-30 14:35:58

1、从工作平率上说:首先接口就全部不同 电压不同 频率的计算方法不同 SDR的频率就是外频 133=133 DDR的频率就是外频的2倍 133=266 DDR2的频率就是外频的4倍 133=533

2014-12-30 14:36:44

你好,有谁知道为什么Spartan-3E系列不支持DDR2接口?至少就MIG而言。问候,亚历克斯以上来自于谷歌翻译以下为原文Hello, does anyone know why DDR2

2019-05-09 14:23:32

为什么利用Spartan-3 FPGA来实现DSP系统?Spartan-3系列器件在平板显示器中的应用有哪些?

2021-04-29 06:32:17

为什么利用Spartan-3 FPGA来实现DSP系统?Spartan-3系列器件在平板显示器中的应用有哪些?

2021-04-30 07:12:22

这里要谈的是Xilinx的spartan-3系列FPGA的配置电路。当然了,其它系列的FPGA配置电路都是大同小异的,读者可以类推,重点参考官方提供的datasheet,毕竟那才是最权威的资料。

2019-10-10 06:16:52

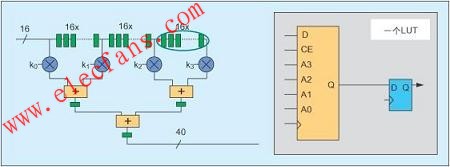

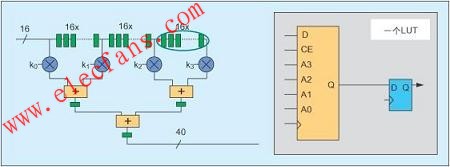

本文阐述了Spartan-3 FPGA针对DSP而优化的特性,并通过实现示例分析了它们在性能和成本上的优势。

2019-10-18 07:11:35

、DDR2与DDR3内存的特性区别: 1、逻辑Bank数量 DDR2 SDRAM中有4Bank和8Bank的设计,目的就是为了应对未来大容量芯片的需求。而DDR3很可能将从2Gb容量起步,因此起始

2011-12-13 11:29:47

`例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 如图

2016-10-27 16:36:58

最近在设计一个需要连接DDR2 SDRAM的FPGA小系统,由于是第一次在使用SDRAM,在硬件连接时就遇到一个很纠结的问题——引脚的连接。看了几种参考设计,发现有两种说法:1、DDR2的数据(DQ

2017-09-25 17:51:50

以前的一个DDR2接口设计,在原板上运行正常,现在重做了一块板子,换了一款FPGA芯片,重新编译后,无法初始化DDR2。IP重新例化了,但是不知到怎么运行TCL文件,运行哪个文件?有高手给指点一下,或者有相关教程,或书籍推荐也可以。先谢谢啦!

2013-12-10 20:38:10

我已经完成了几次搜索,并且无法找到一个文档,告诉我在Spartan-6上可以使用哪些引脚用于DDR2接口。我确实理解引脚交换等,但有些引脚不能用于DDR2。我正在寻找的是以下具体内容......1

2019-01-24 10:22:29

嗨,我想为Spartan3 XC3S4000 FG900设计板,之后我为Spartan-6设计了一块板。在针对Spartan-6的Xilinx文档中,我找到了“Spartan-6 FPGA电源管理

2019-07-17 09:16:04

选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足

2019-06-24 06:07:53

Xilinx公司发布的SP6,V6系列的FPGA中的DDR2的IP核是一大改变。它由原来的软核变为了硬核,此举让开发DDR2变的简单,因为不需要太多的时序调试,当然也带来了麻烦,这是因为当DDR2

2015-03-16 20:21:26

特性。 Spartan-3 FPGA的面世改变了嵌入式DSP的应用前景。虽然Spartan-3系列器件的价位可能较低,但它们同样具有DSP设计所需的平台特性。这些平台特性能够以较高的面积利用率实现信号

2019-06-27 06:12:26

Cyclone III系列型号为EP3C16F484C6N的FPGA作为控制器,以Micron公司生产的型号为MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM为存储器。用一个IP核完成

2011-05-03 11:31:09

基于Xilinx FPGA的DDR2 SDRAM存储器接口

2012-08-20 18:55:15

均衡的定义和重要性是什么如何实现FPGA和DDR3 SDRAM DIMM条的接口设计?

2021-05-07 06:21:53

嗨!我正在寻找Spartan-3A / 3ANFPGA入门KitBoard用户指南(UG334)。具体来说第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因为例如这个内存

2019-07-31 06:18:10

Spartan-3 FPGA系列如何仅通过在接收器数据通路中加入一个倒相器即可避免大量使用过孔?如何利用Spartan-3 FPGA进行LVDS信号倒相设计?

2021-05-06 07:30:25

亲爱的大家! 如何在IOB中为spartan-3生成FPGA使用TFF(TFF1和TFF2三态触发器)? 我想在spartan-3 FPGA(Spartan-3 GenerationFPGA用户指南

2019-06-28 09:53:28

你好我正在使用atlys主板,我必须在spartan-6上实现ddr2(MT47H64M16-25E)接口,...通过使用MIG及其示例设计,在模拟中一切正常....通过注意ddr2接口,例如

2019-10-28 07:46:43

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些

2019-08-09 07:42:01

本文介绍了采用Xilinx公司的Spartan-3 FPGA实现通用视频采集系统的设计方案。

2021-06-08 06:34:30

我正在使用spartan6 MCB与DDR2建立接口。我是VHDL的新手。在我预先编写的示例设计数据和地址中,我想修改设计以给出用户定义的数据和地址,并且想要添加三个控制信号wr,rd

2020-03-25 07:31:23

嗨,我即将使用Virtex-4QV设备(XQR4VFX140)开始一个新项目。虽然我对使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些经验,但我发现MIG IP不支持VIRTEX-4QV器件。那可能是另类?如何将DDR2 SDRAM与此FPGA连接?弥敦道

2020-04-02 06:08:46

DDR2控制和FPGA实现

2015-07-21 19:28:14

DDR,DDR2,DDR3,DDR4,LPDDR区别文所有权归作者Aircity所有1什么是DDRDDR是Double Data Rate的缩写,即“双比特翻转”。DDR是一种技术,中国大陆工程师

2021-09-14 09:04:30

SDRAM的时钟CLK可以差不多,但是DDR2的DQS速度可以达到DDR的两倍,这也就是它们的DQ/DQS操作时序一样的情况下,数据吞吐量却倍增的原因。比对DDR与DDR2的接口,其实DDR2就多了一

2014-12-30 15:22:49

大家好,我开发了DDR2内存和高速ADC 500Mpbs(2 ADC)到Spartan6 LX25器件。我想知道银行分配的最佳选择,因为接口都是高速且需要时钟定时至关重要。根据MIG的推荐,DDR2

2019-07-12 06:30:06

如何测试ARM外接DDR2的正确连接? ARM具有DDR3接口而没有SDRAM接口,目前在调试过程中发现程序在DDR3中跑飞,不知道如何去查或者不知道怎么定位在那出现问题,敬请各位指教,不胜感激。

2020-06-17 06:20:38

的内存控制器的设计与应用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存储器接口设计.pdf一种采用FPGA设计的SDRAM控制器.pdf用Xilinx+FPGA实现DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

各位好!之前用DM368的开发板进行实验,目前需要根据自己公司的产品重新画电路板,由于开发板上的FLASH和DDR2 SDRAM过于老旧,需要对这两颗零件重新选型。我不太清楚在选择DDR2

2018-06-21 05:34:23

,所以4片DDR2以地址和控制线共用、数据线独立的方式进行管脚连接。图1 接口总框图EP3C16只有TOP和BOTTOM边的BANK支持200MHz DDR2接口(因为DDR2管脚的特殊要求,DQS

2019-05-31 05:00:05

DDR2 SDRAM控制器的设计与实现

本文介绍了&&," -&,+. 的基本特征!并给出了一种&&," -&,+. 控制器的设计方法!详述了其基本结构和设计思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 Spartan-3 Generation FPGAs应用资料

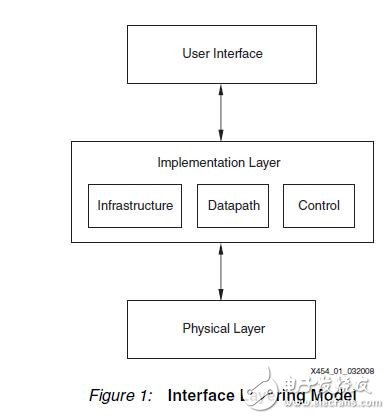

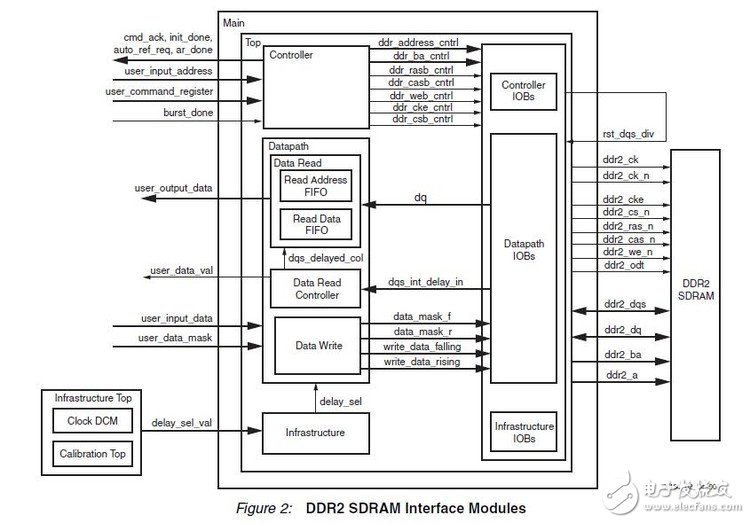

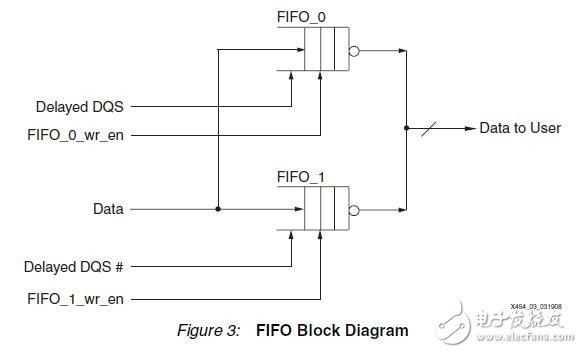

DDR2 SDRAM Interface for Spartan-3 Generation FPGA

2010-05-13 13:57:12 27

27 DDR2 SDRAM 和 FB-DIMM的电气检验:

随着DDR2 SDRAM时钟频率和信号边沿速率不断提高,检查电路板结构、电气系统和信令正变得越来越重要。本应用指南介绍了电路板、电源系统、

2010-08-06 08:29:01 39

39 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 在高速、大容量存储的系统设计中,DDR2 SDRAM为设计者提供了高性价比解决方案。在FPGA中实现DDR2 SDRAM控制器,降低了系统功耗并节省空间, 缩短开发周期,降低系统开发成本

2010-12-13 17:10:35 49

49 DDR2名词解释

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2009-04-26 18:02:22 1186

1186

什么是DDR2 SDRAM

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技

2009-12-17 11:17:59 623

623 DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不

2009-12-17 16:26:19 731

731 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2010-03-24 16:06:36 1381

1381 Spartan-3FPGA能以突破性的价位点实现嵌入式DSP功能。本文阐述了Spartan-3 FPGA针

2010-12-17 11:31:23 675

675

文中在介绍DDR2的工作原理的基础上,给出了一个用VHDL语言设计的DDR2 SDRAM控制器的方法,并且提出了一种在高速图像处理系统中DDR2 SDRAM的应用方案,同时在Virtex-5系列的FPGA上得到了实现

2011-07-23 10:03:16 5102

5102 文章对适用DDR2 SDRAM控制器的结构、接口和时序进行了深入研究与分析,总结出一些控制器的关键技术特性,然后采用了自顶向下(TOP-IX)WN)的设计方法,用Verilog硬件描述语言实现控制器,

2011-09-01 16:36:29 174

174 SDRAM, DDR, DDR2, DDR3 是RAM 技术发展的不同阶段, 对于嵌入式系统来说, SDRAM 常用在低端, 对速率要求不高的场合, 而在DDR/DDR2/DDR3 中,目前基本上已经以DDR2 为主导,相信不久DDR3 将全面取代

2012-01-16 14:53:01 0

0 使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存储控制器的用户接口设计与仿真,本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速

2013-01-10 14:12:45 2990

2990 ddr2_sdram 操作时序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 基于FPGA的VGA接口实现和字符显示论文

2015-10-29 17:18:24 8

8 用FPGA设计DDR2控制器讲解DDR2时序原理用户接口设计帮助用户快速掌握DDR2的控制技术新手上路的非常有帮助的资料。

2015-11-10 10:54:14 3

3 DDR2 SDRAM操作时序规范,中文版规范

2015-11-10 17:42:44 0

0 Xilinx FPGA工程例子源码:Xilinx DDR2存储器接口调试代码

2016-06-07 14:54:57 27

27 SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200 MT/s。

2017-11-17 13:15:49 25152

25152 提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作

2017-11-22 07:20:50 4687

4687

DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用时钟的上升/下降沿同时传输

2017-11-25 01:41:01 3855

3855

本演示介绍了 Spartan®-3A 入门套件如何让您立即获得 Spartan-3A FPGA 器件的节能模式,高速 I/O 选项,DDR2 SDRAM 存储器接口,商用闪存配置支持,以及利用 Device DNA 实现的 FPGA/IP 保护等特性。

2018-05-22 13:45:01 2484

2484 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序

2019-08-14 08:00:00 3401

3401

本用户指南为客户使用 Spartan™-3 FPGA 系列各平台 (Spartan-3、Spartan-3E、Spartan-3A、Spartan-3AN 和 Spartan-3A DSP FPGA

2020-03-05 08:00:00 16

16 DDR2 SDRAM采用双数据速率结构实现高速运行。双数据速率体系结构本质上是4n预取体系结构,其接口设计为在I/O球处每个时钟周期传输两个数据字。DDR2 SDRAM的单次读写操作有效地包括在内部

2020-05-21 08:00:00 1

1 Spartan-3 FPGA包括扩展的斯巴达-3A系列(斯巴达-3A、斯巴达-3AN和斯巴达-3A DSP平台),以及早期的斯巴达-3和斯巴达-3E系列。这些系列的现场可编程门阵列(FPGA)是专门

2021-01-23 08:00:00 21

21 ARM与FPGA的接口实现的解析(应广单片机)-该文档为ARM与FPGA的接口实现的解析详述资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-22 09:47:55 14

14 基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 基于FPGA的SDRAM串口实验(嵌入式开发板实验报告)-基于FPGA的SDRAM串口实验,verilog语言编写

2021-08-04 09:43:17 37

37

电子发烧友App

电子发烧友App

评论