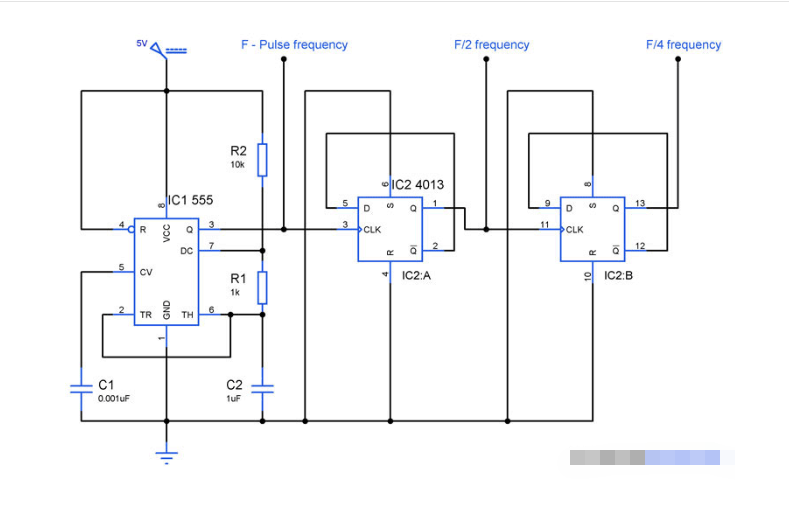

的OCC。像是拔牙操作一类的分频我们今天不讨论。今天讨论的任意分频器在许多的数字IC设计与FPGA面试笔试题中都有考察,所以在实(tou)现(xue)了以后做本次学习记录,供大家参考。1. 先入为主 我们来宏观的看本次分频器的内容,会比较容易理解。关键功能点的电路如图1所示:...

2022-02-09 07:34:15

毕设题目 :75mhz双路时钟缓冲器,求助

2021-02-27 21:45:00

本帖最后由 gk320830 于 2015-3-7 18:17 编辑

跪求 !!分频系数在一定范围内可调的分频器电路图》。。

2013-08-29 18:19:29

请问有哪种可编程分频器芯片啊?适合高频,几十兆到500兆。

2017-08-05 15:00:15

分频器EDA设计代码···仅供参考···

2013-12-09 12:26:46

1.65 GHz时钟扇出缓冲器,带输出分频器和延迟调整

2023-03-28 18:12:34

AKD8181D,AK8181时钟扇出缓冲器评估板。因此,很容易评估DC / AC特性并确认产品功能

2020-08-25 15:26:54

。

CANCLKCON(CAN时钟控制寄存器)中还有CANCLKDIV(CAN时钟分频器选择位),其范围为1 - 128。

据我所知,CANCLKDIV 什么也没做。我只使用普通的 CAN,而不是 CAN-FD

2024-01-22 06:36:03

分频器模块实现的基本原理就是设计一个工作在系统时钟下的计数器,循环地递减或者递加计数,在某个计数的固定值将输出翻转,即可实现时钟分频的功能。例如,实验板上的系统时钟是 50MHz,而所需的读写周期

2018-11-15 09:25:35

SY89871U,GB以太网交换机时钟分频器评估板。 SY89871U,可编程LVPECL时钟分频器评估板

2019-02-19 09:32:47

SY89873L,GB以太网交换机时钟分频器评估板。 SY89873L,可编程LVPECL时钟分频器评估板

2019-02-20 09:27:40

SY89874U,GB以太网交换机时钟分频器评估板。 SY89874U,可编程LVPECL时钟分频器评估板

2019-02-20 09:42:21

HMC905LP3E分频器产品介绍HMC905LP3E询价热线HMC905LP3E现货HMC905LP3E代理王先生 深圳市首质诚科技有限公司, HHMC905LP3E是一款SiGe BiCMOS

2018-10-17 15:49:04

NB6L239MNEVB / D,SONET时钟分频器评估板。 NB6L239是差分接收器到差分LVPECL时钟分频器。电路板功能输出启用输出控制

2019-02-20 09:29:49

NB7V32MMNGEVB,差分时钟分频器评估板。 NB7V32M是一个差分2分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-20 09:41:47

跪求大神相告,在protel99se中哪个库中有分频器

2014-06-24 16:08:41

“外设时钟”Pclk,而没有指定使用哪个 APBx 为每个 SPIx 提供时钟。也与上述相关:手册讨论了 SPI 时钟的预分频器,但是,CubeMX 不提供为 SPI2 设置预分频器的选项。看起来有些

2022-12-15 06:57:22

`请问什么是音频缓冲器?`

2019-08-23 16:27:28

会退出总线繁忙状态和失败。 出于好奇,我尝试将时钟频率配置为 400MHz 并使用分频器 2 来获得 200M 的值。 我想知道 RFDR 中的这个值表示什么以及谁负责更新? 如果我使用分频器值 3,则操作成功,RFDR[0] 值为 0x80,依此类推各种循环序列的变化。

2023-04-03 09:01:11

这种方式只消耗不多的逻辑单元就可以达到对时钟的操作目的。2、整数倍分频器的设计2.1 偶数倍分频 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频

2014-06-19 16:15:28

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

中从电子设计的外围器件逐渐演变为数字系统的核心。伴随着半导体工艺技术的进步,FPGA器件的设计技术取得了飞跃发展及突破。分频器通常用来对某个给定的时钟频率进行分频,以得到所需的时钟频率。在设计数

2019-10-08 10:08:10

Prescaler:定时器预分频器设置,时钟源经该预分频器才是定时器时钟,它设定 TIMx_PSC寄存器的值。可设置范围为 0 至 65535,实现 1 至 65536 分频

2021-08-19 06:47:20

基于特定的开发板上的时钟策略:倍频/分频系数需要在使能 PLL 之前进行配置,所以需要在 Open PLL 之前将所有系统的时钟分频器系数以及PLL的倍频系数配置好。整个时钟的配置流程如下所示:(1

2021-08-23 09:12:44

NB6L239MNEVB,工业用时钟分频器评估板。 NB6L239是差分接收器到差分LVDS时钟分频器。电路板功能输出启用输出控制

2019-02-20 06:26:41

NB7V33MMNGEVB,差分时钟分频器评估板。 NB7V33M是一个4分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-21 09:44:22

是否有评估板的外部(FPGA外部)时钟分频器而不是使用DCM或PLL?问候,半

2020-03-16 09:11:44

实现功能:能对12MHZ以上的方波信号进行分频另一疑问:占空比20%经过分频器分频后,占空比会变吗?

2021-09-24 10:33:52

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

模块,如内核、闪存、存储器和外设,这些模块需要在不同频率下运行。它们的最大运行速率可能受到所使用的实现技术、实施架构、功率目标、以及IP访问时间等因素的限制。时钟分频器电路是必不可少的,它可以从主锁相环

2012-12-11 14:43:20

NB7L32MMNEVB,用于SONET的20000MHz时钟分频器的评估板。评估板旨在便于快速评估NB7L32M GigaComm时钟驱动器

2019-02-20 09:30:29

DC1075A,演示电路1075是用于高速ADC的时钟分频器。每个组件包括一个时钟分频器,后面是一个用于产生尖锐时钟边沿的重定时级

2019-02-21 09:45:45

我想对2GHz的正弦波(相位噪声很低)进行16分频,分频出来的125M信号输入给FPGA,想选用ADi的分频器实现分频功能,我有以下几个问题:1.我查了ADi的分频器,分为(1)时钟分频器,(2

2019-01-11 13:39:43

我打算使用AD9269进行信号采集,关于时钟分频器这块,我不需要进行内部的分频,只需要根据我外部输入时钟频率工作就可以,在控制管脚SYNC这一块,芯片手册上说通过数字输入控制,但是不希望进行数字输入

2018-10-10 10:32:15

PWM预分频器、分频器和定时器的分辨率是多少?

2020-12-07 06:07:09

与传统的时钟缓冲器相比,高速运算放大器有哪些优势?怎样去设计一个灵活的时钟缓冲器?

2021-04-14 06:35:37

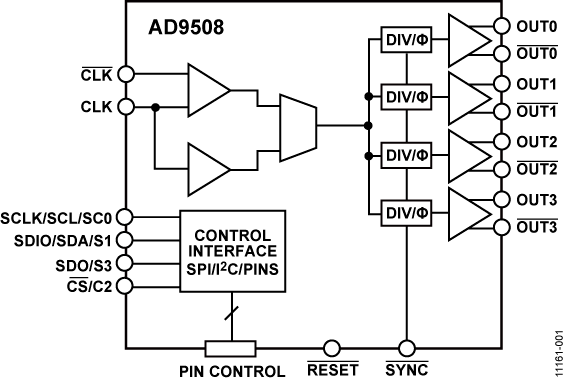

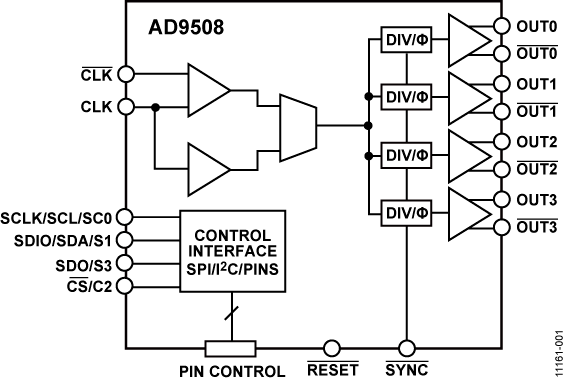

如图,AD9508的差分输入灵敏度要求在360到2200 mVpp,共模电压在1.05V左右。我们设计的电路如下图:其中OCXOUT为恒温晶振输出,作为AD9508的外接信号源,通过巴伦转换为差分信

2018-08-22 07:57:37

分频器的使用问题音响技术分频器是一种可以将声音信号分成若干个频段的音响设备。我们知道,声音的频率范围是在20Hz—20kHz之间,祈望仅使用一只扬声器就能够保证放送、20Hz—20kHz这样宽频

2019-11-01 09:10:30

`音箱分频器电感的制作分频器线圈用线均为0.1mm. 电感量(mH)圈数0.3900.35950.51140.651300.81431.01601.51952.02213.0284漆包线在φ32mm骨架上多层平绕,绕好后脱胎用线扎紧`

2013-08-30 22:12:50

(注:文中的x为数字)初始化1.TIMx的外设时钟使能RCC->APB1ENR |= 1 ARR = arr;3.设定预分频器的值在设定预分频器的值之前,先理解这里的预分频器与时钟系统里

2021-08-18 07:54:36

`请问高速缓冲器是什么?`

2019-08-23 16:32:59

具有分频器的 5/10 路输出时钟缓冲器 Function Differential Additive RMS jitter (Typ) (fs) 200 Output

2022-11-30 16:59:28

具有 8 个 LVDS 输出的 1.6GHz 高性能时钟缓冲器、分频器和分配器 Function Clock divider, Differential Additive RMS

2022-11-30 16:59:30

具有 8 个 LVPECL 输出的 1.6GHz 高性能时钟缓冲器、分频器和分配器 Function Differential, Fanout Additive RMS jitter

2022-11-30 16:59:30

具有 3 个 LVDS 和 5 个 LVPECL 输出的 1.6GHz 高性能时钟缓冲器、分频器和分配器 Function Differential, Fanout Additive

2022-11-30 16:59:31

具有可编程分频器的时钟缓冲器,LVPECL I/O 和 LVCMOS 输出 Function Clock divider, Fanout Additive RMS jitter

2022-12-02 13:46:54

具有可编程分频器的 1:3 LVPECL 时钟缓冲器 Function Differential, Fanout Additive RMS jitter (Typ) (fs

2022-12-02 13:46:55

1:3 LVPECL 时钟缓冲器 + LVCMOS 输出 + 可编程分频器 Function Clock divider, Fanout Additive RMS jitter

2022-12-02 13:46:56

定阻型功率分频器的设计与制作(三)-二阶功率分频器

2009-12-02 15:48:19 76

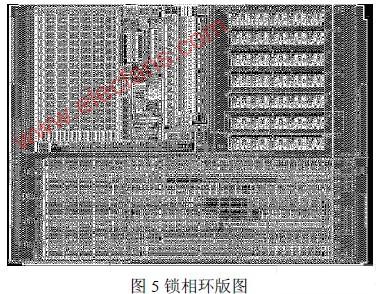

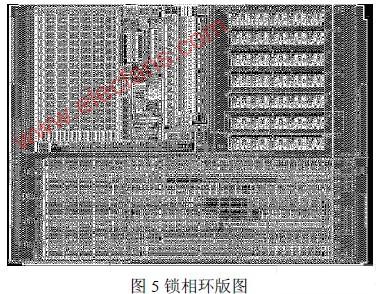

76 给出基于0.13μm CMOS工艺、采用单时钟动态负载锁存器设计的四分频器。该四分频器由两级二分频器级联而成,级间采用缓冲电路实现隔离和电平匹配。后仿真结果表明其最高工作频

2010-12-29 18:00:34 34

34

供数字时钟使用的+5000分频器电路

2009-01-13 20:07:47 1089

1089

分频系数可变的分频器

2009-04-11 10:18:26 1206

1206

具有奇次和偶次分频的分频器

2009-04-11 10:22:12 880

880

TI推出正弦至正弦波时钟缓冲器

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦波时钟缓冲器系列产品中的首款

2009-11-30 10:53:51 815

815 什么是分频器 分频器介绍

分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放

2010-02-05 17:51:10 3676

3676 ADI 公司推出低功耗射频预分频器-- ADF500x 射频预分频器电路工作频率可达 18GHz,功耗非常低,可与业界领先的 ADI PLL 合成器配套使用

&nbs

2010-05-11 16:27:21 580

580 1 引言

本文在传统锁相环结构的基础上进行改进,设计了一款用于多路输出时钟缓冲器中的锁相环,其主 要结构包括分频器、鉴频鉴相器(PFD)、电荷泵、环路滤波器

2010-08-17 15:33:59 1035

1035

用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 The AD9508 provides clock fanout capability in a design that emphasizes low jitter to maximize

2017-10-19 13:26:20 14

14 分频器分为主动式、被动式、脉冲分频器三种。主动式电子分音器的原理就是要把适当频率讯号传给适当的单体,被动式分音器“功能、用途”是介于扩大器与喇叭之间,由于单一喇叭无法达到“全频段响应”,脉冲分频器利用汉稳态电路的计数功能实现分频的电路,又称为数字分频器。

2018-01-10 15:36:20 10793

10793 本文首先介绍了什么是分频器,其次阐述了音箱箱体及音箱分频器结构和原理,最后介绍了音箱分频器特点和作用。

2018-05-25 17:47:16 11413

11413

本文首先介绍了分频器的分类及电子分频器的工作原理,其次介绍了主动分频器的优缺点,最后介绍了被动分频器的优缺点,具体的跟随小编一起来了解一下。

2018-05-28 14:52:31 47204

47204 电子发烧友网为你提供ADI(ti)AD9508相关产品参数、数据手册,更有AD9508的引脚图、接线图、封装手册、中文资料、英文资料,AD9508真值表,AD9508管脚等资料,希望可以帮助到广大的电子工程师们。

2019-02-22 15:53:34

电子发烧友网站提供《NB7V33MMNGEVB 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:06:41 5

5 电子发烧友网站提供《NB7L32MMNEVB 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:21:59 2

2 电子发烧友网站提供《SY89876L 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:22:31 10

10 电子发烧友网站提供《SY89873L 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:23:10 5

5 电子发烧友网站提供《NB6L239MNEVB/D 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:23:51 13

13 电子发烧友网站提供《SY89872U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:24:21 1

1 电子发烧友网站提供《SY89871U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:25:53 6

6 电子发烧友网站提供《SY89875U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:27:06 4

4 AD9508 Evaluation Software Full Install

2021-02-19 09:40:09 2

2 AD9508 IBIS Model

2021-03-09 12:27:12 0

0 AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出

2021-03-21 15:32:58 11

11 AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整

2021-03-21 15:45:30 2

2 AD9512:1.2 GHz时钟分配IC,1.6 GHz输入,分频器,延迟调整,五输出数据表

2021-03-22 19:53:41 13

13 AD9508评估软件Web安装

2021-04-09 10:09:51 0

0 AD9515:1.6 GHz时钟分配IC、分频器、延迟调整、双输出数据表

2021-04-13 14:38:52 9

9 AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

2021-05-08 20:05:05 5

5 AD9508 IBIS型号

2021-05-30 14:31:06 0

0 AD9508评估软件完全安装

2021-06-02 12:20:01 0

0 AD9508评估板是一款紧凑、易于使用的平台,可用来评估AD9508的全部特性。本用户指南将重点说明AD9508评估板和软件。AD9508是一款灵活的高性能1:4时钟缓冲器。每个输出具有一个可编程分频器,可通过SPI/I2C编程或Sx引脚绑定设置。AD9508采用2.5 V和3.3 V电源电压工作。

2021-06-08 17:50:56 6

6 AD9515 1.6 GHz时钟分配IC,分频器,延迟调整,双输出数据表

2021-06-16 17:13:16 12

12 IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

2022-05-05 15:41:13 1500

1500

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

时钟缓冲器选型目录

2021-11-19 16:38:53 789

789

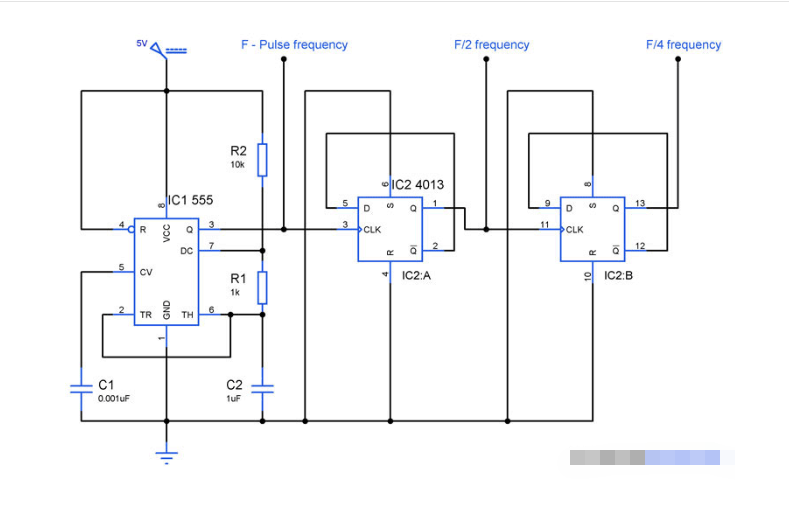

曾经遇到过这样一种情况,即您只有一个特定频率的信号源,需要获取多个频率的信号。如果是,这种电路可能是您需要在设计中使用的电路。上述电路是一个分频器,能够通过一定的因素对输入时钟频率进行分频。该分频器

2023-07-02 11:47:17 791

791

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 471

471

电子发烧友App

电子发烧友App

评论