电源技巧#8:设计12GHz,超低相位噪声(0.09 ps rms抖动)锁相环

- 锁相环(87199)

相关推荐

低相位噪声电压控制振荡器(VCO)和稳定基准电压构成的频率合成器

新兴的PLL + VCO (集成电压控制振荡器的锁相环)技术能够针对蜂窝/4G、微波无线电军事等应用快速开发低相位噪声频率合成器,ADI集成频综产品的频率覆盖为25 MHz到13.6 GHz。

2019-09-19 10:53:20 6311

6311

6311

6311

如何利用相位噪声分析程序和传递函数来降低锁相环的输出相位噪声?

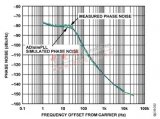

本文是关于相位噪声建模、仿真和传播在锁相环中的应用的第三部分。文章介绍了相位噪声的理论和测量方法,并探讨了相位噪声的分析与建模过程。

2023-10-27 11:42:47 569

569

569

569

低相位噪声&抖动

表示。抖动分为确定性和随机性抖动。确定性抖动是可识别的干扰信号造成的,这种抖动的幅度有限。总抖动的构成如下:在时域中,噪声是非周期的函数。而傅里叶分析可以把此函数分解成多个正弦周期的函数,如下。相位噪声

2020-06-10 17:38:08

电源技巧#8:设计12GHz,超低相位噪声(0.09 ps rms抖动)锁相环

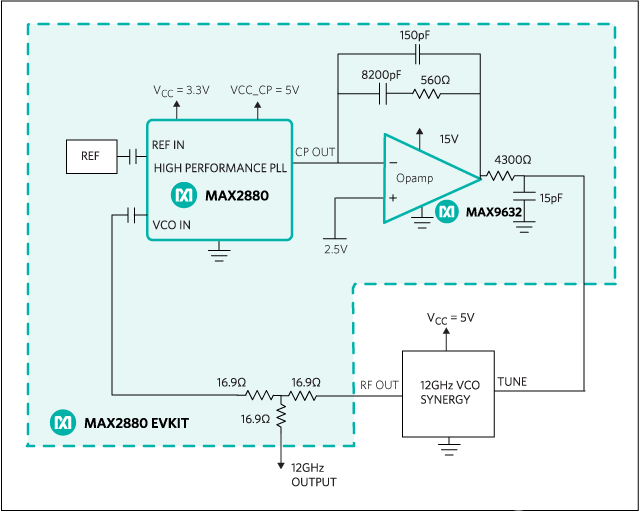

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO

2018-12-10 09:50:52

电源隔离和锁相环对于DSP中EMI的抑制

。本文就将为大家介绍在DSP系统中如何有效避免噪声和EMI产生,对其中的电源隔离和锁相环进行介绍。 电源隔离和锁相环 如何实现最佳供电是控制噪声和辐射的最大挑战。动态负载开关环境很复杂,包括的因素

2018-11-30 17:14:11

相位噪声分析仪-从1 MHz到50/65 GHz

,VCO,发射机,锁相环,频率合成器等,范围从VHF到微波频率),以及有源和无源非自激振荡设备,例如放大器或频率。分隔线。带有FPGA交叉频谱引擎的混合信号系统架构可实现非常快速的信号处理和超低相位噪声

2021-08-31 14:59:22

相位噪声的RMS抖动

我正在使用E5052B信号源分析仪来获取相位噪声数据,载波频率为20.460802MHz,频率范围为1Hz至5MHz。我试图将导出为.csv文件的相位噪声数据转换为RMS抖动(弧度),但是我在整个

2018-10-10 17:50:29

超低抖动时钟发生器与串行链路系统性能的优化

的范围在100fs至300fs之间。这个12kHz-20MHz的标准相位噪声集成范围包括锁相环 (PLL) 频带内和频带外 (VCO) 噪声的影响。基准时钟发生器的相位噪声性能需要在PLL环路带宽内

2018-09-05 16:07:30

锁相环LTC6946电子资料

概述:LTC6946是一款全集成型 VCO 的高性能、低噪声、6.39GHz 锁相环 (PLL),它包括一个基准分频器、具锁相指示器的相位-频率检测器 (PFD)、超低噪声充电泵、整数反馈分频器和 VCO 输出...

2021-04-13 06:31:10

锁相环在电力系统中的应用

硬件锁相环和软件锁相环,这个很好理解,很多东西原来都是直接用硬件电路搞出来,现在有可编程器件了,再利用软件来实现。传统的硬件锁相环在如谐波、频率突变、相位突变等电压畸变以及三相电压不平衡情况下,很难

2015-01-04 22:57:15

锁相环常见问题解答

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-10-31 15:08:45

锁相环常见问题解答

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-11-06 09:03:16

锁相环控制频率的原理

锁相环控制频率的原理锁相环频率自动跟踪-------用锁相环可以确保工作在想要的频率点上如何理解以下两段话?鉴相器是相位比较装置, 它把输入信号和压控振荡器的输出信号的相位进行比较, 产生对应

2022-06-22 19:16:46

锁相环疑问

对于锁相环部分一直有个疑问:1)鉴相器是根据输入信号和输出信号的相位差来输出一个电压,通过LP后,控制压控振荡器的频率输出2)假如输入鉴相器的频率不同,那么电路是如何根据相位差来判断频率之间的差值呢?也就是相位差与频率差之间的关系是怎样的? 有木有相关的资料可以参考?或是请大牛们解释下,多谢啦

2017-07-27 09:03:46

锁相环的原理,特性与分析

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

锁相环知识

本帖最后由 zhihuizhou 于 2011-12-21 17:43 编辑

锁相环PLL原理与应用 第一部分:锁相环基本原理 一、锁相环基本组成 二、鉴相器(PD) 三

2011-12-21 17:35:00

锁相环路是什么?有何特点

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号

2022-01-11 06:34:28

APPH系列相位噪声分析仪和VCO测试仪—输入高达40GHz

必不可少的分析和测量功能,用于评估信号源(晶体振荡器、VCO、发射器、锁相环、频率合成器等,范围从 VHF 到微波频率),以及有源和无源非自振设备,如放大器或分频器等。这些功能包括绝对和加性相位噪声、幅度

2021-12-01 13:15:07

DAC相位噪声测量改进以支持超低相位噪声DDS应用

ADI公司的低噪声稳压器系列对模拟电压和时钟电压供电时,AD9164现在可支持超低相位噪声、基于DDS的应用。参考电路Bergeron, Jarrah. “分析及管理电源噪声和时钟抖动对高速DAC相位噪声

2018-10-17 10:57:21

LabVIEW锁相环(PLL)

LabVIEW锁相环(PLL) 锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环

2022-05-31 19:58:27

MCU锁相环的相关资料分享

原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者

2021-11-04 08:57:18

PVA0865AF-LF锁相环

的步长。 PLL系列产品有几种不同尺寸可供选择从0.866英寸x 0.63英寸到小至0.5英寸x 0.5英寸。整数N和分数N低相位噪声紧凑的尺寸RFS4300A-LF锁相环RFS4500A-LF锁相环

2021-04-03 17:00:58

SFS11000Y-LF锁相环

信号源的任何应用的理想选择,并且利用微带或陶瓷谐振器拓扑结构可提供出色的相位噪声性能。测试仪器雷达系统SFS10500H-LF锁相环SFS10625H-LF锁相环SFS10640H-LF锁相环

2021-04-03 17:05:46

c2000实现的锁相环

a[10]=[0],用观察窗口观察变量时,只有a[0]=0,其他值仍然是随机值。难道数组的初始化必须对每个元素分别赋值吗?

2. 单相数字锁相环的设计。目前我们在进行单相光伏并网逆变器的开发,在对电网相位的跟踪上处理不是特别好,请问贵司有没有数字锁相环的程序包或者相关的说明文档可以参考?

2018-05-14 03:22:42

【模拟对话】锁相环(PLL)基本原理

(ADI公司内部PLL电路仿真器)来演示不同电路性能参数。基本配置:时钟净化电路锁相环的最基本配置是将参考信号(FREF)的相位与可调反馈信号(RFIN)F0的相位进行比较,如图1所示。图2中有一个在

2019-10-02 08:30:00

一文读懂锁相环(PLL)那些事

使用ADIsimPLL(ADI公司内部PLL电路仿真器)来演示不同电路性能参数。基本配置:时钟净化电路锁相环的最基本配置是将参考信号(FREF)的相位与可调反馈信号(RFIN)F0的相位进行比较,如图1所示

2019-01-28 16:02:54

一种宽频率范围的CMOS锁相环(PLL)电路应用设计

本文设计了一种宽频率范围的CMOS锁相环(PLL)电路,通过提高电荷泵电路的电流镜镜像精度和增加开关噪声抵消电路,有效地改善了传统电路中由于电流失配、电荷共享、时钟馈通等导致的相位偏差问题。设计了

2019-07-08 07:37:37

传输线为2~5米产生的附加抖动易引起锁相环失锁吗?

目标:以10或40MHz的差分时钟经2~5米长的电缆传输到至少两块线路板上,倍频为200MHz的时钟;要求此两板上的200MHz时钟保持同步,或者说在每次上电的情况下保持恒定的相位关系。 锁相环

2018-09-18 11:14:35

全数字锁相环的设计及分析

全数字锁相环的设计及分析 1 引 言 锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数

2010-03-16 10:56:10

关于锁相环的组成你了解多少?

)和压控振荡器(VCO)三部分组成。 锁相环特点是:用外部输入的参考信号控制环路内部振荡信号的频率和相位。 锁相环工作原理:相位比较器把输入信号作为标准,将它的频率和相位与从VCO输出端送来的信号进行

2019-03-17 06:00:00

关于使用ADIsimPLL设计锁相环的问题

现在使用了ADI公司的一款芯片设计一个可以产生固定频率的锁相环。在调整环路滤波中的电阻电容值时,也要保证相位裕度在45-60这个范围。现在调整的相噪无法达到客户的要求。先寻一个调试的思路

2017-07-19 18:18:34

关于有源晶振的相位抖动和相位噪音

合成器产生输出频率的振荡器比采用非锁相环技术的振荡器一般呈现较差的相位噪声性能。例如,对于需要低噪声、稳定和精确时钟源的工业级设备(比如收发器模块或数据中心),可选择150fs小型塑封石英PLL振荡器;而

2023-12-14 09:19:08

具有时钟分配的1.4GHz低相位噪声和低抖动PLL的演示板DC1795A

DC1795A,用于LTC6950的演示板,具有时钟分配的1.4GHz低相位噪声,低抖动PLL。演示电路1795A采用具有时钟分配的LTC6950,1.4 GHz低相位噪声,低抖动PLL。为了便于

2019-02-25 09:55:24

利用谐波混频的微波低相噪锁相设计介绍

0 引言众所周知锁相环的环路带宽以内的相位噪声主要由晶体振荡器经过倍频恶化后的相位噪声与鉴相器引入的相位噪声共同决定。对于环路带宽以外的相位噪声则主要由VCO的相位噪声和鉴相器引入的噪声基底恶化共同

2019-06-20 08:09:50

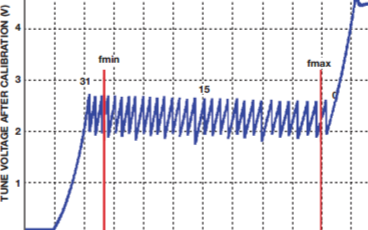

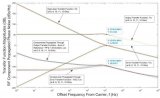

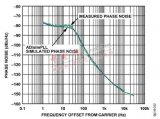

发现抖动、相位噪声、锁定时间或杂散问题怎么解决

图1中,锁相环(PLL)与压控振荡器(VCO)噪声交叉处的偏移,BWJIT(约为140kHz)通过减少曲线下方的面积来优化抖动。 图1:最优抖动带宽 尽管此带宽BWJIT对抖动而言是最优的,但对

2022-11-16 07:56:45

基于低相位噪声的微波源分析

振荡源的相位噪声有较大的影响。2856MHz微波源同时利用了脉冲倍频锁相环和介质振荡器两项技术,有效的提高了微波振荡源的相位噪声,同时具有谐波低、体积小、功耗小、可靠性高的优点。可用于卫星通信、雷达、实验设备等对相位噪声要求较高的场合。

2019-07-09 07:33:14

基于锁相环芯片ADF4106的工作特性设计频率合成器

本文由锁相环频率合成器的基本工作原理入手,介绍基于锁相环芯片ADF4106的工作特性,并结合环路滤波器、压控振荡器和射频通路设计出一种输出频率为2GHz的频率合成器,并经过印制板加工及测试,验证

2018-09-06 14:32:13

怎么设计低噪声12 GHz微波小数N分频锁相环?

的超低噪声 OP184 运算放大器驱动微波VCO,在12 GHz下可实现完全低噪声PLL,经测量积分相位噪声为0.35 ps rms。

2019-08-20 06:44:35

怎样将相位噪声和抖动降至最低及其估算方法

为时间,见下式: 利用图4所绘的噪声功率值,我们可以计算一个312.5MHz振荡器的RMS抖动。将相位噪声曲线在12 kHz到20 MHz范围内积分,得到-63 dBc: 因此可以得到如下式所示

2009-10-13 17:23:19

数字锁相环设计步骤

'。数字锁相环设计步骤:根据设计参数要求合理选取R值,通常R不小于8,本文选取R = 20讲解。以后文中用到20均指R,而提到10则指R/2。确定5个域的宽度,本例选取5个域等宽。由于R = 20

2012-01-12 15:29:12

求助牛人——PFGA做锁相环

大家好,我的课题是要用FPGA做一个高精度锁相环。这个数字锁相环的工作原理为:正弦模拟信号通过低通滤波器后,经过模数转换器(ADC)转化为数字信号,与NCO(数控振荡器) 的输出信号相乘后滤波,从而

2016-08-15 11:31:56

浅析低相噪Hittite锁相环产品

频率源可以说是一个通信系统的心脏,心脏的好坏很大程度上决定着一个机体的健康状况,而锁相环又是频率源的主要组成部分,因此性能优异的锁相环芯片对于通信系统来说是非常重要的。锁相环的相位噪声对电子设备

2019-06-25 06:22:21

测量较低时钟频率的相位噪声和相位抖动

],以获得以秒为单位的RMS相位抖动,如下所示:从f1到f2的偏移频率以Hz为单位进行积分,其中f0是载波或时钟频率。在实践中,所涉及的数量足够小,对于良好的时钟来说,对于12kHz到20MHz的抖动带宽

2021-06-24 07:30:00

电荷泵锁相环电路锁定检测的基本原理,影响锁相环数字锁定电路的关键因子是什么?

本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2021-04-20 06:00:37

请问锁相环可以用来产生FMCW信号么

您好,我们目前在做一个调频连续波的雷达,DDS输出50~60MHz,使用ADI的锁相环ADF4108 96倍频至4.8GHz~5.8GHz,扫频周期4ms,点频测试时锁相环的相位噪声还可

2018-08-16 07:18:19

请问HMC7044锁相环可以配出8路2.5G,相位可调的时钟吗?

HMC7044锁相环可以配出8路2.5G,相位可调的时钟吗,其中7路DCLK加一路SDCLK。特别是同组里面的两路时钟可以分开,分别调整相位吗?

2018-08-02 07:08:29

请问有锁相环芯片开关机相位保持一致吗?

您好! 请问ADI是否这样的锁相环芯片,在外参考输入时钟不关的情况下,开关锁相环芯片,锁相环输出时钟相位保持一致,也就是说只要输入参考不变,开关锁相环芯片,输出时钟相位保持不变,若变,变化范围是多大, 若无此类锁相环芯片,请问ADI是否有此类问题的解决方案。 十分感谢!!

2018-08-31 11:00:43

请问能使用ADIsimPLL仿真双环锁相环吗?

我刚接触锁相环没多长时间,最近想使用ADF4106搭建一个双环锁相环,我阅读的资料都没有说主环路环路滤波器参数计算问题,我想咨询专家ADIsimPLL是否可以仿真计算双环锁相环,如果可以具体怎么考虑,如果可以告诉我一些主环路环路带宽的知识就更好了.

2019-03-07 10:34:03

锁相环频率合成器:相位噪声问题和宽带循环

锁相环频率合成器:相位噪声问题和宽带循环:

In this chapter we locate the context of this thesis by introducing

2009-07-25 17:18:33 0

0

0

0ADF4378BCCZ 具有集成电压控制的相控阵锁相环

ADF4378BCCZ是一款高性能、超低抖动、整数N 具有集成电压控制的相控阵锁相环(PLL) 理想情况下,振荡器(VCO)和系统参考(SYSREF)重定时器 适用于数据转换器和混合信号前端

2024-01-04 19:31:37

锁相环(PLL)和相移键控(PSK)系统的相位噪声

锁相环(PLL)和相移键控(PSK)系统的相位噪声振荡器的相位噪声有可能导致相位变换的错误检测,即在用相位键控法进行数字调制时产生误码。例如,

2008-11-24 12:40:59 1796

1796

1796

1796

低噪声12 GHz微波小数N分频锁相环的设计

具有适当偏置和滤波的超低噪声 OP184 运算放大器驱动微波VCO,在12 GHz下可实现完全低噪声PLL,经测量积分相位噪声为0.35 ps rms。该功能通常用于产生本振频率(LO),适用于微波点对点

2017-11-25 12:37:01 250

250

250

250

低噪声12 GHz微波小数N分频锁相环的设计

具有适当偏置和滤波的超低噪声 OP184 运算放大器驱动微波VCO,在12 GHz下可实现完全低噪声PLL,经测量积分相位噪声为0.35 ps rms。该功能通常用于产生本振频率(LO),适用于微波点对点

2017-11-25 12:37:01 252

252

252

252

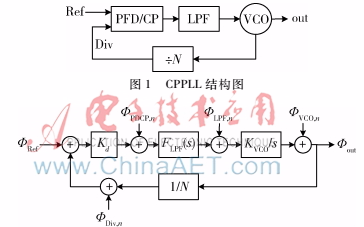

基于款频率数字系统的低抖动八相位锁相环设计

口]。电荷泵锁相环CPPLL(ChargePump Phase Locked Loop)是数模混合锁相环的典型代表,因其具有理论上零静态相位误差、高速、低功耗、低抖动等特征,成为目前使用最为广泛的锁相环。特别是多相位锁相环(Multiphase PhaseLocked Loop)精准的

2017-12-06 11:39:32 0

0

0

0关于2.4 GHz的低噪声亚采样锁相环设计

介绍一种2.4 GHz的低噪声亚采样锁相环。环路锁定是利用亚采样鉴相器对压控振荡器的输出进行采样。不同于传统电荷泵锁相环,由于在锁定状态下没有分频器的作用,由鉴相器和电荷泵所产生的带内噪声不会被放大

2018-06-07 15:58:00 8829

8829

8829

8829

Custom MMIC低相位噪声放大器的主要特性及应用

。Custom MMIC低相位噪声放大器覆盖DC到40 GHz(UHF、L、S、C、X、Ku、K和Ka波段),可以作为本地振荡器(LO)驱动器或接收机放大器,用于各种需要相位噪声或将抖动降低到绝对最低水平

2020-11-06 15:42:10 605

605

605

605浅谈QORVO低相位噪声放大器的特点以及应用

。QORVO低相位噪声放大器覆盖直流至40GHz(UHF、L,S、C、x、Ku、K和Ka波段),可作为本振(LO)驱动器或接收器放大器,在各种需要降低相位噪声或抖动的设计中达到绝对最低水平。QORVO的许多产品都是用裸芯片和表面贴装QFN封装的。 主要特点 10kHz偏置低相位噪声性能低至-16

2020-11-12 15:06:13 991

991

991

991QORVO低相位噪声放大器的主要特点以及典型应用

。QORVO低相位噪声放大器覆盖直流至40GHz(UHF、L,S、C、x、Ku、K和Ka波段),可作为本振(LO)驱动器或接收器放大器,在各种需要降低相位噪声或抖动的设计中达到绝对最低水平。QORVO的许多产品都是用裸芯片和表面贴装QFN封装的。 主要特点 10kHz偏置低相位噪声性能低至-16

2020-11-12 15:09:04 729

729

729

729HMC606LC5:GaAs、InGaP、HBT、MMIC、超低相位噪声、分布式放大器、2 GHz至18 GHz数据表

HMC606LC5:GaAs、InGaP、HBT、MMIC、超低相位噪声、分布式放大器、2 GHz至18 GHz数据表

2021-04-22 09:23:26 0

0

0

0CN0369 低相位噪声的转换锁相环频率合成器

图1所示电路框图是一个低相位噪声转换环路频率合成器(也称为偏移环路)。此电路将ADF4002 锁相环 (PLL) 的较低100 MHz参考频率转换到5.0 GHz至5.4 GHz的较高频率范围

2021-05-29 08:17:44 20

20

20

20MAX2880应用笔记:设计12GHz、超低相位噪声(0.09 ps rms抖动)锁相环

2022-11-16 21:44:14 0

0

0

012GHz、超低相位噪声小数N分频锁相环的设计

本应用笔记详细介绍了集成外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880)、基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)组成。

2023-01-16 11:27:08 761

761

761

761

相位噪声曲线有助于系统测试

每个系统中都存在噪声。相位噪声尤其常见于振荡器中,锁相环会降低系统性能。无线通信系统振荡器中的相位噪声会降低接收器在倒易混频条件下的灵敏度。电信系统中的相位噪声会导致信号链中的时间抖动。虽然工程师

2023-03-08 14:19:00 739

739

739

739

设计12GHz、超低相位噪声(0.09 ps rms抖动)锁相环

本应用笔记详细介绍了具有外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL (MAX2880)、基于运算放大器的有源环路滤波器(MAX9632

2023-10-28 14:45:41 6895

6895

6895

6895锁相环在相位检测中的应用

锁相环在相位检测中的应用 锁相环(PLL)是一种电子技术中广泛应用的电路,用于调整一个输出信号的相位来精确匹配一个参考信号。锁相环在各种不同的应用领域都有着广泛的应用,例如通信系统、控制系统、测量

2023-10-29 11:35:19 358

358

358

358锁相环的输入输出相位一致吗?

锁相环是保证相位一致,还是相位差一致?锁相环的输入输出相位一致吗? 锁相环(PLL)是一种回路控制系统,用于保持输出信号的相位与参考信号的相位之间的恒定关系。简单来说,锁相环的目的是保证相位一致

2024-01-31 15:45:48 202

202

202

202 电子发烧友App

电子发烧友App

评论