电子发烧友网站提供《完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表.pdf》资料免费下载

2024-03-13 13:58:12 0

0 电子发烧友网站提供《适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表.pdf》资料免费下载

2024-03-13 13:53:03 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0 电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

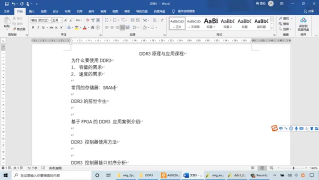

0 DDR的数据信号速率更高,为啥要更关注DDR的地址控制信号?数据信号一般都是点到点的拓扑,而且大多有片上端接(ODT),走线拓扑简单加上端接加持,信号质量通常都比较有保障。而DDR的地址控制类信号

2024-03-04 15:49:14

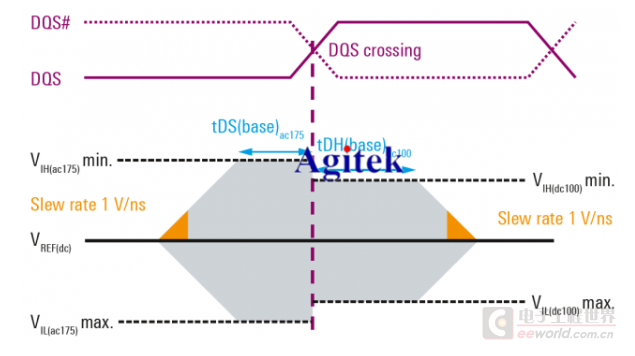

DDR一致性测试的操作步骤 DDR(双数据率)一致性测试是对DDR内存模块进行测试以确保其性能和可靠性。在进行DDR一致性测试时,需要遵循一系列的操作步骤,以保证测试的准确性和完整性。下面将详细

2024-02-01 16:24:52 207

207 使用SC584外扩DDR3,no_boot启动模式,开发环境CCES-2.2.0版本,在线调试过程,程序可正常下载,但是在A5预加载过程中会出现SYS_FAULT拉高现象,经实际汇编单步调试发现

2024-01-12 08:11:46

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 463

463

DDR加终端匹配电阻和不加信号质量的区别 DDR(双倍数据传输速率)是一种常用于计算机内存的高速数据传输技术。在DDR中,终端匹配电阻和信号质量是对于数据传输稳定性至关重要的两个方面。下面将详细

2023-12-29 13:54:22 316

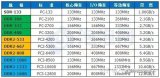

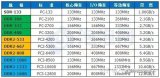

316 时钟频率:可通过倍频技术升级的核心频率。时钟频率可以理解为IO Buffer的实际工作频率,DDR2中时钟频率为核心频率的2倍,DDR3 DDR4中时钟频率为核心频率的4倍。

2023-12-25 18:18:47 1188

1188

被称为 系统时钟 。

DDR内存的数据传输,是通过前沿和下降沿来实现的。在每个时钟周期的前沿和下降沿,DDR内存会传输一个数据,这意味着DDR内存的传输速度是普通SDRAM的 两倍 。

DDR芯片

2023-12-25 14:02:58

被称为 系统时钟 。

DDR内存的数据传输,是通过前沿和下降沿来实现的。在每个时钟周期的前沿和下降沿,DDR内存会传输一个数据,这意味着DDR内存的传输速度是普通SDRAM的 两倍 。

DDR芯片

2023-12-25 13:58:55

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行

2023-12-25 07:45:01 211

211

何有缺点?看过一个介绍是使用直方图统计的方式来计算的,但需要大量的数据;而且在测试这个指标的时候输入的信号是否也需要接近满幅度?

(3)应该怎么样评估外部信号源的质量可以满足ADC测试要求?应该关注

2023-12-22 06:55:00

如何利用示波器测试晶振信号? 示波器是一种广泛用于电子测试和测量的仪器,可以帮助分析和显示电信号的各种特征。在测试晶振信号时,示波器可以用于观察信号的振荡频率、幅度、稳定性等参数。下面将详细介绍

2023-12-18 14:16:13 830

830 目前手上有一个ADI的AD9361子卡AD-FMCOMMS3_EBZ和一块ZED BOARD的板子,想问下怎么能够利用IIOSCOPE软件来快速上手测试。

2023-12-11 06:24:30

稳定性测试、峰值检测等,并自动生成详细的测试报告,包括波形图、统计数据和分析结论。这种自动化不仅大大减少了测试时间,也减少了人为错误,提高了数据的准确性。

通过这个案例,我们成功地利用LabVIEW

2023-12-09 20:37:39

方波测试,仍然存在这样的问题。

难道ADA4932不适合单端转差分的场合?

在50欧姆端接电阻的情况下,信号源能否驱动50欧姆的电阻是未知的,对一般的信号都是运放输出,而运放只能输出到50mA就很大了。那我怎么利用ADA4932来实现高阻输入呢?

2023-11-17 07:50:22

法人方面解释说:“标准型dram和nand目前由三星、sk hynix、美光等跨国企业主导,因此,中台湾企业在半导体制造方面无法与之抗衡。”在ddr3 ddr3的情况下,台湾制造企业表现出强势。ddr3的价格也随之上涨,给台湾半导体企业带来了很大的帮助。

2023-11-14 11:29:36 405

405 DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR3

2023-10-30 09:22:00 3886

3886 DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 516

516

的24个GTY,LVDS信号,DSP的1路以太网

三、软件系统

•提供FPGA的接口测试程序,包括 DDR4、光纤、RapidIO、FMC等接口

•提供DSP接口测试程序,包括DDR3、Flash

2023-10-16 11:12:06

1. 简介

RK3588从入门到精通

ArmSoM团队在产品量产之前都会对产品做几次专业化的功能测试以及性能压力测试,以此来保证产品的质量以及稳定性

优秀的产品都要进行多次全方位的功能测试以及性能

2023-10-09 19:29:50

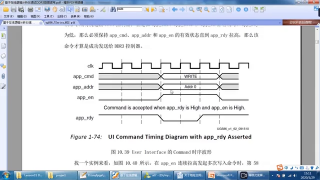

select,导入fdc文件,DDR3的相关配置便会自动更改,而不需要手动一个一个更改。

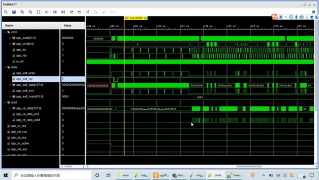

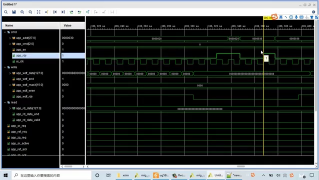

05 测试读写逻辑

自增计数对DDR所有地址写一遍,写完后对所有地址读一遍,读出来的数据与写进去的数据做一个

2023-10-09 19:07:29

摘要:本文将对DDR3和DDR4两种内存技术进行详细的比较,分析它们的技术特性、性能差异以及适用场景。通过对比这两种内存技术,为读者在购买和使用内存产品时提供参考依据。

2023-09-27 17:42:10 1088

1088 采集时,就需要外扩DDR SRAM二级存储来满足需求。

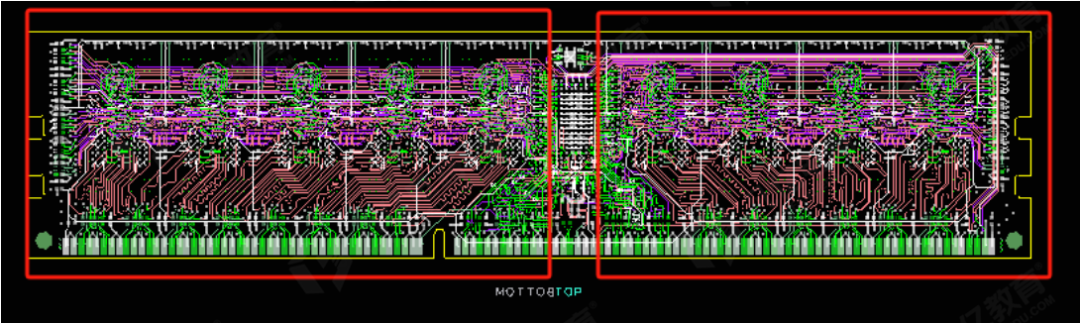

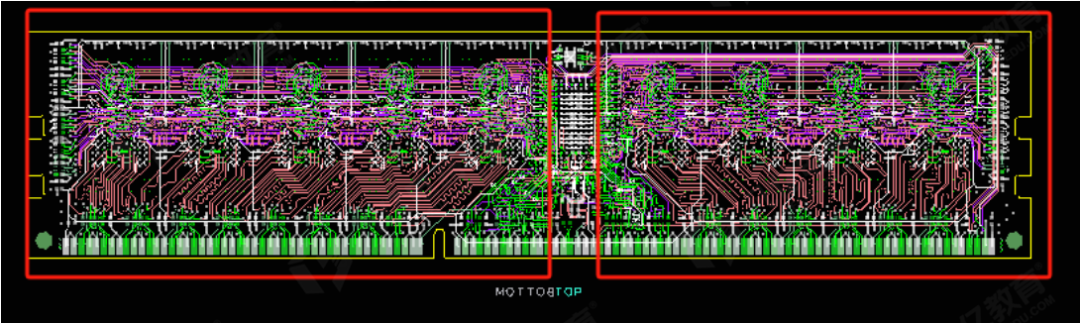

本期的主角盘古PGL50H FPGA就贴心的在核心板上,为我们配备了两片DDR3的芯片,来完成二级存储的需求。

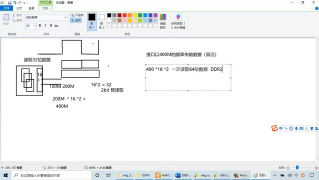

两片DDR3组成32bit的总线数据

2023-09-21 23:37:30

相对于DDR3, DDR4首先在外表上就有一些变化,比如DDR4将内存下部设计为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过渡,这样的设计可以保证金手指和内存插槽有足够的接触面

2023-09-19 14:49:44 1484

1484

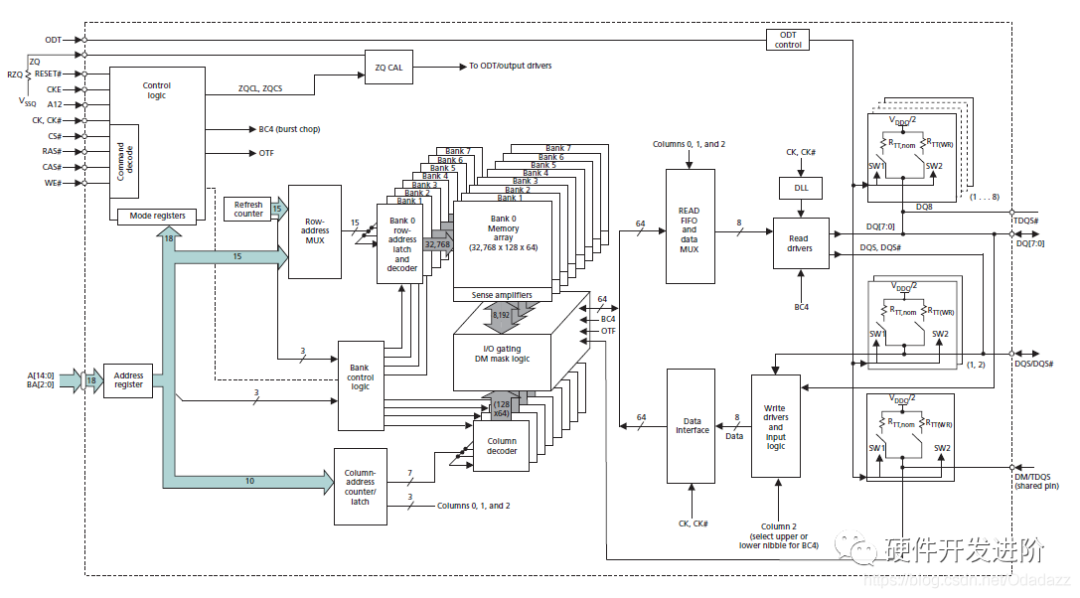

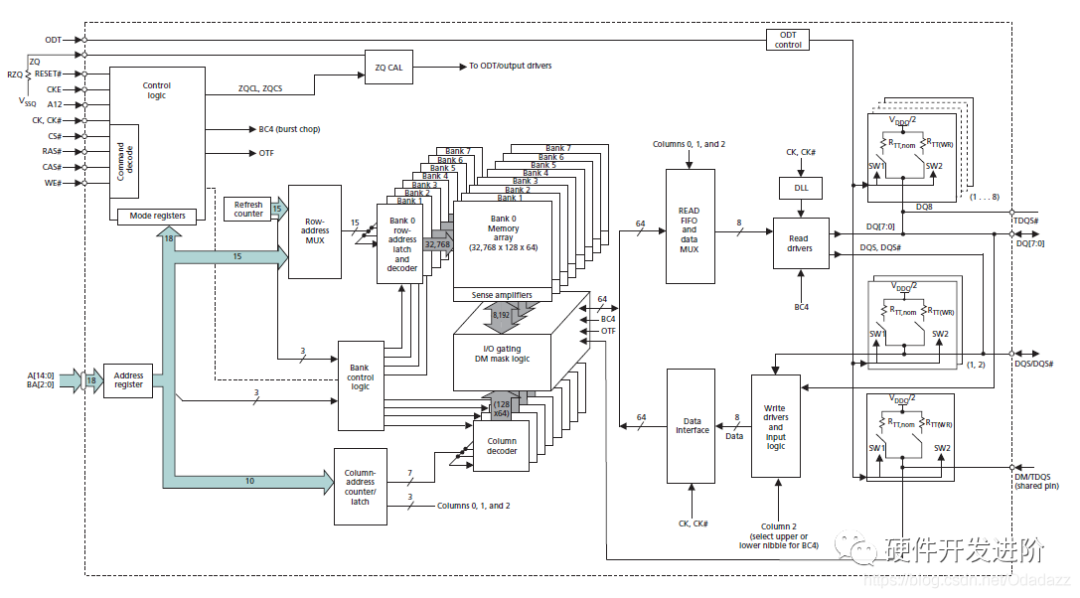

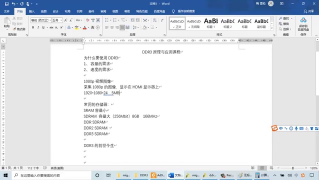

以MT41J128M型号为举例:128Mbit=16Mbit*8banks 该DDR是个8bit的DDR3,每个bank的大小为16Mbit,一共有8个bank。

2023-09-15 15:30:09 629

629

DDR3带宽计算之前,先弄清楚以下内存指标。

2023-09-15 14:49:46 2497

2497

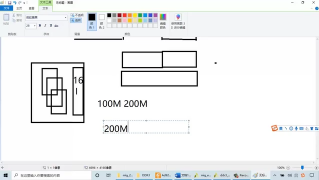

一看到DDR,联想到的就是高速,一涉及到高速板有些人就比较茫然。高速板主要考虑两个问题点,当然其它3W,2H是基本点。

2023-09-15 11:42:37 757

757

内置校准: DDR3和DDR4控制器通常具有内置的校准机制,如ODT (On-Die Termination)、ZQ校准和DLL (Delay Locked Loop)。这些机制可以自动调整驱动和接收电路的特性,以优化信号完整性和时序。

2023-09-11 09:14:34 420

420 本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 743

743

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1888

1888

MCU200T的DDR3在官方给的如下图两份文件中都没有详细的介绍。

在introduction文件中只有简略的如下图的一句话的介绍

在schematic文件中也没有明确表明每个接口的具体信息

2023-08-17 07:37:34

GND回流过孔,尽可能增加GND回流过孔数量,可以进一步改善信号质量,如下图所示。

3、GND过孔和信号过孔的位置会影响信号质量,建议GND过孔和信号过孔交叉放置,如下图所示,虽然同样是4个GND回流

2023-08-16 15:15:53

在配置DDR200T的DDR3时,一些关键参数的选择在手册中并没有给出,以及.ucf引脚约束文件也没有提供,请问这些信息应该从哪里得到?

2023-08-16 07:02:57

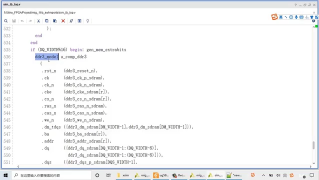

复制Vivado工程路径vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夹。粘贴到仿真路径testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夹)下。

2023-08-12 11:08:27 735

735 PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

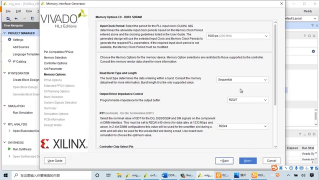

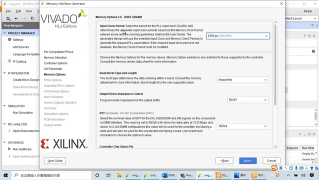

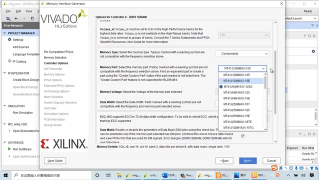

xilinx平台DDR3设计教程之设计篇_中文版教程3

2023-08-05 18:39:58

电子发烧友网站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用.pdf》资料免费下载

2023-07-24 09:50:47 0

0 DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。

2023-07-16 15:27:10 3365

3365

DDR3的速度较高,如果控制芯片封装较大,则不同pin脚对应的时延差异较大,必须进行pin delay时序补偿。

2023-07-04 09:25:38 312

312

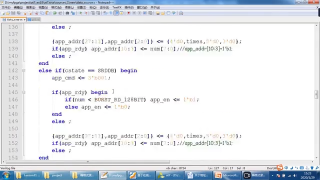

AXI4读写控制模块**

本次实验只是一个简单的读写测试实验,故可以将一些AXI4的信号配置为常量。

使用按键控制数据开始写入DDR3,通过一个移位寄存器来产生这个写标志。

使用状态机来控制写地址信号,写

2023-06-25 17:10:00

。若信号传输质量不够理想,可以通过在serial I/O link的参数设置进行调整,再重新扫描眼图查看是否有改善。

为了测试GTX四个通道的误码率,创建多个links,对四个通道都进行近端环回测试

2023-06-21 11:23:12

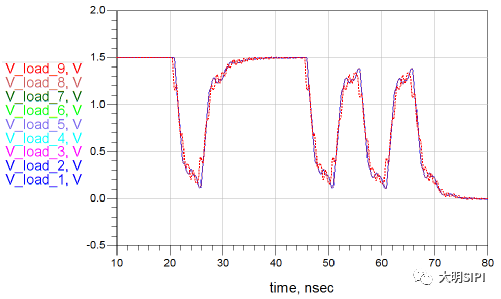

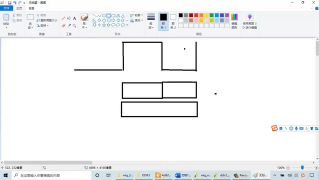

这里介绍两种方式改善带有ECC的奇数负载的DDR2信号质量。一种不需要改变拓扑结构,另一种需要对拓扑结构进行调整。

2023-06-15 17:39:34 474

474

视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。 与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 1024

1024 一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

PGL50H 为用户提供一套完整的 DDR memory 控制器

2023-05-31 17:45:39

我正在使用带有 ECC 芯片的 4GB DDR3 RAM 连接到 T1040 处理器 DDR 控制器。

我尝试了这个序列,但未能成功生成 DDR 地址奇偶校验错误:

步骤1:

ERR_INT_EN

2023-05-31 06:13:03

数据速率 800Mbps

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

GL50H 为用户提供一套完整的 DDR

2023-05-19 14:28:45

你好 :

专家,我们想使用S32R45和DDR3,你能帮我在哪里找到示例项目或用例吗?

2023-05-17 08:13:46

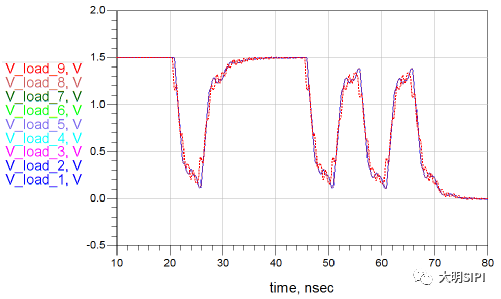

先对比下做容性负载补偿前后DDR链路前端颗粒信号质量情况,因为对于Fly_By链路,前端颗粒的信号质量是最差的。下图是有无做容性负载补偿链路中前端颗粒仿真得出的信号眼图。

从以上仿真结果来看,当

2023-05-16 17:57:26

Read Mode的报告,测试的信号为CLK_t/c DQS_t/c & DQ这三组信号, 下面这张图是使用33GHz示波器运行LPDDR4 Compliance的数据表格,Fail了很多

2023-05-16 15:43:05

在 i.MX6 SOLO 中有没有办法读取芯片 DDR3 的大小?

2023-05-06 07:04:11

嗨,我们想在 iMX8M 上测试 USB 眼图

但我们不知道如何测试,我们已经看到这个链接i.MX6Q/USB HS1 设置的眼图

我们试过寄存器(DCTL)

#./memtool -32 0x3810c704=0x00F00008

但它对我们和 evk 板不起作用。

我们想强制输出测试包,怎么办?

2023-05-04 06:22:19

正如标题,我们的产品准备量产,但面临信号认证问题。

我们需要通过 USB 眼图测试,但我不知道如何启用它。

我的软件设置:

平台:IMX8MP(USB3.0)、IMX8MM(USB2.0)

操作系统

2023-05-04 06:00:08

目前对于DDR4、DDR5等并行信号,信号速率越来越高,电源性能要求也越来越高,今天我们就来看看电源噪声对信号质量的影响;

2023-04-21 09:47:46 1289

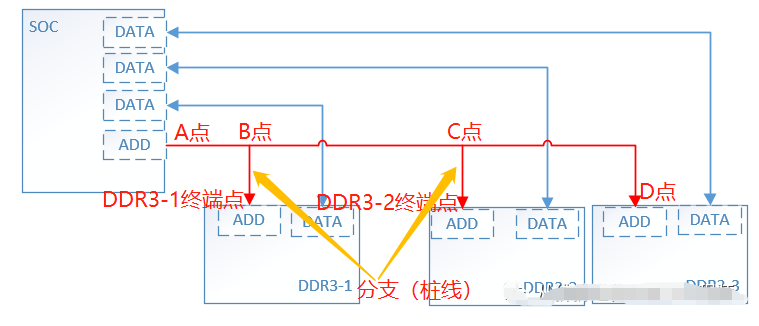

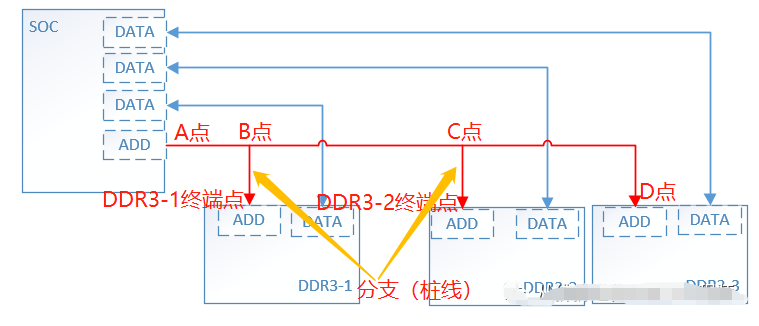

1289 有些设计中可能是三个或者更多芯片在同一个信号链路上,按照flyby拓扑结构布局。如下图是一颗SOC和3颗DDR3的PCB布局设计。因为三颗DDR3的ADD是共用一组来自SOC的信号线,因此只有ADD

2023-04-15 16:07:50 841

841

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

电子发烧友App

电子发烧友App

评论