逻辑芯片输入的低电平有效和高电平有效

- 编码器(131223)

- 电平(39524)

- 数字电路(79615)

- 逻辑芯片(30136)

相关推荐

在通用定时器PWM输出实现呼吸灯的实验中,通道输出极性选择中选择高电平有效,LED0为啥会一直亮?

大佬们,在通用定时器PWM输出实现呼吸灯的实验中,我在这个通道输出极性选择中选择高电平有效,LED0为啥会一直亮?按理说应该是输出低电平才会亮啊。

2024-03-07 06:47:45

CYT4B pwm怎么反转输出信号极性,比如原先低于比较值为低电平,怎么改成高电平?

CYT4B pwm 怎么反转输出信号极性,比如原先低于比较值为低电平,怎么改成高电平

2024-03-04 07:34:31

ttl与非门有哪些主要性能参数 TTL与非门的工作原理

: 逻辑电平参数是描述输入或输出信号在逻辑门内部的电压范围的指标。 VIL:输入的低电平(Logic Low)电压。TTL逻辑门规定,输入低电平范围为0V到0.8V。 VIH:输入的高电平(Logic High)电压。TTL逻辑门规定,输入高电平范围为2V到5V。 VOL:输出的低电平电压。TTL逻辑门

2024-02-22 11:25:25 238

238

238

238CMOS电路什么输入为高电平 cmos门电路输出电平判断

半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,判断输出电平的关键是输入电压。在理想的情况下,当输入电压为高电平时,输出为低电平;当输入电压为低电平时,输出电平为高电平。这是因为CMOS电路的输入管道是一个开关,当输入电压为高

2024-02-22 11:12:34 509

509

509

509cmos电平与ttl电平如何转换 怎么判断ttl电路高低电平

的CMOS电平一般分为逻辑高电平(High Level)和逻辑低电平(Low Level)。CMOS电平的取值一般在0V到Vcc之间,Vcc是CMOS电路供电电压。逻辑高电平一般为Vcc,逻辑

2024-02-22 11:10:52 332

332

332

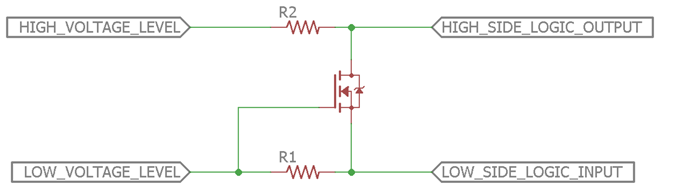

332双向逻辑电平转换器电路图分享

双向逻辑电平转换器是一种电子器件,用于在不同电压逻辑电平之间进行转换。它可以将一个逻辑电平转换为另一个逻辑电平,从而确保在不同电压环境下的设备之间能够正常通信和协作。

2024-02-19 16:54:00 465

465

465

465

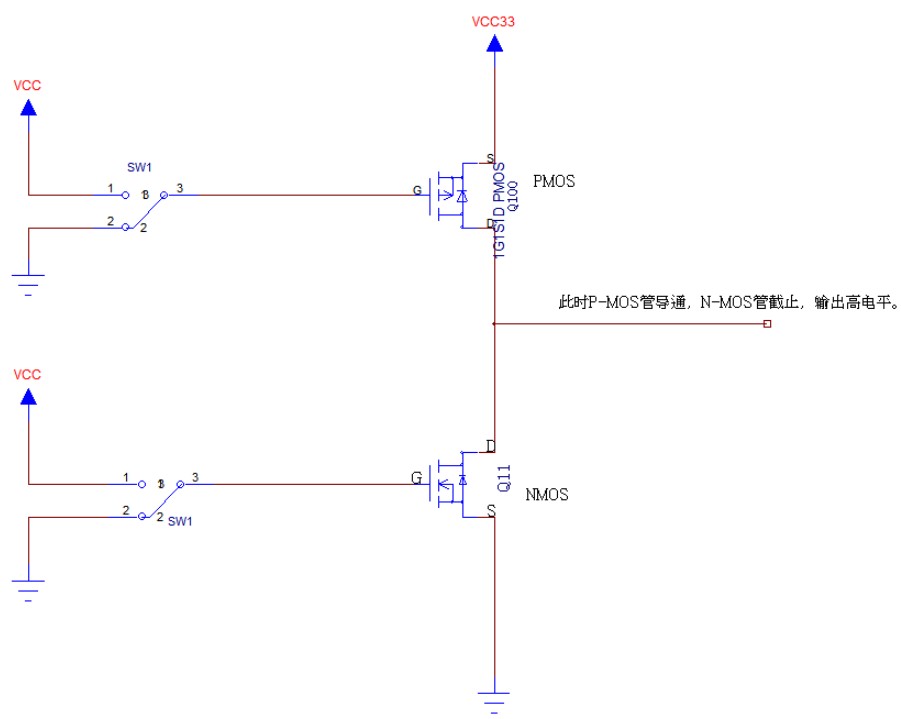

什么是推挽电路 推挽输出高低电平介绍

在推挽输出模式下,一个晶体管用于提供高电平输出,而另一个晶体管则用于提供低电平输出。当内部输出为1电平时,上边的晶体管(如MOS管)导通,同时下边的晶体管截止,这时输出高电平。

2024-02-06 09:27:10 637

637

637

637

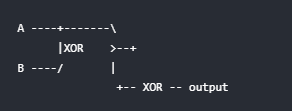

如何用异或门实现反向功能 异或门如何连接输入端实现求反

在这种实现中,当控制信号 B 为高电平时,异或门的输出将反转输入信号 A 的逻辑电平。如果 A 是高电平,则输出是低电平;如果 A 是低电平,则输出是高电平。而当控制信号 B 为低电平时,异或门的输出与输入信号 A 保持一致。

2024-02-04 17:40:01 990

990

990

990

什么是可控反相器 可控反相器芯片的优缺点有哪些

当控制信号处于高电平状态时,输入信号的逻辑电平将被反转。例如,若输入信号为高电平,则输出信号为低电平;若输入信号为低电平,则输出信号为高电平。

2024-02-04 17:35:00 451

451

451

451二进制与逻辑电平的变化范围

二进制中的两个数字0和1称为位(bit, 是二进制数字binary digit的缩写)。在数字电路中,使用两个不同的电平表示这两个位。一般情况下,1 用高电平表示,0用低电平表示,这种逻辑体制称为正逻辑。

2024-02-04 16:54:09 462

462

462

462

单片机中的外部中断低电平触发和下降沿触发有什么区别

触发和下降沿触发。 首先,我们需要了解一下什么是低电平触发和下降沿触发。低电平触发是指当外部信号的电平低于某个特定阈值时,触发中断。而下降沿触发是指当外部信号从高电平变为低电平时,触发中断。这两种触发方式在实

2024-01-31 10:32:49 488

488

488

488xmc7200开发COOLDIM_PRG_BOARD,用逻辑分析仪捕捉输出的最后一位一直为低电平的原因?

我使用 xmc7200 开发 COOLDIM_PRG_BOARD。 我用PWM输出正弦波,我用逻辑分析仪捕捉输出的最后一位异常,最后一位应该是高电平,但长时间低电平,为什么?

2024-01-18 09:37:08

jk触发器悬空是高电平还是低电平

触发器会触发并改变输出状态,这取决于JK触发器的触发方式。 在真实的电路中,JK触发器的触发方式是由实际的电压电平决定的,通常有两种模式,分别是悬空状态为低电平和悬空状态为高电平。在本文中,将详细介绍这两种触发方式,并探讨它

2024-01-15 13:35:53 446

446

446

446AD7985 CNV时钟保持高电平20ns时发现SDO脚一直是低电平,无法检测到中断怎么解决?

AD7985芯片已设置为/CS模式(三线式且有繁忙指示)。

设置方法:TURBO管脚下拉,SDI上拉,SDO接10K的上拉。输出给CNV时钟(1.953Mhz);

问题现象:CNV时钟保持高电平

2024-01-12 06:46:44

NE555触摸电路中人体杂波信号是高电平还是低电平?

NE555电路中,触摸2脚低电平有效有动作,触摸6脚高电平有效有动作,触摸电路中人体杂波信号是高电平还是低电平?

2024-01-10 13:03:22

一文了解电平转换芯片

电平转换芯片可以在数字电路和模拟电路中使用。在数字电路中,它可以将不同的逻辑电平(例如TTL、CMOS、LVCMOS等)转换为其他逻辑电平,以便实现电路之间的兼容性。在模拟电路中,它可以将不同的电压范围(例如±5V、0-10V等)转换为其他电压范围,以便满足不同电路的需求。

2024-01-09 13:08:56 567

567

567

567cmos输入端接电阻后接地是低电平吗

CMOS是一种常见的逻辑门电路,它使用CMOS技术来实现数字逻辑功能。在CMOS电路中,输入端接电阻后接地的情况下,一般情况下是低电平。 首先,让我们先了解一下CMOS电路的基本原理。CMOS(互补

2024-01-09 11:25:51 653

653

653

653如何使ADP2164的PGOOD管脚输出高电平?

我的目的是使得ADP2164的PGOOD管脚输出高电平。

EN管脚使用示波器测得其为斜坡信号(上下峰均为4.1646V和4.076V)

VIN/TRK/SYNC/PVIN是4.9mV,RT

2024-01-08 08:16:25

LTC6813-1 pin 49 DRIVE引脚是一直输出高电平?还是周期性的高/低电平?

LTC6813-1,pin 49 DRIVE 引脚是一直输出高电平?还是周期性的高/低电平?

我司在测试的过程中发现,如果不与主MCU通信,DRIVE 输出的 是1.88s的高电平后,随即变成低电平

2024-01-03 07:26:44

无论怎么设置ADXL345_DATA_FORMAT 0x31寄存器的INT_INVERT中断有效位,2个中断脚都一直是低电平的原因?

无论怎么设置ADXL345_DATA_FORMAT 0x31寄存器的INT_INVERT中断有效位,2个中断脚都一直是低电平。

按datasheet上

INT_INVERT位值为0,设置中断至高电平

2024-01-01 06:06:35

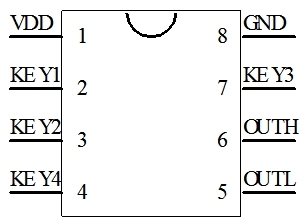

SOP-8开关电源芯片方案开发

EH2730-A948长按开关机芯片 一.功能说明 四路按键(KEY1、KEY2、KEY3、KEY4)输入控制,两路信号同步输出(可二选一)。上电状态OUTL为高电平、OUTH为低电平。 KEY1

2023-12-23 09:15:22 158

158

158

158

数字隔离器芯片哪款默认输出低电平

数字隔离器芯片是一种将输入信号隔离处理的器件。它的主要功能是在输入和输出之间提供电气隔离,以防止传递噪声、干扰和高电压等问题。在数字隔离器芯片中,默认输出低电平意味着在没有输入信号时,输出信号

2023-12-22 13:47:36 373

373

373

373AD7656高电平指的是什么?

本人初次使用AD7656。引脚接高电平是指接 VDD(12V)、AVCC(5V)、DVCC(5V)还是Vdrive(3.3V)?还是对于不同的引脚不一样?我看到的各种文献中接法不同。

另外硬件模式

2023-12-21 07:46:08

AD9220在时钟高电平下是不是一直采样但不转换,到低电平的时候才进行转换并输出?

1AD9220在时钟高电平下是不是一直采样但不转换,到低电平的时候才进行转换并输出?

2AD9220是不是在上升沿启动采样保持,到下一个上升沿开始输出(我注意到手册标注的输出延迟是从上升沿开始

2023-12-21 06:39:57

ad7656bstz busy无高电平转换信号是为什么?

你好,我用并口16,读转换数据,负电源VSS直接接到AGND上。rest 低电平后,给CONVST ABC 高电平开始转换,但是BUSY一直无高电平信号。

2023-12-18 06:36:21

当没有数据输入的时候,AD9780的DCI数据时钟输入管脚是否可以一直保持在高电平或者低电平?

您好,

当没有数据输入的时候,AD9780的 DCI数据时钟输入 管脚是否可以一直保持在高电平或者低电平?

谢谢!

2023-12-15 06:41:13

AD9224的逻辑输入高电平最低是3.5V吗?

当DRVDD使用5V时,手册上写了,AD芯片的数字输入输出是5V的逻辑电平。当DRVDD使用3.3V时,AD芯片的数字输入输出是3.3V的逻辑电平。但是当DRVDD = 3.3 V时,不知道数字输入

2023-12-14 07:09:38

有谁知道为什么AD7712的DRDY引脚一直是高电平吗?

有谁知道为什么AD7712的DRDY引脚一直是高电平吗?它不是一上电就一直工作即使没有输入,它的DRDY引脚应该会周期性的变为低电平啊?一直是高电平也就没有数据输出了。

2023-12-13 07:41:21

调试AD7173-8的时候,将CS拉低DIN保持高电平,一直等不到DOUT为低电平的状态如何解决?

在调试AD7173-8的时候,首先发送了读IP寄存器的命令,收到的回复是30D5,也即SPI通信无误。然后将CS拉低,DIN保持高电平,但是一直等不到DOUT为低电平的状态。看datasheet上说

2023-12-11 06:53:37

AD7606 busy信号一直为低电平的原因?

。请给位专家帮忙分析下问题所在。谢谢!上电后复位ADC电平 2us高电平,启动转换信号周期10us,convest低电平1us

2023-12-04 06:37:59

什么是逻辑电平?如何实现电平转换?(原理讲解+电路图)

逻辑电平是数字电子系统中的关键概念之一。它决定了信号被认定为高电平还是低电平,并进一步影响着数字电路的正确操作。逻辑电平是用来表示数字信号状态的电压水平。在数字电子系统中,常用的逻辑电平有高电平

2023-11-24 08:20:20 1672

1672

1672

1672

你知道哪些常用逻辑电平?TTL与COMS电平可以直接互连吗?

Metal-Oxide-Semiconductor)。 TTL是一种基于晶体管的数字逻辑电平标准,使用5V电源供电,逻辑高电平(1)通常在2.4V以上,逻辑低电平(0)在0.4V以下。TTL逻辑电平的优点是速度快、噪声容忍度高,常见于早期的数字电路。然而,由于功耗较大,现在更常用的是

2023-11-17 14:16:06 648

648

648

648什么是线与逻辑?要实现它,在硬件特性上有什么具体要求?

什么是线与逻辑,要实现它,在硬件特性上有什么具体要求? 线与逻辑是一种基本的数字逻辑电路,用于实现布尔代数中的逻辑运算。在线与逻辑中,当所有输入信号都是高电平时,输出信号才为高电平;否则,输出信号

2023-11-17 14:11:38 1389

1389

1389

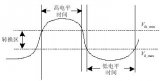

1389判断高电平,低电平和方波的几种方法

读取某一个上拉电平信号,它可能输出是低电平,可能是高电平,可能是方波,并且这个方波不知道频率何占空比,那么如何来通过程序来判断呢?高电平和低电平都好说,利用HAL库读取即可,如下

2023-11-07 08:00:52 995

995

995

995

电平触发、脉冲触发、边沿触发的区别和示例代码

是基于信号保持在特定电平的条件触发操作。通常,高电平触发(信号为高电平时触发)和低电平触发(信号为低电平时触发)是两种常见的电平触发方式。-操作持续时间:操作会持续进行,

2023-10-31 08:00:52 3407

3407

3407

3407

怎么编程去计算51单片机某个io口的输入高低电平时间?

本人是个新手刚刚接触51单片机,怎么编程去计算51单片机某个io口的输入高低电平时间,比如我从P1.0口输入了一个方波信号,那么怎么通过单片机编程去检测我这个方波高电平的时间(或者说长度),还有低电平的时间(或者说长度),这个检测时间要精确到ms。

2023-10-20 07:11:25

数字电路常见逻辑符号

信号为高电平,否则为低电平,逻辑符号为"|" 3、非门 (NOT) 有一路输入信号一路输出信号,当输入为高电平时输出为低电平,输入为低电平时输出为高电平,逻辑符号为“~” 4、与非门 (NAND) 有两路输入信号一路输出信号,当且仅当两路输入信号

2023-10-12 14:35:03 4294

4294

4294

4294为什么rs触发器可以消除机械抖动

RS触发器是一种基本的数字逻辑电路,它由两个输入(R和S)和两个输出(Q和Q‘)组成。R和S分别代表复位(Reset)和置位(Set)信号。当R和S都是逻辑低电平时,RS触发器会保持上一个状态不变

2023-09-21 15:44:05 1873

1873

1873

1873CML电平学习笔记

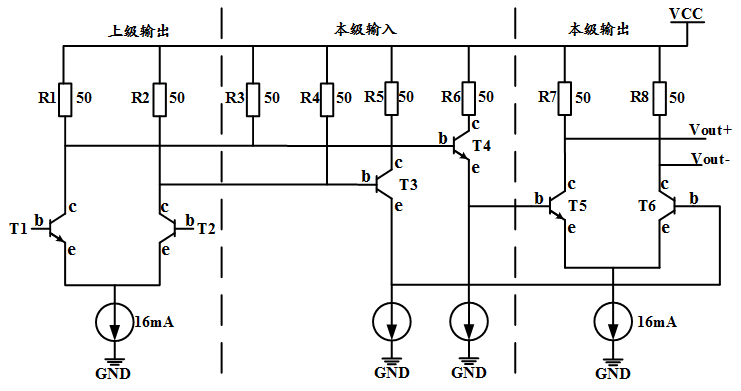

CML电路如图1 所示,输入部分为一射随器,假设T3管为N端,T4管为P端,当P大于N时即输入为高电平,反之为低电平。由于输入部分为射随器,输出端接收到高低电平的相位与输入端一致,当接收为高电平

2023-09-20 15:32:41 510

510

510

510

用逻辑笔测量信号的逻辑状态属于?

进行逻辑计算或判断,从而实现数字电路的功能。 在现代电子设备中,信号的逻辑状态往往通过逻辑电平来表示。逻辑电平分为高电平和低电平两种,通常高电平表示“1”,低电平表示“0”。“1”和“0”是数字电路中最基本的逻辑符号,

2023-09-19 17:16:11 692

692

692

692ttl与非门悬空相当于输入什么电平

端电平都为低电平时,输出端就给出高电平;在其它情况下,输出端均为低电平。TTL 与非门的功能可以表示为:Y = ¬ (A ∧ B)。其中,A 和 B 分别是两个输入电平,Y 是输出电平,¬ 是取反符号,表示将输入电平取反。 TTL NAND 门通常用于数字电路中,作为逻辑电路的基础元件

2023-09-17 15:42:18 2006

2006

2006

2006推挽输出是低电平还是高电平?

推挽输出是低电平还是高电平 推挽输出器是一种常见的输出方式。它由负和正三项组成,其中,负电平被连接到PNP晶体管,而正电平被连接到NPN晶体管。当给定输入信号时,晶体管被开启或关闭,电流流过负极

2023-08-31 10:26:31 1540

1540

1540

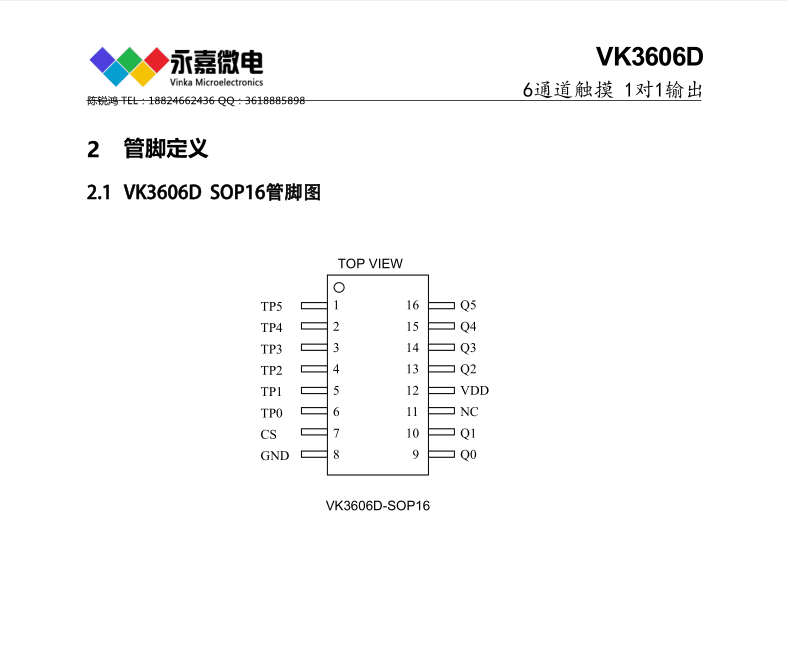

1540VK3606D高抗干扰6通道6键触摸检测芯片防呆功能,1对1直接输出低电平有效

,仅需极少的外部组件便可实现触摸按键的检测。 提供了6路1对1直接输出低电平有效。最长输出时间10S。芯片内部采用特殊的集成电路, 具有高电源电压抑制比,可减少按键检测错误的发生,此特性保证在不利环境条件的应用中芯 片仍具有很高的可靠性。 此触摸芯片具有自动校准功能,

2023-08-29 10:21:28 256

256

256

256

FH154C6电子开关芯片手册

FH154C6电子开关芯片手册

功能说明:CMOS制造工艺,低工耗。驱动能力大,适用于各种电子开关。一路按键输入控制,一路OUT低电平输出。上电输出低电平,短按开关后输出高电平,再短按按键,0UT输出低电平。再短按输出高电平,如此循环。(注:输出为延时0.5S缓慢开启)

2023-07-03 15:30:43 2

2

2

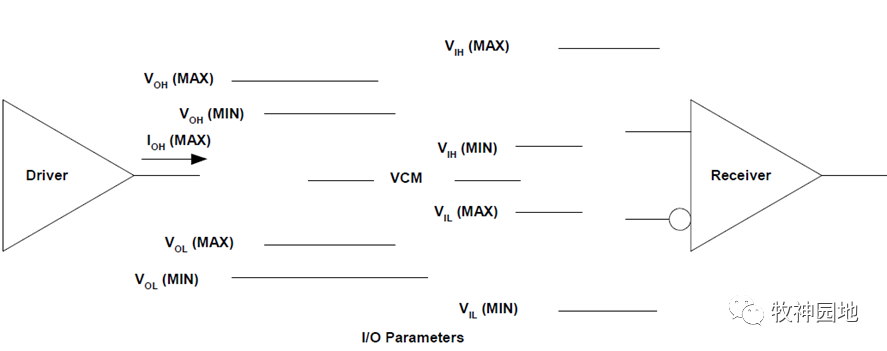

2电平设计基础:电平匹配设计

单端逻辑电平的匹配是我们平时在硬件设计中最经常碰到的,我们在《TTL&CMOS电平》章节中已经对TTL和COMS电平的匹配设计做了一些分析,一般3.3V LVTTL和LVCMOS是可以直接相互驱动的。但是其它不同逻辑电平之间呢?举个栗子,3.3V逻辑电平和1.8V逻辑电平之间呢?

2023-06-25 14:52:24 1380

1380

1380

1380

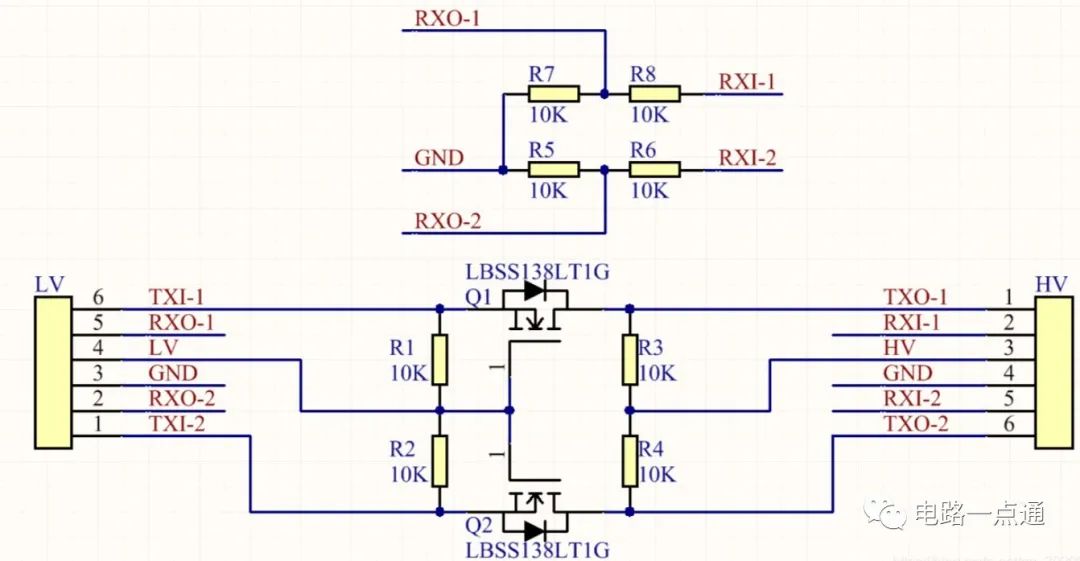

逻辑电平转换电路原理讲解

当LV连接器的TXI-1为3V3高电平信号(LV排针接3V3,HV排针接5V)时,Q1 mos管的栅极和源极之间的压降为0V(TXI-1与LV排针之间的电压),此时Q1 mos管不导通,TXO-1被R3电阻拉高,输出5V高电平。

2023-06-25 09:10:43 569

569

569

569

低静态功耗PS7A20 LDO芯片设计

芯片的电压输入引脚,建议放置一个100nf陶瓷电容滤波。 PIN.2: 芯片输出使能引脚,高电平打开输出,低电平关闭输出。

2023-06-14 09:16:07 784

784

784

784

使用K312芯片测试Wakeup功能时,如何在唤醒时保持输出端高电平?

我在使用K312芯片测试Wakeup功能时,发现OutPut输出的GPIO在进入待机后可以保持高电平输出,但唤醒后会变为低电平。

下面是我的设置:

1. 使用DS工具在Power组件中

2023-06-09 06:59:11

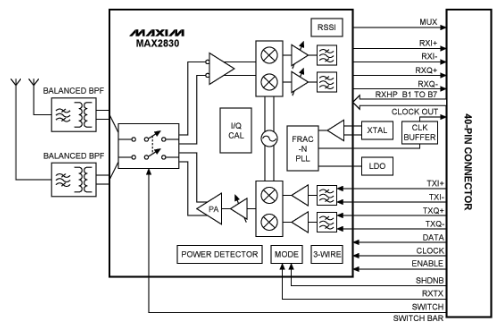

MAX2830 WLAN参考设计

工作条件为:Vcc= 2.85V;V。.BAT = 3.3V; fRF = 2.437GHz; 根据工作模式设置RXTX和低电平有效SHDN; 低电平有效CS = 高电平; SCLK

2023-06-08 15:12:26 249

249

249

249

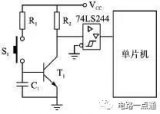

单片机I/O的常用驱动与隔离电路设计

一般输入信号最终会以开关形式输入到单片机中,以工程经验来看,开关输入的控制指令有效状态采用低电平比采用高电平效果要好得多,如图1如示。当按下开关S1时,发出的指令信号为低电平,而平时不按下开关S1时,输出到单片机上的电平则为高电平。该方式具有较强的耐噪声能力。

2023-05-30 09:06:44 1775

1775

1775

1775

高电平和低电平是什么意思?区别是什么?

高电平和低电平是数字电路中经常会出现的专业名词,它们所表面的意思就是电路上有和无,两者之间没有中间值,在不同的电路上,电压的具体值也是各不相同的。如果用简单的语言表达它们的意思就是开和关,平时

2023-05-26 10:17:30 24015

24015

24015

24015

如何复用配置GPIO_AD0作为普通的GPIO口输出高电平或低电平?

在RT1011芯片上,我想复用配置GPIO_AD0作为普通的GPIO口输出高电平或低电平。你能给我一个例子或一些参考文件吗?

2023-05-05 06:56:06

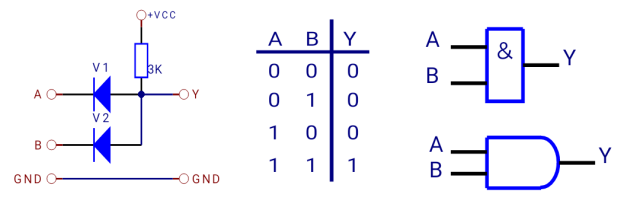

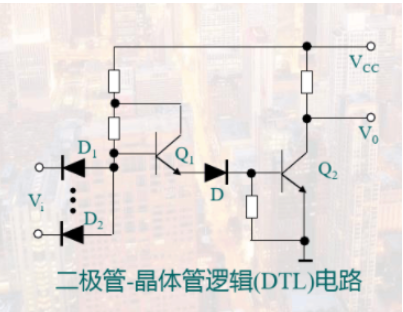

逻辑门电路的原理及组成

逻辑门可以用电阻、电容、二极管、三极管等分立原件构成,成为分立元件门。也可以将门电路的所有器件及连接导线制作在同一块半导体基片上,构成集成逻辑门电路。简单的逻辑门可由晶体管组成。这些晶体管的组合可以使代表两种信号的高低电平在通过它们之后产生高电平或者低电平的信号。

2023-04-30 17:49:00 4912

4912

4912

4912逻辑门电路基本知识

关于逻辑电路的几个规定

①有关高电平,低电平的规定;

在逻辑电路中,电位的高低常用高电平,低电平来描述,单位也用“V”表示。实际的高电平和低电平都不是一个固定的数值,因此通常规定一个电平

2023-04-30 16:41:00 3484

3484

3484

3484

为什么LM324做比较器的时候输出总是高电平呢?

我想用LM324做比较器,在反向输入端加一个4V的参考电压,正向输入端随电平的变化而输出高低电平,图中A点是用来取样电压,由于是PNP三极管,当LM324输出一个低电平时,由于低电平会使PNP导

2023-04-25 16:22:23

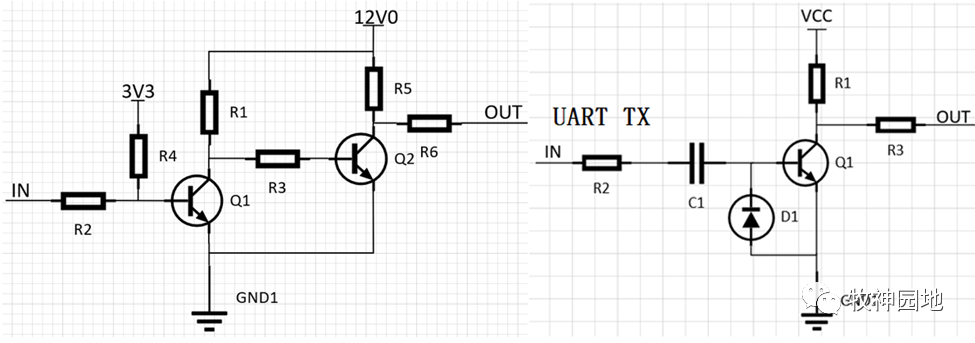

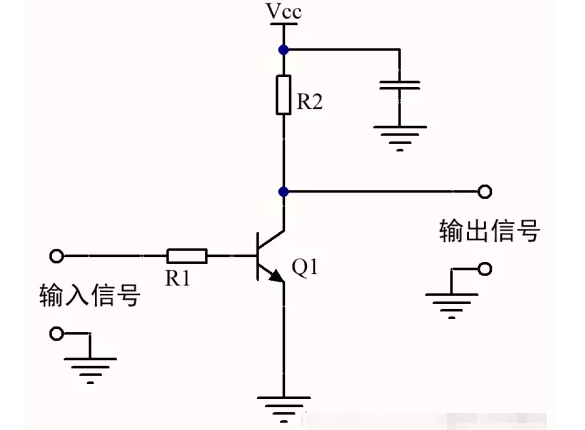

三极管电平转换电路设计

在数字电路的领域,常常把电压简化为电平,来描述逻辑状态。比如TTL电平信号规定,+5V等价于逻辑“1”,也称为高电平,0V等价于逻辑“0”,也就是低电平。数字电路里,只有0和1两个状态。其实从0V

2023-04-20 14:35:09 1739

1739

1739

1739

如何将LS1046A的RCW配置为高电平有效IRQ1和IRQ2中断?

我需要将 LS1046A 的 RCW 配置为高电平有效 IRQ1 和 IRQ2 中断。有人可以告诉我如何设置它们吗?我对 LS1046A 还是很陌生。

2023-04-17 07:21:47

运算放大器和电压比较器的工作原理分析

比较器的原理挺简单,目的是比较两个输入端的电压大小,若正输入端的电压为a,负输入端的电压为b,则当a>b时,输出为高电平(逻辑1);当a<b时,输出为低电平(逻辑0)。

2023-04-12 16:09:55 3372

3372

3372

3372STM32F1和F4的区别?STM32的ADC系统的功能特性

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high。

2023-04-10 16:21:34 4807

4807

4807

4807imx8mm spi芯片选择不会保持低电平是为什么?

我可能遇到了 spi 驱动程序的问题。我正在尝试读取和写入 eeprom,但是当读取过程开始时,芯片选择不会保持低电平,而是返回高电平并在每个传输字节后取消选择芯片。结果,eeprom 停止读取

2023-04-06 06:50:40

stm8和stc单片机比较 单片机的输出信号是什么电平 stm8s单片机采用那种电平

单片机的输出信号电平可以是高电平(通常为Vcc电压,即正电源电压)或低电平(通常为GND电压,即接地电压),具体取决于单片机的设计以及输出端口的连接方式。

2023-04-01 15:55:36 2379

2379

2379

2379如何使用emios的GPIO模式输出S32K312芯片PTA24引脚的高电平或低电平?

如何使用emios的GPIO模式输出S32K312芯片PTA24引脚的高电平或低电平

2023-03-31 06:40:06

如何使gpio引脚为高电平和低电平?

我想将一个 GPIO 引脚(即 A17)设置为高电平和低电平。如果一个条件为真,我将 A17 设置为高,否则 A17 为低。我为 A17 配置了输出方向的时钟。我尝试

2023-03-27 07:05:14

LS1046a上的Linux如何使IRQ00..IRQ02低电平有效?

ARM 手册中找不到关于支持类型限制的任何限制。它专门讨论了可能是高电平有效或低电平有效的电平敏感中断。所以我不知道这个限制是从哪里来的。谁能给我指出一份解释其起源的文件?继续,我注意到在

2023-03-24 06:45:09

电子发烧友App

电子发烧友App

评论