Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 213

213 电子发烧友网站提供《适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表.pdf》资料免费下载

2024-03-13 13:53:03 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0 电子发烧友网站提供《TPS65295完整 DDR4 存储器电源解决方案数据表.pdf》资料免费下载

2024-03-06 10:17:54 0

0 FPGA设计高级技巧 Xilinx篇

2024-01-08 22:15:53

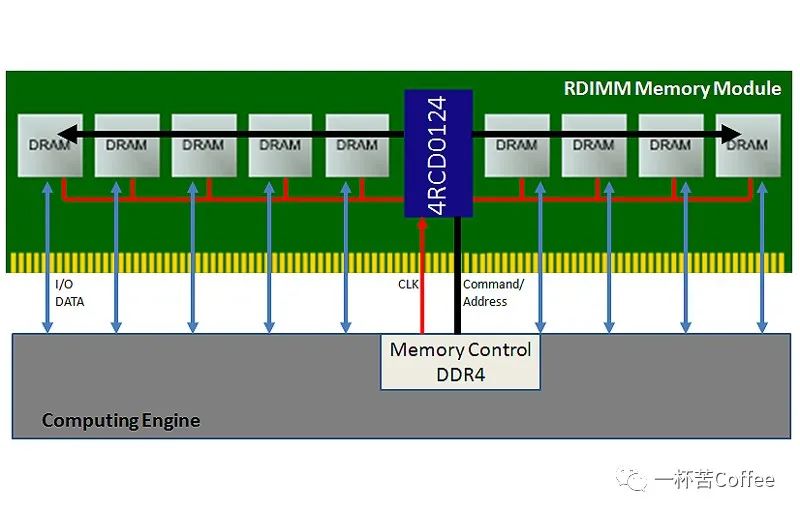

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 463

463

架构,包含2个FTC664核和2个FTC310核,其中FTC664核主频可达1.8GHz,FTC310核主频可达1.5GHz。主板板载64位 DDR4内存,分2G和4G两个版本,支持SD或者eMMC外部

2024-01-02 22:43:09

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-23 09:24:37

通过在时钟上升沿和下降沿的同时传输数据,实现了比传统SDRAM更高的传输速率。目前,市场上主要有DDR、DDR2、DDR3、DDR4等几代DDR内存。

2023-12-11 09:27:49 320

320 PCB的DDR4布线指南和PCB的架构改进

2023-12-07 15:15:58 755

755 DDR4(第四代双倍数据速率同步动态随机存取存储器)是一种高带宽的存储器,今天主要讲述一下DDR4在Layout过程中的一些细节。在DDR的设计过程中,DDR的Layout是十分重要的环节。

2023-11-29 15:39:10 1470

1470

对于ddr5市场的发展,威刚表示,现阶段观察到需求端春燕来临,主要来自pc,随着顾客需求的明显好转和pc内存内容的提高,明年上半年ddr5将超过ddr4,形成黄金交叉。目前在现货市场上,ddr5的单价比ddr4高4-50%,从威强的情况来看,ddr5比重的上升有助于总利润率。

2023-11-24 10:38:38 217

217 Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

主板的逻辑控制核心是海思8K超高清移动摄像头SoC,配合莱迪思半导体的FPGA ,加上Macronix 的串行闪存 ISSI 的 DDR4 SDRAM 内存

2023-11-13 11:46:05 2576

2576

罗彻斯特电子携手AMD/Xilinx,为Xilinx传统FPGA和相关配置PROM产品提供供货支持。

2023-11-07 09:04:42 250

250 ZYNQ器件中为1.8v。

(3) Vccpll为内部锁相环供电电压。

(4) Vcc_mio0为PS的MIO0 BANK的基准电压,VCCO_DDR为PS端的DDR的电压,此电压通常和选择的DDR颗粒

2023-11-03 11:08:33

DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR

2023-10-30 09:22:00 3886

3886 电子发烧友网站提供《基于FPGA的一种SDRAM控制器简易化设计方法.pdf》资料免费下载

2023-10-26 09:08:37 0

0 飞腾派是由飞腾携手中电港萤火工场研发的一款面向行业工程师、学生和爱好者的开源硬件,采用飞腾嵌入式四核处理器,兼容ARM V8架构,板载64位 DDR4内存,分为2G和4G两个版本。主板板载WiFi

2023-10-25 11:44:22

;

•DSP 外挂一路千兆以太网1000BASE-T;

•FPGA处理器采用Xilinx VirtexUltralSCALE+ 系列芯片XCVU9P;

•FPGA外挂2组DDR4 ,每组2GB,64bit

2023-10-16 11:12:06

做高速链路的小伙伴都知道,Stub总是会带来各种影响,或者导致阻抗突变,或者导致插入损耗曲线上存在谐振,等等。本文介绍了Via stub在DDR4并行链路上的表现。下面是论文的全文。

2023-10-09 10:35:30 321

321

摘要:本文将对DDR3和DDR4两种内存技术进行详细的比较,分析它们的技术特性、性能差异以及适用场景。通过对比这两种内存技术,为读者在购买和使用内存产品时提供参考依据。

2023-09-27 17:42:10 1088

1088 DDR4 3200和3600是内存模块的频率标准,表示其频率值,具有以下差异

2023-09-26 15:24:18 8981

8981 电子发烧友网站提供《PIC32系列参考手册之DDR SDRAM控制器.pdf》资料免费下载

2023-09-25 11:39:59 0

0 电子发烧友网站提供《具有最大1Gb DDR2 SDRAM的SAMA5D2 SIP MPU.pdf》资料免费下载

2023-09-25 10:11:12 0

0 相对于DDR3, DDR4首先在外表上就有一些变化,比如DDR4将内存下部设计为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过渡,这样的设计可以保证金手指和内存插槽有足够的接触面

2023-09-19 14:49:44 1484

1484

三星公司计划在下半年再次削减DRAM制程的产能,而今年以来这一减产主要针对DDR4。业界普遍预期,三星的目标是在今年年底之前将库存水平降至合理水平。这一减产举措可能会导致DDR4市场价格上涨,而目前

2023-09-15 17:42:08 996

996 Xilinx是一家专业的可编程逻辑器件(PLD)厂商,其产品包括FPGA、CPLD、SOC等。Xilinx的FPGA产品线有多个系列,其中7系列和Ultrascale系列是比较常见的两种。那么,这两个系列有什么区别呢?

2023-09-15 14:44:54 1765

1765

随着英特尔和amd将新的pc/笔记本电脑和服务器平台更换为ddr4, ddr4的需求开始减少。因此,三星大幅减少ddr4的生产,转向ddr5,试图巩固业界第一的位置。

2023-09-15 11:40:33 555

555 本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1952

1952

电子发烧友网站提供《面向Xilinx FPGA和SoC的超快设计方法指南.pdf》资料免费下载

2023-09-14 10:02:31 1

1 电子发烧友网站提供《Teledyne e2v的宇航级DDR4的硬件设计指南.pdf》资料免费下载

2023-09-13 17:14:55 1

1 上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

2023-09-13 12:29:37 654

654

电子发烧友网站提供《基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响.pdf》资料免费下载

2023-09-13 09:56:49 0

0 本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 743

743

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

2023-08-26 11:57:42 2050

2050 / O 端口和DDR4 内存,适用于

各种不同的可编程应用,带有ZU27DR FPGA 的ZXB-RFSOC-2T2R 由 4 路12 位,采样率

4.0GSPS ADC 和 4 路14 位,采样率

2023-08-25 15:11:55

DDR4 3200和DDR4 3600是两种常见的内存频率规格,它们在性能上会有一定的差别,但差别大小取决于具体的应用场景和系统配置。

2023-08-22 14:45:05 28274

28274 适用于需要将小型处理器集成到FPGA中的深度嵌入式应用。

该处理器实现ARMv6-M架构,并与用于ASIC实现的Cortex-M0和Cortex-M0+处理器密切相关。

本章介绍了Cortex-M1 DesignStart FPGA-Xilinx版的功能和目录结构。

2023-08-16 06:10:25

我手上有一张DDR200T的开发板,板载了一块512M的SDRAM内存,板子烧了一个UX600的demosoc,我是要在这个板子跑RT-Thread。

要是想使用这块SDRAM应该怎么做呢?应该

2023-08-11 08:05:46

PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

使用DDR4作为外接存储单元时,蜂鸟e203的访问地址为0x40000000,但是经过vivado的Block design后使用DDR4,在板子上跑测试DDR4读写程序,报store访问异常

2023-08-11 06:17:58

DDR5的主板不支持使用DDR4内存。DDR5(第五代双倍数据率)和DDR4(第四代双倍数据率)是两种不同规格的内存技术,它们在电气特性和引脚布局上存在明显差异。因此,DDR5内存模块无法插入DDR4主板插槽中,也不兼容DDR4内存控制器。

2023-08-09 15:36:25 12804

12804 xilinx平台DDR3设计教程之设计篇_中文版教程3

2023-08-05 18:39:58

64-bit DDR4,总容量达4GB,可稳定运行在2400MT/s,PL端支持两组64-bit DDR4,每组容量均为4GB,最高运行速率支持2666MT/s;板

2023-08-04 10:33:46 267

267

以下内存设备:

•双倍数据速率3(DDR3)SDRAM。

•低压DDR3 SDRAM。

•双倍数据速率4(DDR4)SDRAM。

2023-08-02 11:55:49

内存设备:

•双倍数据速率3(DDR3)SDRAM。

•低压DDR3 SDRAM。

•双倍数据速率4(DDR4)SDRAM

2023-08-02 08:30:00

电子发烧友网站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用.pdf》资料免费下载

2023-07-24 09:50:47 0

0 DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。

2023-07-16 15:27:10 3365

3365

OFDM中调制使用IFFT,解调使用IFFT,在OFDM实现系统中,FFT和IFFT时必备的关键模块。在使用Xilinx的7系列FPGA(KC705)实现OFDM系统时,有以下几种选择。

2023-07-10 10:50:52 604

604

DDR是DDR SDRAM的简称,只是人们习惯了称之为DDR,全称为Double Data Rate Synchronous Dynamic Random Access Memory,中文名为:双倍速率同步动态随机存储器,同步是指需要时钟。

2023-06-25 15:06:40 4905

4905

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5524

5524

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。 与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 1024

1024 [APEE] 已设置

DDR_SDRAM_CFG2[AP_EN] 已设置

第2步:

DDR_ECC_ERR_INJECT[APIEN] = 1

第 3 步:

读取 DDR_ERR_DETECT 中的 APE 位

APE 的读取值为零。

2023-05-31 06:13:03

Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

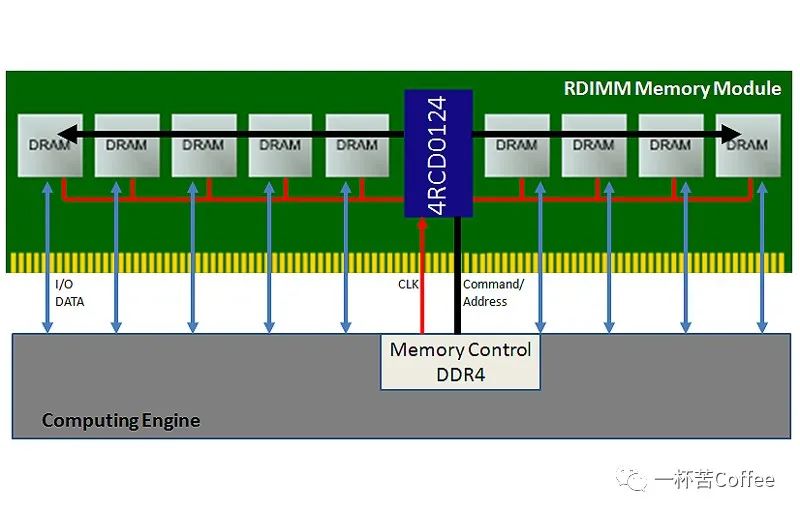

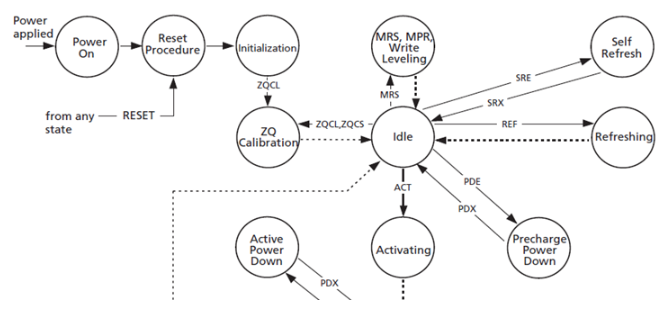

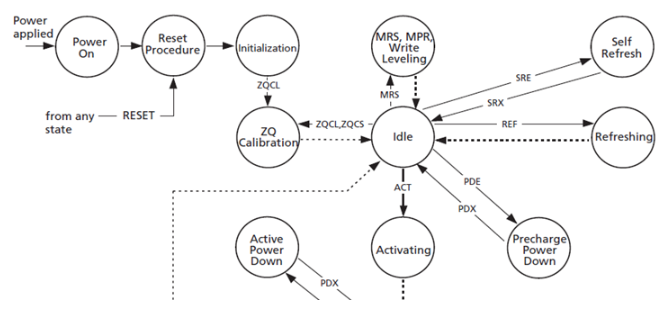

0 1 – DDR3 SDRAM JEDEC 标准 JESD79-3F 状态图和图 2 – DDR4 SDRAM JEDEC 标准 JESD79-4 状态图所示。

2023-05-26 18:02:27 996

996

DRAM 连接32位SDRAM时,最大支持64Mx32bit?

2023-05-26 07:27:07

S32G3开发板上使用的ddr芯片是micro MT53E1G32D2FW-046 AUT: B

但是我们的开发板使用的是三星的芯片(K4FBE3D4HM THCL)。

如何查看 S32G3 支持的 DDR 芯片?。以及如何支持新的DDR芯片?

2023-05-23 07:15:48

MES50HP 开发板简介

MES50HP 开发板集成两颗 4Gbit(512MB)DDR3 芯片,型号为 MT41K256M16。DDR3 的总线宽度共为 32bit。DDR3 SDRAM 的最高

2023-05-19 14:28:45

我们想在 16 位模式下使用带 DDR4 的 LS1043A 定制板。关于这一点,请按照附件文档确认 LS1043A 和 DDR4 之间的接口连接。

16位模式下MA14\\\\MBG1有什么用。

2023-05-17 11:21:19

我有一块自制的imx8mp主板,使用DDR4的型号是:K4ABG165WA-MCWE,单片容量32Gb,主频3200Mhz,我的主板使用了两颗芯片,但是使用MX8M_Plus_DDR4_RPA_v9.xlsx无法完成配置

2023-05-17 06:12:25

DDR4内存模块支持单个64位通道(如果考虑ECC,则为72位通道)。相比之下,DDR5内存模块配备了两个独立的32位通道(40位ECC)。

2023-05-08 10:27:44 1331

1331 /MCK0_B) 感到有点困惑。

在上一代相同的主板上,启动并运行不同的 DDR4 内存,我们可以按预期测量 DDR 时钟。

我们了解 NXP 是否无法支持特定的内存配置,但我们想知道在 LS1046A

2023-05-06 08:20:49

使用 MIMXRT1024CAG4B 并计划在我们的设计中连接一个 8 位 SDRAM ( IS42S86400F-7TLI )。我可以从 A0 配置 8 位 SDRAM 的地址引脚吗?或者在配置这些地址引脚时是否有任何特定的限制?

2023-04-28 08:58:11

MIPI 接口现在非常流行,国产FPGA目前基本都带MIPI接口,而AMD-Xilinx是从U+系列开始支持MIPI电平,从国内使用情况来看,7系列FPGA是使用最广的器件,所以这次使用的FPGA是7系列FPGA使用电阻网络实现MIPI电平的例子。

2023-04-24 09:30:06 3710

3710

我有 LS1046AFRWY 板的克隆。高速公路板使用 MT40A512M16JY-083E:B(商业级DDR4)。我的克隆使用 MT40A512M16JY-083E IT:B(工业级 DDR4

2023-04-24 08:08:20

将 DDR4 内存添加到 imx8mp

2023-04-20 10:59:17

NXP IMX8M Mini DDR4 校准

2023-04-20 07:36:55

Multimedia Processor for Mobile Applications (EMMA Mobile1) DDR SDRAM Interface 用户手册 (R19UH0028EJ0500_EMMAMOBIL)

2023-04-18 19:47:17 0

0 电路板设计和布局指南......................... 62.1 DDR4 简介........................... 62.2 支持的 DDR4 器件实现

2023-04-14 17:03:27

2 组 64bit 的DDR4 SDRAM,每组容量2GB,可稳定运行在2400MT/s。支持PCIE Gen3 x8模式及一路FMC HPC接口。同时可提供 Windows,Linux 上位机驱动

2023-04-13 15:56:21

组DDR4 SDRAM缓存单元,每组最大支持4GB容量,72bit(包含ECC,8bit),可实现进行复杂逻辑与算法时的数据缓存。PCIe总线最大支持Gen3、x8,具备超强的数据吞吐能力;前面板预留

2023-04-08 10:38:05

IC SDRAM DDR4 FBGA

2023-04-04 20:41:52

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

你能告诉我在哪里可以获得 i.MX8M Plus 的详细 DDR4 布局跟踪路由指南吗?我在 i.MX8M Plus 硬件开发人员指南中找不到它。顺便问一下,NXP 有带 DDR4 的 i.MX8M Plus 评估板吗?

2023-03-31 07:52:02

Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 4751

4751 需要加上一个控制模块。控制模块中需要符合一定的项目设计规则。 SDR SDRAM是支持页突发的,可以一次进行整行数据的输入或者读出。当有大量数据时,页读和页写是经常用到的。 页读和页写并不是每次都必须

2023-03-27 17:09:14

支持所有Xilinx器件下载 包括FPGA CPLD ISP Configuration PROM 下载接口电压:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

你好 我们正在使用 4 * 2GB DDR4 芯片构建我们的定制 ls1046a 板。(我们参考LS1046AFRWY,容量翻倍,去掉ECC)首先我生成了 BL2 二进制文件制作 PLAT

2023-03-24 08:50:43

SDRAM支持读写的长度为1、2、4、8和一行(整页)。

具体的SDR SDRAM的介绍可以查看手册。下面只介绍几个相对重要的时序图。

在SDR SDRAM正常使用之前,需要进行初始化。初始化

2023-03-23 17:40:58

IC SDRAM DDR4 FBGA

2023-03-23 13:08:42

IC SDRAM DDR4

2023-03-23 13:08:37

电子发烧友App

电子发烧友App

评论