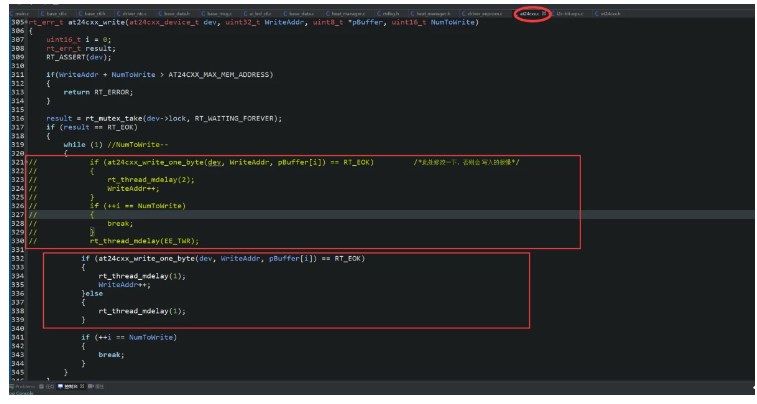

是我的代码,我会加注释的,方便大家查看。

系统时钟是72MHZ,芯片型号是STM32F103RE

#define FRAM_WREN_INST0x06 //设置写使能

#define

2024-03-20 08:08:05

pktend_n信号拉低一个周期,按照对AN65974的理解,这里应该为发送1024B之后再发送一个零数据包(ZLP)来包装缓冲区,这里如果我没有延迟紧跟着将pktend_n信号拉低一个周期,则在

2024-02-28 07:45:10

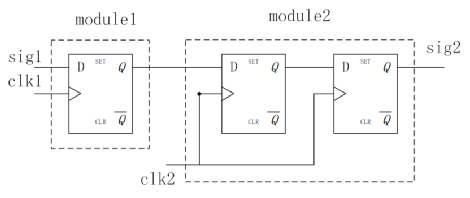

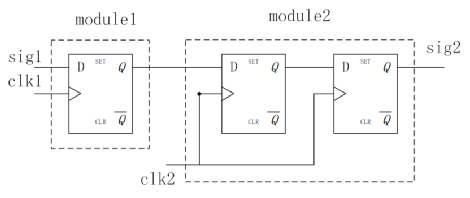

时钟传播延迟Latency,通常也被称为插入延迟(insertion delay)。它可以分为两个部分,时钟源插入延迟(source latency)和时钟网络延迟(Network latency)。

2024-02-27 11:20:03 173

173

嗨

如何调整时钟或数据通道的 mipi 定时延迟?

2024-02-27 08:26:24

dma_wm_thn 这样的过渡触发器需要一些周期的延迟才能断言吗?

在我的实践中,DMA_WM_THN 触发器似乎有 1 个时钟周期延迟:

图像是我的状态机的一部分,数据总线是 32 位

2024-02-23 07:43:36

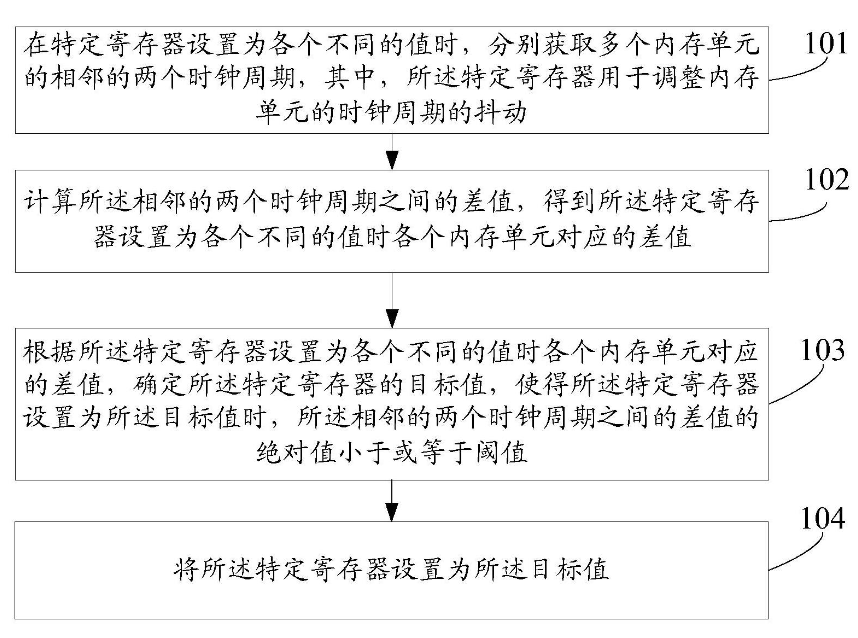

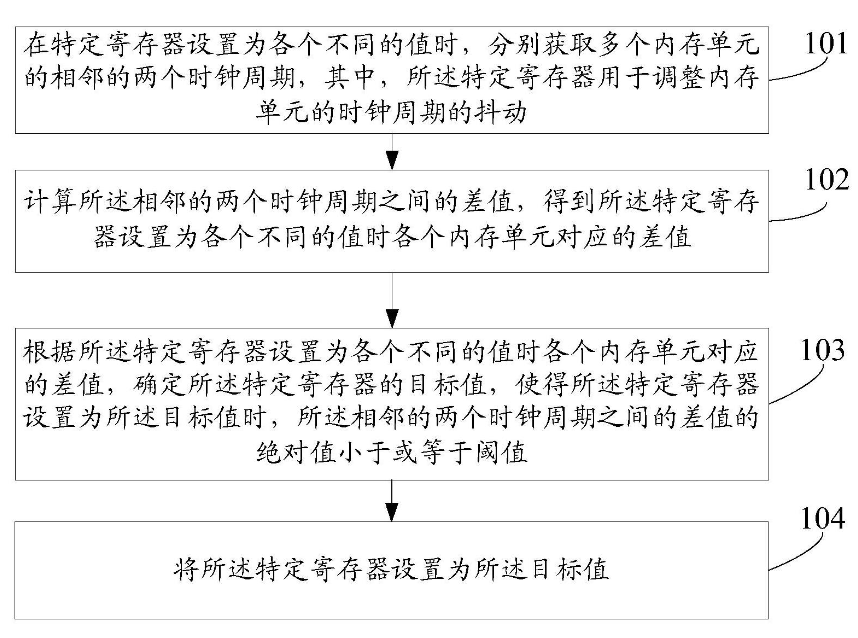

该专利主要涉及到通过对特定寄存器进行调整来减少内存时钟周期的抖动问题,其可以帮助主板制造商进一步提升时钟周期的稳定性与一致性,以及主板稳定性测试的优良率。

2024-02-21 09:42:13 106

106

FRAM的“耐力”定义为疲劳后的记忆状态保持能力,或在许多开关周期后维持铁电开关电荷的非易失性部分的能力。

2024-02-19 10:21:17 79

79

电子发烧友网站提供《系统时钟温度补偿AN-B-100应用说明.pdf》资料免费下载

2024-01-31 10:10:30 0

0 我正在使用 TC377 主板,我想分析一个功能。 它运行多少个时钟周期? 不知道该怎么做。

2024-01-30 08:09:44

是一个周期性的方波,每个周期都分为高电平(或1)和低电平(或0)两个状态。在每个周期的上升沿或下降沿,电路中的操作被触发执行。时钟信号的频率决定了电路的操作速率,也称为时钟频率。 产生时钟信号的方法取决于特定应用的要求

2024-01-25 15:40:52 900

900 当我发送读取请求或 RDID 请求时,我没有收到从 FRAM 芯片返回的数据。

我不确定自己做错了什么。

我已经将我的波形 HOLD_N、CS_N、FRAM 中的串行数据、串行数据附加到 FRAM、CLK、WP_N 中。

2024-01-25 07:07:12

你好,我们看到一种奇怪的行为,即稳压器输出 VDP 和调试时钟在运行模式下关闭并再次循环开启。 你能帮忙解决问题吗?

更新:

ADC 通道配置不正确。 Channel0 已在软件中更新,但是 Channel3 是在 Configwizard 中配置的。 这会造成问题吗?

2024-01-19 06:52:03

一、接口说明

接口名

接口描述

startWork(work: WorkInfo): void;

申请延迟任务

stopWork(work: WorkInfo, needCancel

2024-01-17 17:53:42

台仪器上的两个时钟信号减去。为了完成这一步骤,可以按照以下过程进行: 1. 准备好一个出现快速变化的测试信号源。这样可以在测量过程中更容易观察到延迟的差异。 2. 将测试信号源连接到差分探头的输入端口,并将差分探头的输出

2024-01-17 11:32:17 238

238 的时钟在一开始很可能并不完全一致,这可能是由于硬件差异、通信延迟、时钟漂移或其他因素引起的。因此,时钟同步对于网络中各个节点的协同操作具有重要意义。在网络中实现时钟同步有许多不同的方法和协议可供选择,我们将在

2024-01-16 15:10:13 168

168 一、功能介绍

应用退至后台后,需要执行实时性要求不高的任务,例如有网络时不定期主动获取邮件等,可以使用延迟任务。当应用满足设定条件(包括网络类型、充电类型、存储状态、电池状态、定时状态等)时,将任务

2024-01-16 14:57:24

假定使用内部32.768Khz振荡频率,倍频至10.24MHZ,内核频率为一分频即10.24MHZ,那么一个指令周期是多少?一个指令周期为几个机器周期?一个机器周期为多少个振荡周期?

若定时器1使用32768HZ作为时钟源,那么定时一秒为什么是0x8000(32768*4)而不是0x2000(32768)呢

2024-01-15 07:22:24

在说明这几种定义之前,我们先来对时钟,也就是clock的周期做一个定义。

2024-01-08 13:30:10 171

171

单片机芯片的程序写入是通过将程序代码写入单片机芯片的非易失性存储器(如Flash)中实现的。 在计算机科学和电子工程领域,单片机是一种集成电路,它集成了处理器核心、内存、输入/输出接口等组件

2024-01-05 14:06:26 1445

1445 富士通嵌入FRAM的RFID射频芯片MB89R118C的优点:• 抗金属,可在金属环境中使用。• 可耐200度高温。• 高速数据写入:可提高数据写入时的效率。• 稳定的通信距离

2023-12-27 13:53:33

开启了过零中断和线周期中断,可是没有过零中断产生,只有周期中断产生,用示波器测了channel2的两个管脚的波形是周期为20ms的正弦波。而读取电压寄存器一直是一个恒定的小值,无论有没有加电压信号。这是什么问题?期待解答!

2023-12-27 07:05:13

功能,并提供一些实例演示。 LabVIEW多列列表框数据写入功能简介 1.1 LabVIEW多列列表框简介 多列列表框是LabVIEW中一种常用的界面控件,它可以同时显示多个列的数据,并提供对这些数据进行编辑的能力。我们可以通过多列列表框将数据以表格的形式呈现。 1.2 多列列

2023-12-26 13:49:26 1042

1042 一直是零。下面是FPGA输出的片选CS信号,和时钟信号,时钟信号频率为97KHz,采样频率为500Hz。

图1 片选信号与时钟信号,3个周期

图2 片选信号与时钟信号,1个周期

图1 片选信号与输出信号,3个周期

图1 片选信号与输出信号,1个周期

2023-12-21 06:37:20

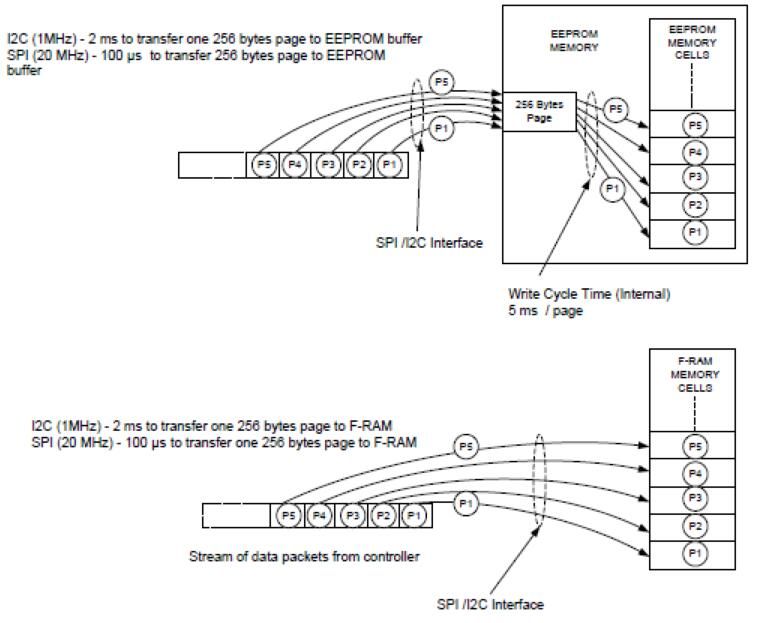

FRAM具有其他传统内存产品所不具备的四个突出特性。特点是:“非易失性”、“高读写耐久性”、“写入速度快”和“低功耗”。

2023-12-15 11:35:46 412

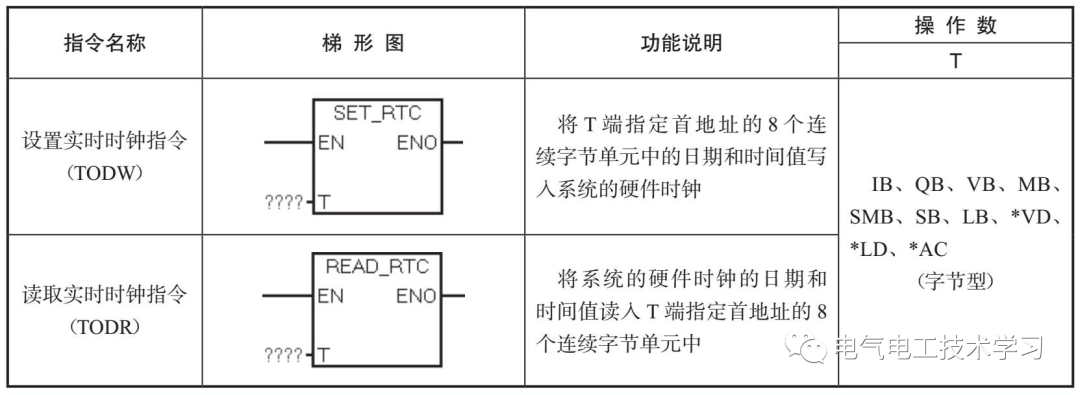

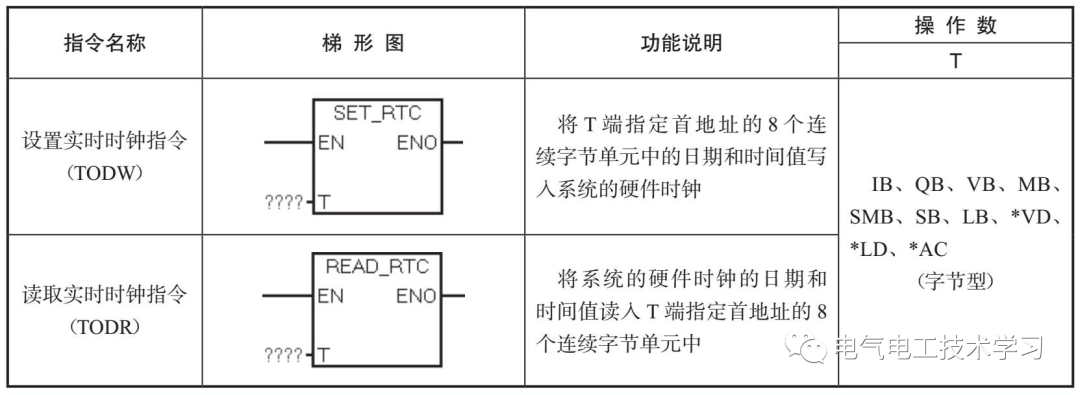

412 时钟指令的功能是调取系统的实时时钟和设置系统的实时时钟,它包括读取实时时钟指令和设置实时时钟指令(又称写实时时钟指令)。这里的系统实时时钟是指PLC内部时钟,其时间值会随实际时间变化而变化,在PLC切断外接电源时依靠内部电容或电池供电。

2023-12-13 13:45:46 1959

1959

给S1200,不得已又在机械轴上添加了一个绝对值编码器(可以选MODBUS,DP或者485协议的),直接连接到PLC中来,以便监视伺服电机的实际位置值; 此外系统有一个寻零光电开关

1. 当我执行寻零时

2023-12-11 07:33:28

的模拟信号大于0时,最高位为1,即输出的数值大于2047,当采样的模拟信号小于0时,最高位为0,即输出的数值小于2047。

从上面两张图可以看出来,输入模拟量的过零点到AD9238最高位的跳变均超过2us。

数据手册上说7个时钟周期后输出。

2023-12-11 07:08:18

使能MCLK_CNT_EN 后延迟一段时间读取MCLK_COUNT寄存器他的值一直为0,

时钟源我使能的是00,

那为什么我读上来的MCLK_COUNT寄存器的值为零?

请帮忙回答一下,谢谢

2023-12-11 06:26:55

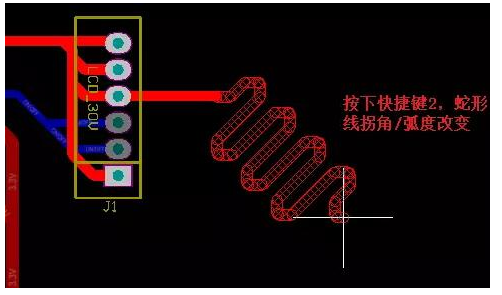

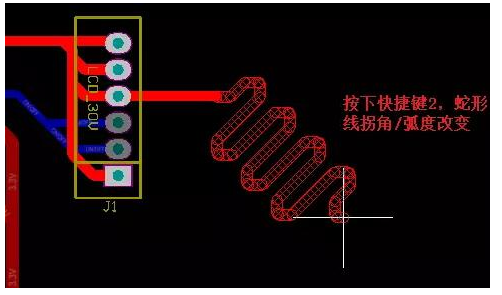

高速数字PCB板的等线长是为?使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差?超过1/4时钟周期,单位长?

2023-12-08 15:20:52 174

174

专家您好,

我参照AD2S1210的官方例程,对寄存器进行写入,写入后第一次读取显示正确,第二次再读取时,读回来的值为零,这是什么原因?中间没有其他操作,两次读取在一起。

下面是读写代码,麻烦帮忙

2023-12-05 07:20:19

AD9629的2路输出数据和时钟都是周期性的有无,真是见鬼了。

这个可能是哪方面的问题?硬件和SP配置也查了很长时间了,这个错误是哪方面的错误引起的?多谢。

2023-12-01 07:22:48

AD2S1200解码芯片使用时,正常5V给芯片供数字电和模拟电,CS拉低使能,EXC输出引脚正弦电压经过几个周期后置零,请问是什么问题? 或者单纯想看励磁引脚正弦波形,还需要什么配置

2023-12-01 06:19:33

电子发烧友网站提供《零延迟时钟定时技术应用笔记.pdf》资料免费下载

2023-11-28 14:25:22 0

0 围绕该特性展开的系统设计极为关键,因为从模拟采样点到处理模块之间的任何延迟失配都会使性能下降。对于交错式处理而言,样本对齐同样是必需的;在交错式处理时,一个转换器样本后紧跟另一个样本,且时间仅为一个时钟周期中的一小部分。...

2023-11-27 17:24:02 0

0 掌握实用的计算公式是电气工作者应具备的能力,但公式繁多应用时查找不方便,下面将整理和收集的一些常用的实用公式和口诀整理出来,并用实例说明和解释。

2023-11-17 14:46:02 401

401 我之前写的一篇文章《西门子SCL编程实例——(电机)周期性运行》收到小伙伴反馈。

2023-11-07 09:05:13 311

311

什么是时钟周期?机器周期?指令周期?它们之间的关系?

2023-10-27 07:51:56

什么是时钟电路?什么是脉冲?时钟电路是如何生成脉冲的? 时钟电路是一种电路,它产生的周期性的信号被用作计算机系统的基准。时钟电路产生的信号被称为时钟脉冲或时钟信号。在计算机系统中,时钟信号用于同步

2023-10-25 15:14:17 795

795 闪存零等待区(ZW)和非零等待区(NZW)有何区别?请说明。

2023-10-20 07:01:33

单周期cpu和多周期cpu的区别 多周期cpu和流水线的区别 单周期CPU和多周期CPU的区别 单周期CPU是指在CPU执行指令时,每个指令都需要一个固定的时钟周期来完成,这个时钟周期被称为

2023-10-19 16:53:23 5041

5041 对于做快速存储采集数据类产品的用户来说,在处理突发掉电情况时需要保存现有数据并避免数据丢失,这种情况下有很多种解决方案,铁电存储器(FRAM) 就是个很好的选择。FRAM是一种具有快速写入速度

2023-10-19 09:28:15

FPGA在一个时钟周期可以读取多个RAM数据吗?如何理解FPGA中存放程序的RAM? FPGA在一个时钟周期可以读取多个RAM数据 FPGA中的RAM是FPGA中存储数据的主要形式之一,许多FPGA

2023-10-18 15:28:20 597

597 clock驱动实例 clock驱动在时钟子系统中属于provider,provider是时钟的提供者,即具体的clock驱动。 clock驱动在Linux刚启动的时候就要完成,比 initcall

2023-09-27 14:39:35 367

367

对于做快速存储采集数据类产品的用户来说,在处理突发掉电情况时需要保存现有数据并避免数据丢失,这种情况下有很多种解决方案,铁电存储器(FRAM)就是个很好的选择。FRAM是一种具有快速写入速度

2023-09-22 08:01:59 496

496

的基础,因此,在电子学领域中,如何产生和控制时钟信号是一项至关重要的技术。 时钟信号是指一个周期性的方波信号,其周期性能和稳定性非常重要。为了使时钟信号精确可靠地产生,需要考虑多种因素的影响,包括设备的稳定性、

2023-09-15 16:28:22 1493

1493 件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 1764

1764 在本文中,我将介绍如何使用 Python 和 pandas 库读取、写入文件。 1、安装 pip install pandas 2、读取 import pandas as pd df

2023-09-11 17:52:32 720

720 时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 503

503

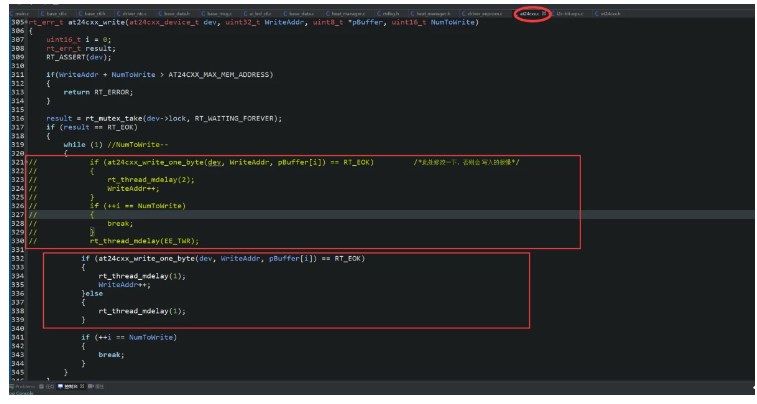

在项目中用到了 AT24C512 EEPROM,实际操作发现在写入稍多写的数据时 出现非常慢的情况

2023-09-06 15:35:39 428

428

,芯片需要一个外挂晶振来提供时钟,以便用来计时。VCC1和VCC2为两路电源,其中VCC2为板卡提供的电源,VCC1为纽扣电池供电。供电关系会在下面的管脚说明里面进行讲解。GND为电源地。

三、管脚

2023-09-04 20:36:40

本书特点

一是循序渐进,由浅入深。本书针对零基础的初学者,以FS4412开发板(基于ARMCortex-A9架构)为例,首先从开发环境的安装和配置及ARM基本指令等相关基础知识开始讲解,然后详细说明

2023-09-03 20:56:45

·AHB时钟是固定的,并且您有多个主机,每个主机具有不同的核心频率·AHB时钟是固定的,您想要将核心时钟减少到例如10 MHz以节省电能。

与正常访问的5或6周期延迟相比,使用异步桥的额外1周期延迟较小

2023-08-30 07:02:10

·未定义长度的突发被转换为单传输·最小的延迟开销,假设AXI从设备以零等待状态接受和呈现数据/响应:

-读取延迟开销=1+0+0,初始、节拍间、最后一拍-写入延迟开销=0+0+1

2023-08-21 06:43:35

时钟周期约束是用于对时钟周期的约束,属于时序约束中最重要的约束之一。

2023-08-14 18:25:51 471

471 此前,CT扫描机控制系统的存储器有使用能够快速写入的SRAM芯片,而SRAM需要电池来保存数据,电池需要定期进行更换。如果是用FRAM替换SRAM,就不用使用电池,因此可以减少维护成本,防止因电池

2023-08-11 11:18:20

(output delay)的限制,以及同步输入的输入 延迟(input delay)的限制。

7)、多周期路径(multicycle path)以及非法路径(false path)的限制。

8

2023-08-11 07:13:40

显示的延迟假设内存访问命中1级数据缓存,并表示加载指令写入的所有向量寄存器的最大延迟。

与标准负载相比,将结果转发到矢量管道需要额外的周期。

2023-08-11 06:14:44

双沿时钟使得原本一个周期输出/输入一个数据的架构,改变为一个周期输出/输入两个数据,这样在不升高时钟频率的前提下,提升了信号的吞吐率,从而带来「性能的提升」。

2023-08-05 09:50:51 2625

2625

TBW是衡量闪存存储器寿命和耐用性的重要指标。但由于写入放大的影响,实际TBW值可能会偏离理论值。本文将介绍TBW的概念以及写入放大系数,并探讨如何降低写入放大对存储器的影响。

2023-07-25 14:38:09 404

404

TBW(Total Bytes Written)是衡量闪存存储器寿命和耐用性的重要指标。但由于写入放大的影响,实际TBW值可能会偏离理论值。本文将介绍TBW的概念以及写入放大系数,并探讨如何降低写入放大对存储器的影响。

2023-07-25 14:34:02 880

880

TBW(Total Bytes Written)是衡量闪存存储器寿命和耐用性的重要指标。但由于写入放大的影响,实际TBW值可能会偏离理论值。本文将介绍TBW的概念以及写入放大系数,并探讨如何降低写入放大对存储器的影响。

2023-07-25 14:19:39 253

253 。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

原理

LED灯按照一定的时间进行亮与灭的转换,在FPGA中,实际原理是LED灯在一定的时钟周期内保持高电平或者低电平。时钟周期也称为振荡周期,定义为时钟频率的倒数,我们通常称之为周期(T)。时钟周期也是数字系统

2023-06-14 16:51:44

定时器输出周期 = (输入时钟源周期)*(8位预分频计数器+1)*(24位TCMPR)

(TCMPR:定时器比较缓存器)

2023-06-14 08:07:30

前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 864

864 电子发烧友网站提供《达拉斯DS1225Y FRAM适配器开源.zip》资料免费下载

2023-06-09 14:24:31 0

0 上升沿输出。

当 ECSPI_CONREG[PHA] 清零时,发送数据在 SCLK 的下降沿移出,接收数据在 SCLK 的上升沿锁存。当主处理器加载传输的数据时输出 MSB。

听起来CPHA和CPOL

2023-06-08 09:44:27

。

我们希望所有这些实例都可以独立运行,因此它们都配置了时钟模块。而且它们独立运行时没有问题。但是当我们使用Bootloader来加载和运行所有这些实例时,有些功能就无法工作,甚至会出现系统复位的情况。

以上案例如何配置时钟模块,所有实例一起工作时都需要配置时钟且不冲突。

2023-05-30 08:12:04

请教个问题,异步复位信号的有效时长至少大给定的时钟周期?

2023-05-10 14:48:36

怎么解释setup time和hold time的定义和在时钟信号延迟时的变化呢?

2023-05-10 11:46:59

和 test2 lua 都达到 3400 文件系统时,开始重置模块。我只通过格式化来激活模块。如果我只使用一个文件,它会达到大约 6800 个写入周期。使用 (a+) 命令和 2 个文件,我只能设法

2023-05-09 07:43:36

manager将地址放在 AWADDR 上并在时钟周期 2 中断言 AWVALID。

2023-05-08 09:21:16 199

199

时钟周期约束:用户需要将设计中的所有时钟进行约束后,综合器才能进行合理的静态时序分析。一个设计中的时钟主要分为两类:主时钟和生成时钟。主时钟包括由全局时钟引脚接入的时钟、高速收发器的输出时钟。

2023-05-06 09:31:34 1253

1253

我们已经在我们的 IMXRT1172 定制板中测试了 RTC,我们观察到一些与实际时间相关的延迟。以下是测试用例。在设置/不设置日期和时间的情况下观察到延迟。

1. 安装程序连续运行 70 小时

2023-05-05 13:35:41

Python 文件写入和创建是 Python 开发中必须掌握的技能之一。在本文中,我们将介绍 Python 中文件创建与写入的基本方法

2023-04-27 09:22:46 2778

2778 带继电器延迟定时器电路 所示图非常简单,此外,延迟周期是可变的,使得设置对于建议的应用非常有用。 可以通过以下几点来理解其功能: 假设负载需要延迟导通动作连接到继电器触点上,当电源接通时,12V

2023-04-26 09:52:27 0

0 参数REG_OUTPUT用于确定是否对最终输出信号寄存;参数RST_USED用于确定是否使用复位信号;参数SIM_ASSERT_CHK则用于确定是否显示仿真信息。从输入/输出端口来看,源端时钟域的输入信号为src_pulse和src_rst;

2023-04-20 09:38:02 1002

1002 通常的写入过程是把整个PLC的程序内存进行写入,然而大多编写程序往往并不需要写入全部内存,所以我们需要通过调整PLC内存

容量达成只写入适量的步数程序,来避免不必要的写入时间。

2023-04-17 14:31:45 0

0 大家好, 我试图建立一个项目来测量 PWM 信号的占空比和周期。 PWM 信号是使用 MCAL-PWM 模块通过在其下配置一个 EMIOS 实例来生成的。用于 PWM 输出的端口 PIN 使用跳线连接馈入一个 ICU-EMIOS 通道。

2023-04-12 06:02:19

Everspin的8Mb MRAM MR3A16ACMA35可以在较慢的富士通8Mb FRAM MB85R8M2T上运行,但还允许系统设计人员利用MRAM的四倍随机存取周期时间。Everspin

2023-04-07 16:26:28

说明书 90*130

2023-03-28 15:15:19

理论上讲,快时钟域的信号总会采集到慢时钟域传输来的信号,如果存在异步可能会导致出现时序问题,所以需要进行同步处理。此类同步处理相对简单,一般采用为延迟打拍法,或延迟采样法。

2023-03-28 13:50:29 1386

1386

下午好,我正在寻找有关 LS1046 的参考时钟电压电平的说明。在 LS1046 数据表中,第 3.7.6.2 节表示 DIFF_SYSCLK/_B 的推荐工作条件为 OVdd = 1.8V。然而

2023-03-28 08:58:26

用altera cyclong EP1C12Q240IC控制DAC7734,用IL715进行信号隔离,DCR010505做电源隔离。我输出的电压+5V,但会周期性到零,输出电压问题如图所示,绿线

2023-03-27 13:51:56

(基于品脱示例)暂时禁用深度睡眠/掉电模式。我确实设法自己设置了一个周期性定时器,并分别进入一个持续的掉电模式,通过按钮中断唤醒。主要目标是在定时器达到零时产生一个周期性事件,并在定时器期间由按钮触发一个不同的事件,从定时器停止的地方恢复。

2023-03-27 07:08:16

为 FPGA 编写一个状态机,它的时钟周期取决于状态的改变,因此我需要确保 i.MX RT 1064 的状态与 FPGA 控制器上的状态相匹配。 另外,有使用FlexSPI连接FPGA的编程实例吗?我检查了 MCUXpresso 中的示例,但它们适用于 NOR 芯片。

2023-03-27 06:23:57

200us;预充电时间(Trp)设置为3个时钟周期(30ns);自刷新时间(Trfc)设置为7个时钟周期(70ns);模式寄存器应用时间(Tmrd)设置为3个时钟周期(30ns);突发长度为2;列选

2023-03-23 17:40:58

电子发烧友App

电子发烧友App

评论