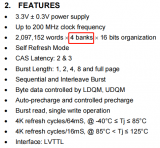

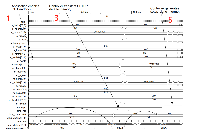

使用STM32H723ZG通过FMC操作外部SDRAM W9825G6KH时, 数据宽度16bit, 总线频率108M, FMC操作时序如图

SDRAM CAS值为2,从0XC0000000到

2024-03-11 06:40:14

在mdk里面可以利用attribute关键字来将数组存放在外扩的SDRAM里面。但是在cubeide里面这样做就会报错,哪位大佬可以解释一下

2024-03-06 07:25:37

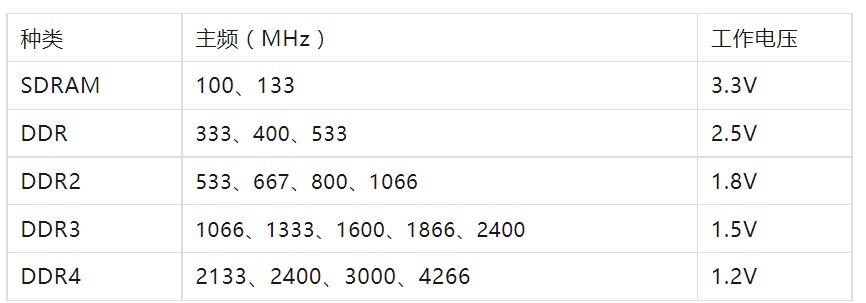

服务器内存条和普通内存条的区别 服务器内存条和普通内存条是计算机中常见的两种内存设备。它们在设计、功能和应用方面存在一些显著的区别。 1.物理特性 普通内存条通常采用DIMM封装形式,而服务器

2024-02-19 10:19:58 466

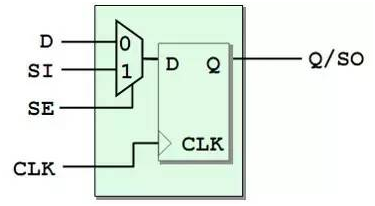

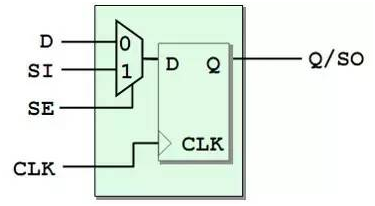

466 ,时序电路可以分为同步时序电路和异步时序电路。接下来,我们将详细讨论时序电路的分类以及其基本单元电路。 一、同步时序电路 同步时序电路是指所有的时钟信号在整个电路中具有相同的时钟频率和相位。它包括锁存器、触发器

2024-02-06 11:25:21 394

394 时序电路是由触发器等时序元件组成的数字电路,用于处理时序信号,实现时序逻辑功能。根据时序元件的类型和组合方式的不同,时序电路可以分为同步时序电路和异步时序电路。本文将从这两个方面详细介绍时序

2024-02-06 11:22:30 288

288 产生相应的输出信号。本文将详细介绍时序逻辑电路的分类、基本原理、设计方法以及与组合逻辑电路的区别。 一、时序逻辑电路的分类 时序逻辑电路主要分为三类:锁存器、触发器和计数器。 锁存器(Latch): 锁存器是一种用于存

2024-02-06 11:18:34 496

496 系统内存和运行内存都是计算机中重要的概念,它们在计算机的存储和运行方面起着不可或缺的作用。虽然它们与计算机存储和运行息息相关,但是它们具有不同的功能和实现方式。接下来我将详细介绍系统内存和运行内存

2024-01-15 16:32:25 461

461 STM32H750是STMicroelectronics推出的一款高性能微控制器,其特点之一是可扩展的SDRAM(同步动态随机存储器)接口。本文将详细介绍STM32H750扩展SDRAM的相关知识

2024-01-04 14:09:23 339

339 和DDR5的主要特点。LPDDR5是为移动设备设计的内存标准,它具有低功耗的特点,能够提供高带宽和大容量的存储。而DDR5是桌面和服务器领域的内存标准,它更注重性能和可靠性。 在时序方面,LPDDR5的时序比DDR5慢。这是因为LPDDR5的主要目标是降低功耗,因此它采用

2024-01-04 10:22:06 1156

1156 的引脚介绍

DDR内存条的引脚数,取决于内存条的类型和规格。以下是一些常见的 DDR内存条类型和它们的引脚数 :

DDR1内存条,184引脚(92针对每侧)

DDR2内存条,240引脚(120针对每侧

2023-12-25 14:02:58

的引脚介绍

DDR内存条的引脚数,取决于内存条的类型和规格。以下是一些常见的 DDR内存条类型和它们的引脚数 :

DDR1内存条,184引脚(92针对每侧)

DDR2内存条,240引脚(120针对每侧

2023-12-25 13:58:55

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 内存溢出与内存泄漏:定义、区别与解决方案 内存溢出和内存泄漏是计算机科学中常见的问题,在开发和调试过程中经常会遇到。本文将详细介绍内存溢出和内存泄漏的定义、区别以及解决方案。 一、内存溢出的定义

2023-12-19 14:10:12 883

883 时,位宽变为64bit,即8个字节,于是SIMM就顺势变为DIMM(Double-Inline Memory Module)。这种形态一直延续至今,也是内存条的基本形态。

2023-12-16 15:00:57 1072

1072

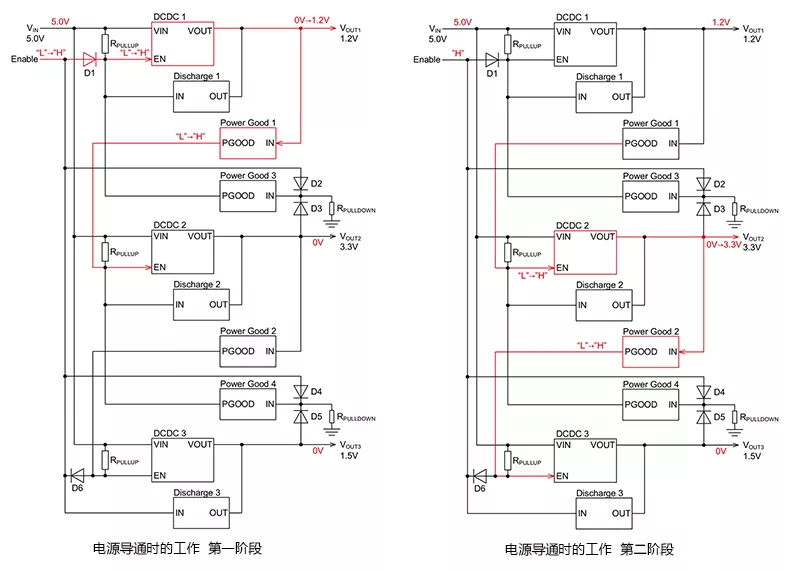

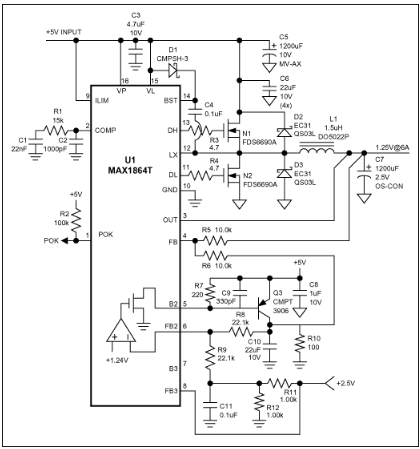

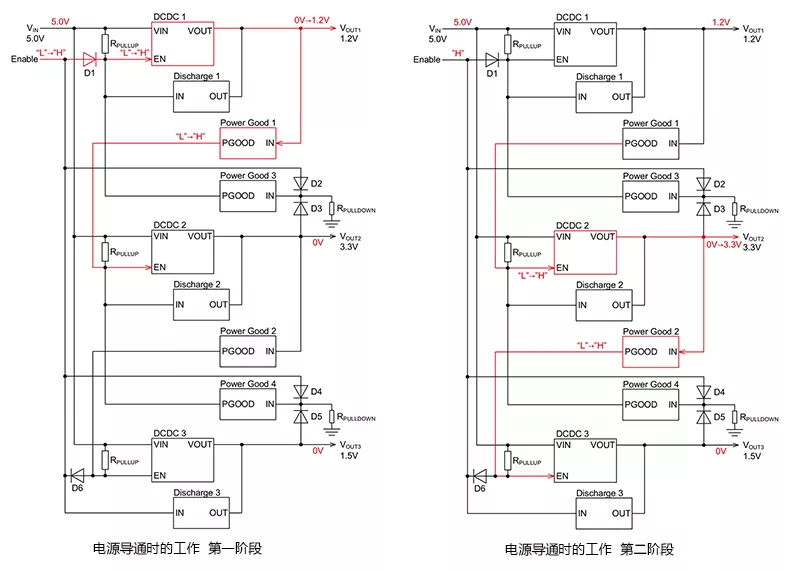

电源时序规格:电源导通时的时序工作

2023-12-08 18:21:43 326

326

什么是内存呢?在计算机的组成结构中,有一个很重要的部分,就是存储器。存储器是用来存储程序和数据的部件,对于计算机来说,有了存储器,才有记忆功能,才能保证正常工作。存储器的种类很多,按其用途可分为

2023-12-07 11:02:27 622

622 追风A60采用新一代DDR5内存规格,相较DDR4,性能提升接近1倍。高配6000MHz频率实现DDR4 3200MHz的1.6倍传输速度和1.9倍传输带宽,让用户在使用台电内存条时获得更快速、更流畅的电脑体验。

2023-12-05 15:52:49 411

411

将详细介绍每个运行时数据内存的作用和特点。 堆内存(Heap Memory): 堆内存是JVM管理的最大的一块内存,用于存储对象实例。当我们使用new关键字创建对象时,对象实例被分配在堆内存中。堆内存是线程共享的,所有的线程都可以访问堆中的对象。它被划

2023-12-05 14:09:34 167

167 JVM(Java虚拟机)是Java程序的运行平台,它负责将Java程序转换成机器码并在计算机上执行。在JVM中,内存模型和内存结构是两个重要的概念,本文将详细介绍它们。 一、JVM内存模型 JVM

2023-12-05 11:08:39 320

320 通过 SDRAM 的 7 个模式寄存器,可以对 SDRAM 的特性,功能以及设置进行编程。这些寄存器本身通过 MRS 命令编辑。模式寄存器一般在初始化期间进行设定,但也可以在后续正常工作期间进行修改。

2023-12-02 13:44:08 921

921

过程中常见的问题之一,可能导致应用程序崩溃、性能下降甚至系统崩溃。在本文中,将详细介绍如何排查和解决Java内存溢出问题。 一、什么是Java内存溢出 在开始解决Java内存溢出问题之前,首先需要了解Java内存

2023-11-23 14:46:07 539

539 电子发烧友网站提供《多电源系统监控和时序控制介绍.pdf》资料免费下载

2023-11-22 16:04:24 0

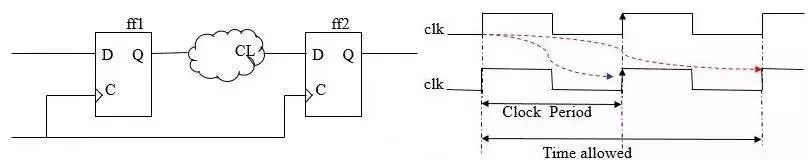

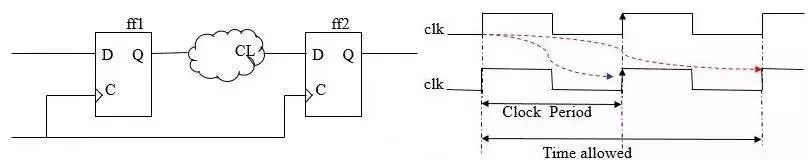

0 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

随着科技的不断进步,光纤技术已经成为现代通信网络的核心组成部分。其中,光纤反射内存产品作为一种新型的存储方式,在数据存储、传输和处理等方面具有显著的优势,逐渐得到了广泛的应用。本文将详细介绍光纤反射

2023-11-11 12:26:12 1110

1110 时序数据库的一哥 InfluxDB,是我们最初选择的时序数据库。但随着时序曲线的规模变大,InfluxDB 的局限性也开始暴露了出来。同时社区中关于 InfluxDB OOM 的讨论也日益增多

2023-10-13 16:04:25 257

257

遇到一个比较有意思的问题。一个朋友问我说:他的电脑内存坏了,想换一条新的内存,换DDR5内存条是不是更好?看了他的配置之后,电脑使用的是DDR4的条子。显然这是不能换的。

2023-10-10 11:18:13 606

606

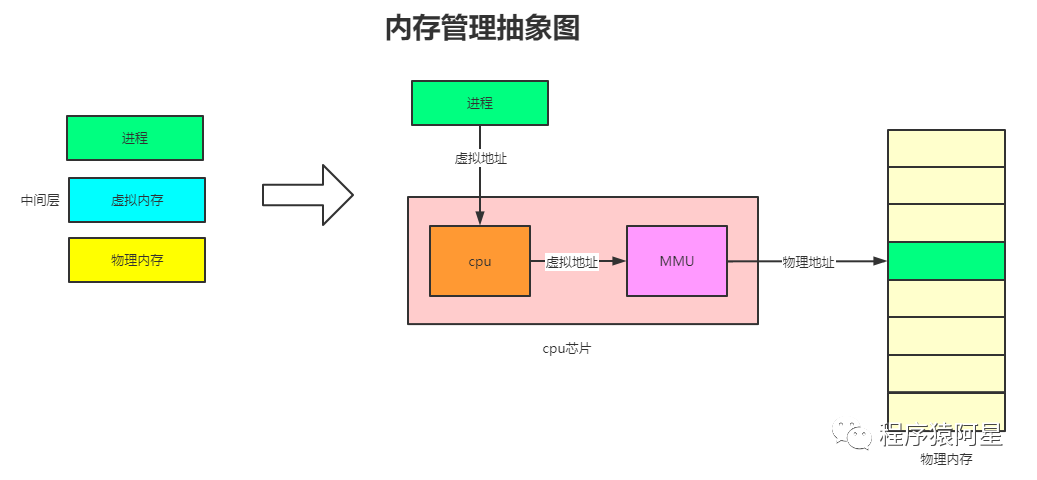

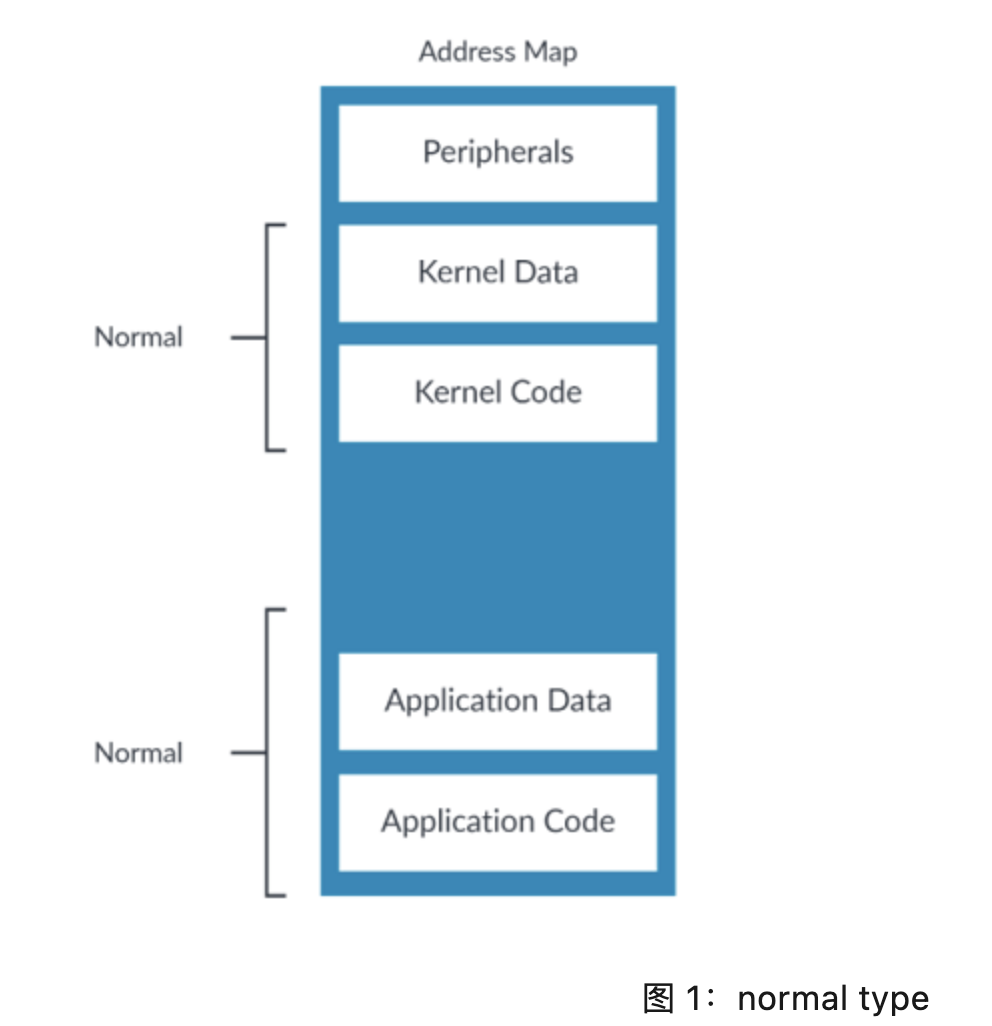

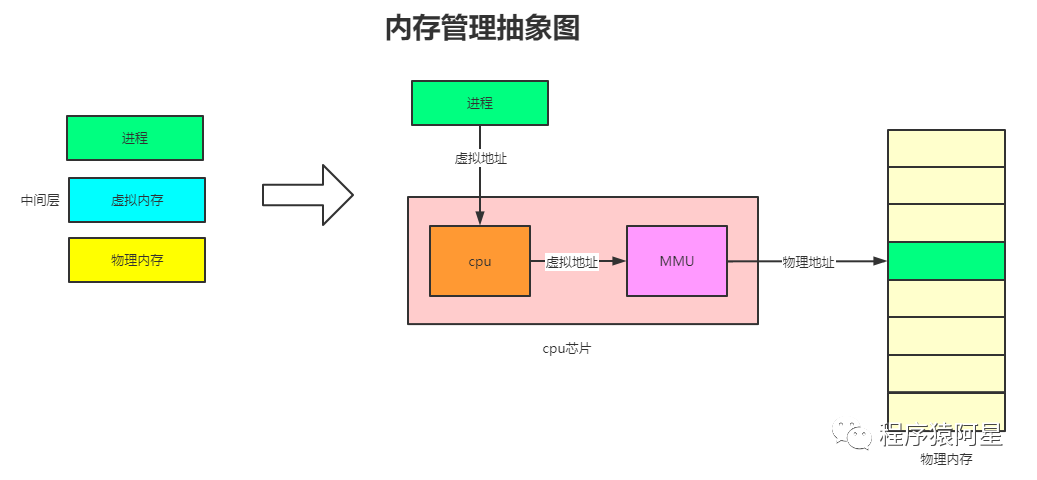

什么是内存 我们想准备运行程序进程需要经过那几个步骤,这里猜测一下。 首先要去申请内存,操作系统根据现在剩余的地毯空间与你地毯的规模划分一块相应大小的内存给你,接着你就可以愉快的运行程序进程

2023-10-09 16:23:42 433

433

在电脑上拆到2条rdram内存条,这个和sdram内存条有什么区别,可以兼容吗

2023-10-08 09:01:45

事件内存管理定义为在DEM模块中添加、更新和删除事件内存条目的过程。DEM模块确定事件内存条目是新的还是当前存在于事件内存中。 Event retention Event retention定义

2023-10-04 11:45:00 317

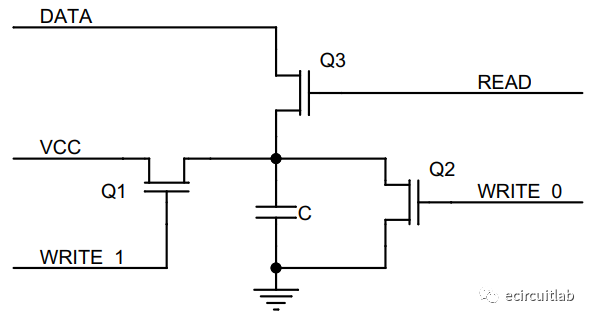

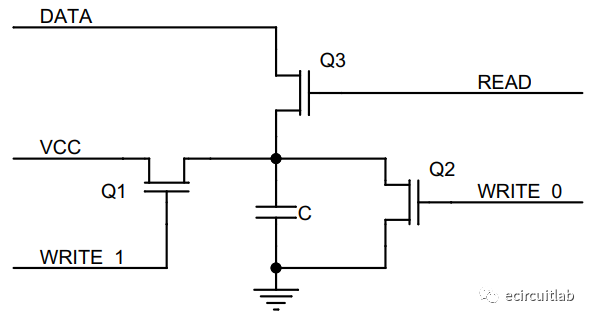

317 SDRAM的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

2023-09-28 17:26:29 637

637

SDRAM(synchronous dynamic random-access memory)即同步动态随机存取内存。在介绍SDRAM前,我们先了解下DRAM(Dynamic random-access memory),DRAR中文译为动态随机存取内存

2023-09-27 15:02:32 1004

1004

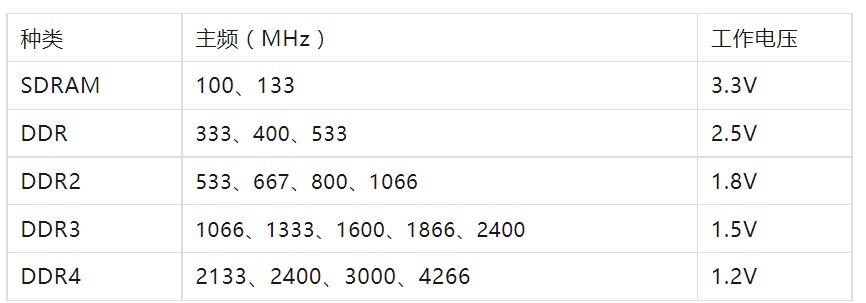

DRAM 由于其结构简单,设计体积小,在服务器的内存中占主导地位,并得到了长足的发展,从 DRAM 逐渐演进到 SDRAM 再到 DDR SDRAM 系列。SDRAM为同步的动态随机处理器,同步

2023-09-15 10:13:03 964

964

最新的32Gb DDR5内存芯片,继续采用12nm级别工艺制造,相比三星1983年推出的4Kb容量的第一款内存产品,容量已经增加了50多万倍!

2023-09-04 14:28:11 264

264 关于农林气象站的基本介绍

2023-08-23 16:58:56 220

220 石墨烯电池技术详细介绍 石墨烯电池技术是当今电池领域的新宠,它拥有高功率、长寿命、较低的负载,以及高能量密度等特点,正逐渐成为该领域实现突破的重要技术手段之一。本文将为大家详细介绍石墨烯电池技术

2023-08-22 17:06:07 2468

2468 时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 451

451

PL340内存控制器是一款高性能、面积优化的SDRAM或移动SDR内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结

2023-08-12 06:25:03

PL341内存控制器是一款高性能、面积优化的DDR2 SDRAM内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结了周期模型的功能与硬件的功能,以及周期模型的性能和准确性。

2023-08-12 06:01:49

我手上有一张DDR200T的开发板,板载了一块512M的SDRAM内存,板子烧了一个UX600的demosoc,我是要在这个板子跑RT-Thread。

要是想使用这块SDRAM应该怎么做呢?应该

2023-08-11 08:05:46

SDRAM全称Synchronous Dynamic RAM,同步动态随机存储器。首先,它是RAM,即随机存储器的一种。

2023-08-08 15:10:46 896

896

贴片Y电容是一种常见的电子元件,它在电子设备中具有广泛的应用。贴片Y电容的型号众多,每个型号都有其独特的特点和应用场景。今天弗瑞鑫小编将详细介绍贴片Y电容的各种型号及其特点,以便读者更好地了解和选择适合自己应用的型号。

2023-08-04 08:41:38 558

558 关于该产品是DMC-620的高级概述。

DMC-620是Arm AMBA 5芯片SoC外设,由Arm开发、测试和许可。它是一款高性能、区域优化的内存控制器,与AMBA 5 CHI协议兼容。

它支持

2023-08-02 11:55:49

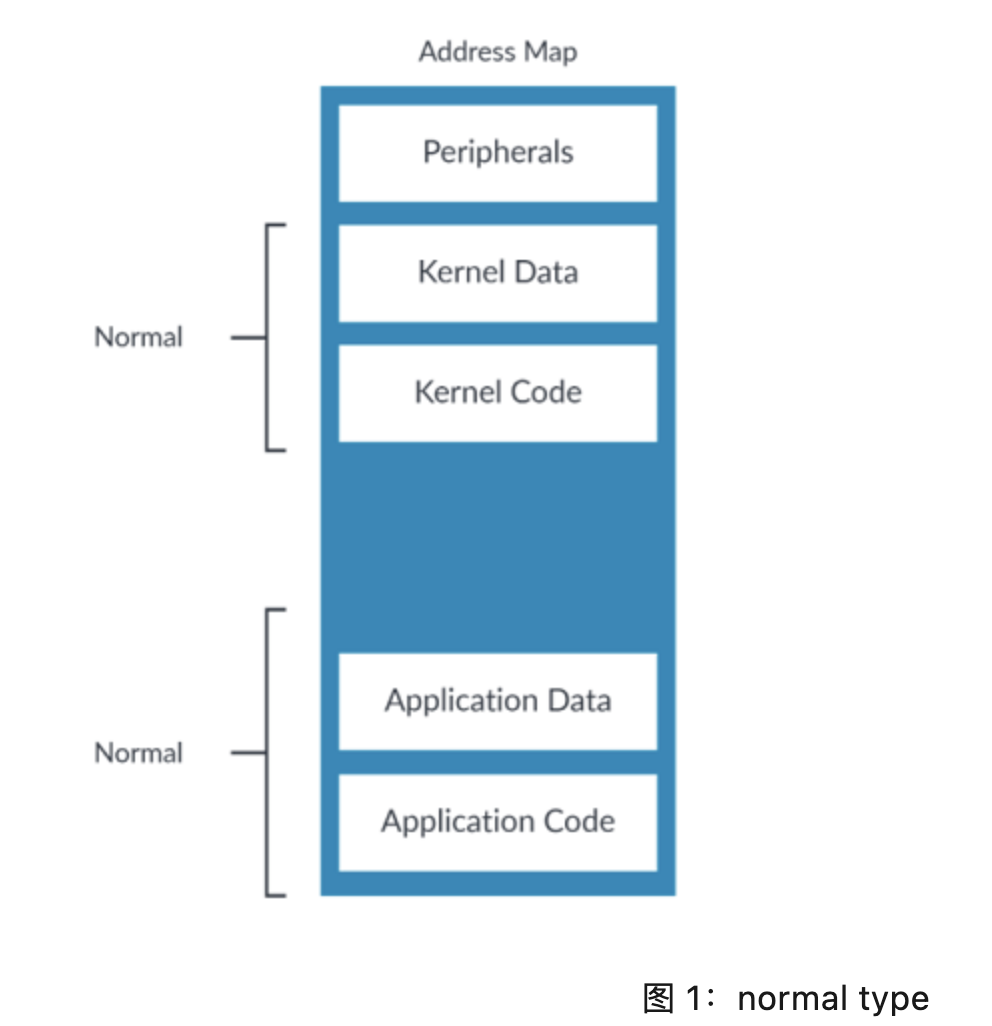

1. 本指南介绍由 Armv8-A 架构定义的内存定序模型,并介绍所提供的不同内存障碍;本指南还确定一些需要明确定序的常见情况,以及如何使用内存障碍以确保实现正确操作;本指南适用于低级别代码的开发者

2023-08-02 11:03:30

可以作为内存堆,但是 STM32 内部 RAM 比较小,遇到那些需要大容量 RAM 的应用就不行了,如音视频处理。不过 STM32 可以外接 SRAM 甚至大容量的 SDRAM ,如果

2023-07-30 10:47:42 500

500 的工作原理 DDR芯片内存的工作原理可以分为两部分, 一部分是时序,一部分是数据传输 。 控制DDR内存的时序,是由内存控制器控制的,它负责管理内存的读写操作。内存控制器会向DDR内存发送时钟信号,这个时钟信号被称为 系统时钟 。 DDR内存的数据传输,是通过前沿和下降沿来实现的

2023-07-28 13:12:06 1883

1883

时序:字面意思,时序就是时间顺序,实际上在通信中时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫时序。

2023-07-26 10:06:03 1641

1641 今天要介绍的时序基本概念是Mode(模式). 这是Multiple Scenario环境下Sign off的一个重要概念。芯片的设计模式包括最基本的功能function模式,以及各种各样相关的测试模式。

2023-07-10 17:21:38 1716

1716

今天主要介绍的时序概念是时序库lib,全称liberty library format(以• lib结尾),

2023-07-07 17:15:00 1638

1638

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00:02 1396

1396

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

今天要介绍的时序分析基本概念是Slew,信号转换时间,也被称为transition time。

2023-07-05 14:50:53 1530

1530

今天要介绍的时序分析基本概念是skew,我们称为偏差。

2023-07-05 10:29:37 2119

2119

今天我们要介绍的时序分析基本概念是MMMC分析(MCMM)。全称是multi-mode, multi-corner, 多模式多端角分析模式。这是在先进工艺下必须要使用的一种时序分析模式。

2023-07-04 15:40:13 1461

1461

今天要介绍的时序分析基本概念是Latency, 时钟传播延迟。主要指从Clock源到时序组件Clock输入端的延迟时间。

2023-07-04 15:37:08 1305

1305

本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 691

691 本文主要介绍了静态时序分析 STA。

2023-07-04 14:40:06 525

525

今天我们要介绍的时序分析概念是 **AOCV** 。全称Stage Based Advanced OCV。我们知道,在OCV分析过程中,我们会给data path,clock path上设定单一的timing derate值。

2023-07-03 16:29:05 1155

1155

今天我们要介绍的基本sdc是 **时序特例** ,也就是我们常说的Path exception。针对一些路径需要的一些特殊设定,常用的有set_false_path, set_multicycle_path, set_max_delay,set_min_delay等

2023-07-03 15:34:52 471

471

今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省功耗。

2023-07-03 15:06:03 1481

1481

今天我们要介绍的时序分析概念是 **min pulse width** ,全称为最小脉冲宽度检查。这也是一种非常重要的timing arc check,经常用在时序器件或者memory上面。

2023-07-03 14:54:11 1197

1197

今天要介绍的时序分析基本概念是lookup table。中文全称时序查找表。

2023-07-03 14:30:34 664

664

向量和动态仿真 。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,时序裕量,setup检查和hold检查等。 时序路径 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最

2023-06-28 09:38:57 714

714

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1834

1834

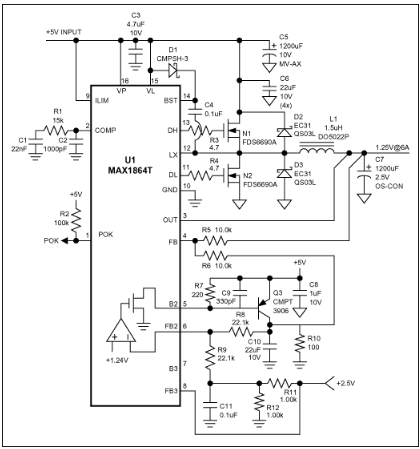

本设计笔记显示了用于工作站和服务器的高速内存系统的双倍数据速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/电缆调制解调器电源,电路产生等于并跟踪VREF的终止电压(VTT)。

2023-06-26 10:34:36 549

549

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 1260

1260

本文介绍 Armv8-A 架构的内存序模型,并介绍 arm 的各种内存屏障。本文还会指出一些需要明确内存保序的场景,并指明如何使用内存屏障以让程序运行正确。

2023-06-15 18:19:37 864

864

,频率更高:采用超短进口双头探针设计,相比同类测试产品使IC与PCB之间数据传输距离更短;

⑥可自行维修,节省时间:采用带定位孔内存颗粒测试专用PCB,探针板与PCB 孔定位,保证探针与PCB精确定位;以上就是关于DDR内存条治具六大特点 的介绍 ,希望对您有益~

2023-06-15 15:45:22

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1229

1229 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6199

6199

内存管理是计算机系统中负责管理系统内存资源的一种机制,主要包括内存分配、内存释放、内存映射和虚拟内存管理等方面。它是计算机系统中非常重要的一个组成部分,能够有效地提高系统的资源利用率和应用程序的性能。

2023-05-29 14:09:37 1356

1356

内存,也就是电脑中的内存条,其用于暂时存放CPU中的运算数据,以及与硬盘等外部存储器交换的数据。只要计算机开始运行,操作系统就会把需要运算的数据从内存调到CPU中进行运算,当运算完成,CPU将结果传送出来。内存决定了我们应用的上限,也就是我们能够同时运行多少应用,从硬盘向CPU调取多少数据。

2023-05-26 11:22:32 15066

15066

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 1879

1879

5G单站验证详细介绍

2023-05-22 12:38:38 309

309

本篇介绍了UML时序图的基础知识,并通过visio绘制一个物联网设备WIFI配网的UML时序图实例,来介绍UML时序图的画法与所表达的含义。

2023-05-16 09:09:22 1225

1225

本文介绍接口和协议时序

2023-05-10 15:37:16 2022

2022

我想将 i.MX RT1024 与外部 64MB SDRAM 一起使用。根据数据表,它支持 8/16 位 SDRAM 外部存储器接口。从性能的角度来看,哪种模式更好?如何?如果有任何链接/参考可以通过此详细信息,请告诉我。谢谢

2023-05-05 11:17:30

本公司目前MCU系列,到目前为止, SWM34x 支持外接8M16M SDRAM,SWD34S系列已经把SDRAM合封入芯片,合封的SDRAM大小根据芯片型号不同,具体见官方手册。

2023-04-28 09:30:22 1496

1496

想用SDRAM运行SAI,修改内存配置后好像不能正常运行。是什么原因?

我在 SDK 中使用 evkmimxrt1020_sai_edma_record_playback,并调整 RAM 以指向 BOARD_SDRAM。该程序似乎无法正常运行。

2023-04-26 06:42:50

本章教程主要在SPI单工通信方式下进行1条时钟线和1条单向数据线配置,并进行主机接收从机发送。 1、SPI简介及相关函数介绍关于SPI单工通信模式下1条时钟线和1条单向数据线配置介绍,在第46章已经

2023-04-25 16:50:41

本章教程主要在SPI单工通信方式下进行1条时钟线和1条双向数据线配置,并进行主机接收从机发送。 1、SPI简介及相关函数介绍关于SPI单工通信模式下1条时钟线和1条双向数据线配置介绍,在第46章已经

2023-04-25 16:48:14

详细介绍安科瑞产品中关于绝缘监测和绝缘故障定位的相关产品,从含义,解决方法,产品技术参数等 详细介绍。

2023-04-23 15:29:14 495

495

大佬们,这个free在finsh里面介绍是列出系统使用的内存,我把sdram打开了,在list——memheap里面能找到sdram,为什么在free里面的total不包括sdram的大小

2023-04-14 10:06:25

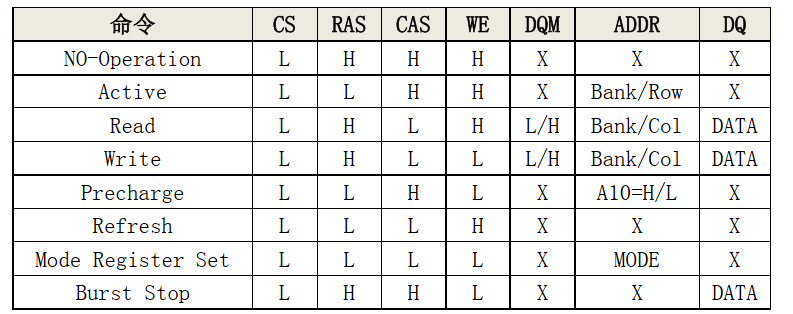

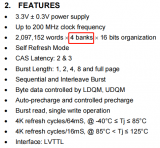

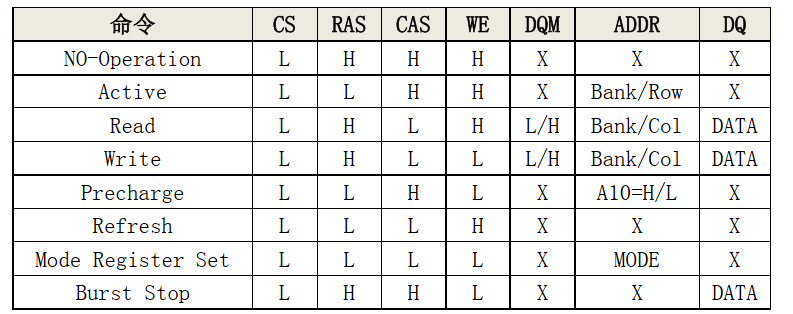

SDRAM的驱动需要用到一些命令,介绍几个常见的命令。

2023-04-04 17:13:19 1814

1814

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

本章节主要介绍一些简单的时序约束的概念。

2023-03-31 16:37:57 928

928

SDRAM SLICE CARD

2023-03-30 12:05:53

我正在尝试修改 SDK 示例以使用一个 SDRAM 而不是板上可用的两个。我修改了内存设置和DCD文件。我尝试了多种配置,但总是以错误告终。如何使用一个 SDRAM 运行 lVGL 示例?

2023-03-30 07:27:47

读写整个行,我们可以利用突发终止命令将其终止掉。 下面两个时序就是SDRAM的页读页写时序,在某个位置使用突发终止命令将其终止掉。 页写被终止时序图:页读被终止时序图: 具体的参考设计请参考图像显示系统设计。

2023-03-27 17:09:14

在win10/win11下使用PADS layout时,报错‘’Out of memory‘’,或者报错‘’数据库严重错误编号 2010‘’已经尝试过:1.加大内存条内存,无法解决2.加大虚拟内存

2023-03-25 18:58:13

SDRAM支持读写的长度为1、2、4、8和一行(整页)。

具体的SDR SDRAM的介绍可以查看手册。下面只介绍几个相对重要的时序图。

在SDR SDRAM正常使用之前,需要进行初始化。初始化

2023-03-23 17:40:58

正在加载...

电子发烧友App

电子发烧友App

评论