嵌入式铁电存储器可实现超低功耗微控制器的设计。将铁电存储器添加到微控制器中可以进行快速可靠的非易失性数据存储与处理,是存储系统状态、数据记录及在多种应用的非易失性的理想选择,例如传感器与计量仪表到

2024-03-06 09:57:22

TC364 微控制器是否支持外部存储器?

根据我的阅读,外部总线接口用于外部存储器。 在该微控制器的数据手册中,我看到外部总线为 0。

2024-03-04 06:13:37

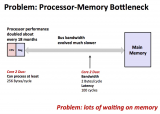

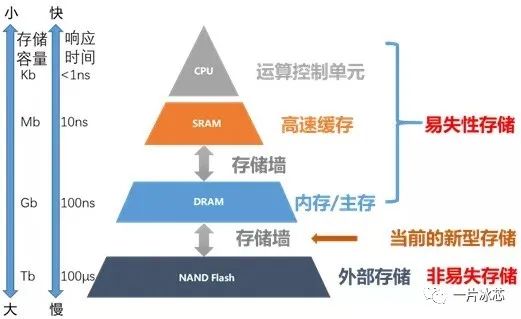

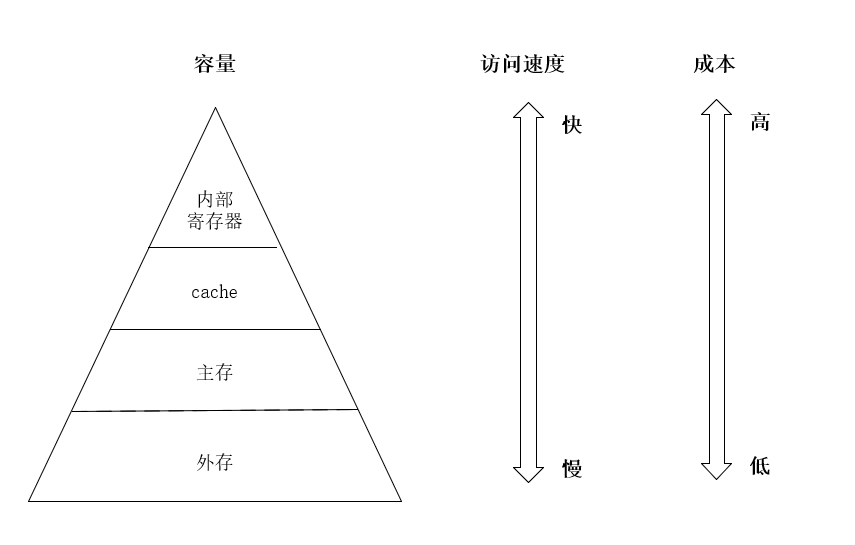

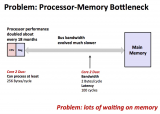

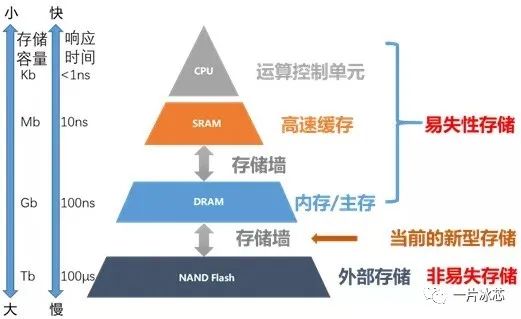

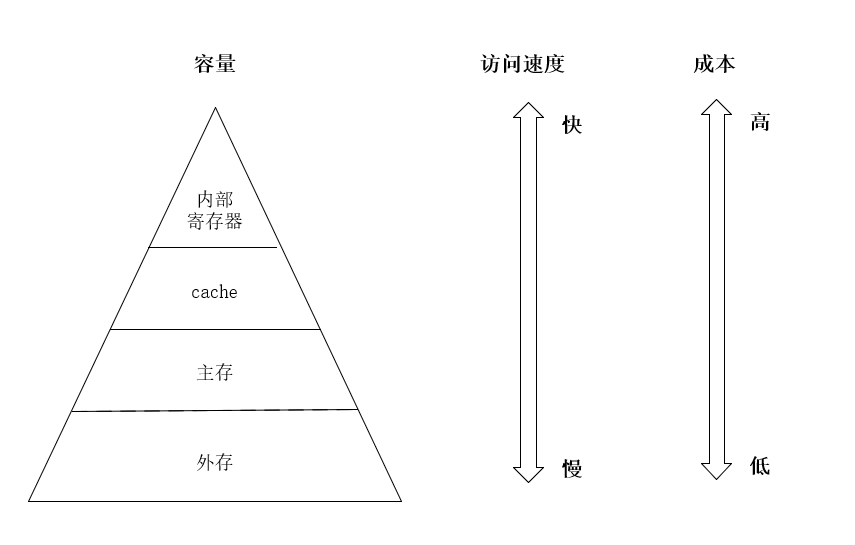

通过多级存储器的设计,存储器层次结构能够在存储容量和访问速度之间找到一个平衡点。高速缓存存储器和主存储器提供了快速的访问速度,而辅助存储器则提供了大量的存储空间。

2024-02-19 13:54:42 121

121

1) 允许一个物理内存(即 XRAM) 可同时作为程序存储器和数据存储器进行访问

如何使用 SCR XRAM 作为程序存储器和数据存储器。

1) 用于存储 scr 程序的程序存储器

2) 用于在 tricore 和 scr 之间交换数据的数据存储器。

2024-01-30 08:18:12

据报道,全球领先的半导体制造公司台积电在次世代MRAM存储器相关技术方面取得了重大进展。该公司成功开发出自旋轨道转矩磁性存储器(SOT-MRAM)阵列芯片,并搭配创新的运算架构,使其功耗仅为其他类似技术的1%。

2024-01-19 14:35:12 6646

6646 ADuCM360/1是否支持存储器到存储器DMA传输?

2024-01-15 07:43:09

MRAM或磁性随机存取存储器使用具有铁磁性材料的磁性“状态”的1晶体管–1磁性隧道结(1T-1MTJ)体系结构作为数据存储元素。

2024-01-09 14:24:03 208

208

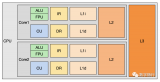

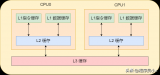

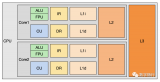

CPU的核心功能包括数据运算和指令控制。CPU运算的数据和执行的指令全部存储在CPU的寄存器中,这些数据和指令又都来自于CPU高速缓存。

2024-01-02 16:01:48 662

662

靠近 CPU 的小、快速的高速缓存存储器(cache memory)做为一部分存储在相对慢速的主存储器(main memory)中数据和指令的缓冲区域。

2023-12-25 09:21:50 242

242

描述AT28C256是一种高性能的电可擦可编程只读存储器。它的256K内存由8位的32,768个字组成。该器件采用Atmel先进的非易失性CMOS技术制造,访问时间高达150 ns,功耗仅为440

2023-12-08 15:05:01

该 FRAM 芯片(铁电随机存取存储器)配置为 16,384 × 8 位, 通过铁电工艺和硅栅 CMOS 工 艺技术形成非易失性存储单元和 SRAM 不同,该芯片不需要电池就可以保持数据。 该芯片

2023-11-27 16:41:47

该 FRAM 芯片(铁电随机存取存储器)配置为 16,384 × 8 位, 通过铁电工艺和硅栅 CMOS 工 艺技术形成非易失性存储单元和 SRAM 不同,该芯片不需要电池就可以保持数据

2023-11-27 16:37:59

易失性存储和精确的实时时钟,本文推荐使用国产PB85RS2MC铁电存储器用于该存储系统中。铁电存储器PB85RS2MC在系统主要是实现数据的非易失性存储和的实时时

2023-11-27 10:17:05

单片机的存储器主要有几个物理存储空间

2023-11-01 06:22:38

单片机的存储器从物理上可划分为4个存储空间,其存储器的空间范围是多少?

2023-11-01 06:20:34

SRAM是目前最成熟的易失性高速存储器,通常由6管(6T)实现数据的读写,可以用做CPU和内存(DRAM)之间的高速缓存。

2023-10-31 17:46:55 1259

1259

描述AT28C256是一种高性能的电可擦可编程只读存储器。它的256K内存由8位的32,768个字组成。该器件采用Atmel先进的非易失性CMOS技术制造,访问时间高达150 ns,功耗仅为440

2023-10-26 10:45:10

大家有谁知道AT89C52怎么选择外部存储器,我之前用的是P89V51,选择外部存储器是定义AUXR=0x02;,但是现在想用AT89C52单片了,程序该怎么改了啊??AT89C52手册上找不到怎么选择外部存储器说明,各位高手有谁知道啊 ?

2023-10-26 06:11:25

EPM1270F256C4N,ALTERA/阿尔特拉,即时开启非易失性CPLD,处理器EPM1270F256C4N,ALTERA/阿尔特拉,即时开启非易失性CPLD,处理器

2023-10-24 15:38:16

存储器测试问题怎么才能稳定

2023-10-17 06:51:11

使用,需要增添片外存储器。因此铁电存储器(FRAM)是便携式医疗设备的理想解决方案。1、高写入耐久度PB85RS2MC是通过铁电工艺和硅栅CMOS工艺技术形成非易失性存

2023-10-16 10:13:25

怎么随机存取存储器ram中的存储单元

2023-09-28 06:17:04

众所周知,铁电存储器(FRAM)是一种融合了在断电的情况下也能保留数据的非易失性、随机存取两个特长的铁电随机存储器。本文所提到的国产铁电存储器PB85RS2MC在数据保持上,不仅不需要备用电池,而且

2023-09-27 10:00:51

电子发烧友网站提供《管理基于Cortex-M7的MCU的高速缓存一致性.pdf》资料免费下载

2023-09-25 10:11:48 0

0 如何检测24c存储器容量

2023-09-25 06:48:32

电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7(SAM S70/E70/V70/V71)MCU上创建不可高速缓存的存储区.pdf》资料免费下载

2023-09-20 11:50:46 0

0 电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7 MCU上在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-20 11:40:24 0

0 电子发烧友网站提供《使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-19 16:28:10 0

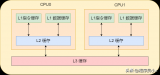

0 典型的SoC存储体系包括处理器内部的寄存器、高速缓存(Cache)、片内ROM、片外主存。其中,内部寄存器通常由十几个到几十个构成,用于缓存程序运行时频繁使用的数据(局部变量、函数参数等)。

2023-09-19 09:30:30 1434

1434

STM32MP151A/D器件基于高性能ARM®Cortex®-A7 32位RISC内核,运行频率高达800 MHz。

Cortex-A7处理器包括一个32K字节的一级指令高速缓存、一个32K字节

2023-09-13 07:23:32

片上闪存特性和系统框图

存储空间组织架构

用户闪存

系统闪存

OTP

选项字节

闪存读接口

等待周期

指令预取

指令高速缓存

数据高速缓存

擦除和编程操作

读保护和写保护

STM32F2和STM32F1的闪存特性比较

2023-09-13 07:10:38

闪存。

主32位AHB5多层总线矩阵,位于中央图中的11个主设备和10个从设备互连。

128位AHB5指令高速缓存再填充总线矩阵为由两个128位接口和两个32位接口组成接口。

128位接口是连接到的从0端口到闪存的指令缓存和主0端口存储器接口或FLITF。

2023-09-08 06:48:06

什么是高速缓存?• 高速存储器块,包含地址信息(通常称作TAG)和相关联的数据。• 目的是提高对存储器的平均访问速度• 高速缓存的应用基于下面两个程序的局部性 :• 空间局部性:如果一个存储器的位置

2023-09-07 08:22:51

下表中列出的 STM32 微控制器(MCU)中。这些缓存使用户从内部和外部存储器提取指令和数据时或在用于外部存储器的数据流量时提高应用性能并降低功耗。本文档提供了典型示例,以强调 ICACHE 和 DCACHE 功能,并便于配置。

2023-09-07 07:51:27

1.具有双发布功能的高性能6级流水线(每个时钟周期最多执行两条指令)。

2.作为系统总线的64位AXI总线接口。

3.可选的指令高速缓存(4至64KB)和数据高速缓存(4至64KB),每个高速

2023-09-04 06:28:56

新能源汽车的核心技术是大家熟知的动力电池、电池管理系统和整车控制单元。车载电子控制系统对于存取各类传感器资料的需求持续增加,因此对于高性能非易失性存储技术的需求也越来越高,因为当系统在进行资料分析

2023-09-01 10:04:52

每当一个核通过MVA操作对另一个核执行广播无效指令高速缓存时,例如,当将可执行代码从闪存复制到存储器时,其他核每次都刷新并重新启动它们的预取单元,而不进行任何处理。

由于该错误,其他核心可能停止它们的执行,直到不再发生剩余的广播操作。

2023-09-01 09:16:59

受影响的ARM CPU上,建议的缓解措施包括在转换到需要保护以前的执行上下文的执行上下文时,使部分或全部分支预测器缓存失效。

有关术语执行上下文的定义,请参见第1.2节。

CVE-2018-3639,也

2023-08-25 07:36:27

软件可能会允许恶意行为者不正当地从特权内存(DRAM或CPU缓存)中收集少量敏感数据。

·ARM认为这些利用不会损坏、修改或删除数据。

·所有变体都基于导致高速缓存分配的推测性内存访问。

然后,可以

2023-08-25 07:15:47

架构的卓越响应性和易用性。

凭借内置的指令和数据高速缓存以及紧密耦合的存储器(TCM),这款超标量处理器即使在终端要求最苛刻的处理应用程序中也不会变慢

2023-08-25 06:25:54

随着高速数据通信的进步,数据更频繁地发送意味着对非易失性存储器的需求增加,因为非易失性存储器可以承受这种频繁的数据操作。铁电存储器是具有物联网新时代所要求的高读写耐久性和快速写入速度的理想存储设备

2023-08-24 10:05:59

)的原理,与微程序复杂指令集计算机(CISC)相比,指令集和相关的解码机制得到了极大的简化。

片上混合数据和指令高速缓存与写缓冲区一起,大大提高了平均执行速度,并减少了处理器所需的平均内存带宽。

这允许外部存储器以最小的性能损失支持额外的处理器或直接存储器访问(DMA)通道

2023-08-24 07:16:02

CPU高速缓存集成于CPU的内部,其是CPU可以高效运行的成分之一,本文围绕下面三个话题来讲解CPU缓存的作用

2023-08-21 12:17:35 797

797

高速缓存维护操作。

中断延迟通过中断和重新启动加载存储多条指令以及使用集成中断控制器来保持较低的延迟。

Cortex-R8处理器为低延迟和确定性提供了两种专门的内存解决方案:

·紧耦合存储器(TCM

2023-08-18 08:28:22

Cortex-A7 MPCore处理器是一款实现ARMv7-A架构的高性能、低功耗处理器。

Cortex-A7 MPCore处理器在带有一级高速缓存子系统、可选集成GIC和可选二级高速缓存控制器的单个多处理器设备中具有一到四个处理器

2023-08-18 07:25:18

,并且提供了可选的硬件加速器一致性端口(ACP),以减少与其他主机共享存储器区域时的软件高速缓存维护操作。

中断延迟通过中断和重新启动加载-存储多条指令以及使用集成中断控制器来保持低。

Cortex-R7 MPCore处理器为低延迟和确定性提供了两种专门的内存解决方案

2023-08-18 06:34:29

为了有效利用其他资源,例如寄存器文件,实现了有限的双指令发布。

提供硬件加速器一致性端口(ACP)以减少在与其他主机共享存储器时对缓慢的软件高速缓存维护操作的要求。

通过中断和重新启动加载存储多条指令

2023-08-18 06:09:34

(SB)、所有内核以及内核之间共享的逻辑。

共享逻辑包括CPU桥(CPU侧)(CBC)、L2高速缓存,以及维护核心中的高速缓存与L2高速缓存和低延迟RAM(LLRAM)存储器之间的一致性的一致性逻辑

2023-08-17 08:02:29

和纠正的纠错码(ECC)功能在实现时包括在数据和指令高速缓存中。

Tcm接口支持实施外部ECC,以提供更高的可靠性并满足与安全相关的应用。

Cortex-M7处理器包括可选的浮点算术功能,支持单精度和双精度算术。

请参见第8章浮点单元。

该处理器适用于需要快速中断响应功能的高性能、深度嵌入式应用程序

2023-08-17 07:55:23

执行模式将嵌入式内存内容转储到调试器,使其适用于芯片启动和调查软件故障,如高速缓存一致性错误。

它允许快速测试内存和内存保护逻辑。

因此,MBIST事务是使用IP核时钟连续执行的,因此,可以通过以全功能

2023-08-17 07:10:53

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有四个Cortex-A32处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A32处理器支持

2023-08-16 06:54:59

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有八个处理器可用,该监听控制单元维护L1、L2和L3数据高速缓存一致性。

本节提供周期模型与硬件的功能比较的摘要,以及周期模型的性能和准确性

2023-08-12 07:30:35

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存关联群集中最多有四个Cortex-A53处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A53多处理器支持

2023-08-12 06:44:40

ARM946E-S™ 是一个可合成的宏小区,结合了ARM9E-S™ 加工机具有指令和数据缓存、紧密耦合的指令和数据SRAM的核心带有保护单元、写缓冲区和AMBA的存储器™ (高级微处理器总线体系结构

2023-08-08 07:33:30

ARM946E-S™ 是一个可合成的宏小区,结合了ARM9E-S™ 带指令和数据高速缓存的处理器核心、带保护单元的紧密耦合指令和数据SRAM存储器、写缓冲区和AMBA™ (高级微处理器总线体系结构

2023-08-02 17:50:31

消息支持,以管理分布式内存管理单元(MMU),例如CoreLink MMU-400。这些可以通信通过具有多达三个ACE Lite从机的CCI-400。

硬件管理的一致性可以通过以下方式提高系统性能并降低系统功耗共享片上数据。管理一致性有以下好处:

•减少外部存储器访问。

•减少软件开销。

2023-08-02 17:33:01

:

•用于增强操作系统安全性的TrustZone架构•专为高性能系统设计的主、从和外围AXI/AMBA接口•智能能源管理器(IEM)支持。

高速缓存控制器是一个统一的、物理寻址的、物理标记的8路高速缓存。您可

2023-08-02 15:09:49

当中央处理器(CPU)产生大量内存流量时,添加片上二级缓存(也称为二级缓存,L2CC)是提高计算机系统性能的公认方法。根据定义,二级缓存假定存在与CPU紧密耦合或内部的一级缓存或主缓存。

2023-08-02 13:11:45

ARM720T是一款通用的32位微处理器,具有8KB的高速缓存、扩大的写入缓冲区和内存管理单元(MMU),组合在一个芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是与ARM处理器

2023-08-02 11:36:56

)一种设备,是存储器区域的归属节点,接受来自RN Fs和RN is的相干请求,并根据需要生成对系统中所有适用RN Fs的窥探,以支持相干协议。

I/O主节点(HN-I)作为从属I/O子系统的主节点

2023-08-02 10:38:59

ARM946E-S是一个可合成的宏单元,结合了ARM处理器。它是ARM9Thumb系列高性能32位片上系统处理器解决方案的一员。

ARM946E-S具有紧密耦合的SRAM存储器、指令和数据缓存

2023-08-02 09:41:21

MBIST是测试嵌入式存储器的行业标准方法。MBIST通过根据测试算法执行对存储器的读取和写入序列来工作。存在许多行业标准的测试算法。MBIST控制器生成正确的读取和写入序列。ARM L210 MBIST控制器用于与ARM L210一起执行二级高速缓存RAM的内存测试。

2023-08-02 08:07:10

动态存储运行时数据在神经网络的推理过程中。

•AXI接口M1用于允许更低带宽和更高带宽的内存事务

延迟因此,AXI M1接口可以连接到较慢或较少突发的存储器例如闪存或DRAM。内存用于运行时的非易失性

2023-08-02 06:37:01

电子发烧友网站提供《STM32F7技术--高速缓存.pdf》资料免费下载

2023-08-01 15:18:55 0

0 就需要一块非易失性存储芯片来储存这些数据。非易失性存储器一般包括EPROM、EEPROM和FLASH等,它们在系统掉电的情况下仍可保留所存数据,但因其技术都源于R

2023-07-25 10:31:33

该 FRAM 芯片(铁电随机存取存储器)配置为 16,384 × 8 位, 通过铁电工艺和硅栅 CMOS 工 艺技术形成非易失性存储单元和 SRAM 不同,该芯片不需要电池就可以保持数据。 该芯片

2023-07-18 17:13:33

该 FRAM 芯片(铁电随机存取存储器)配置为 16,384 × 8 位, 通过铁电工艺和硅栅 CMOS 工 艺技术形成非易失性存储单元和 SRAM 不同,该芯片不需要电池就可以保持数据。 该芯片

2023-07-18 17:08:13

兼容12个内核时钟周期。片内集成有62 KB非易失性Flash/EE程序存储器。片内同时集成4 kB非易失性Flash/EE数据存储器、256字节RAM和2 kB扩

2023-07-14 17:15:06

,用于构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32590集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指

2023-07-14 14:33:26

构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32591集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令

2023-07-14 14:09:44

构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32592集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令

2023-07-14 14:04:11

DS28E80为用户可编程非易失存储器芯片。与浮栅存储单元相比,DS28E80采用了耐γ辐射的存储单元技术。DS28E80具有248字节用户存储器,分成8字节大小的存储块,每个存储块可具有写保护

2023-07-13 17:01:58

DS28E80为用户可编程非易失存储器芯片。与浮栅存储单元相比,DS28E80采用了耐γ辐射的存储单元技术。DS28E80具有248字节用户存储器,分成8字节大小的存储块,每个存储块可具有写保护

2023-07-13 11:31:16

缓存服务器是什么?缓存服务器是专用网络服务器或充当在本地保存网页或其他互联网内容的服务器的服务。通过将以前请求的信息放入临时存储(或高速缓存)中,高速缓存服务器既可以加快数据访问速度,又可以减少

2023-07-07 17:48:59 353

353 RAID控制卡的日志存储器存放重要数据,如日志和数据写入完成、奇偶校验写入、错误日志等。在断电的情况下,控制器查询日志内存,以了解从哪里开始恢复。

2023-06-12 17:11:11 323

323

************************************************* *************************************

* 详细说明:

* 这个例子的目的是展示如何保存数据在 SRAM 存储器中通过

2023-06-05 09:47:48

我们正在构建一个设备来测量消耗。电路 ACS712 读取那一刻的消耗量,所以,我需要做一个每秒累加的方法。问题:非易失性内存有写入限制,所以我需要使用易失性内存。写入易失性存储器是否有一些限制?我们的想法是每秒读取一次 ACS712 并写入易失性存储器,每 10 分钟写入一次非易失性存储器。

2023-05-30 08:48:06

MRAM是一种新型的非易失性存储器技术,与传统的存储器技术相比,MRAM具有更快的读写速度、更低的功耗、更高的可靠性和更长的寿命。

2023-05-23 17:34:15 395

395 在单板设计中,无论是涉及到一个简易的CPU、MCU小系统或者是复杂的单板设计,都离不开存储器设计:

1、存储器介绍

存储器的分类大致可以划分如下:

ROM和RAM指的都是半导体存储器,ROM在系统

2023-05-19 15:59:37

标准的Flash存储卡,也是非易失性存储设备。USB大容量存储设备类(USB MSC)是Cs/FS文件系统最常用的大容量存储设备。U盘也是非易失性存储设备,在连接主机时被识别为外部硬盘驱动器。而RAM

2023-05-18 14:13:37

其数据始终是非易失性的,可以取代具有相同功能的FRAM、低功耗SRAM或nvSRAM,并有助于简化系统设计。由于STT-MRAM的非易失性和几乎无限的续航特性,它适用于工业设计中的代码存储、数据记录、备份存储器和工作存储器。

2023-05-12 16:31:39 268

268 单片机的程序存储器和数据存储器共处同一地址空间为什么不会发生总线冲突呢?

2023-05-10 15:17:56

80C51单片机中存储器是RAM和ROM分开编址的吗?求解答

2023-05-09 16:04:22

MRAM(Magnetoresistive Random Access Memory)是一种新型的非挥发性的磁性随机存储器。它拥有静态随机存储器(SRAM)的高速读取写入能力,以及动态随机存储器

2023-04-19 17:45:46 2544

2544 本章教程讲解DMA存储器到存储器模式。存储器到存储器模式可以实现数据在两个内存的快速拷贝。程序中,首先定义一个静态的源数据,存放在内部 FLASH,然后使用DMA传输把源数据拷贝到目标地址上(内部SRAM),最后对比源数据和目标地址的数据,判断传输是否准确。

2023-04-17 15:28:08

中,事情就会迅速恶化......我会遇到硬故障(有时调试器在调试时“死机”)。我已经为此工作了几天,似乎触发因素是以下情况之一:a) 整个 8 MByte 的 HyperRAM 在 MPU 中被定义为

2023-04-17 07:04:11

我目前正在使用 YOCTO sumo linux 内核 L4.14.98-2.3.1 和 imx6ul。在我的应用程序中,我们需要将安全数据(例如密钥)存储在安全非易失性存储 (SNVS) 区域

2023-04-14 07:38:45

我想用非易失性密钥获取CMAC值(仅验证甚至可以)。我正在使用修改后的“csec_boot_protection_s32k148”项目。初始化 CSEc 模块后,我使用给定的指令加载密钥 ROM

2023-04-10 06:34:32

和用于读取,写入和擦除数据的操作略有不同。而EEPROM指的是电可擦可编程只读存储器是一种存储器,可以在字节级别读取,写入和擦除数据。另一方面Flash是EEPROM的一种,在结构上以块的形式排列,在块中

2023-04-07 16:42:42

具有非易失性,即使切断电源,信息也不会丢失,而且它和DRAM一样可随机存取。表1存储器的技术规格比较在性能方面,自旋注入MRAM的读取1擦写时间都很短,均在2ns~20ns之间。它不需要闪存所必需

2023-04-07 16:41:05

据保留•无限的读/写耐力•无磨损•有竞争力的定价•稳定的制造业供应链•小尺寸BGA封装图1 引脚普通针MR3A16ACMA35是一个8Mb非易失性RAM,组织为512kx16,采用3.3V标称电源供电

2023-04-07 16:26:28

可用于断电(NMI)中断或其他目的的通用比较器。该器件的工作电压为2.7V至3.6V。FM33256B-G提供256Kb的非易失性FRAM存储器容量。快速的写入速度和无限的耐用性使该存储器可以用作额外

2023-04-07 16:23:11

在CH573存储中,分为用户应用程序存储区CodeFlash,用户非易失数据存储区DataFlash,系统引导程序存储区Bootloader,系统非易失配置信息存储区InfoFlash。一般在使用时

2023-04-07 11:46:50

我们正在尝试将内部 ROM 闪存用作 LPC 1768、LPC 55S16 中的辅助存储器(而不是 EEPROM)。是否可以将 FLASH 用作辅助存储器,如果可能,我们如何使用。请指导我们实现这一目标

2023-04-04 08:16:50

我目前正在尝试防止临时对称密钥在重新启动后保留在内存中。我的巧妙计划是使用 i.MX RT1064 处理器寄存器(保证在重启时归零)对它们进行异或,我在重启时将其设置为随机数。(这与非易失性寄存器

2023-03-23 07:07:21

电子发烧友App

电子发烧友App

评论