FAKRA&HSD技术条件l IEC60512电子设备连接器试验和测量检测项目(1)信号完整性测试类:特性阻抗、插入损耗、回路损耗、差分阻抗、远端串扰、近端串

2024-03-14 14:27:28

信号完整性(Signal Integrity,SI)在电子工程领域中具有极其重要的意义,也是现代电子设计的核心考量因素之一,尤其在高速PCB设计、集成电路设计、通信系统设计等领域,对保证系统性

2024-03-05 17:16:39

信号完整性(Signal Integrity,SI)在电子工程领域中具有极其重要的意义,也是现代电子设计的核心考量因素之一,尤其在 高速PCB设计、集成电路设计、通信系统设计 等领域,对保证系统性

2024-03-05 17:16:32 303

303

,特别是电源参考平面,应保持 低阻抗特性 ,可通过旁路电容和叠层调整来优化。2、多种电源的分割● 对于小范围的特定电源,如某IC芯片的核心工作电压,尽量在 信号层上敷铜 ,以确保电源层的完整性,但避免在

2024-02-21 21:37:07

的顶层和底层使用组合微带层时要小心。这可能导致相邻板层间走线的串扰,危及信号完整性。

按信号组的最长延迟为时钟(或选通)信号走线,这保证了在时钟读取前,数据已经建立。

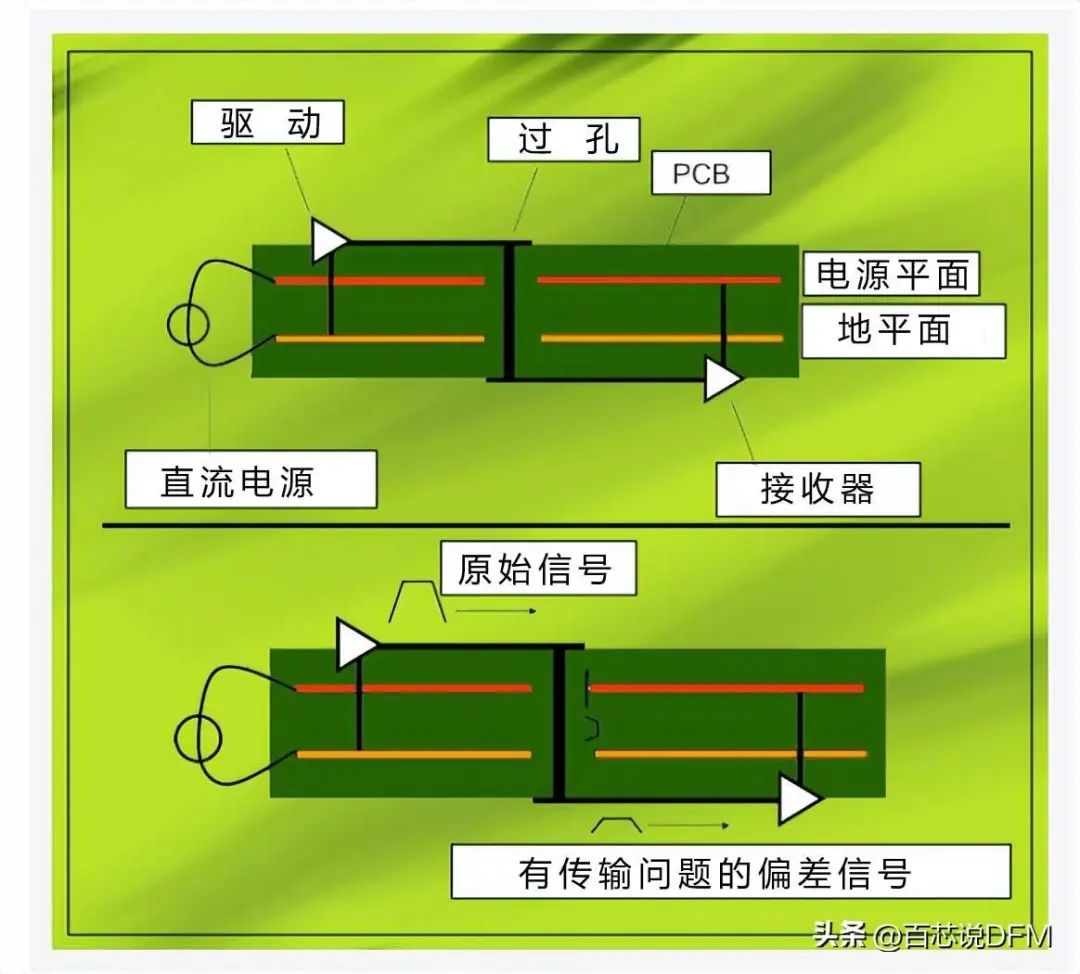

在平面之间对嵌入式信号进行走线

2024-02-19 08:57:42

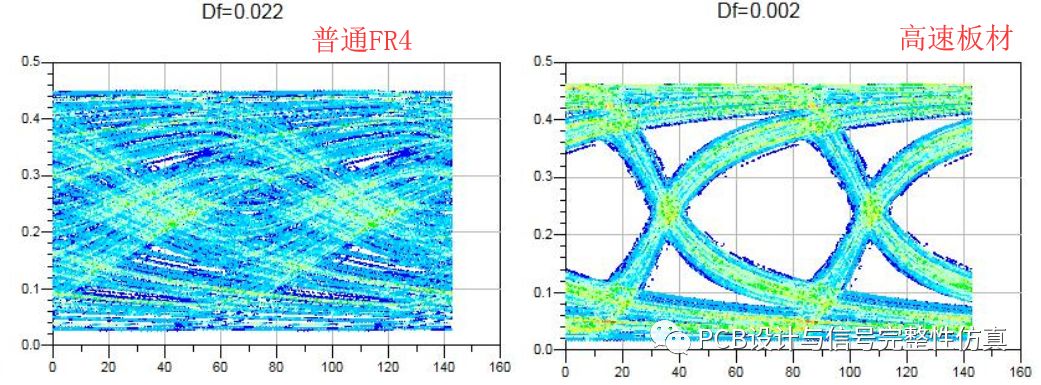

信号完整性(Signal Integrity,简称SI)指的是信号线上的信号质量。信号完整性差不是由单一因素造成的,而是由板级设计中多种因素共同引起的。破坏信号完整性的原因包括反射、振铃、地弹、串扰等。随着信号工作频率的不断提高,信号完整性问题已经成为高速PCB工程师关注的焦点。

2024-01-11 15:31:02 123

123 PCB上信号速度高、端接元件的布局不正确或高速信号的错误布线都会引起信号完整性问题,从而可能使系统输出不正确的数据、电路工作不正常甚至完全不工作,如何在PCB板的设计过程中充分考虑信号完整性的因素,并采取有效的控制措施,已经成为当今PCB设计业界中的一个热门话题。

2024-01-11 15:28:00 86

86

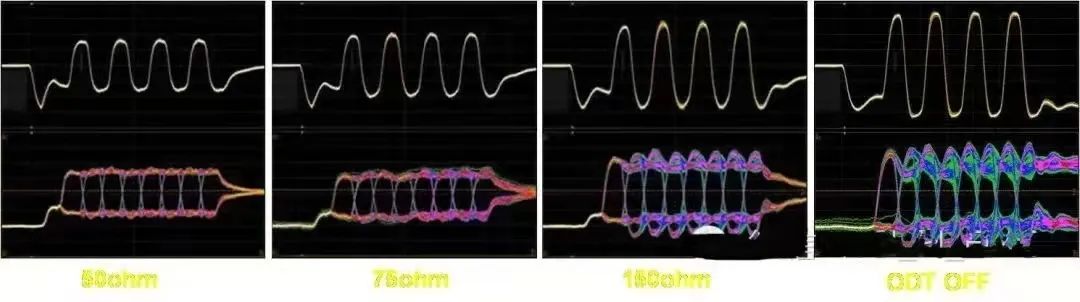

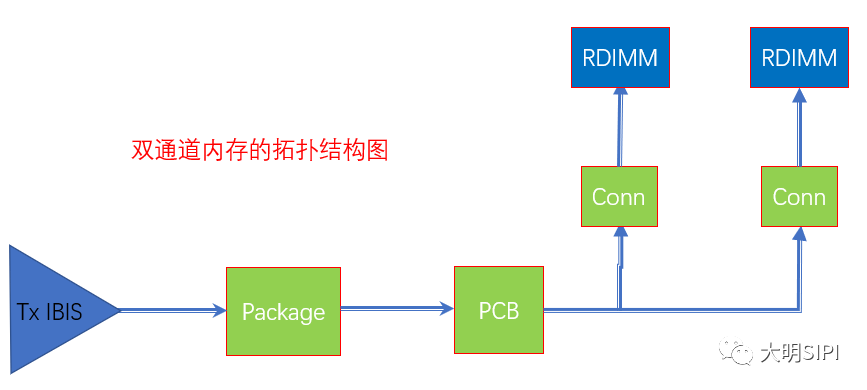

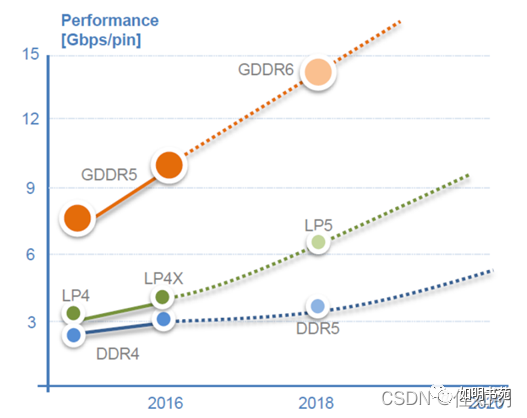

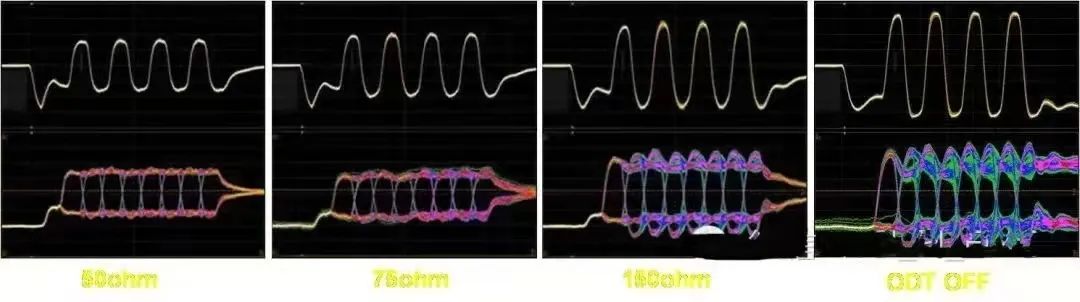

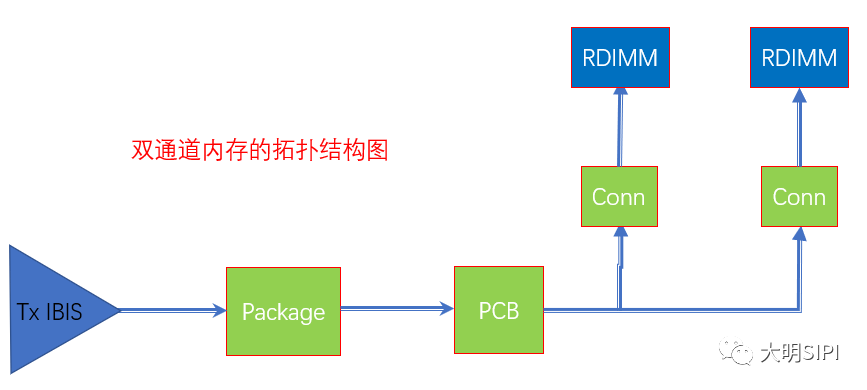

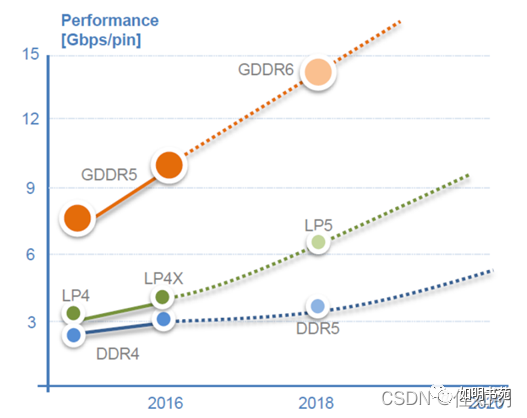

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 463

463

。LTC6754手册上显示为轨对轨输入,同样的TTL输入,当阈值小于150mV时,输出信号出现抖动,出现多个差分信号。比较阈值设置较大时,没有抖动。是需要增加下图的迟滞回路?该如何保持信号的完整性不展宽信号。

2024-01-05 12:06:25

电子发烧友网站提供《使用Keysight ADS收集信号完整性问答.pdf》资料免费下载

2023-12-25 09:53:32 0

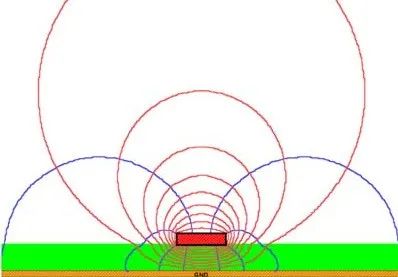

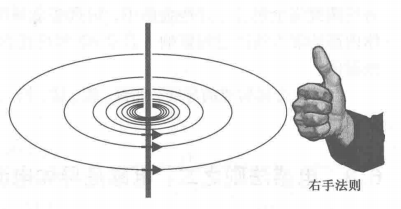

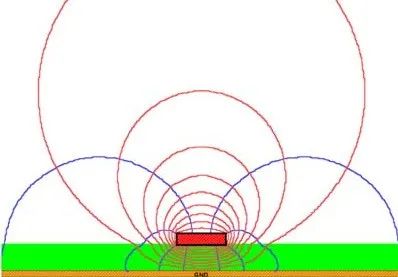

0 磁环如何抑制干扰信号 磁环抑制干扰信号是一种常见的电磁兼容技术,可以在电子设备中使用,以降低来自外部电磁场的干扰。 一、磁环的工作原理 磁环是一种环形磁性材料,如铁氧体或钢等。它具有高磁导率

2023-12-21 16:34:25 862

862 在“如何使用LTspice获得出色的EMC仿真结果"系列文章的第1分部中,我们介绍了针对电源器件、传导辐射和抗扰度的LTspice仿真工具。在第2部分中,我们将介绍LTspice和C程序的组合,旨在帮助设计人员了解和改善有线网络信号完整性。

2023-12-15 12:30:19 654

654

通信技术的飞速发展,我们面临着越来越多的挑战,如信号失真、干扰和衰减等问题。因此,了解和掌握信号完整性的原理和方法变得尤为重要。

2023-12-01 11:26:23 500

500 或无线电波。无论是哪种传输媒介,信号传输的目标都是确保信息能够准确地从发送端传输到接收端,而不会损失或失真。 然而,在实际的传输过程中,会发生一些不可避免的干扰,其中包括串扰和反射,这些干扰会对信号完整性产生负面影

2023-11-30 15:21:55 190

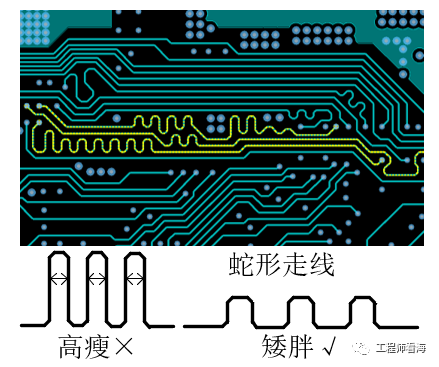

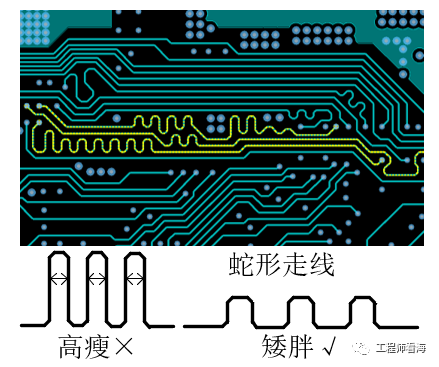

190 中的噪声和干扰,提高信号的完整性和可靠性。在设计和调整走线拓扑架构时,需要考虑信号线路的长度、走向、分布以及与其他线路之间的距离等因素。下面将详细介绍走线的拓扑架构及其调整方法。 1. 单线拓扑架构: 单线拓扑架构是最

2023-11-24 14:44:40 271

271 对于只有一个输出端的时钟信号线,如何实现差分布线? 在设计电路或系统时,差分信号线被广泛应用于传输时钟信号。差分信号线可以有效地抵抗噪声、串扰和损耗,从而提高信号完整性和系统性能。对于只有一个输出

2023-11-24 14:32:30 269

269 在高速设计中,如何解决信号的完整性问题? 在高速设计中,信号完整性问题是一个至关重要的考虑因素。它涉及信号在整个设计系统中的传输、接收和响应过程中是否能够维持其原始形态和性能指标。信号完整性问题可能

2023-11-24 14:32:28 227

227 信号传输并非严格针对网络设计师,您的PCB设计可能会遇到相同类型的问题。由于您无需费力地摆弄耳朵,因此防止电源完整性和信号完整性问题对于您的PCB设计流畅且无静电至关重要。

2023-11-08 17:25:01 344

344

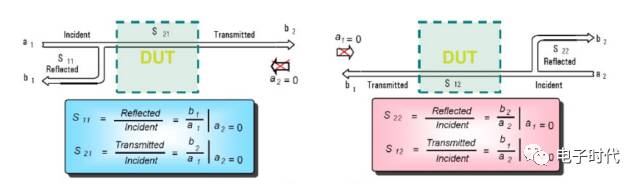

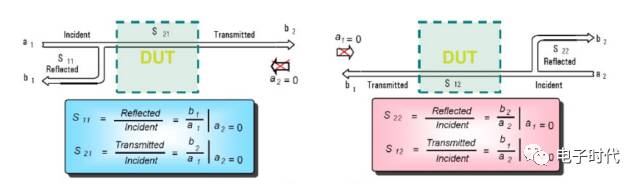

有源等等都会是非常低的标准,但是对于高速信号,这些条件就会变得非常苛刻,不然测试测量结果就会出现较大偏差。 其中比较重点的方向就是信号完整性测试,对于信号完整性的测试手段有很多,有从频域的,时域的角度,也有一

2023-11-06 17:10:29 337

337

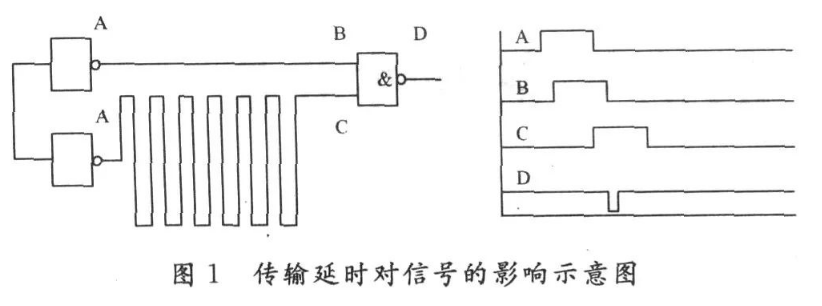

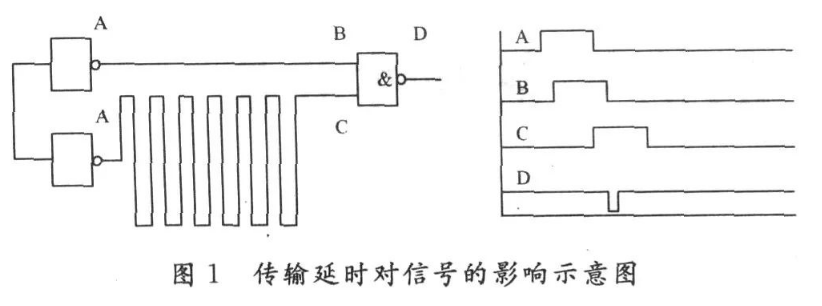

一类问题是与信号路径相关的反射问题和相邻路径间的串扰问题,这类问题都与信号的上升时间和时钟工作频率有关,称之为信号路径问题。

2023-10-31 10:37:49 224

224

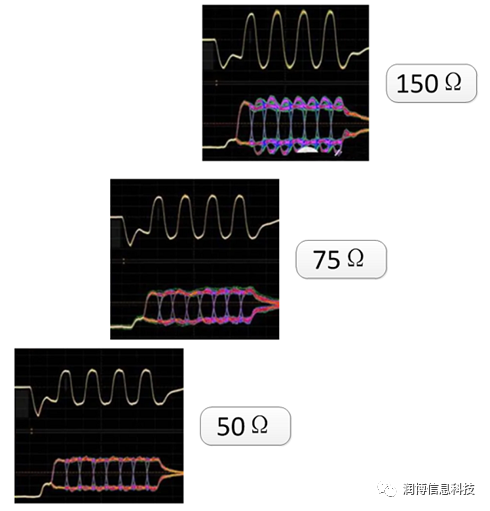

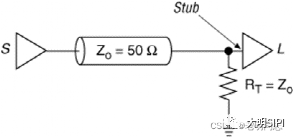

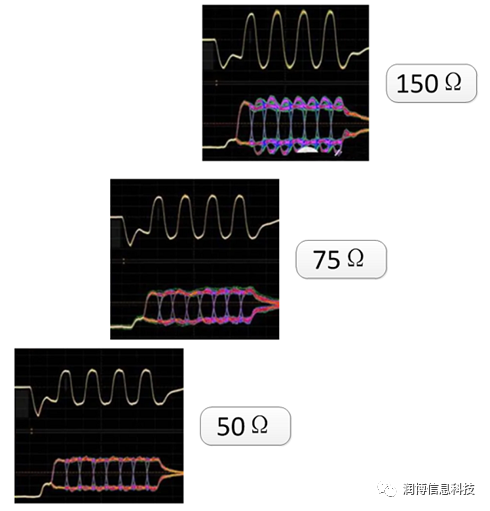

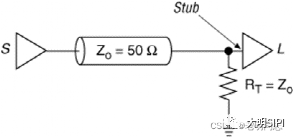

为什么电路端接电阻能改善信号完整性? 在电路设计中,信号完整性是一个极其重要的概念。信号完整性是指信号在传输、转换和处理过程中所遭受的失真、干扰或损失。这些信号可能是模拟信号或数字信号,它们的完整性

2023-10-24 10:04:52 372

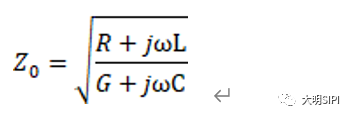

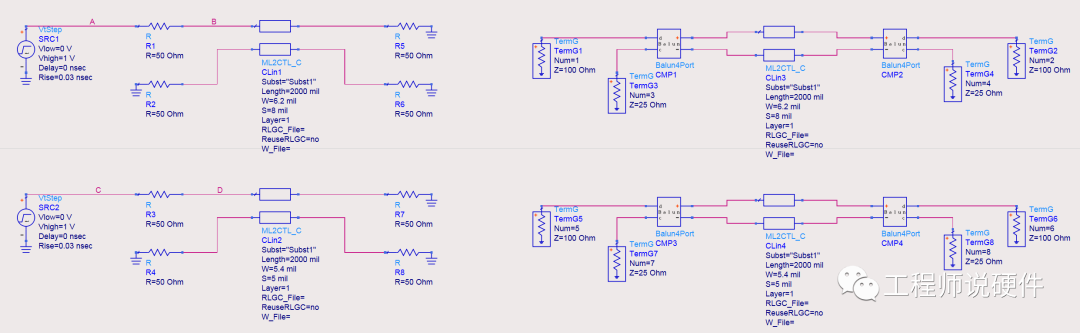

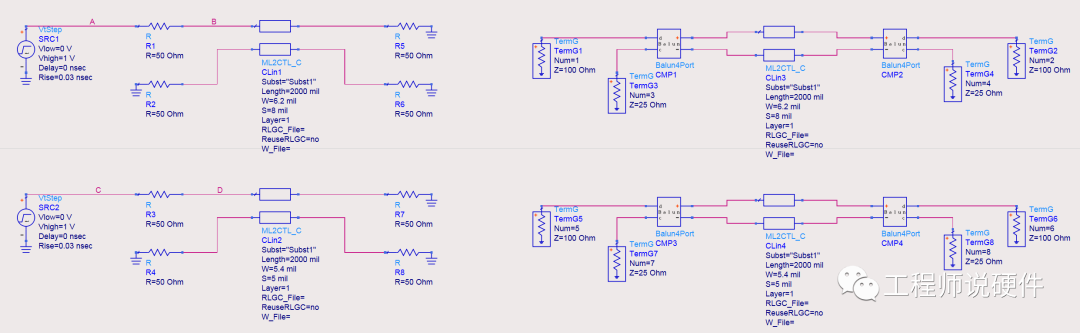

372 什么是传输线?什么是信号完整性分析?为什么传输线要测试差分信号? 什么是传输线? 传输线是指电路板上的导线,它们的特点是导线两端的阻抗不同。这些导线可以用于传输电信号,也可以用于传输数据信号。传输线

2023-10-23 10:34:34 334

334 正式发布2023年10月13日Cadence15年间最具影响力的版本更新之一AllegroX/OrCADX23.1本文要点:掌握信号完整性基础知识实现良好信号完整性的PCBlayout技术有助于提高

2023-10-21 08:13:07 688

688

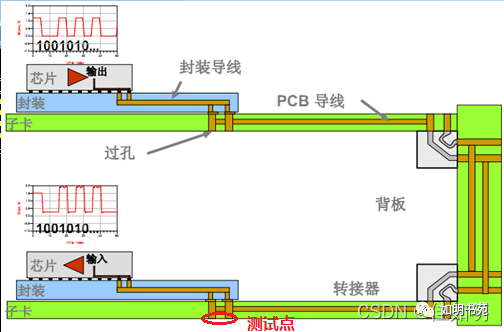

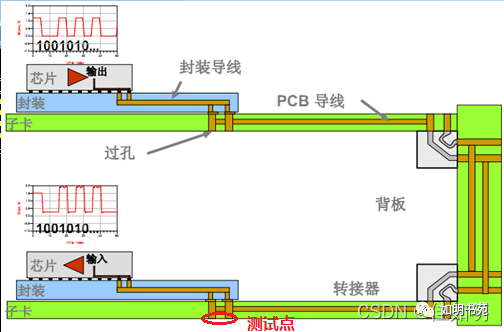

完整性需要在整个系统和组件设计过程中加以考虑。与过去不同的是, 互连不再是事后考虑的问题 。随着上升时间的缩短和时钟频率的提高,曾经被认为是电气透明的连接器和电缆会对系统传输信号的质量产生重大影响。这些因素包括 串扰、回波损耗、插入损耗和电磁干扰(EMI) 等因素都会对确定哪种互连解决方

2023-10-19 15:09:49 116

116

信号完整性分析在高频信号中,在图像处理中有何应用,s参数如何确定其最佳标准。

2023-10-18 07:32:09

通孔的阻抗控制对PCB信号完整性会触发什么样的影响?

2023-10-17 11:56:11 254

254

信号完整性是指信号能够在传输过程中保持其原有特征和形状的能力。

2023-10-01 14:12:00 2468

2468

广义上讲,信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。

2023-09-28 11:48:37 1148

1148

信号完整性(Signal Integrity,SI)是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该信号是完整的。

2023-09-28 11:27:47 1002

1002

手工连线面成的样机同规范布线的最终印制板产品一样都能正常工作。

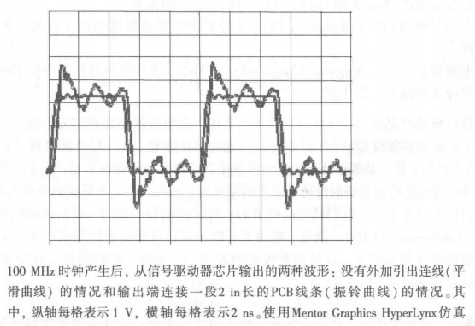

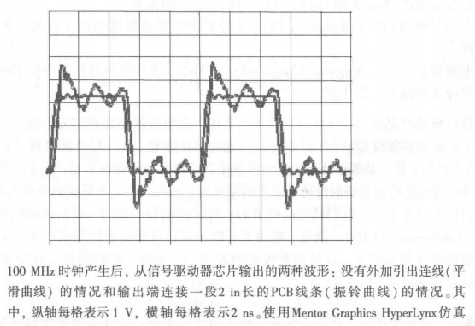

但是现在时钟频率提高了,信号上升边也已普遍变短。对大多数电子产品而言,当时钟频率超过100MHz或上升边小于1 ns时,信号完整性效应

2023-09-28 08:18:07

信号完整性问题和印制电路板设计

2023-09-28 06:11:27

无菌药品完整性检漏仪 压力衰减测试是一种用于检测无孔、刚性或柔性包装中泄漏的定量测量方法。如果加压气体的引人导致包装壁或密封件破裂,则该测试是破坏性的。如果将气引人测试样品不会损害包装屏障

2023-09-27 15:54:16

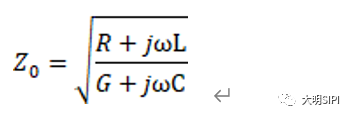

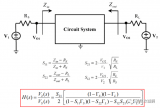

信号完整性分析是以电磁场理论作为基本理论,所涉及的基本电磁理论基础包括麦克斯韦方程组、传输线理论、匹配理论等。

2023-09-25 14:20:32 426

426

串扰是四类信号完整性问题之一,指的是有害信号从一个线网传递到相邻线网。任何一对线网之间都存在串扰。

2023-09-25 11:29:07 690

690

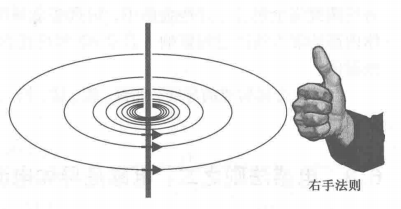

电感是一个非常重要的电气参数,因为它影响几乎所有的信号完整性问题。对于线间耦合、电源分配网络及电磁干扰问题,电感就是信号沿均匀传输线传播过程中遇到的突变。

2023-09-22 11:14:10 739

739

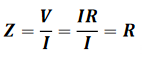

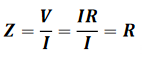

我们把阻抗定义为电压和电流之比,通常用大写字母Z表示。Z = V/I。在信号完整性扮演重要角色的高速数字系统中,信号是指变化的电压或变化的电流。

2023-09-21 16:45:54 433

433

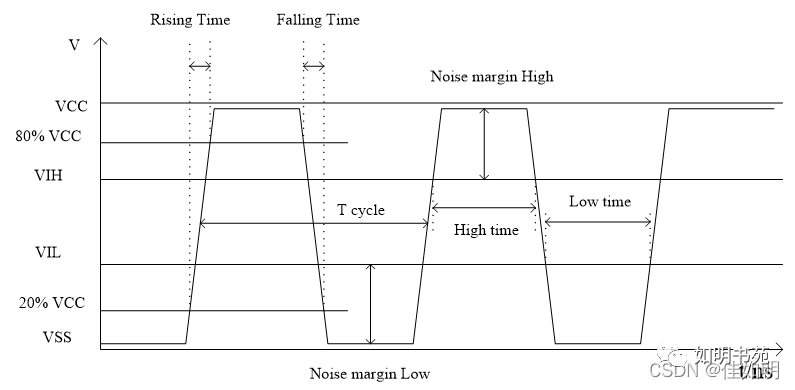

信号完整性是指在规定的时间内,信号从源端传输到接收端,信号不失真(能判断出信号的高低电平)。

2023-09-21 16:30:14 1270

1270

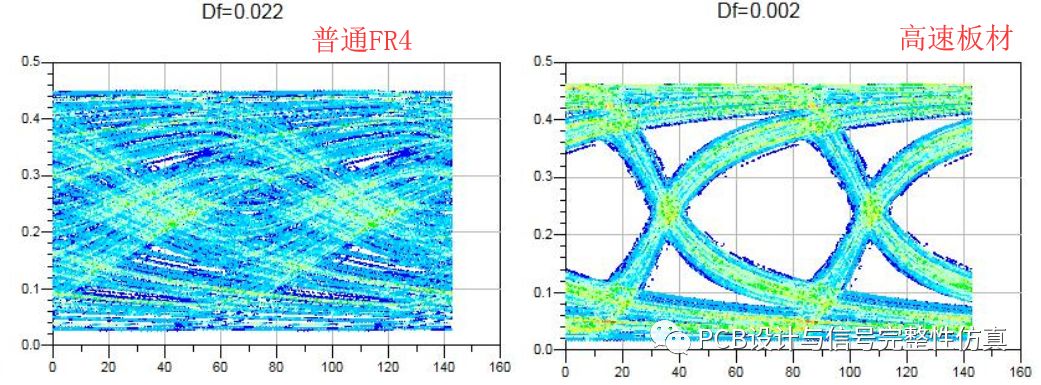

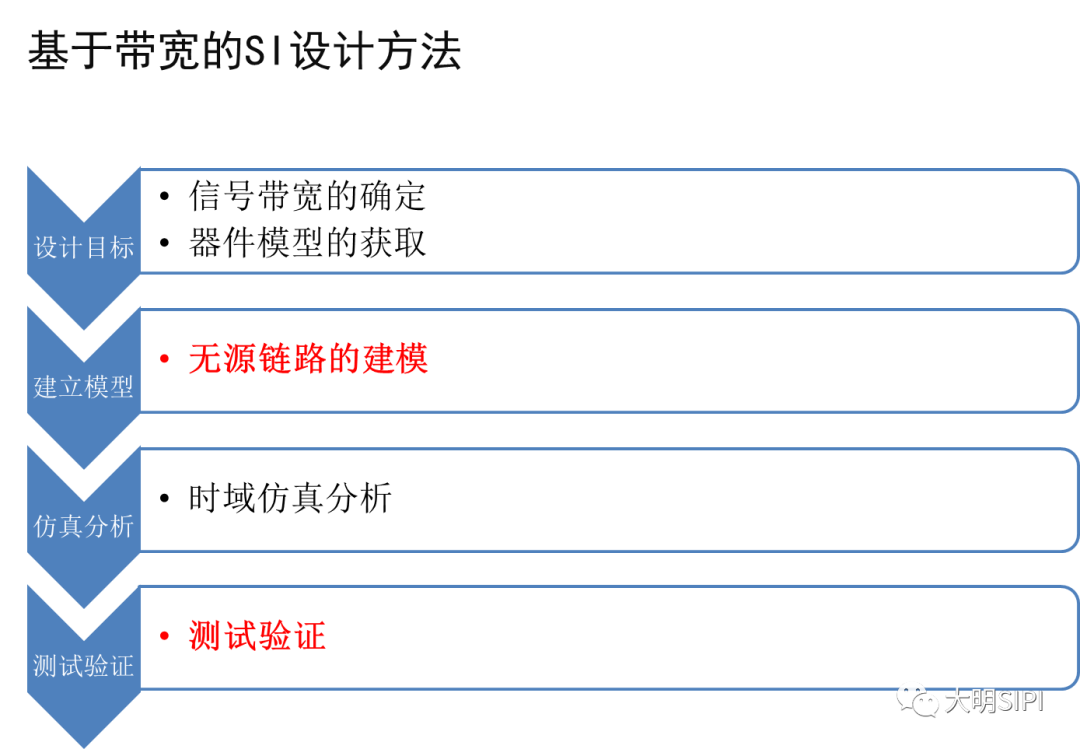

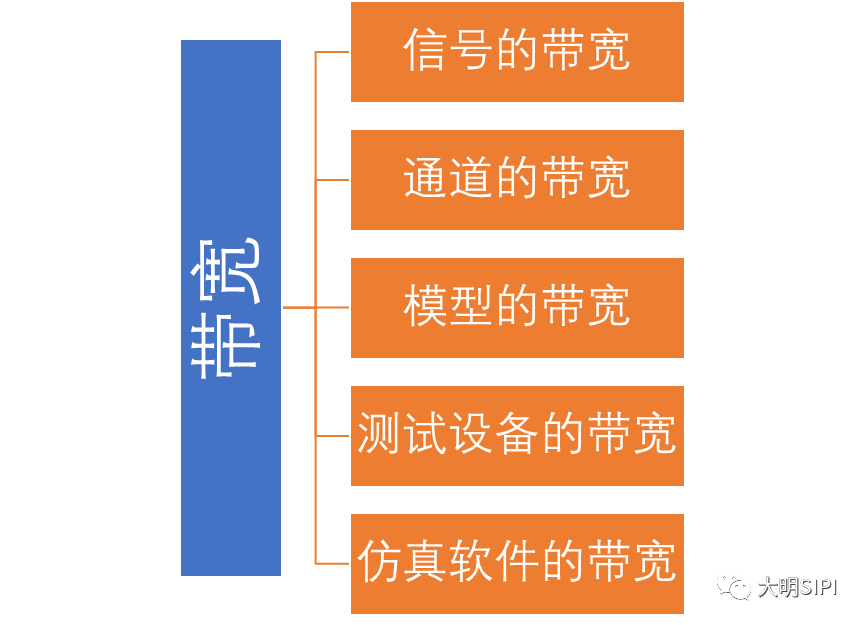

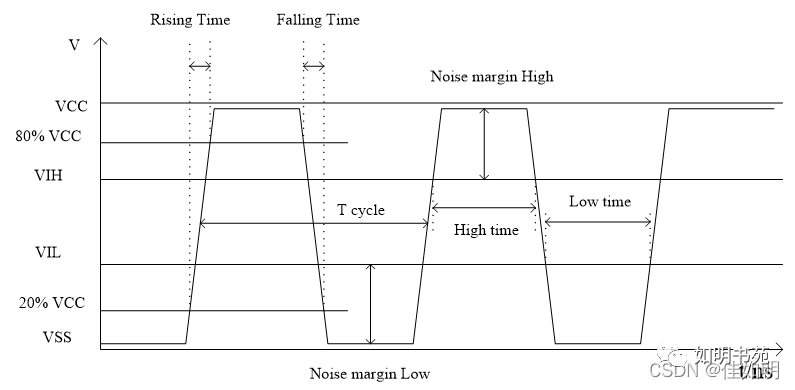

信号完整性设计,在PCB设计过程中备受重视。目前信号完整性的测试方法较多,从大的方向有频域测试、时域测试、其它测试3类方法。

2023-09-21 15:43:30 781

781

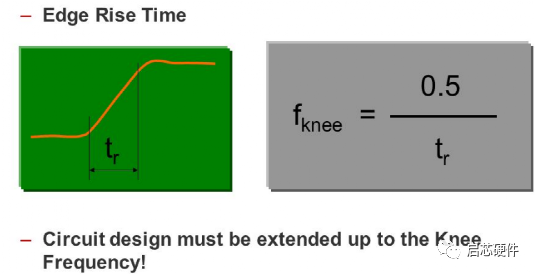

件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 1764

1764 电子发烧友网站提供《基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响.pdf》资料免费下载

2023-09-13 09:56:49 0

0 时钟信号电磁辐射很强的原因是什么? 时钟信号电磁辐射很强的原因是因为时钟本身包含了很多电子元器件,可以发射出强烈的电磁波。这些电磁波可能会对周围的环境和人体造成不良影响,这也是时钟信号电磁辐射存在

2023-09-12 16:08:01 621

621 什么是信号完整性?为什么它如此重要呢?如何更好地保证信号完整性?下面将为您详细阐述这些问题。 一、什么是信号完整性 所谓信号完整性,即保证信号在从信号发生器到接收端完整、正确地传输的能力,即保证电路中的信号与信号发生器的输出

2023-09-08 11:46:58 917

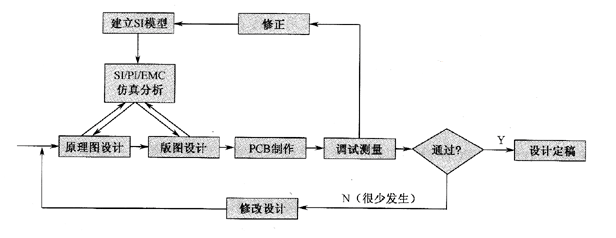

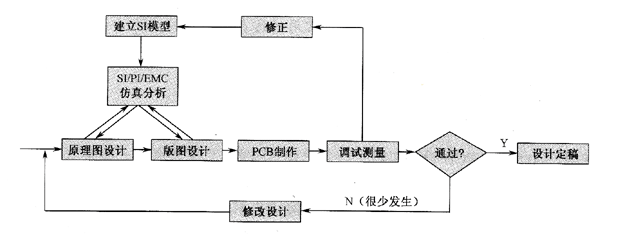

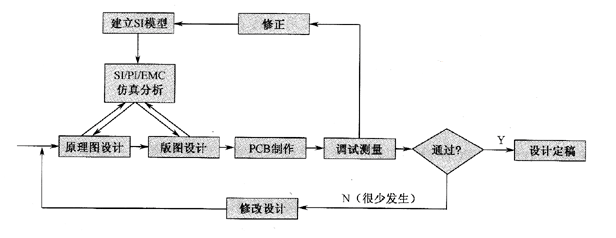

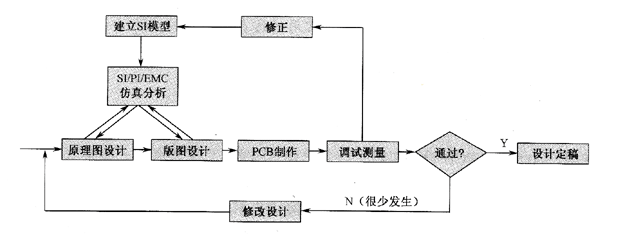

917 在原理图设计完成后,结合PCB的叠层设计参数和原理图设计,对关键信号进行信号完整性原理分析,获取元器件布局、布线参数等的解空间,以保证在此解空间中,终的设计结果满足性能要求。

2023-09-01 17:02:03 325

325

摘要/前言 一种新的连接器系统 通过改善电源完整性来提高信号完整性 。优化电源完整性可提供更大的信号完整性余量,并提高电源和热效率。 高速连接器系统的BOR(Breakout Region

2023-08-31 11:33:15 406

406

一种新的连接器系统通过改善电源完整性来提高信号完整性。优化电源完整性可提供更大的信号完整性余量,并提高电源和热效率。

2023-08-30 10:37:36 775

775

在原理图设计完成后,结合PCB的叠层设计参数和原理图设计,对关键信号进行信号完整性原理分析,获取元器件布局、布线参数等的解空间,以保证在此解空间中,终的设计结果满足性能要求。

2023-08-29 14:34:02 191

191

应用:本示例代码使用 NUC1262 CRC 对代码完整性进行自我验证。

BSP 版本: NUC1262_Series_BSP_CMSIS_V3.00.001

硬件

2023-08-29 06:49:52

随着现代数字电子系统突破1GHz的壁垒,PCB板级设计和IC封装设计必须都要考虑到信号完整性和电气性能问题。凡是介入物理设计的人都可能会影响产品的性能。所有的设计师都应该了解设计如何影响信号完整性

2023-08-22 12:40:57 261

261 用小的成本,快的时间使产品达到波形完整性、时序完整性、电源完整性的要求;我们知道:电源不稳定、电源的干扰、信号间的串扰、信号传输过程中的反射,这些都会让信号产生畸变,

2023-08-17 09:29:30 3108

3108

信号完整性分析的目的就是用小的成本,快的时间使产品达到波形完整性、时序完整性、电源完整性的要求;

2023-08-16 10:09:08 946

946

电磁干扰是指电子产品向外发出噪声,引起设备、装置或系统工作性能降低的电磁变化现象,主要分为传导干扰和辐射干扰两种。传导干扰是指电磁通过导电介质把信号从一个电网络上耦合(干扰)到另一个电网络上;辐射干扰是指干扰源(电磁)通过空间把其信号耦合(干扰)到另一个电网络上。

2023-08-01 14:34:53 232

232

信号完整性分析第1版中文版

2023-07-14 11:07:42 0

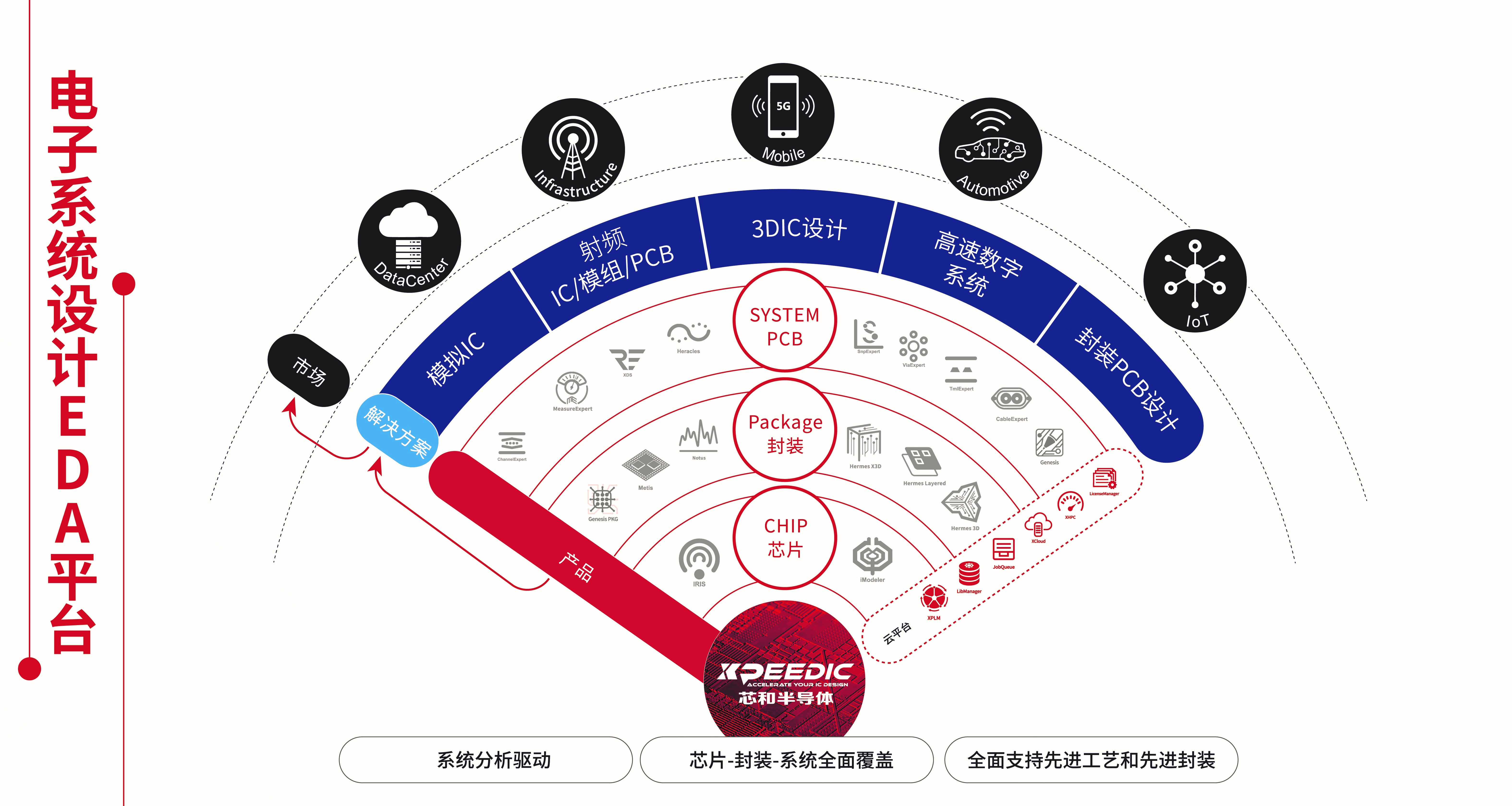

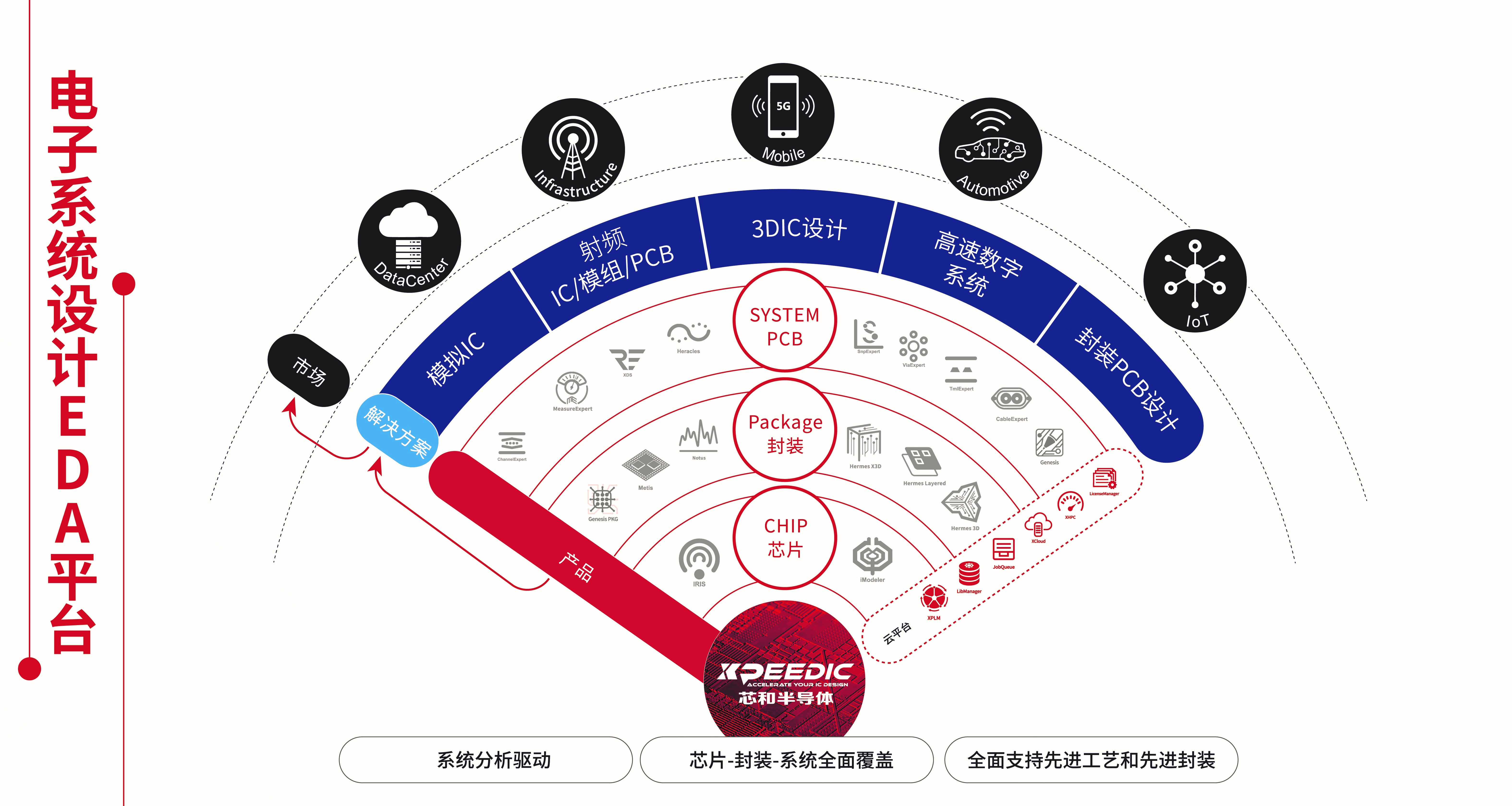

0 ) EDA2023软件集 ,涵盖了众多先进封装和高速设计领域的重要功能和升级。 继上月在国际微波展IMS上发布射频EDA解决方案2023版本之后,芯和半导体此次发布了全系列EDA产品2023版本的剩余部分,包括针对先进封装的2.5D/3D信号完整性和电源完整性仿真,以及3D EM电磁仿真平台、多场协

2023-07-11 17:15:13 559

559 ) EDA2023软件集,涵盖了众多先进封装和高速设计领域的重要功能和升级。 继上月在国际微波展IMS上发布射频EDA解决方案2023版本之后,芯和半导体此次发布了全系列EDA产品2023版本的剩余部分,包括针对先进封装的2.5D/3D信号完整性和电源完整性仿真,以及3D EM电磁仿真平台、多场协同

2023-07-11 09:58:22 226

226

串扰 :即两条信号线之间的耦合引起的线上噪声干扰。

2023-07-06 09:15:48 844

844

今天给大家分享的是PCB信号完整性、9个影响PCB信号完整性因素、提高PCB信号完整性规则。

2023-06-30 09:11:22 806

806

业界经常流行这么一句话:“有两种设计师,一种是已经遇到了信号完整性问题,另一种是即将遇到信号完整性问题”。固态硬盘作为一种高集成度的高时钟频率的硬件设备,信号完整性的重要性不言而喻。借着这句话本文主要跟大家聊下信号完整性的一些基本内容。

2023-06-27 10:43:26 1102

1102

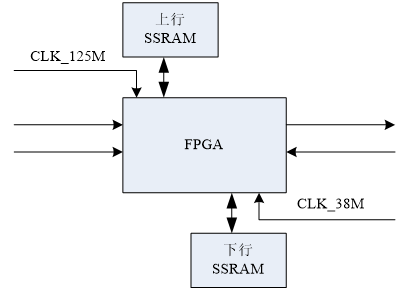

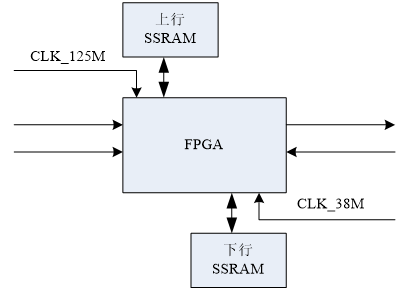

本文结合某单板(下文中统一称M单板)FPGA调试过程中发现地弹噪声造成某重要时钟信号劣化从而导致单板业务丢包的故障,来谈下如何最大程度地降低地弹噪声对单板信号完整性影响。

2023-06-26 10:17:37 381

381

随着速率的不断提高,信号能够在链路中传输的难度越来越大,信号质量会不断下降,我们把高速信号在传输中遇到各种问题统称为信号完整性问题。

2023-06-21 14:17:56 1019

1019

在模拟电路时期以及模拟向数字信号过渡的初期,由于电路的信号速度并不高,这个时候信号完整性的问题并不突出。

2023-06-21 11:37:16 822

822

信号完整性分析是一个很复杂的系统工程,它是各种影响信号质量和时序的问题的叠加组合。且随着信号速率的提高,信号完整性问题变得越来越复杂,需要考虑的因素越来越多。

2023-06-15 15:07:59 989

989

终端端接对于信号完整性有着重要的意义,它和源端匹配一样都是解决信号完整性问题的重要手段。

2023-06-15 11:08:03 892

892

信号完整性分析是基于传输线理论的,研究信号完整性必须从认识传输线开始,而传输线中最基本的概念就是阻抗和反射。

2023-06-14 15:40:58 3720

3720

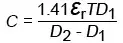

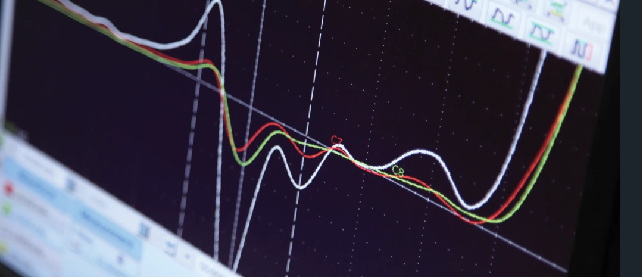

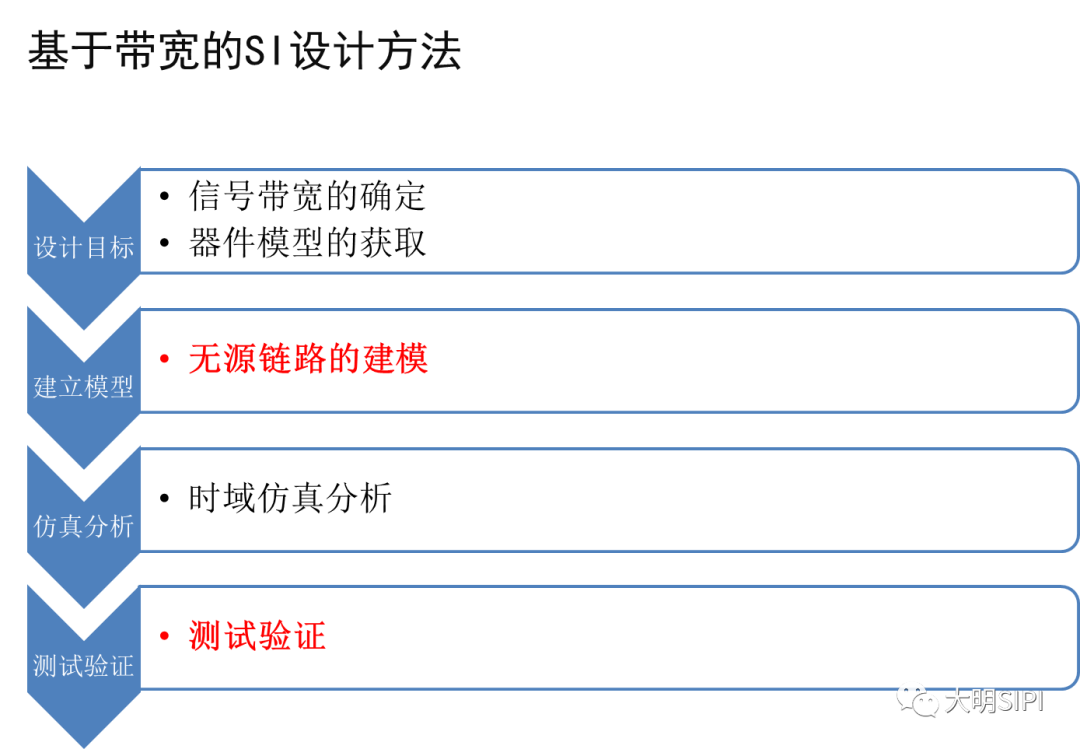

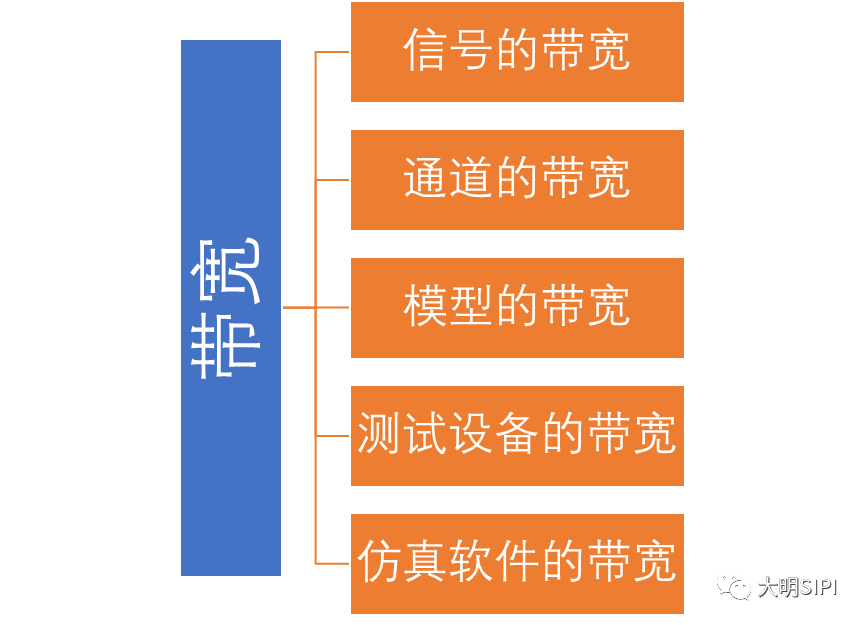

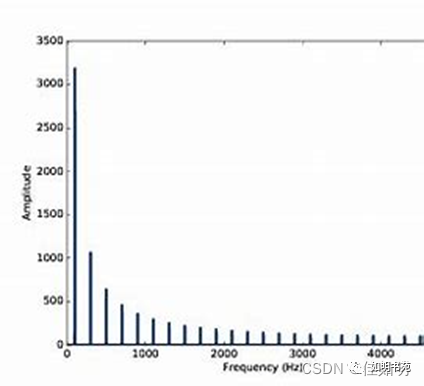

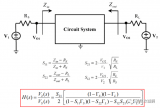

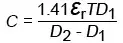

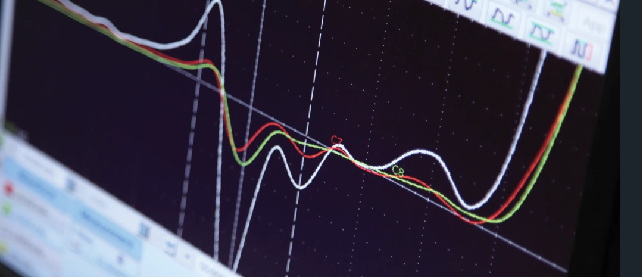

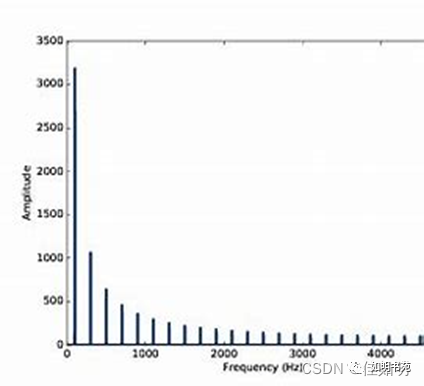

信号完整性分析的两个维度--时域和频域,而带宽是连接时域和频域的桥梁。同样,带宽也将信号的特性、传输通道、测试设备联系在一起,可见带宽是信号完整性分析中非常重要的一个概念。

2023-06-14 10:36:10 598

598

时域是真实存在的域,频域只是一个数学构造,但频域对我们分析解决信号完整性问题非常重要。那么如何将频域和时域建立联系方便的分析解决信号完整性问题?因此引出了时域和频域之间的纽带--带宽。对于信号完整性分析来说,带宽实在是太重要了,这里再唠叨唠叨。

2023-06-14 10:20:06 1045

1045

广义上讲,信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。

2023-06-14 10:15:35 1352

1352

早在十几年前信号完整性还并没有进入硬件工程师的视野,工程师对付干扰、噪声等问题的“三大法宝”就是接地、滤波、屏蔽,这种仅凭工程师的经验的做法显然非常粗放。

2023-06-14 10:11:21 599

599

我们经常听到身边的硬件工程师们提到关于信号完整性的话题。那么信号完整性具体是指什么呢?

2023-06-12 17:41:25 369

369

信号完整性研究的是如何使驱动器输出的信号传输到接收器件并被正确接收。

2023-06-12 17:22:48 1576

1576

信号完整性(Signal Integrity,SI),也就是我们通常所说的信号质量。随着信号速率的提高,数字信号的传输已经不能只考虑逻辑上的实现,而要考虑如何能够使接收器件接收到正确的信号波形。

2023-06-12 15:48:28 3974

3974

在模拟电路时期以及模拟向数字信号过渡的初期,由于电路的信号速度并不高,这个时候信号完整性的问题并不突出。

2023-06-09 15:22:32 702

702

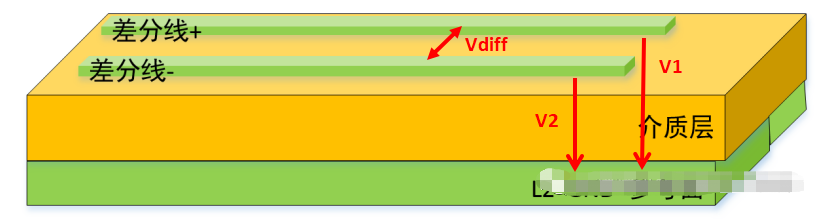

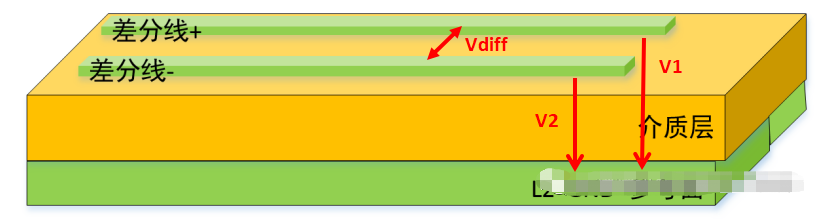

本章我们开始《信号完整性基础》 系列第五章节差分信号相关知识的讲解。随着信号速率的不断提高,传统并行接口的应用挑战越来越大,基于差分信号的Serdes接口越来越普及,差分信号在其中的重要性不言而喻。

2023-06-09 10:37:38 2874

2874

PCB中信号完整性分析的基础知识可能不是基本的。信号完整性仿真工具非常适合在原理图和布局设计期间计算不同网络中信号的行为,但您仍然需要采取一些步骤来解释结果。

2023-06-09 10:31:57 628

628

差分信号是共模信号和差模信号的叠加,理想情况下共模信号是恒定的。

2023-06-09 09:08:13 1898

1898

模拟电路设计(电源or信号链)和电源完整性,职业发展前景差距大吗?

2023-06-07 11:31:37

随着现代电子产品的快速发展,高速连接器LM393越来越广泛地应用于各种领域。高速连接器的信号完整性分析是确保高速数据传输的关键之一。本文将介绍如何通过使用仿真工具和适当的测试方法来实现高速连接器信号完整性分析。

2023-06-04 14:30:00 983

983 在嵌入式产品应用中,为了保证系统数据在存储或者传输过程中的完整性,固件映像中通常包含完整性检查(integrity checks),以检测映像是否损坏。例如,bootloader可以基于完整性检查

2023-05-18 13:50:32

起因:

产品执行研发信号完整性一致性验证时,DPoC 5.4Gbps Pre-Emphasis Level over the criteria,具体数据如下,4个DP Lane

2023-05-16 15:32:40

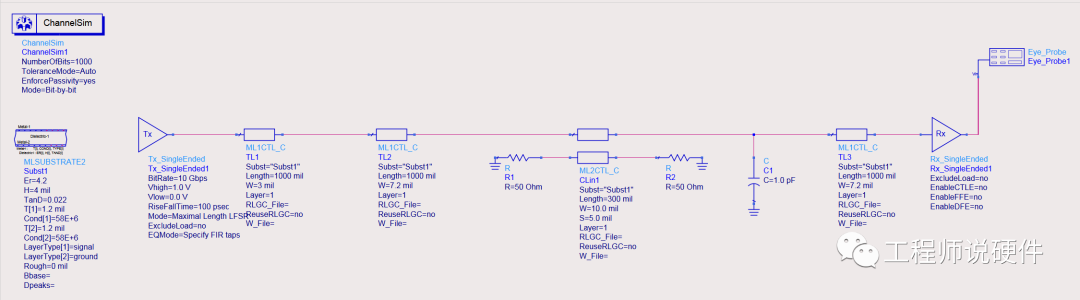

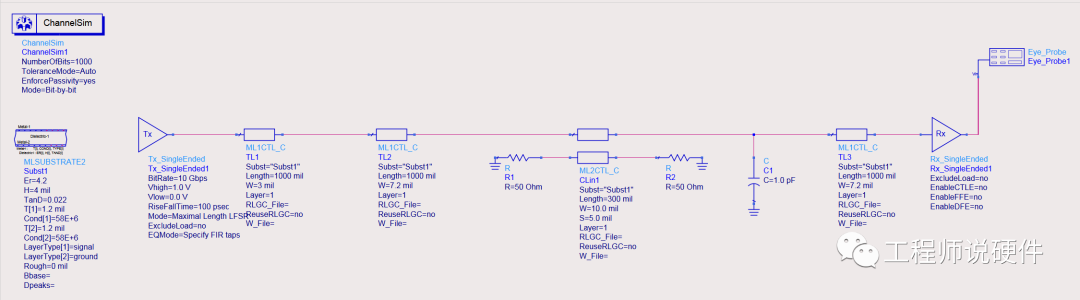

数据中心利用发射系统和接收系统之间的通道,可以准确有效地传递有价值的信息。如果通道性能不佳,就可能会导致信号完整性问题,并且影响所传数据的正确解读。

2023-05-15 09:03:29 380

380

编者注:在分析信号完整性和电源完整性问题时经常会提到在时域中分析和在频域中分析。不管是什么分析,分析都是同一个对象。因为有的问题在时域中难以描述,比如能量损失,因为能量是一个系统概念,很难对应到物理

2023-05-14 10:45:12 540

540

差分信号是指利用两个输出驱动pin去驱动两根传输线。这两根传输线,一根传输信号,另一根传输它的互补信号。接收端看到的信号是这两条传输线上的信号压差。差分对就是用来传输一对差分信号,并且存在耦合关系的传输线。例如LVDS就是一种常见的低压差差分信号。

2023-05-06 16:02:47 6076

6076

信号完整性包括由于互连结构、电源系统、电子器件等引起的所有 信号质量及延时等问题 。高比特率和更长的传输距离会让信号受到噪声,失真,损耗等影响。

2023-05-06 14:43:53 288

288 本章我们开始《信号完整性基础》 系列第四章节S参数相关知识的讲解。 S参数能反映在频域范围内传输信号、反射信号的特性,是我们在做PCB SI仿真时最常用的手段。

2023-05-05 12:26:59 2293

2293

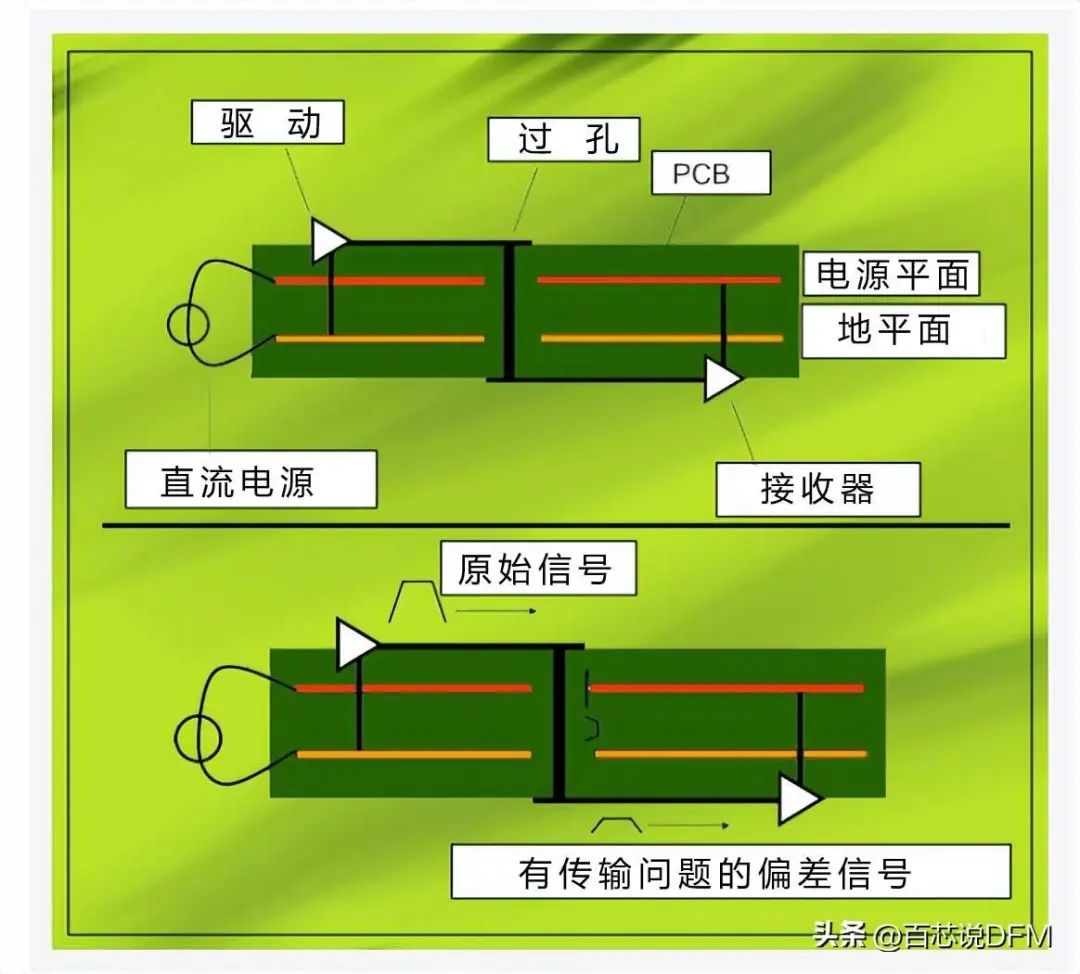

回流最终通过电容耦合回到GND,形成了完整的回流路径。但由于去耦电容位置摆放的问题可能会增大信号的回流面积,从而影响信号质量,所以对于多数高速信号,参考GND是比较好的选择。

图4 参考平面选择

2023-04-28 16:03:15

发生。

它根据最高保真度的电磁数值分析来求解PCB和IC封装高速数字设计所涉及的所有方面。

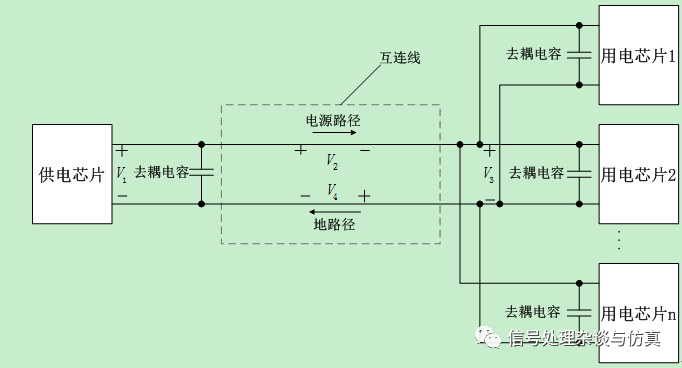

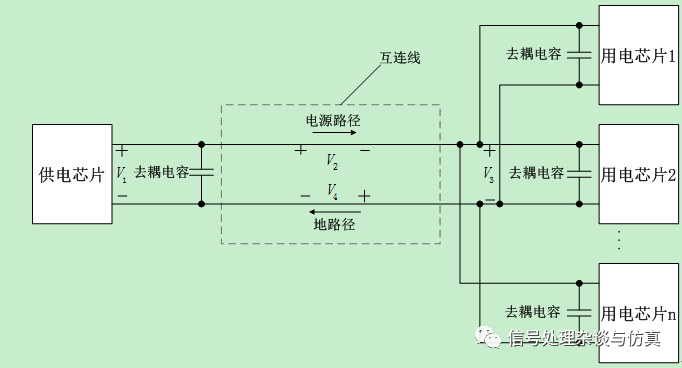

所谓电源完整性是指系统供电电源在经过电源分配系统后在需要供电的器件端口处相对于该器件端口对工作电源

2023-04-24 11:46:21

我们经常听说PCB走线间距大于等于3倍线宽时可以抑制70%的信号间干扰,这就是3W原则,信号线之间的干扰被称为串扰,串扰是怎么形成的呢?

2023-04-18 11:06:22 992

992

信号沿互连线传播时,如果感受到的瞬态阻抗发生变化,则一部分信号被反射回源端,另一部分信号发生失真并且继续向负载端传输过去。这是单一信号网络中信号完整性主要的问题。反射和失真会导致信号质量下降,例如振铃。过强的振铃会超过逻辑电平的阈值,造成误触发。

2023-04-15 15:50:38 1186

1186

的问题了。 防止电磁干扰的方法: 1)减小信号线的回路(磁场的相互抵消)。即让信号线和与它构成回路的回流信号线尽量的靠近。因为它们所产生的电磁场正好是相反的,距离越靠近,电磁场就可以相互抵消得越多

2023-04-11 16:49:29

发生。 它根据最高保真度的电磁数值分析来求解PCB和IC封装高速数字设计所涉及的所有方面。 所谓电源完整性是指系统供电电源在经过电源分配系统后在需要供电的器件端口处相对于该器件端口对工作电源要求

2023-04-11 15:17:05

高速pcb的信号完整性问题主要有哪些?应如何消除?

2023-04-11 15:06:07

现有产品设计对信号完整性很重视,但对于电源完整性的重视好像不够,主要是因为,对于低频应用,开关电源的设计更多靠的是经验,或者功能级仿真来辅助即可

2023-04-10 09:16:16 1018

1018 高速pcb的信号完整性问题主要有哪些?应如何消除?

2023-04-07 17:32:10

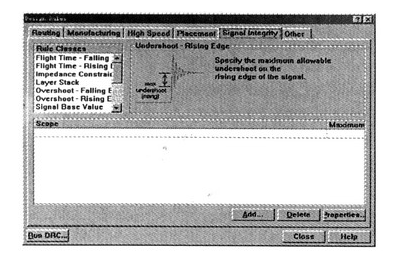

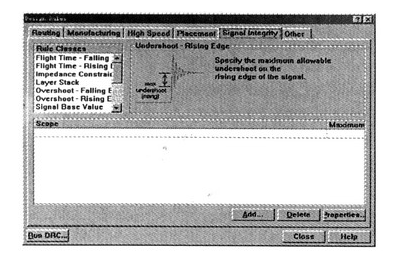

信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

2023-04-03 10:40:07 888

888 避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加groundguard/shunttraces在模拟信号旁边。

2023-03-30 14:33:06 262

262 由信号频率升高、上升时间减小所引起PCB互连线上的所有信号质量问题都属于信号完整性的研究范畴。本论文的主要研究可概括为传输线在PCB设计制造过程中所产生的信号完整性问题,具体分为三个方面

2023-03-27 10:40:30 0

0

电子发烧友App

电子发烧友App

评论