STM8S003F3能否输出2路可调的相位相差180度的独立PWM波形?

两路pwm波形有死区时间可控制

2024-03-22 06:34:43

,现货库存CYV15G0203TB-BGXCCYV15G0101DXB-BBXCCYV15G0204TRB-BGXCCYV15G0401DXB-BGXCCYV15G0104TRB-BGXC如需其他型号,欢迎点击右侧客服咨询!!!

2024-02-26 10:08:43

(如i2c1)。因为例程中的时钟初始化,只有机器定时器1是分到group1和core1的,所以不太确定。

3-只有共享内存(linker文件中已配好16k)是双核都能访问的,且该ram区只能

2024-02-06 21:14:30

我有[i] KIT _A2G_[i] TC377 _[i] 5V _TRB,如何使用 HighTec IDE 和板载 DAS 来 下载和调试?

2024-01-26 07:47:50

使用两片LTM4630可以实现三路并联(电压为1.0),另一路独立输出吗(电压为1.2V).

2024-01-04 07:00:37

FIFO方案,则无法正常工作。

该问题的一种解决方案是让双通道转换器使用多点链路JESD204B接口,其中每个转换器都使用各自独立的串行链路输出。然后便可针对每个ADC使用非相干时钟,且每个串行链路

2024-01-03 06:35:04

电子发烧友网站提供《具有串行I2C接口的实时时钟1339 数据表.pdf》资料免费下载

2023-12-21 10:45:31 0

0 请问,AD9788芯片,能否两路DA输出完全独立的两路信号分别去混频,而不是分IQ输出进解调器?谢谢

2023-12-18 06:49:29

您好:

使用AD9690时,想知道数据具体是怎样映射到串行链路上的。

我打算不使用AD9690内置的DDC,直接将采样后的一路数据通过串行链路传递到FPGA;在手册中看到一幅图描述着,一个采样点的高

2023-12-12 08:22:45

请问,要搭一个传输链路,链路中的ADC和DAC的参数,比如:采样率和分辨率一定要一样吗?

中频模拟信号,先模数转换数字化进行传输,之后需要数模转换,前后的ADC和DAC采样率和位数是否要完全相等?完全符合指标的器件不太好找。

2023-12-12 06:21:04

称48位或48bit LVDS接口。

单路和双路:单路就是只有一路 R、G、B 三色和HS、VS、DE控制信号; 双路就是有两路 R、G、B 三色和HS、VS、DE控制信号。

经常碰到什么单6,双6

2023-12-11 13:21:58

假设我有4个AD5422采用菊花链方式连接,当前状态输出电流都为10mA,现在想改变第3个的电流输出为5mA,不改变其他路的输出电流值。

问题1:那前24个时钟(即操作第4个AD5422的时钟

2023-12-11 07:56:50

描述 MAX9275/MAX9279是3.12Gbps千兆位多媒体串行链路(GMSL)串行器,具有并行LVCMOS输入和CML串行输出,可编程用于50ω同轴电缆或100ω屏蔽双绞线(STP

2023-12-07 10:30:47

使用内部PLL,输入参考频率为100MHz。在采样率时钟设置为1GHz时,DAC的JESD204B链路能建立,但是当频率改为1.5GHz时,SYNC一直为低。其他相关寄存器都已经修改,serdes

2023-12-05 08:17:30

我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是[时钟周期]() 约束。

2023-12-04 15:44:02 352

352

各音频的时钟不相同,因此用4个ASRC去进行同步,而SPDIF、ADC与I2S0共用一路ASRC。用PCG产生输出给,AD/DA的主时钟,SPORT 0-1,6-7的FS,CLK。基本上设计是这样

2023-11-30 06:09:13

关于AD8221

1)热偶方式为何要用单端偏置?可否也用双端平衡偏置电阻

2)8221的差分输入信号是否必须与8221共地?还是共不共都行?

欢迎讨论

2023-11-27 07:45:59

的答案:

(1)总的建立时间就等于两级运放的建立时间之和,即90 ns + 90 ns =180 ns

(2)总的建立时间还是90 ns

(3)认为两级运放相互独立,总的建立时间等于两级运放建立时

2023-11-27 06:54:56

华创翼联HC-G30是一款使用 Wi-Fi 6 协议的便携式路由器。采用 MT7981B 主频1.3GHz 双核处理器,支持160MHz, 无线速率和信号强度都有卓越的提升。它可以满足家庭多设备连接

2023-11-23 15:38:45

。

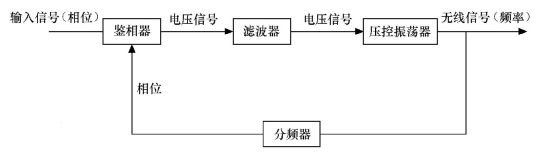

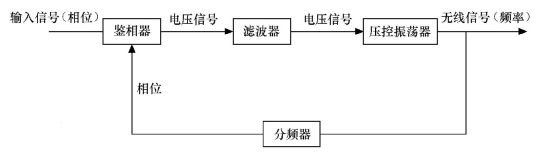

时钟输出蜂鸣器输出控制电路的框图如图13-1所示。

最大输出频率

功能引脚

可以输出两路方波CLKBUZ0与CLKBUZ1

CLKBUZ0可选为P31、 P140。

CLKBUZ1可选为P15

2023-10-25 11:20:01

C语言或Matlab如何实现FF链路调度器仿真

2023-10-18 06:12:23

仅当存在待发送数据时串行时钟波特发生器才产生对应数据位模式的时钟脉冲吗?如果缓冲区没数据,串行时钟就一直空闲吗?

2023-10-17 08:20:06

C语言或matlab如何实现ff链路调速器仿真

2023-10-17 07:34:56

STM32的独立看门狗用的时钟是内部时钟还是外部时钟呢

2023-10-15 11:58:05

1. 产品简介

USR-G808 是一款双 4G 无线工业路由器,提供了一种用户通过 WIFI 或是网口接入4G 网络的解决方案。产品采用商业级高性能嵌入式 CPU,工作频率高达 580MHz

2023-09-25 07:18:54

很多应用场合需要检测系统时钟是否在正常范围内,以保证MCU能正常工作,CLASS B功能安全实现系统时钟自检的方法是采用两个独立时钟源交叉检查来进行测量

2023-09-14 17:30:49 945

945

耗电与频率成正比最低为1.5μA。如果有32.768kHz的振荡器连接到LSE精度可达0.5% 复位和从停止/待机模式退出后MSI将作为默认的系统时钟其建立时间的最大值为2us。 低速内部振荡器

2023-09-12 08:25:02

功能

•60 GHz V波段收发器,可实现高达

480 Mbit/s

•集成全射频收发器和天线的紧凑型解决方案,在半双工模式下运行

•44 dB典型的总链路预算,高达6 cm的自由空间传播损耗

2023-09-07 06:49:02

信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间;

2023-09-04 15:16:19 391

391

应用:此示例代码使用 M030G I2C 读取 NCT7712Y 热感应器。

BSP 版本: M030G_Series_BSP_CMSIS_V3.02.000

硬件:NuMaker-M030GTD

2023-08-29 08:05:00

产品介绍PXIe7301双路万兆网卡具有局域网性能加速、网络安全、网络融合、网络虚拟化、数据中心桥接等多项功能,通讯带宽为双口10Gbps,芯片的逻辑门数量达到一千八百万,片上SRAM容量达到

2023-08-22 11:53:18

TTM Technologies 的 XMC0204P2-30G 是一款定向耦合器,频率为 2.3 至 4 GHz,耦合 30 dB,耦合变化 ±1.5 dB,频率灵敏度 ±0.25 dB,方向性

2023-08-16 09:49:04

安路CPLD可否提供内部时钟

2023-08-11 09:14:56

使用,可通过经济高效的 50Ω 单端同轴电缆或 100Ω 差分屏蔽双绞线 (STP) 电缆提供单通道或双通道高速串行流。它对 OpenLDI 输入进行串行化处理,支持

2023-08-08 14:22:50

74HCT165是符合JEDEC标准7A的高速Si栅极CMOS器件。它们与低功率肖特基TTL(LSTL)引脚兼容。

74HCT165是8位并行加载或串行移位寄存器,具有可从最后一级获得的互补串行输出

2023-08-04 17:39:53

RJK0204DPA 数据表

2023-07-14 10:20:37 0

0 HITK0204MP 数据表

2023-07-14 09:46:50 0

0 HITJ0204MP 数据表

2023-07-14 09:45:24 0

0 RQK0204TGDQA 数据表

2023-07-13 19:10:10 0

0 RQJ0204XGDQA 数据表

2023-07-13 19:07:18 0

0 MAX9209/MAX9213将21位的LVTTL/LVCMOS并行输入数据串行化为三路LVDS输出。第四路LVDS输出为并行速率时钟,为解串器提供时钟。MAX9209/MAX9213具有可编程直流

2023-07-11 10:25:35

。MAX9217与MAX9218解串器组成一个完整的数字视频串行链路。可通过阻抗受控的PCB走线或双绞线实现互连。专用数据编码降低EMI并提供DC平衡。DC平衡允许使用

2023-07-11 10:14:49

。MAX9247与MAX9248/MAX9250解串器配合使用,组成一个完整的数字视频串行链路。可通过阻抗受控的PCB走线或双绞线实现互连。专用数据编码降低EMI并提供

2023-07-11 10:08:09

MAX9257A串行器与MAX9258A解串器配对形成完整的数字视频串行链路。MAX9257A/MAX9258A具有可编程并行数据宽度、并行时钟频率范围、扩频和预加重功能。在上电时,集成控制通道会在

2023-07-11 09:24:33

MAX9257A串行器与MAX9258A解串器配对形成完整的数字视频串行链路。MAX9257A/MAX9258A具有可编程并行数据宽度、并行时钟频率范围、扩频和预加重功能。在上电时,集成

2023-07-11 09:22:05

本文主要介绍了建立时间和保持时间。

2023-06-21 14:38:26 1079

1079

建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持时间是进行时序分析的基础。

2023-06-21 10:44:01 881

881

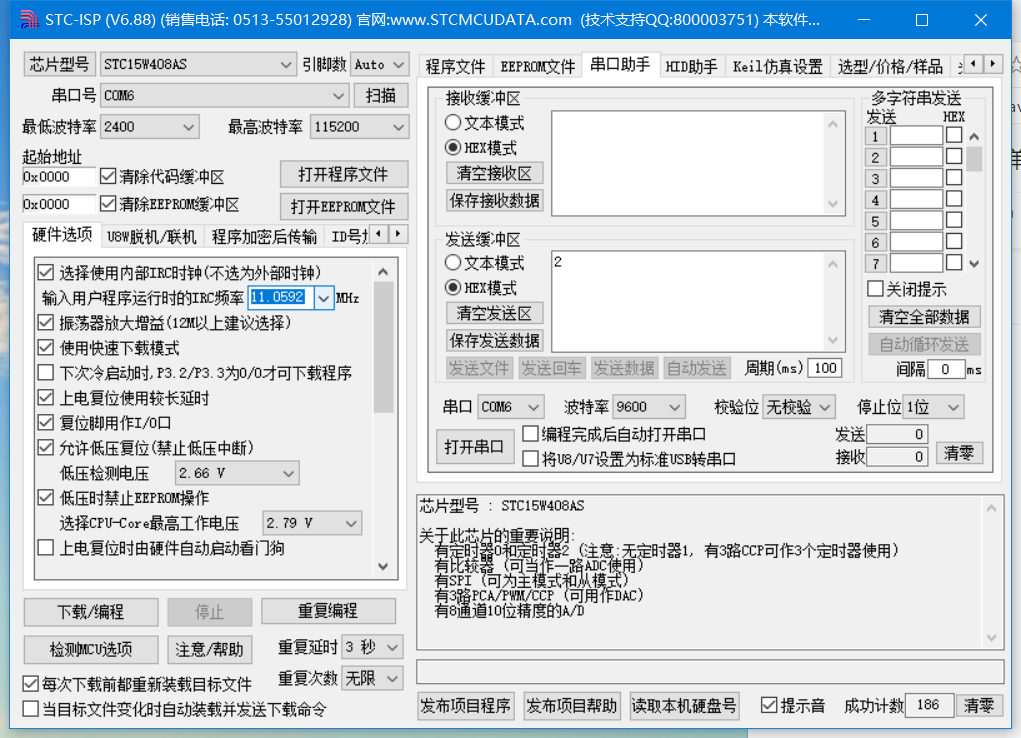

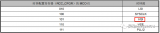

STC15W408AS单片机有两个时钟源:内部高精度R/C时钟和外部时钟(外部输入时钟或外部晶体振荡器产生的时钟)。内部高精度R/C时钟(±0.3%),±1%温漂,常温下温漂±0.6%(-20℃~+65℃)。

2023-06-15 14:45:08 1211

1211

振荡器

--时钟监测系统

--允许独立关断各外设时钟

•支持最多 39 路 I/O 接口

--所有 I/O 口支持中断功能

--所有 I/O 支持中断输入滤波功能

•五通道 DMA 控制器

2023-06-07 11:04:28

flexcan在QSPI启动模式下无法初始化OK ,但在串行启动模式下可以初始化OK;

在qspi启动模式和串行启动模式下比较flexcan init之后的所有flexcan寄存器,只有两个寄存器的位不同。

2023-06-06 07:18:53

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

。

我们希望所有这些实例都可以独立运行,因此它们都配置了时钟模块。而且它们独立运行时没有问题。但是当我们使用Bootloader来加载和运行所有这些实例时,有些功能就无法工作,甚至会出现系统复位的情况。

以上案例如何配置时钟模块,所有实例一起工作时都需要配置时钟且不冲突。

2023-05-30 08:12:04

大家好,

请帮助我了解 S32G2 是否支持双内存进行 OTA 更新。基本上在这里我们期待双分区。

2023-05-29 08:51:39

,中频频率为 DC 至 2 GHz,转换损耗为 5 dB,LO/RF 隔离度为 38 dB。标签:表面贴装,双平衡混频器。M1-0204的更多细节可以在下面看到。产品

2023-05-24 17:08:00

基站的内部,都有自己独立的时钟模块:晶振(晶体振荡器),在没有外部时钟源时,就处于自由震荡状态。

可想而知,在自由震荡状态的各个基站间的时钟没有同步,每个基站都只是一个孤岛,只能独立运行无法协同

2023-05-10 17:09:50

和8K@30fps H265/H264视频编码。

核心板

核心板+底板结构,拆卸方便,核心板引脚320PIN全部引出满足扩展需求助力产品开发。

接口丰富

双路千兆以太网、5G/4G模块、HDMI输入、HDMI输出

2023-05-09 10:31:24

采用modbus的串口链路,这3个设备公用一条链路,该如何设设置?有一个主控屏,一台pc上位机,和一个受控设备.PC远控端,屏近地控制

2023-05-05 16:17:00

200017f NbrPorts 2

启动控制器

USB XHCI 1.00

扫描总线 usb3@2f00000 设备...警告已停止端点,无论如何都在排队 URB。

意外的 XHCI 事件 TRB

2023-05-05 06:26:11

备件转生产的物资信息转换、工程文档整理等文档类工作耗时耗力,工程余料盘点难。

数字化助力工程物资供应链管理价值提升为了最大限度发挥物资供应链管理的实效,释放供应链管理价值,可借力数字化技术,强化

2023-04-25 11:28:10

IC SERDES HOTLINK 256LBGA

2023-04-06 11:31:43

IC SERDES HOTLINK 256LBGA

2023-04-06 11:31:07

KL05,30 个 K10。我们检查了 K10 和 K20 uc 它不起作用。我通过 SWD 连接器 J6 对 FRDM-KL46Z 板进行编程来检查 PE 多链路,它对板进行编程没有任何问题。我

2023-04-04 06:52:58

RJK0204DPA 数据表

2023-04-03 19:21:25 0

0 HITK0204MP 数据表

2023-04-03 18:46:08 0

0 HITJ0204MP 数据表

2023-04-03 18:44:32 0

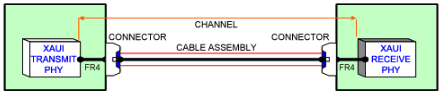

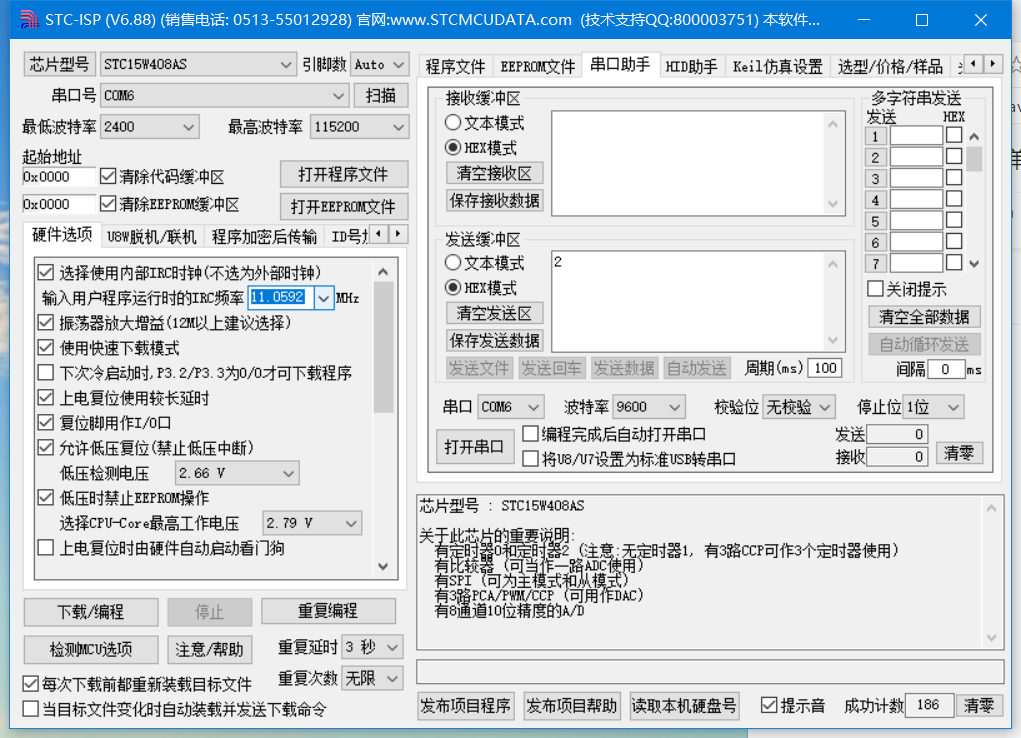

0 高速串行链路的表征取决于SI工程师发现、理解和解决严重抖动问题的能力。在本讨论中,我们假设 PHY(物理层)或 SerDes(串行器-解串器)设备的时钟和数据恢复 (CDR) 模块符合适用于该设备

2023-04-03 11:27:21 995

995

[0x0000004EB: cpsid i]。请告诉我是否需要在启动时初始化 PC、MSP 和更多寄存器,以及如果需要该怎么做。此外,为什么当我使用 PE 多链路通用探针进行调试时,它没有初始化就可以工作?

2023-03-31 06:17:11

RQK0204TGDQA 数据表

2023-03-30 19:39:38 0

0 RQJ0204XGDQA 数据表

2023-03-30 19:36:47 0

0 BL-2020RGB-TRB

2023-03-29 21:50:26

BB-2020BGR-TRB

2023-03-29 21:50:25

BL-HJC35B-TRB

2023-03-29 21:43:02

RP114K331D-TRB

2023-03-29 21:38:32

DA-15S-II

2023-03-29 17:52:56

BL-HB335B-TRB-6

2023-03-29 17:42:20

BL-HZ337A-L6-TRB

2023-03-29 17:41:56

BL-HKC36P-TRB

2023-03-29 17:35:50

几乎稍微复杂的数字设计都离不开时钟。时钟也是所有时序逻辑建立的基础。前面介绍建立时间和保持时间时也涉及过时钟偏移的概念。下面将总结下时钟的相关知识,以便更好的进行数字设计。

2023-03-28 13:56:41 978

978

和2024年,随着AI大数据领域、以及超级计算机或者超级计算单元等应用的迅猛发展,大电流和高功率密度模块、以及高能量密度的Power Block模块也将会迎来爆发式的需求增长。MPS最新推出的双路输出系列

2023-03-24 15:42:26

64 x 8,串行,I²C实时时钟

2023-03-24 14:48:57

64 x 8,串行,I²C实时时钟

2023-03-24 14:01:39

根据参考手册,NXP S32K144HAMLL 具有 3 个低功耗串行外设接口,使用 SIRC 时钟源运行。 我想知道 3 LPSPI 是否与时钟源一起独立运行。我找不到显示时钟源如何连接到所有三个 SPI 的完整总线图。如果有人能澄清这一点,那将非常有帮助。

2023-03-24 06:27:34

I2C 串行实时时钟

2023-03-23 05:01:01

电子发烧友App

电子发烧友App

评论