、DS92LV16的特性亮点 1. 高速数据处理能力 DS92LV16具备25 - 80 MHz的工作频率,能实现16:1/1:16的串行化/解串行化

2025-12-31 14:45:06 79

79 DS90CR485芯片具有高达6.384 Gbps的吞吐量,能够将24路LVCMOS/LVTTL双沿输入(每个时钟周期锁存48位数据)串行化到8路低压

2025-12-30 11:05:03 106

106 探索LM2502:MPL显示接口串行器和解串器的技术奥秘 在当今的电子设备设计中,显示接口的高效性和低功耗是至关重要的。TI的LM2502作为一种双链路显示接口SERDES(串行器/解串器),为现有

2025-12-29 17:10:24 413

413 深入解析 8P34S2106A:高性能双路 1:6 LVDS 输出扇出缓冲器 在电子设计领域,时钟和数据信号的分配至关重要,它直接影响着系统的性能和稳定性。今天,我们要深入探讨的是瑞萨

2025-12-29 16:00:02 109

109 DS90C241和DS90C124:5 - MHz至35 - MHz DC平衡24位FPD - Link II串行器和解串器深度解析 在硬件设计领域,数据传输的高效性和稳定性至关重要

2025-12-29 14:10:06 106

106 详解DS90C241与DS90C124:5 - 35MHz FPD - Link II 串行器与解串器芯片组 作为电子工程师,在日常设计中我们常常会面临数据传输的挑战,而寻找合适的解决方案至关重要

2025-12-29 14:05:08 102

102 深入解析LMH0202:双路SMPTE 292M/259M串行数字电缆驱动器 在当今的高速数字视频和数据传输领域,对高性能电缆驱动器的需求日益增长。TI的LMH0202双路SMPTE 292M

2025-12-27 16:35:09 969

969 一下德州仪器(TI)的DS90C241和DS90C124芯片组,这是一款适用于5 - 35MHz时钟频率的DC平衡24位FPD - Link II串行器与解串器,在汽车显示和远程摄像等应用中具有出色

2025-12-27 09:55:02 495

495 芯片组由DS90UR241串行器和DS90UR124解串器组成,能够将24位并行总线转换为带有嵌入式时钟信息的全透明数据/控制FPD - Link II LVDS串行流。这

2025-12-27 09:45:05 498

498 深入解析DS90URxxx - Q1:高效FPD - Link II串行解串器芯片组 在电子设计领域,数据传输的高效性和稳定性一直是工程师们关注的焦点。DS90URxxx - Q1 5MHz 至

2025-12-26 09:25:09 273

273

–内置32KHz RC振荡器

–内置10KHz RC振荡器

–内置150KHz RC振荡器

–时钟监测系统

–允许独立关断各外设时钟

• 支持39路I/O接口

– 所有I/O口支持

2025-12-26 06:51:13

探索DS90C241和DS90C124:5 - MHz至35 - MHz DC平衡24位FPD - Link II串行器和解串器 一、引言 在电子设计领域,数据的高效、可靠传输一直是工程师们关注

2025-12-25 17:15:13 405

405 DS92LV241x:5 - 50 MHz 24 位通道链路 II 串行器和解串器的深度解析 在电子设计领域,数据的高效、稳定传输至关重要。DS92LV2411(串行器)和 DS92LV2412(解

2025-12-25 14:30:09 108

108 SN65LVCP15:高速串行链路的理想选择 在电子设计领域,高速数据传输的需求日益增长,对于能够可靠处理高速串行链路的器件需求也愈发迫切。今天我们要探讨的是德州仪器(TI)推出

2025-12-25 14:30:03 107

107 高速串行链路的理想之选:DS100BR410低功耗四通道中继器 在高速串行链路设计领域,工程师们总是在寻找能够兼顾高性能与低功耗的理想解决方案。TI的DS100BR410低功耗四通道中继器,就是这样

2025-12-24 16:40:12 144

144 )的 TLK10081 多速率链路聚合器,看看它在高速双向点对点数据传输系统中是如何发挥作用的。 文件下载: tlk10081.pdf 一、TLK10081 概述 TLK10081 是一款专为高速双向点对点数据传输系统设计的多速率链路聚合器。它的主要功能是将 1 到 8 条独立的低速千兆串行线路自动进

2025-12-23 10:20:03 154

154 深入解析TLK10022:高速串行链路聚合器的技术奥秘 在高速数据传输的领域中,链路聚合技术对于提升数据吞吐量和优化物理链路使用至关重要。TI公司的TLK10022作为一款双通道多速率串行链路聚合器

2025-12-23 10:10:02 135

135 LMH1226低功耗双路输出12G超高清时钟恢复器详解 在当今的超高清视频领域,时钟恢复器扮演着至关重要的角色,它能够确保信号的稳定传输和高质量处理。LMH1226作为一款低功耗双路输出12G超高清时钟

2025-12-19 14:45:06 172

172 带集成时钟恢复器的LMH1228 12G UHD - SDI双路输出电缆驱动器深度解析 在当今超高清视频飞速发展的时代,对于高性能视频传输接口的需求也日益增长。LMH1228作为一款带集成时钟恢复器

2025-12-18 18:00:13 1128

1128 探索LMH1208超高清UHD - SDI双路输出电缆驱动器的奥秘 在超高清视频飞速发展的今天,对于能够支持高速、高质量视频传输的硬件需求也日益增长。LMH1208作为一款12G UHD - SDI

2025-12-18 18:00:06 1060

1060 汽车电子新宠:TLIN1022A - Q1双路LIN收发器深度剖析 引言 在汽车电子领域,随着车辆智能化和电动化的发展,对可靠、高效的通信系统需求日益增长。本地互连网络(LIN)作为一种低成本、低速

2025-12-17 10:25:09 195

195 使用,能通过低成本的50Ω同轴电缆或STP电缆提供高速串行化接口。这款芯片符合D - PHY v1.2标准,可对MIPI DSI输入进行串行化处理,支持包

2025-12-16 14:20:02 197

197 串行时钟发生器用来产生 I2C 通信的波特率时钟 SCL。串行时钟发生器采用 PCLK 作为输入时钟,通过 1 个 8bit的计数器计数,输出所需波特率的 I2C 时钟信号。

SCL 时钟频率计

2025-12-08 08:16:31

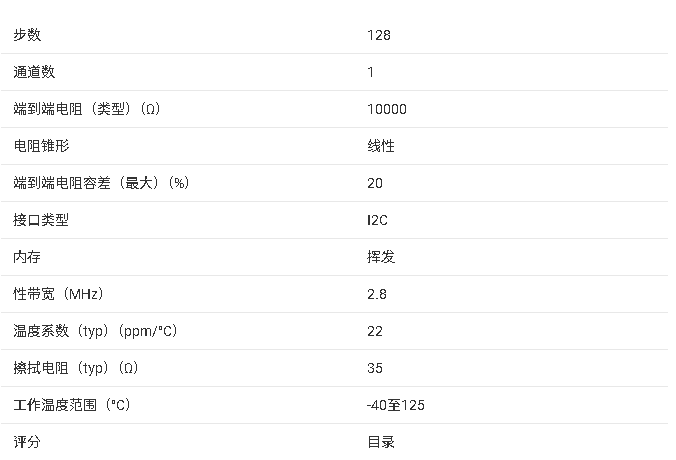

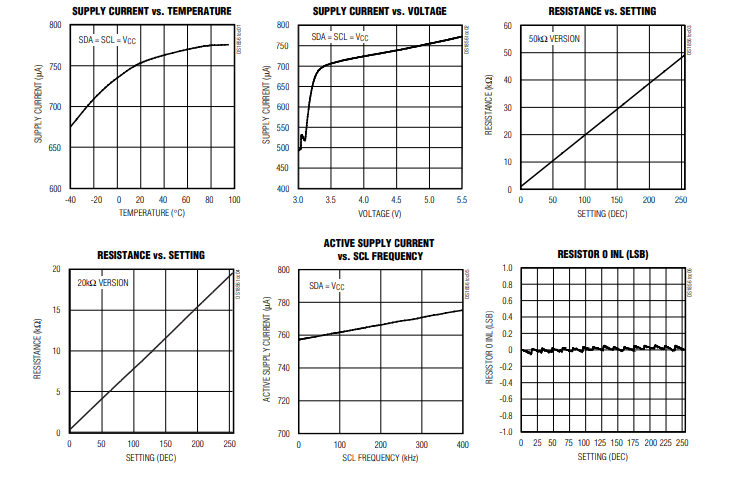

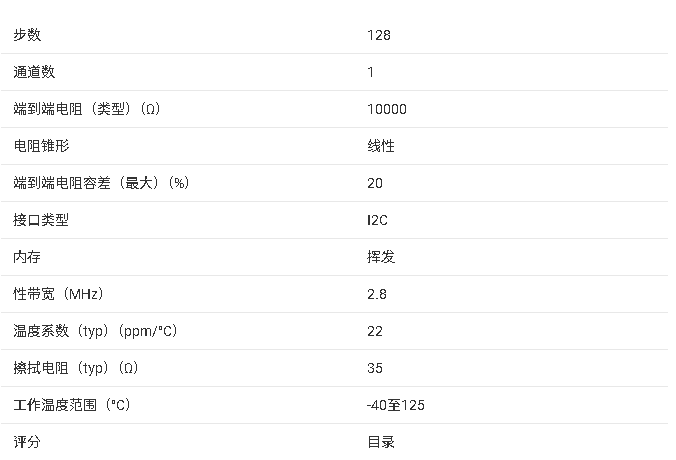

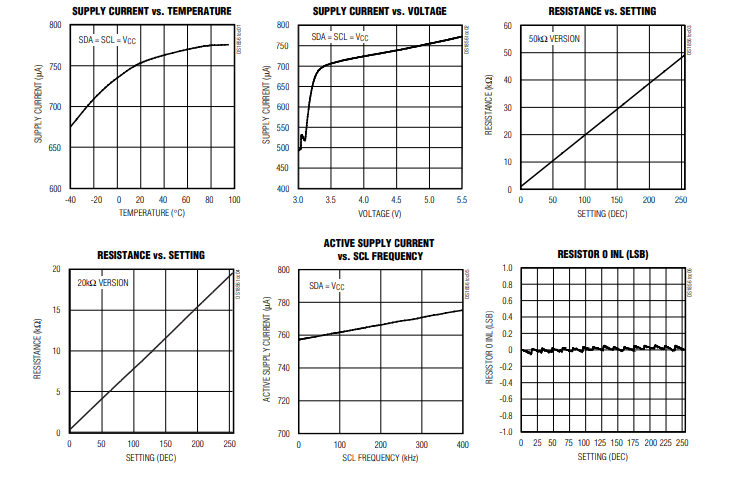

TPL0401x-10 设备是一款单通道线性锥形数字电位器,拥有 128 个擦拭位置。TPL0401x-10 的低端位于内部并连接到 GND。滑动器的位置可以通过 I 键进行调节^2^C接口

2025-11-18 14:09:36 439

439

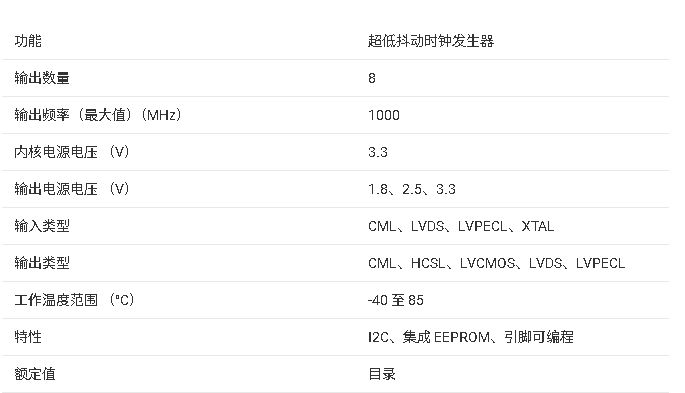

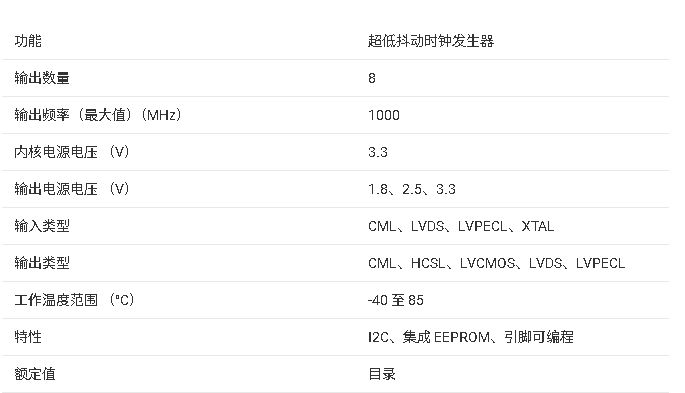

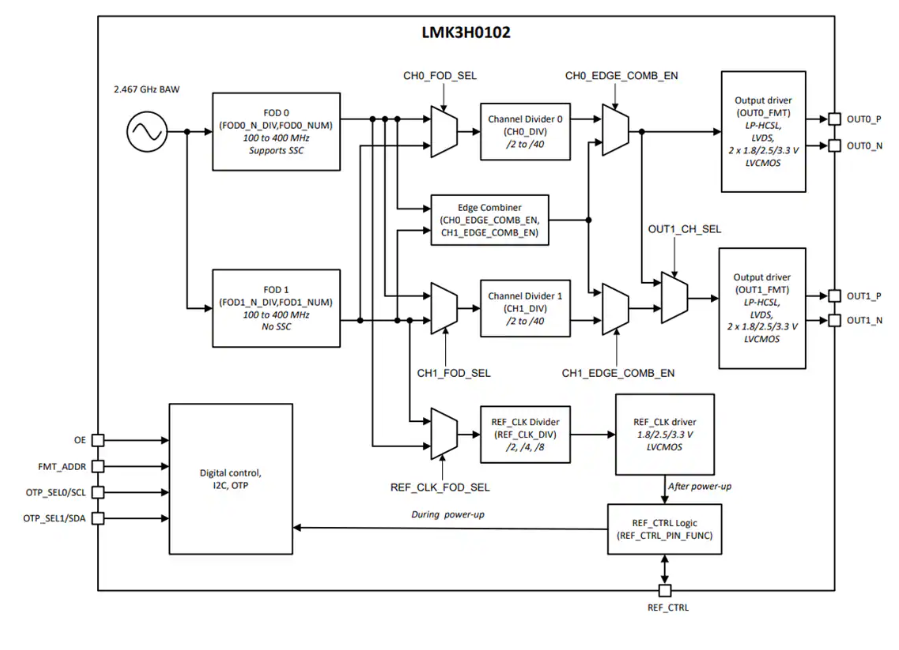

即可满足 PCIe Gen1 到 Gen7 的抖动规范,适用于数据中心、服务器、存储系统及工业高速链路的主时钟分配。核心特性BAW 谐振器技术集成体声波(BAW)谐振器,无需外部晶体或振荡器,简化设计并

2025-11-11 09:10:42

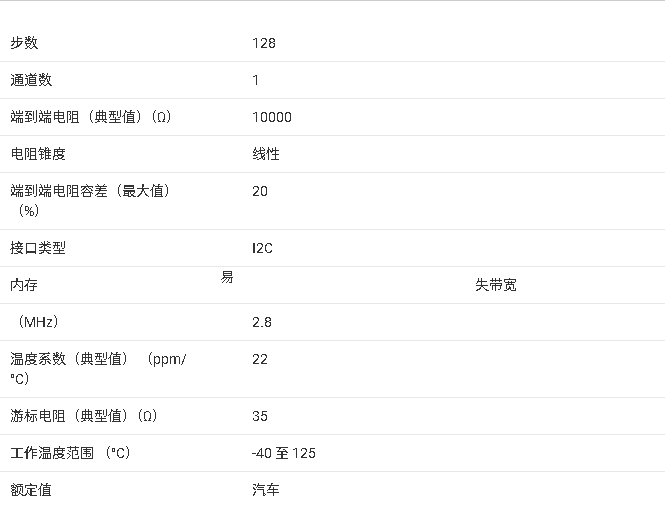

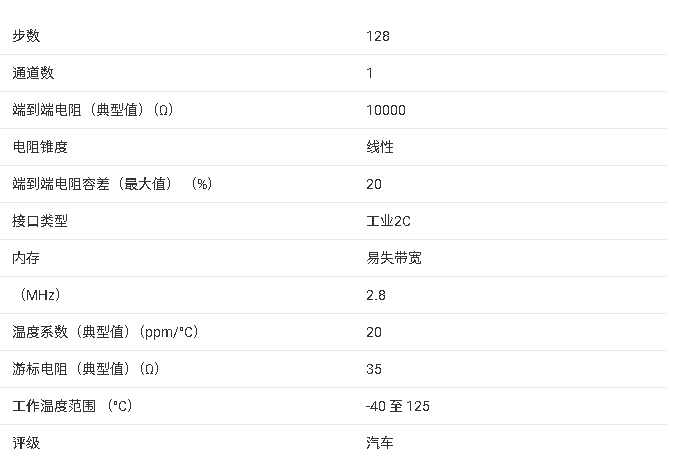

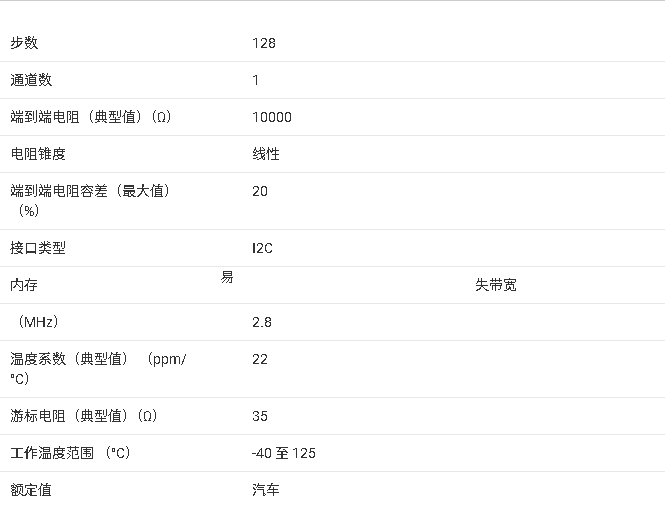

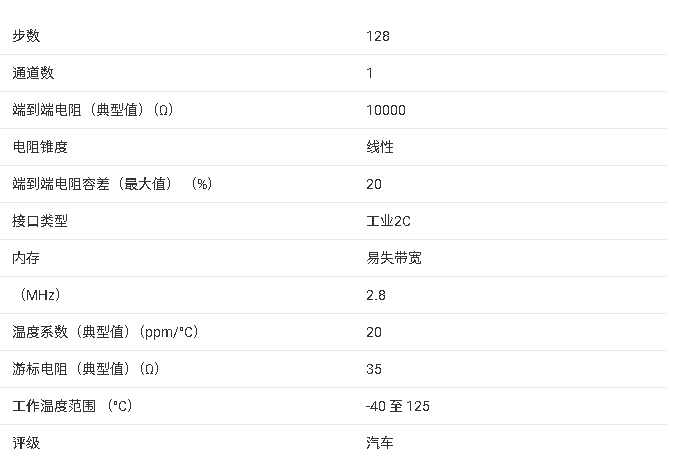

TPL0401x-10-Q1 器件是一款单通道线性锥度数字电位器,具有 128 个雨刮器位置。TPL0401x-10-Q1 具有低端子内部并连接到 GND。这 雨刮器的位置可以使用 I 进行调整^2

2025-11-10 11:18:03 529

529

TPL0401x-10-Q1 器件是一款单通道线性锥度数字电位器,具有 128 个雨刮器位置。TPL0401x-10-Q1 具有低端子内部并连接到 GND。这 雨刮器的位置可以使用 I 进行调整^2

2025-11-10 11:09:11 491

491

判断电能质量在线监测装置的备用链路是否正常,核心是通过 状态可视化查看、信号与参数检测、功能模拟测试、数据连续性验证 四个维度,结合设备自带工具和外部辅助手段,全面验证 “链路就绪、切换有效、数据不

2025-11-06 16:34:46 1127

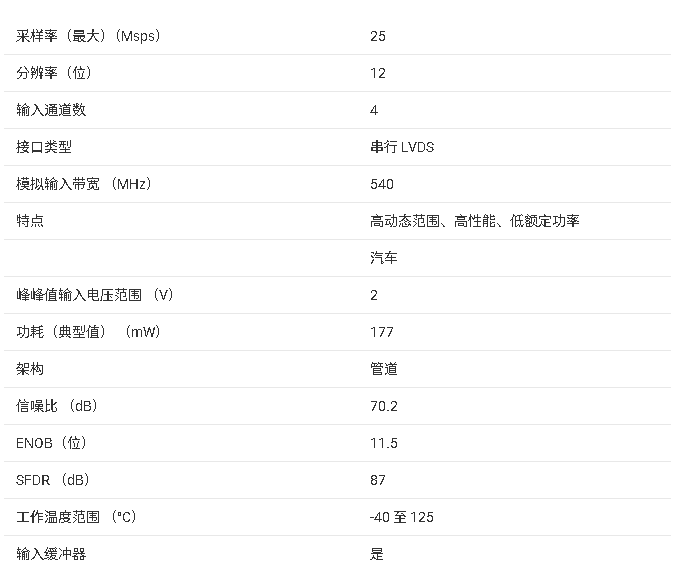

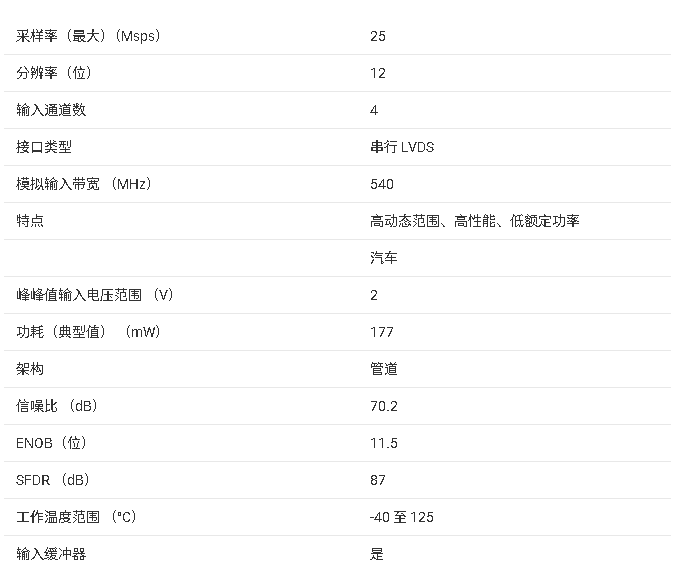

1127 每个 ADC 数据都经过两个 LVDS 对串行化和输出。内部锁相环 (PLL) 将输入的 ADC 采样时钟相乘,以得出用于序列化每个通道的 12 位输出数据的位时钟。除了串行数据流外,帧和位时钟也作为LVDS输出传输。

2025-11-03 15:33:50 453

453

: 一、PTP 同步(IEEE 1588)常见异常类型(适配 A 级装置) PTP 同步依赖高精度链路与主从时钟协同,异常多源于 “链路中断、主时钟失效或参数不匹配”,典型类型如下: 1. 链路类异常:物理连接中断或信号劣化 表现 : 装置显示 “PTP 链路断连”“报文

2025-10-22 14:15:36 330

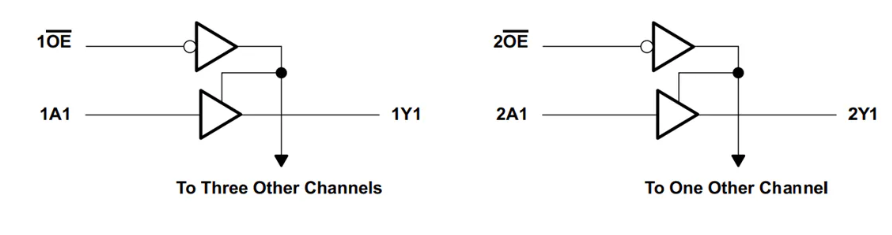

330 CDC208包含双时钟驱动器电路,可将一个输入信号扇出到四个输出,时钟分配的偏斜最小(见图2)。该器件还为每个电路提供两个输出使能(OE1\和OE2\)输入,可以强制将输出禁用到高阻抗状态或高或低逻辑电平,而与相应A输入上的信号无关。

2025-09-24 10:55:36 631

631

LMH2180是一款高速双时钟缓冲器,专为便携式通信和 需要多个精确多时钟系统的应用。该LMH2180集成了两个 75 MHz 低电平 带有独立关断引脚的噪声缓冲器集成到小型封装中。LMH2180确保一流的 通过消除串扰,在基带和振荡器信号路径之间进行系统作 在多个时钟信号之间。

2025-09-18 14:35:58 580

580

多个时钟,可降低BOM成本和板面积,并通过替代多个振荡器和时钟分配器件来提高可靠性。超低抖动可降低高速串行链路中的误码率 (BER)。

2025-09-14 09:37:32 886

886

位串行接口和数字设备生成多个时钟,从而降低BOM成本和电路板面积,并通过替代多个振荡器和时钟分配设备来提高可靠性。超低抖动可降低高速串行链路中的误码率 (BER)。

2025-09-13 17:35:11 1192

1192

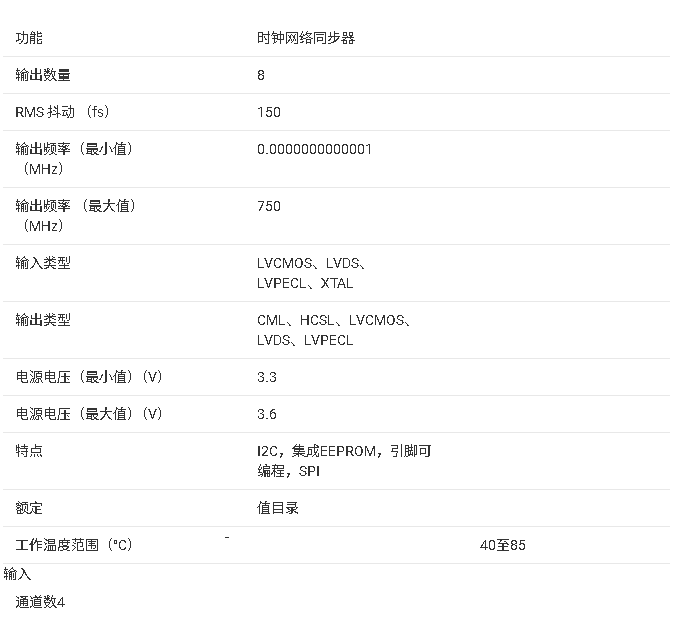

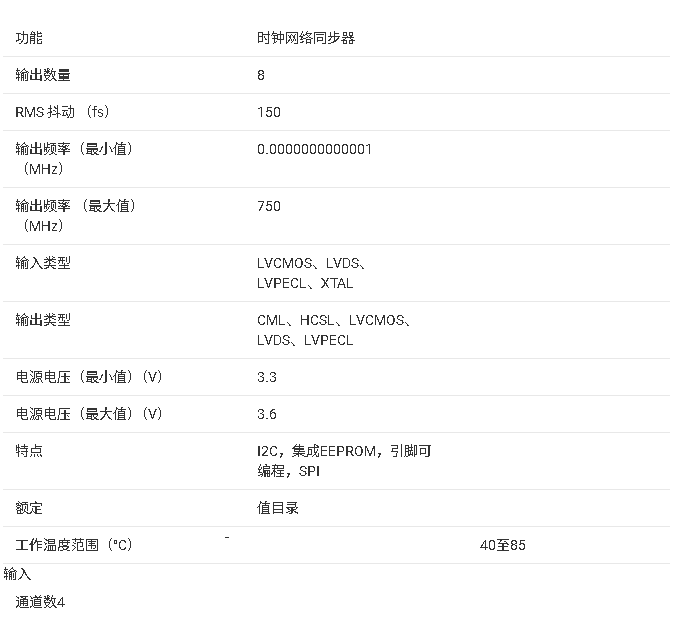

该LMK05028是一款高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和良好的无中断开关性能,以满足通信基础设施和工业应用的严格时序要求。该器件的低抖动和高PSNR降低了高速串行链

2025-09-12 14:18:25 859

859

该LMK05318是一款高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和卓越的无中断开关性能,以满足通信基础设施和工业应用的严格时序要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可降低高速串行链路中的误码率 (BER)。

2025-09-12 13:49:59 687

687

链路初始化和同步。SYNC 是异步信号(由发射端或接收端触发),用于通知接收端/发射端开始链路初始化流程(如建立时钟同步、对齐数据帧)。

•SYNC 触发后,链路进入“已同步”状态,但后续运行中若时钟

2025-09-05 21:18:18

对两个独立通道的精确控制。今天,由我来为大家揭秘一款极具创新性的调光解决方案 ——FP7195双路调光。双路调光的主要优势体现在三个方面:① 设计灵活性:可独立控制两

2025-08-27 10:35:47

里,参考时钟不只是“配件”。它直接写进 EVM、CFO 和频谱裙摆(ACLR/SEM)的预算表。本帖用「工程师视角」把 相噪/抖动、温度频稳(ppm/ppb)、场景化选型 和 PCB/供电/屏蔽 逐条

2025-08-25 14:25:16

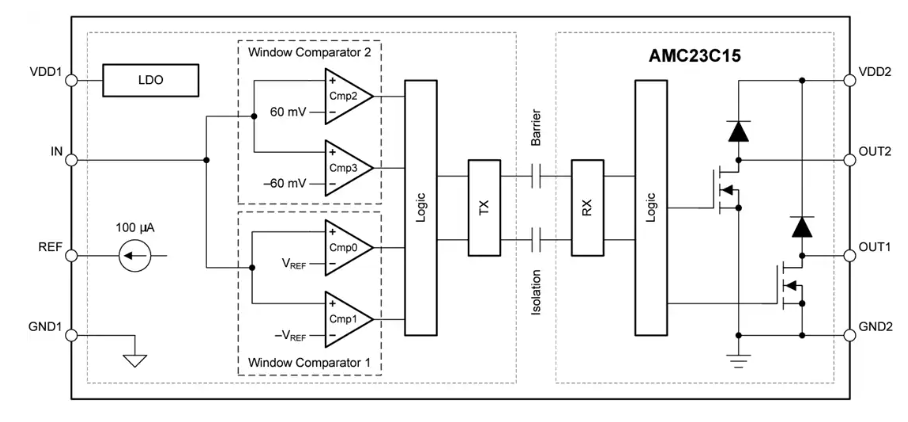

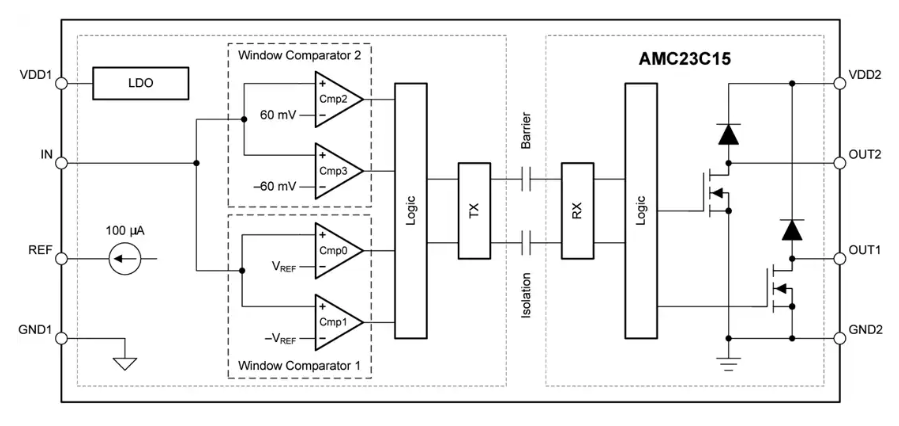

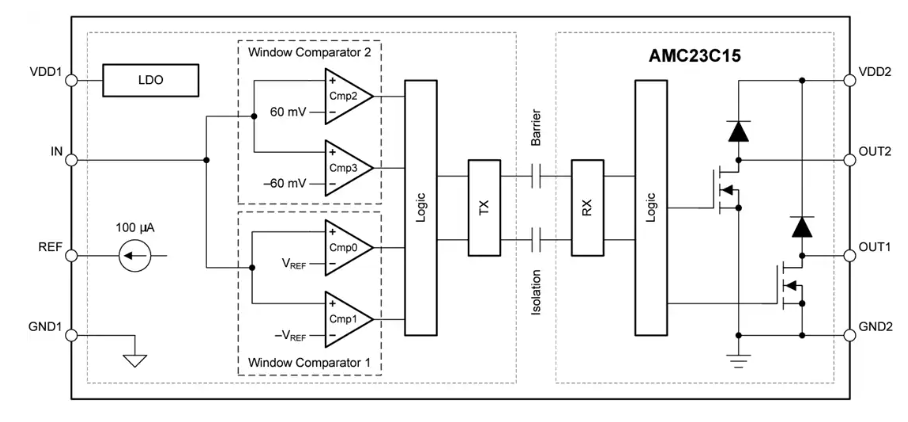

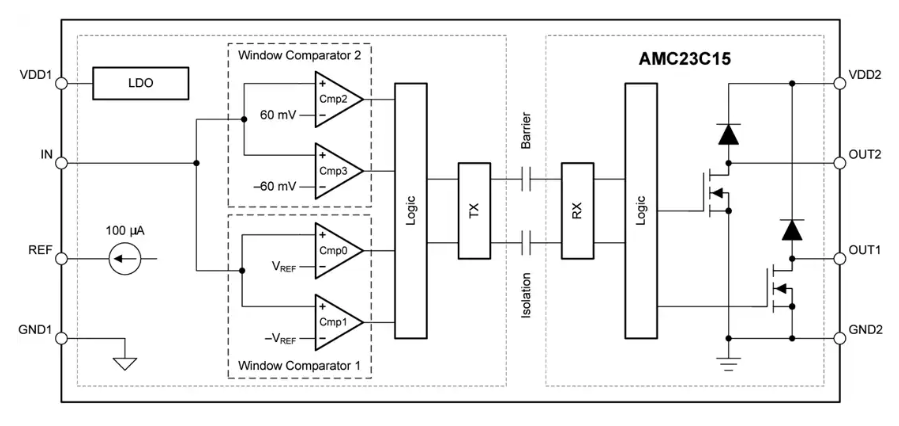

Texas Instruments AMC23C15/AMC23C15-Q1隔离式窗口比较器是一款响应时间较短的双路隔离式窗口比较器。开漏输出与输入电路由高度抗电磁干扰性的隔离栅隔开。该隔离栅经认证

2025-08-25 11:20:25 723

723

Texas Instruments AMC23C15/AMC23C15-Q1隔离式窗口比较器是一款响应时间较短的双路隔离式窗口比较器。开漏输出与输入电路由高度抗电磁干扰性的隔离栅隔开。该隔离栅经认证

2025-08-22 16:07:23 760

760

在工业自动化与智能化浪潮中,热成像技术与机器人云台正成为推动行业变革的核心力量。前者以非接触式测温能力破解复杂场景监测难题,后者通过多自由度运动控制实现全方位信息采集。当KC-2R06U-15热

2025-08-22 10:15:01 624

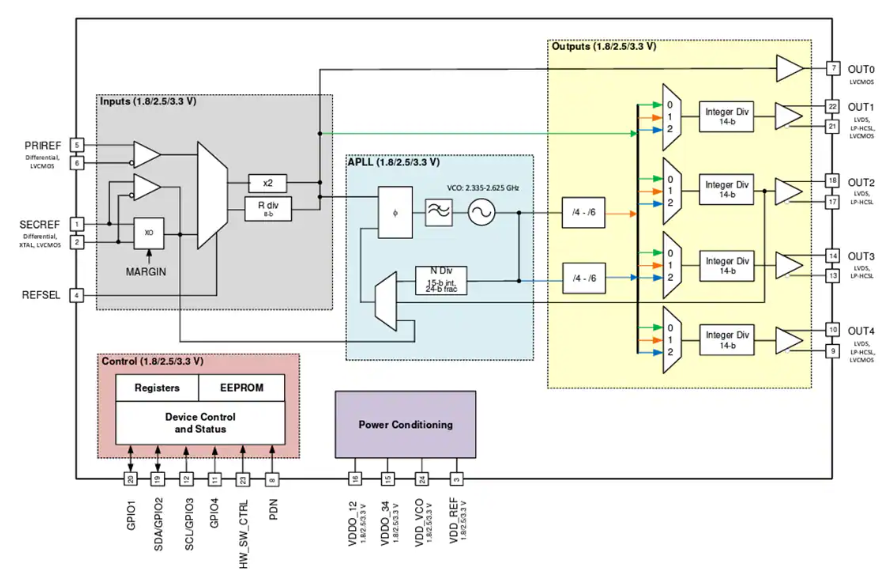

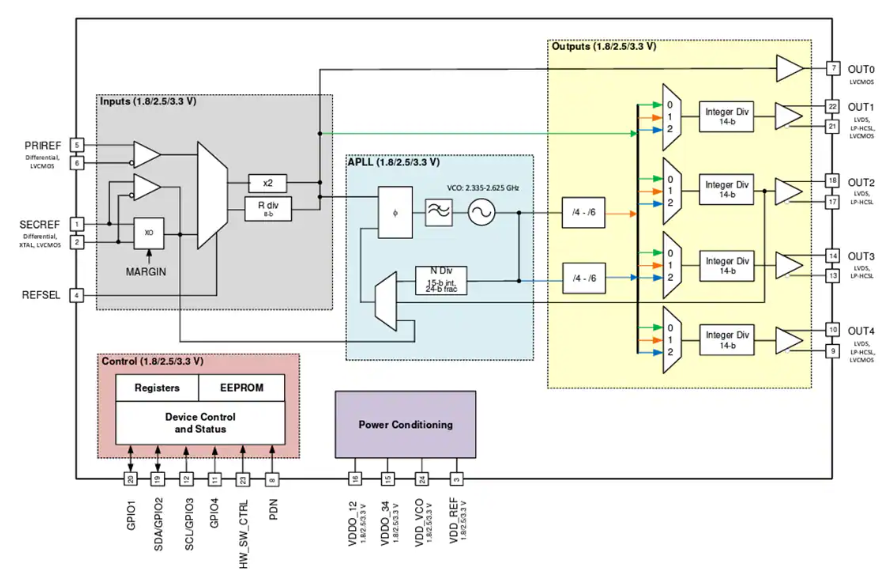

624 Texas Instruments CDCE6214Q1TM超低功耗时钟发生器是是一款适合汽车应用的4通道、中级抖动时钟发生器,可生成五个独立时钟输出。这些输出在各种驱动器模式之间可选。输入源可以

2025-08-18 14:12:05 684

684

电子发烧友网为你提供()2.4 A / 2 A 双路独立闪光灯 LED 驱动器,带 TrueFlash™相关产品参数、数据手册,更有2.4 A / 2 A 双路独立闪光灯 LED 驱动器,带

2025-07-30 18:30:00

单模双芯光纤只接1芯可以使用,但需根据具体应用场景和需求评估其适用性。以下是详细分析: 一、单模双芯光纤的结构特点 单模双芯光纤(如G.652D双芯光纤)是在同一根光纤包层内集成两根独立单模纤芯

2025-07-28 10:03:18 2177

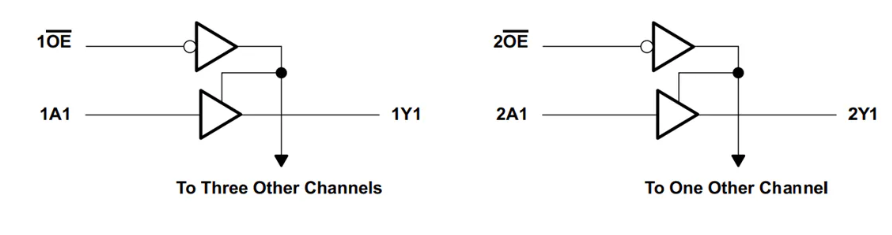

2177 供真实输出。该器件是一款双4路和2路缓冲器/驱动器,具有低电平有效输出使能输入。Texas Instruments SN74AHCT367的闩锁性能超过100mA,符合JESD 78的II类标准。

2025-07-14 09:56:27 527

527

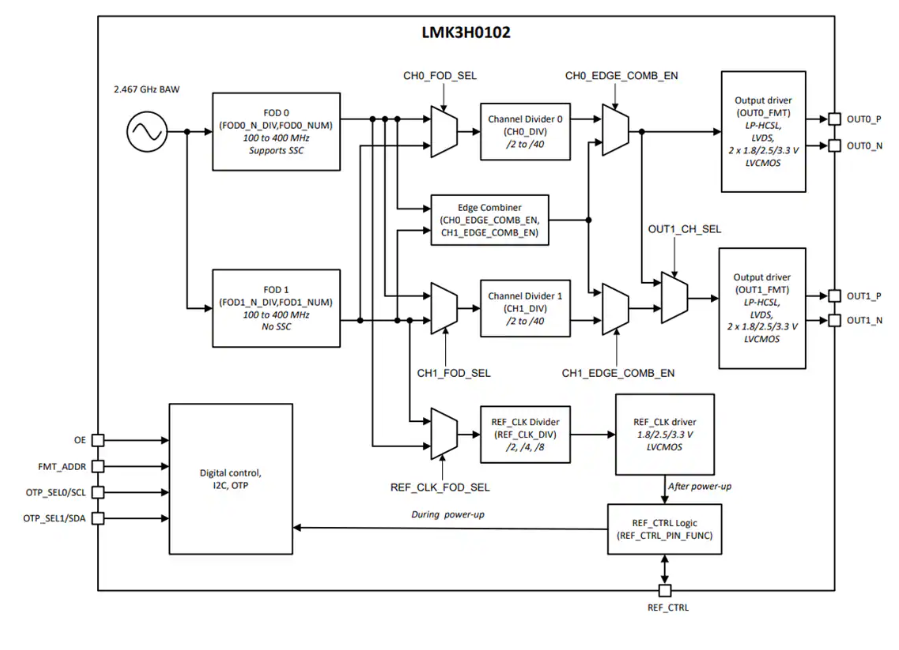

Texas Instruments LMK3H0102无基准时钟发生器是符合PCIe Gen 1至Gen 6标准的双路输出无基准时钟发生器,支持扩频时钟 (SSC)。它们基于TI专有的体声波

2025-07-08 11:12:19 685

685

电子发烧友网为你提供()SkyOne® 汽车多模多频段前端模块,用于 4G LTE 和 4G LTE-A(下行链路载波聚合 (CA) 应用)相关产品参数、数据手册,更有SkyOne® 汽车多模多频段

2025-07-01 18:31:30

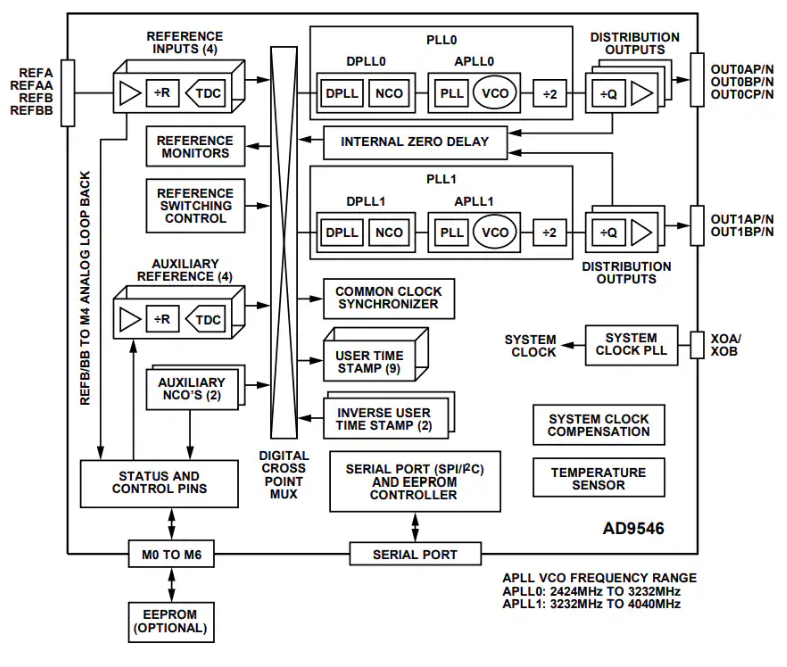

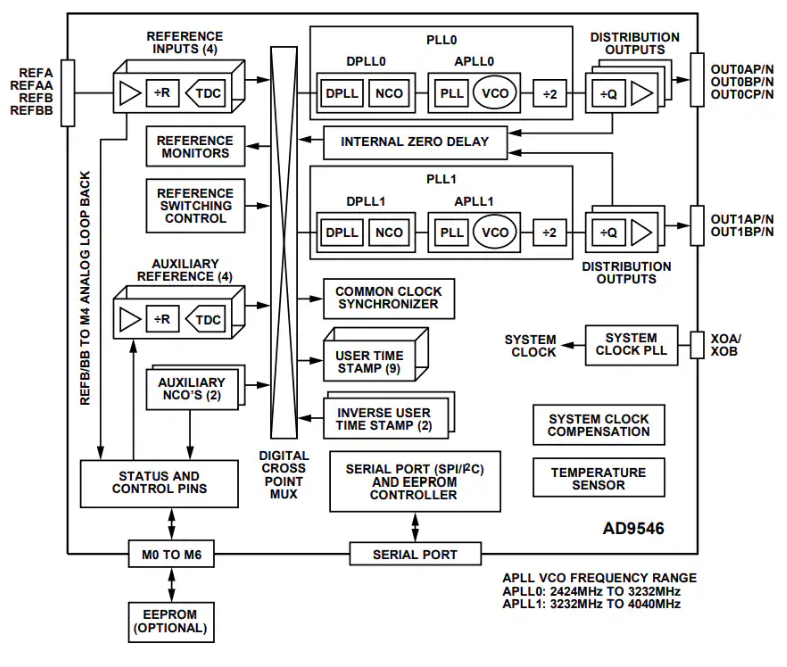

Analog Devices Inc. AD9546双通道DPLL数字化时钟同步器结合了数字化时钟技术,可在系统中高效传输和分配时钟信号。AD9546上的数字化时钟支持设计具有良好控制相位(时间

2025-07-01 09:53:02 590

590

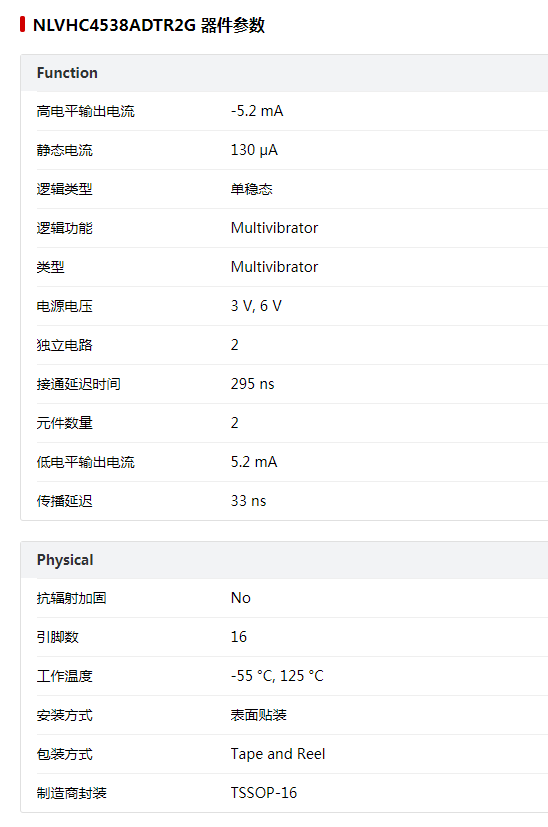

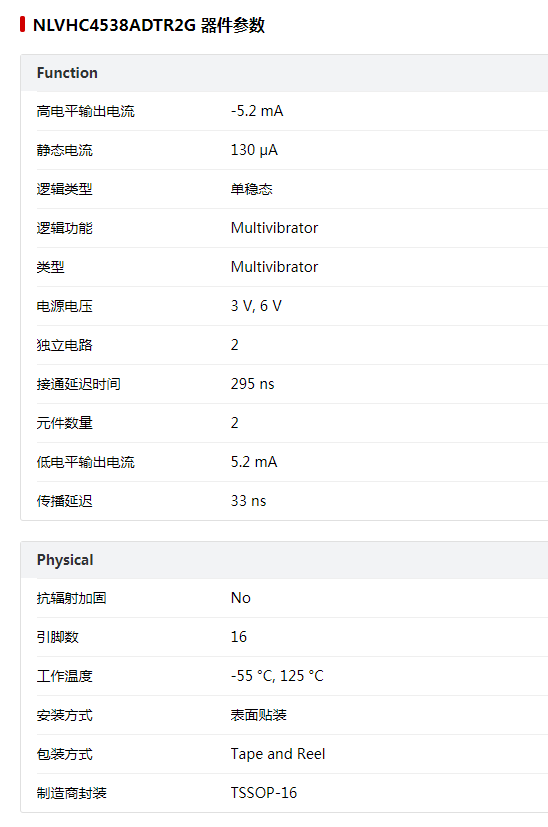

ON Semiconductor 的NLVHC4538ADTR2G双路精密单稳态多谐振荡器的参数特性与EDA模型 数据手册等资料。

2025-06-17 16:46:50 1111

1111

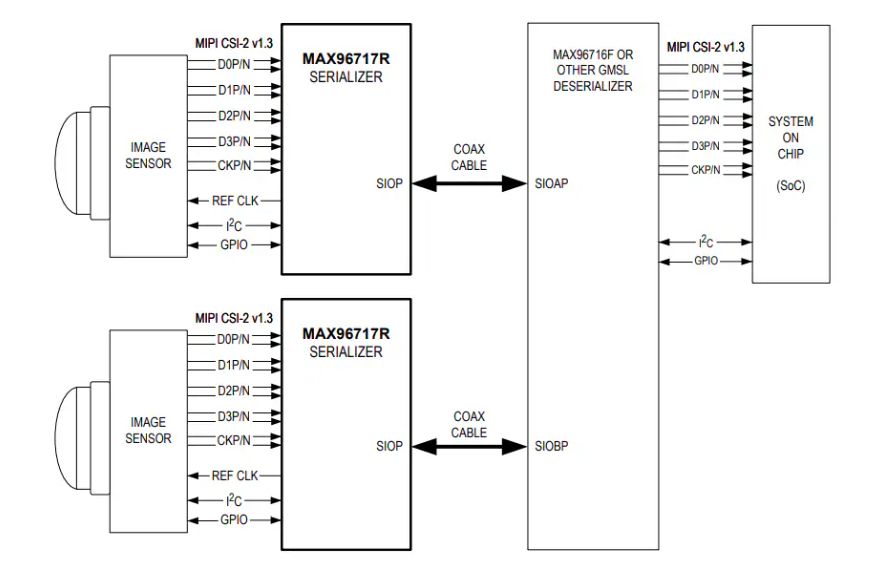

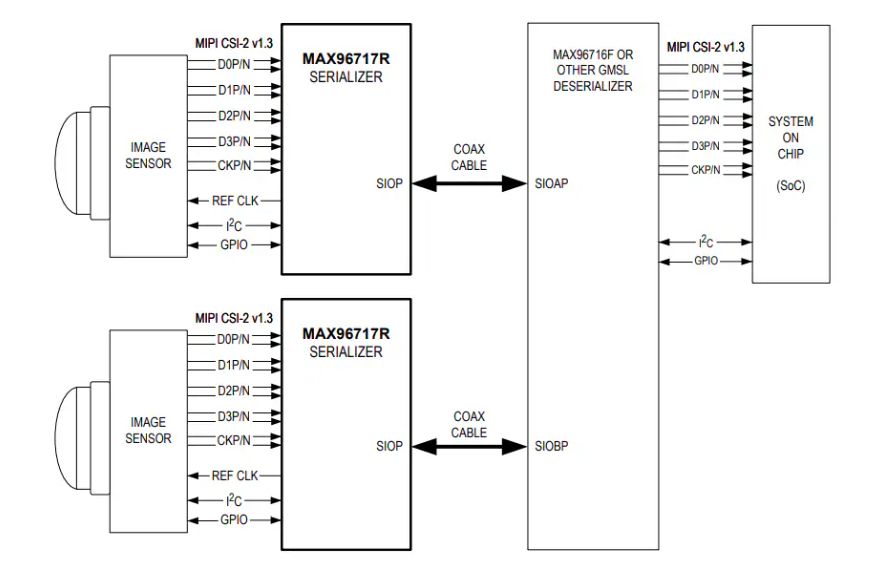

Analog Devices MAX96717 CSI-2转GMSL™2串行器接受4路MIPI CSI-2接口上的视频,然后在GMSL2串行链路收发器上输出,通过同轴电缆传输。同时,该器件通过同一

2025-06-17 14:02:52 1007

1007

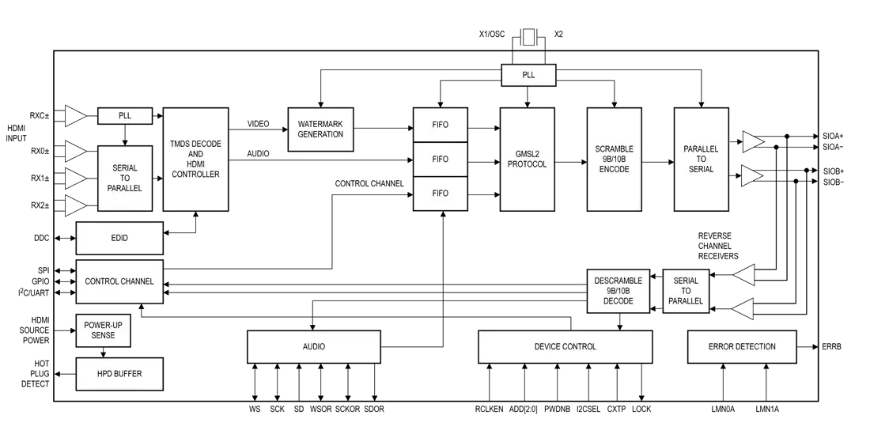

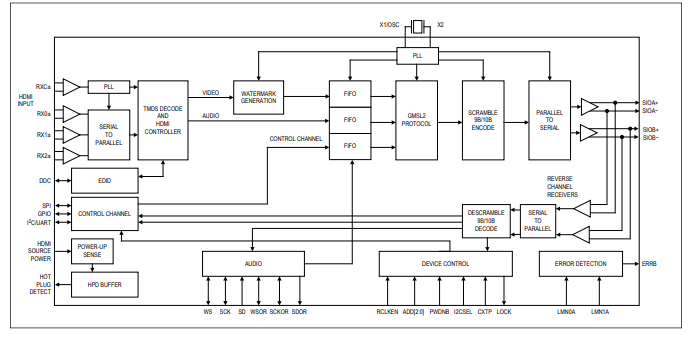

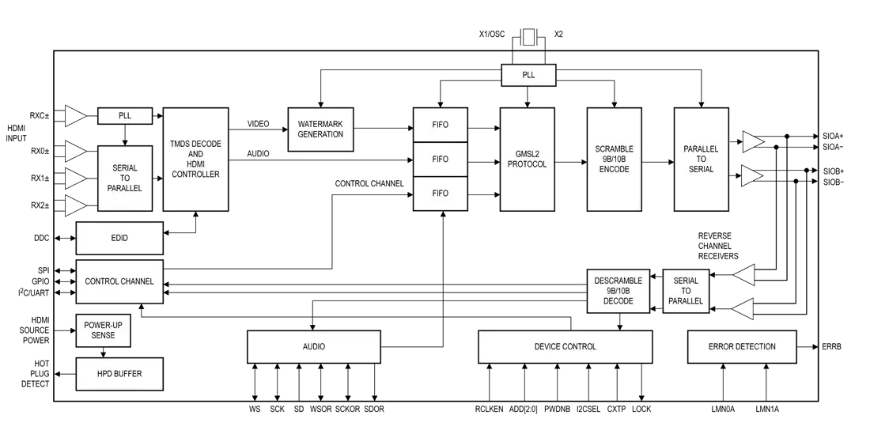

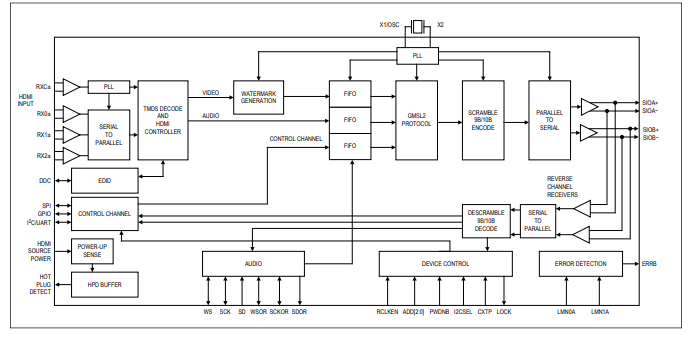

Analog Devices/Maxim Integrated MAX96751 GMSL2串行器(带HDMI 2.0输入)可将HDMI^®^ 转换为单或双GMSL™串行协议。这些器件还可发送和接收

2025-06-06 13:51:22 1009

1009

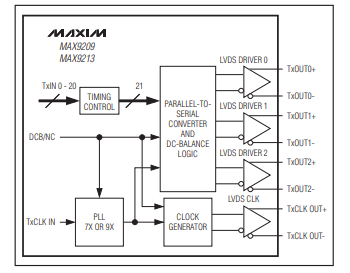

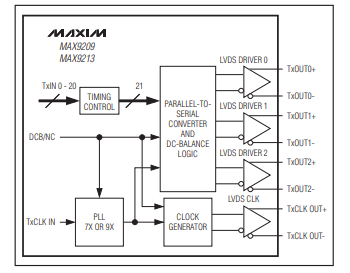

MAX9209/MAX9213将21位的LVTTL/LVCMOS并行输入数据串行化为三路LVDS输出。第四路LVDS输出为并行速率时钟,为解串器提供时钟。

MAX9209/MAX9213具有

2025-05-28 18:14:27 754

754

MAX9259/MAX9260芯片组采用Maxim吉比特多媒体串行链路(GMSL)技术。MAX9259串行器与MAX9260解串器配合使用,构成完整的数字串行链路,实现高速视频、音频和控制数据的传输。

2025-05-28 16:57:20 853

853

MAX9249串行器带有LVDS系统接口,采用Maxim吉比特多媒体串行链路(GMSL)技术。MAX9249串行器与GMSL解串器配合使用,构成完整的数字串行链路,实现高速视频、音频和控制数据的传输。

2025-05-28 16:43:37 881

881

MAX9268解串器采用Maxim吉比特多媒体串行链路(GMSL)技术,具有LVDS系统接口,可有效减少引脚数、缩小封装面积,器件可以与任意一款GMSL串行器配合使用,构成完整的数字串行链路,实现高速视频、音频和双向控制数据的传输。

2025-05-28 16:38:08 904

904

MAX9265吉比特多媒体串行链路(GMSL)串行器具有LVDS系统接口和宽带数字内容保护(HDCP)加密,用于DVD和Blu-ray™视频及音频数据的内容保护。串行器可配合任何HDCP GMSL解

2025-05-28 16:12:08 790

790

MAX9266多媒体串行链路(GMSL)解串器带有LVDS系统接口和宽带数字内容保护(HDCP)加密,用于DVD和Blu-ray™视频及音频数据保护。该款解串器配合任何HDCP-GMSL串行器,构成数字串行

2025-05-28 16:05:12 1078

1078

MAX9257A串行器与MAX9258A解串器配对形成完整的数字视频串行链路。MAX9257A/MAX9258A具有可编程并行数据宽度、并行时钟频率范围、扩频和预加重功能。在上电时,集成控制通道会在

2025-05-28 15:45:44 764

764

MAX9271结构紧凑的串行器用于驱动50Ω同轴或100Ω屏蔽双绞线(STP)电缆。器件与MAX9272解串器配对使用。

并行输入可设置为单路或双路输入。采用双路输入时,在串行转换之前将典型

2025-05-28 15:38:02 776

776

MAX9271结构紧凑的串行器用于驱动50Ω同轴或100Ω屏蔽双绞线(STP)电缆。器件与MAX9272解串器配对使用。

并行输入可设置为单路或双路输入。采用双路输入时,在串行转换之前将典型

2025-05-28 15:32:17 780

780

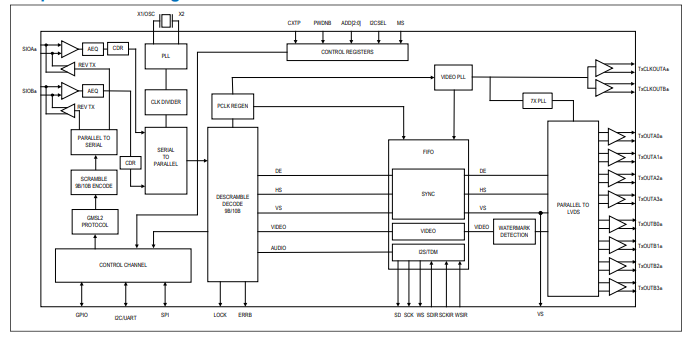

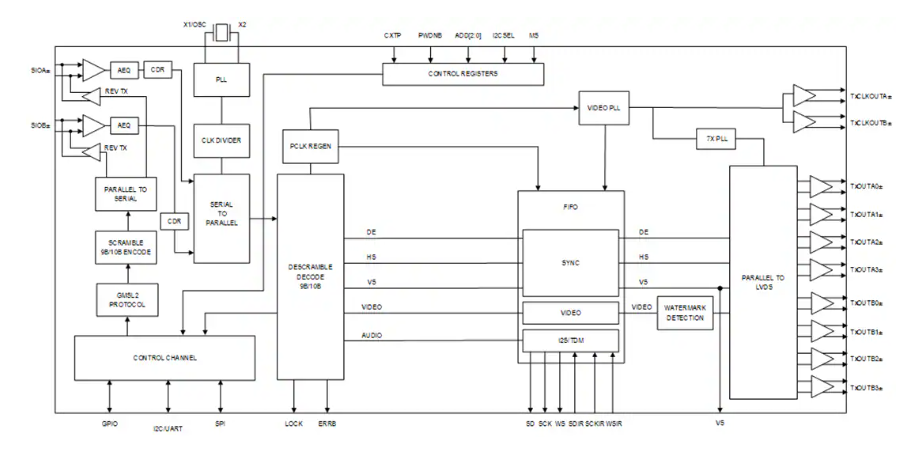

MAX96751 串行器将 HDMI转换为单或双 GMSL™ 串行协议。它还发送和接收侧信道和外设控制数据,实现全双工、单线、视频和双向数据传输。每个 GMSL2 链路以正向 3Gbps 或

2025-05-27 14:23:23 1666

1666

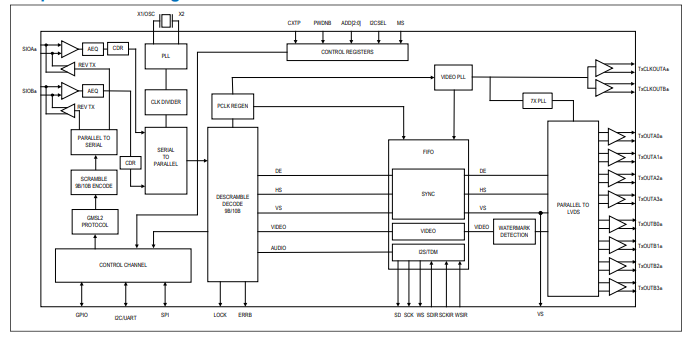

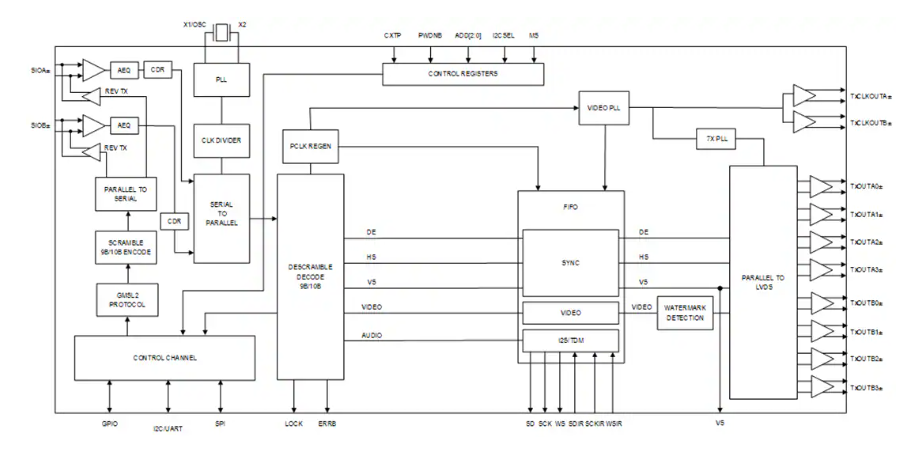

MAX96752解串器将单链路或双链路 GMSL™ 串行输入转换为单链路或双 OLDI。它们还发送和接收侧信道和外设控制数据,实现视频和双向数据的全双工、单线传输。

OLDI 输出可配置为单

2025-05-27 14:18:33 1625

1625

Analog Devices/Maxim Integrated MAX96752 GMSL2解串器(带双LVDS(OLDI)输出)可将单链或双链路GMSL™ 串行输入转换为单路或双路OLDI。这些

2025-05-23 13:56:47 1359

1359

MAX9263/MAX9264芯片组将Maxim的吉比特多媒体串行链路(GMSL)技术扩展到支持宽带数字内容保护(HDCP)加密,用于DVD和Blu-ray™视频及音频数据保护。MAX9263串行器

2025-05-22 09:47:04 950

950

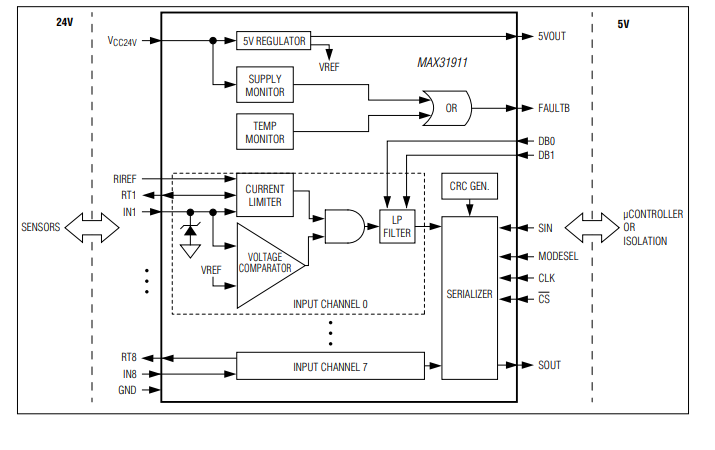

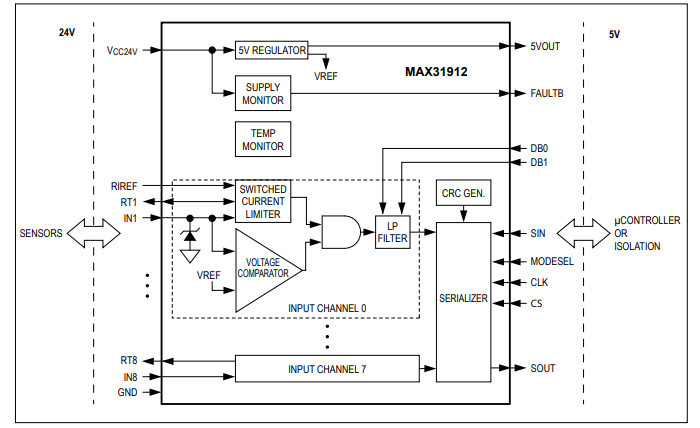

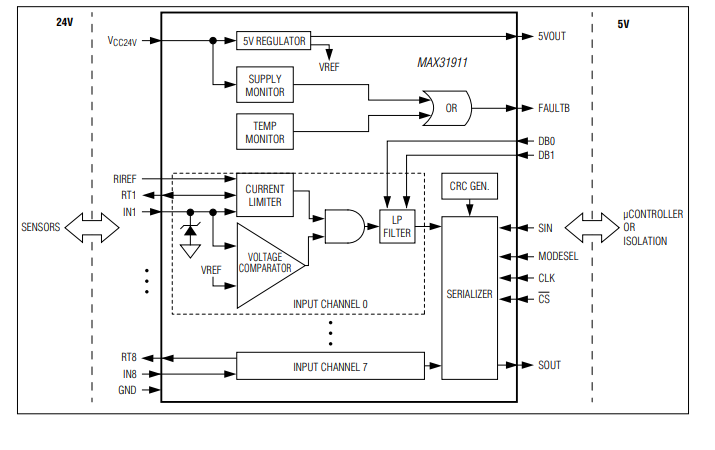

MAX31911是一款工业接口串行器,对传感器、开关的24V数字输出进行电平转换、调理和串行化处理,产生微控制器能够接受的5V CMOS兼容信号,适用于工业、过程控制和楼宇自动化上应用。器件提供了

2025-05-21 14:38:01 753

753

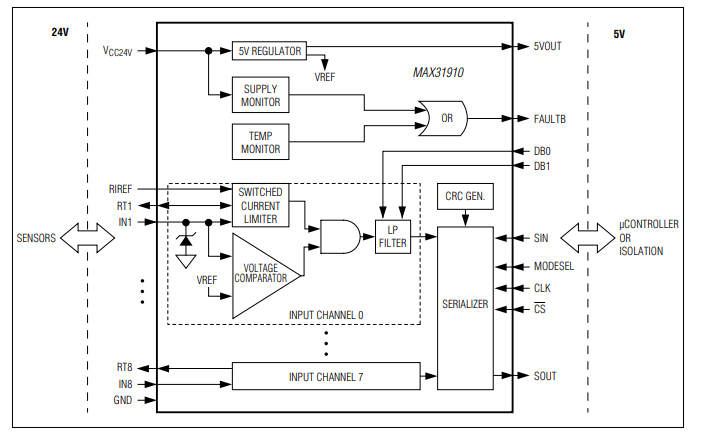

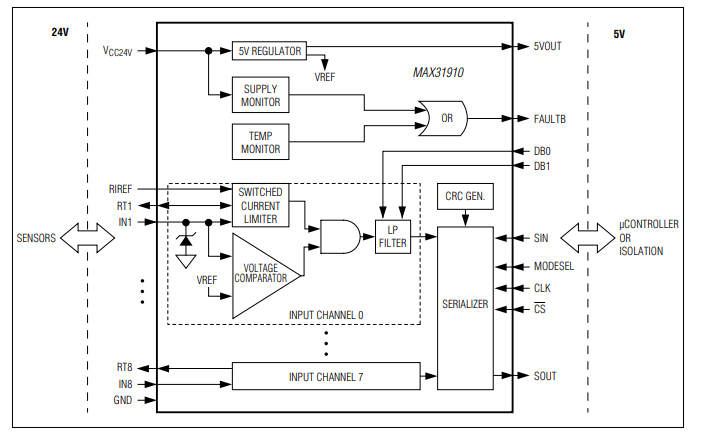

MAX31910是一款工业接口串行器,对传感器、开关的24V数字输出进行电平转换、调理和串行化处理,产生微控制器能够接受的5V CMOS兼容信号,适用于工业、过程控制和楼宇自动化。器件提供可编程逻辑控制器(PLC)数字输入模块前端接口电路。

2025-05-21 14:30:14 647

647

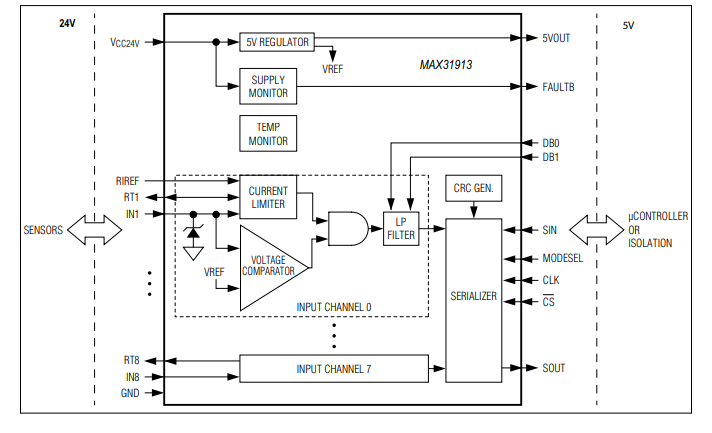

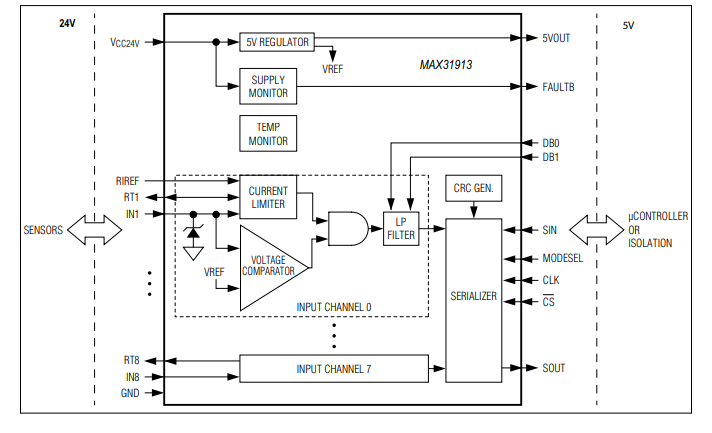

MAX31913是一款工业接口串行器,对传感器和24V数字开关输出进行电平转换、调理和串行化处理,产生微控制器能够接受的5V CMOS兼容信号,适用于工业、过程控制和楼宇自动化应用。器件提供可编程

2025-05-21 14:17:41 869

869

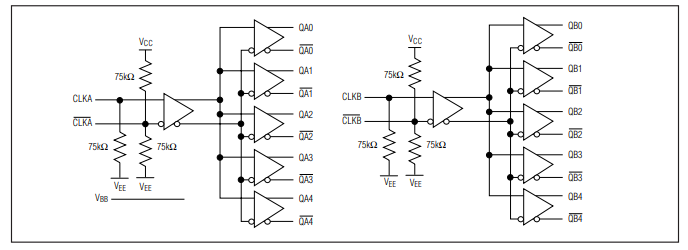

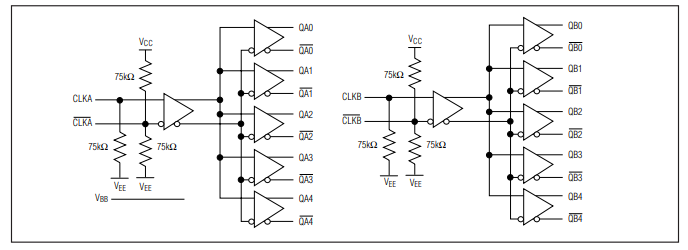

MAX9312/MAX9314是低扭曲、双路1:5差分驱动器,设计用于时钟和数据分配。这些器件接受两路输入。每个输入再生5路差分输出。差分输入经过调整后,可以允许单端输入,只需将片上V~BB~电源接到一个输入端作为参考电压即可。

2025-05-19 11:25:58 943

943

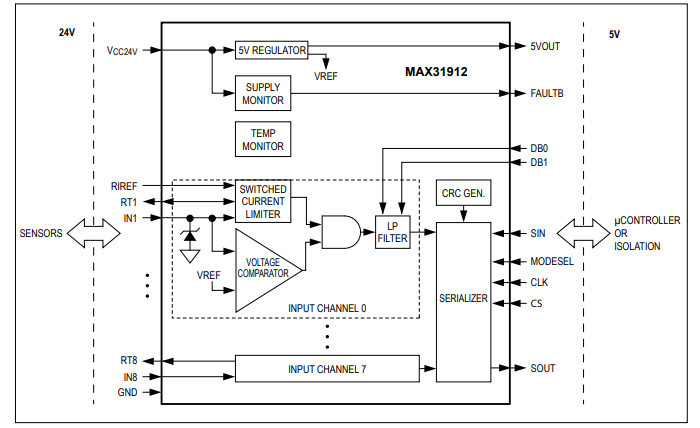

MAX31912是一款工业接口串行器,对传感器和24V数字开关输出进行电平转换、调理和串行化处理,产生微控制器能够接受的5V CMOS兼容信号,适用于工业、过程控制和楼宇自动化应用。器件提供[可编程

2025-05-15 15:19:23 555

555

DS1856双路、温控、非易失(NV)可变电阻具有3路监测器,内置2个256级、线性可变电阻;3路模拟监测器输入(MON1、MON2、MON3)和直接数字化传感器。这款器件可理想用于偏置电压、电流

2025-05-12 11:44:02 660

660

随着5G、物联网、通信等技术的快速发展、国际环境复杂多变,传统测试仪器因体积庞大、功能单一、扩展性差等问题难以满足高频、高精度、多场景的测试需求,在此背景下,“国产化全链路模块测试仪器大会”将于4月

2025-04-18 16:44:48 661

661

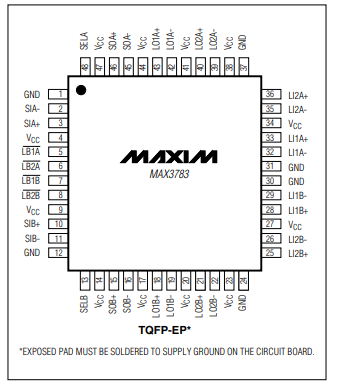

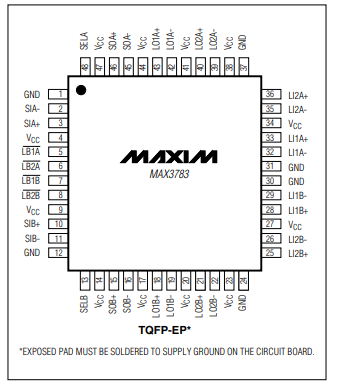

MAX3783为带有可选线端环回的双路串行复用器和缓冲器,用于系统互连的串行背板应用、速率达2.7Gbps。每条独立信道包括一路两扇出的传送器和一路2:1输入复用的接收器。可选环回通道支持系统检测。

2025-04-16 10:01:36 757

757

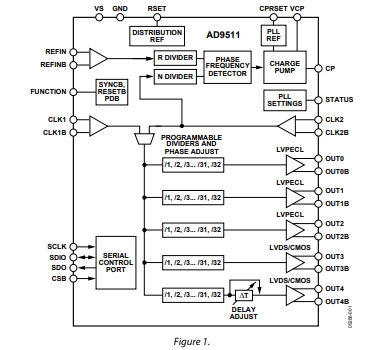

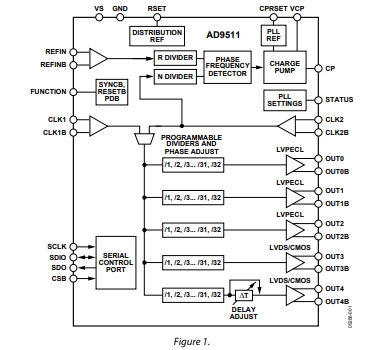

AD9511提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。3路独立的LVPECL时钟输出和2路LVDS时钟输出工作频率分别为1.2 GHz和800 MHz。可选的CMOS时钟输出工作频率为250 MHz。

2025-04-15 13:48:04 960

960

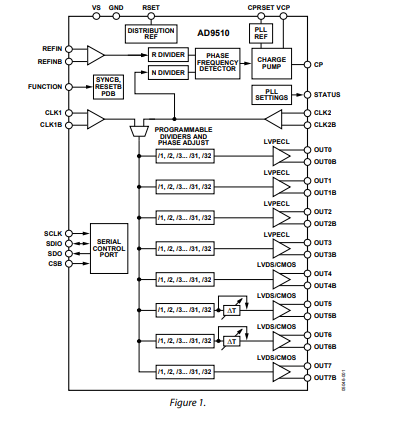

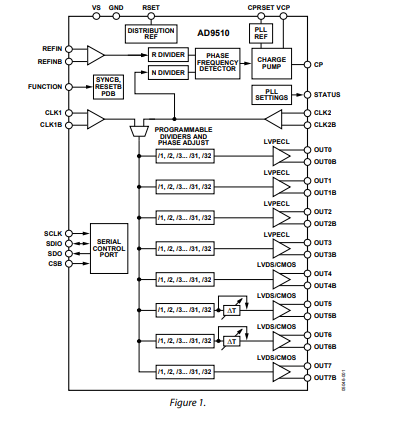

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟输出和4路LVDS时钟输出工作频率分别为1.2 GHz和800 MHz。可选的CMOS时钟输出工作频率为250 MHz。

2025-04-15 11:41:58 809

809

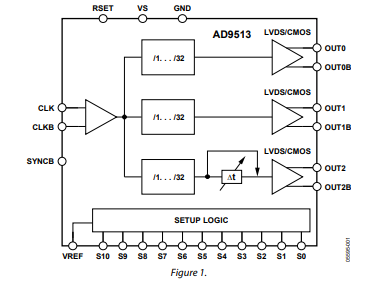

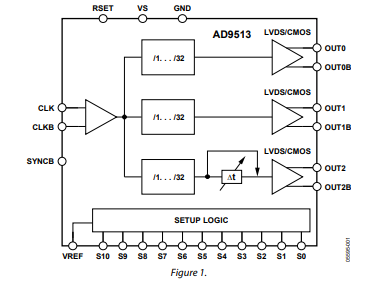

AD9513是一款三路输出时钟分配IC,其低抖动和低相位噪声特性能够实现优质的数据转换器性能。这款器件也适合于对相位噪声和抖动有严格要求的其它应用。

三路独立的时钟输出可被设置为LVDS或CMOS电平。在LVDS模式下,输出工作在800 MHz;在CMOS模式下,输出工作在250 MHz。

2025-04-15 10:57:02 893

893

随着LED照明技术的快速发展和智能照明需求的激增,双路调光技术正成为照明行业的重要发展方向。传统单路调光方案只能实现整体亮度的统一调节,而双路调光则能够实现对两个独立通道的精确控制。今天,由我来为大家揭秘一款极具创新性的调光解决方案 ——FP7195双路调光。

2025-04-11 14:11:38 770

770

AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考时钟之一同步。数字锁相环(PLL)可以降低与外部参考时钟

2025-04-11 09:37:58 757

757

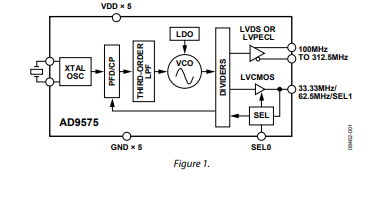

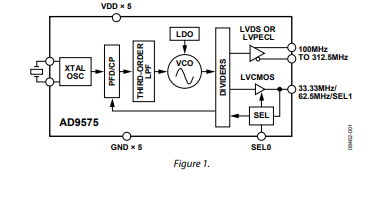

AD9575是一款高度集成的双路输出时钟发生器,包括一个针对网络定时而优化的片内PLL内核。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现线路卡的较高性能。对相位噪声和抖动要求苛刻的其它应用也能受益于该器件。

2025-04-10 17:00:26 957

957

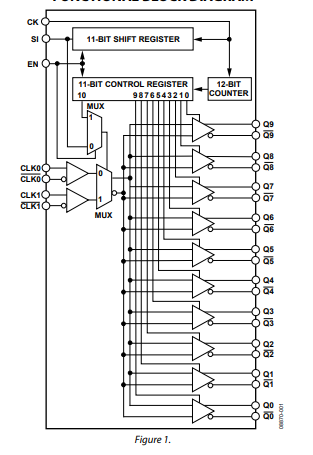

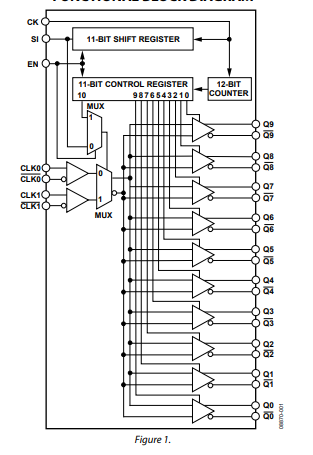

ADN4670是一款低压差分信号(LVDS)时钟驱动器,可以将一路差分时钟输入信号扩展为十路差分时钟输出。这款器件可以通过简单的串行接口进行编程,以便选择两路时钟输入之一(CLK0/CLK0 或

2025-04-10 16:19:00 964

964

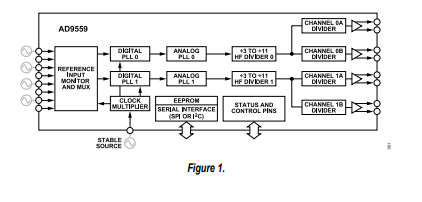

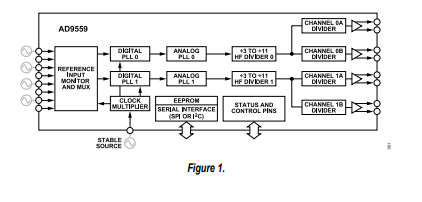

AD9559是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。AD9559产生的输出时钟可以与多达四路外部输入参考时钟同步。DPLL可以

2025-04-10 14:35:01 929

929

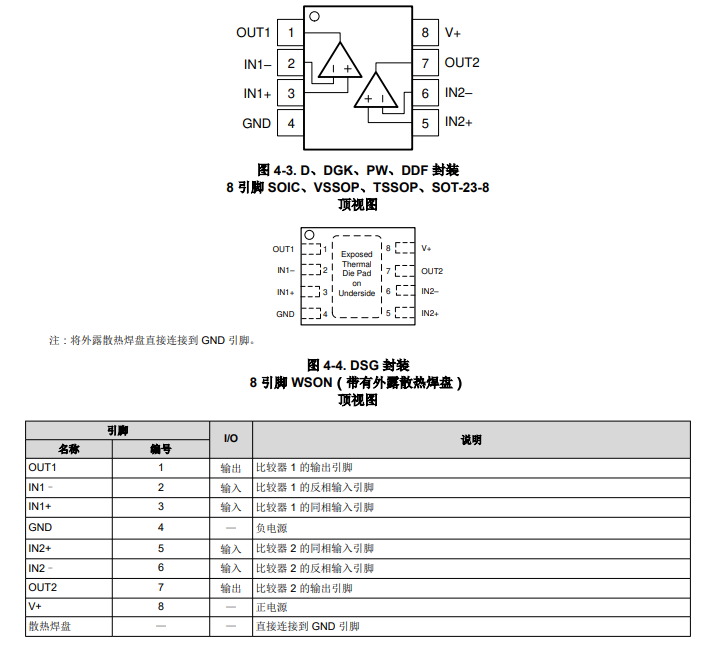

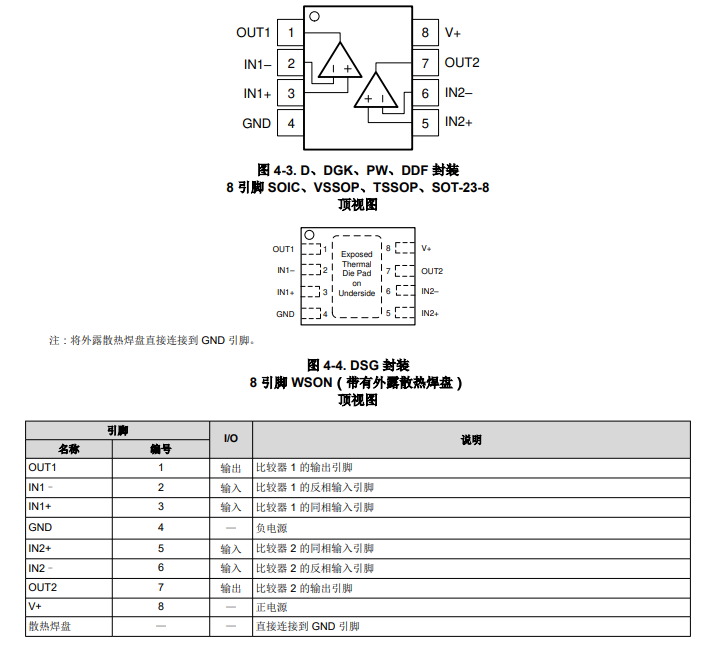

LV 器件系列包含单路、双路和四路独立电压比较器,这些比较器可在宽电源电压范围内运行。LV 器件可直接替代低压 (≤ 5V) 应用中的标准 TL331、LM2xx、LM3xx 和 LM290x 比较器系列,以便提高性能,并增添功能。

2025-04-09 10:55:09 1177

1177

爱立信、Telstra、高通近日携手创下5G上行链路516 Mbps速度新纪录,成为目前在商用Sub-6GHz 5G SA现网实现的最高上行链路速度。

2025-03-26 16:31:42 12970

12970 DAC8143 是一款 12 位串行输入、菊花链数模转换器。它专为多个串行 DAC 系统而设计,其中一个接一个的串行菊花链大大简化了。菊花链功能可节省地址解码线路,从而在多个封装 DAC 设计中实现

2025-03-26 16:11:24

电子发烧友网为你提供AIPULNION(AIPULNION)FA15-220S15G2N4相关产品参数、数据手册,更有FA15-220S15G2N4的引脚图、接线图、封装手册、中文资料、英文资料,FA15-220S15G2N4真值表,FA15-220S15G2N4管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-24 18:52:21

特点DSI 接收器可配置 1 路至 4 路数据通道的 DSI 链路在数据通道 0 上支持双向通信每通道最大比特率为 1Gbps视频输入数据格式:每个像素 16 位的 RGB565 格式每个像素 18

2025-03-05 20:49:50

14路差分输出时钟抖动消除器SC6302,兼容HMC7044

2025-03-05 10:18:43 785

785

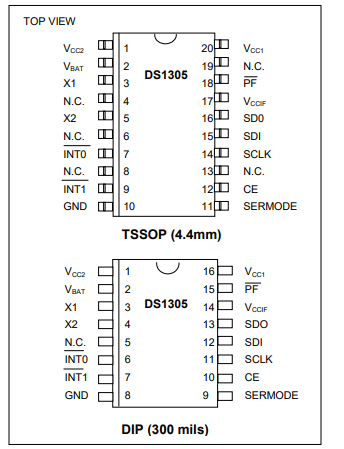

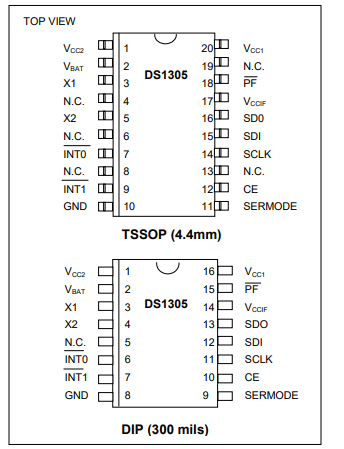

DS1306串行报警实时时钟(RTC)提供完整的二进制编码十进制(BCD)时钟日历,可通过简单的串行接口进行访问。时钟/日历提供秒、分、时、星期、日期、月和年信息。对于少于31天的月份,月底的日期

2025-02-27 15:57:29 1241

1241

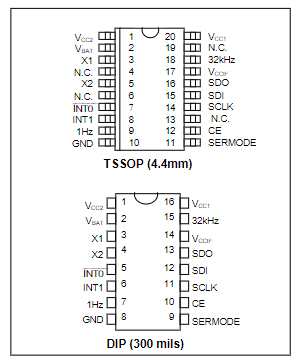

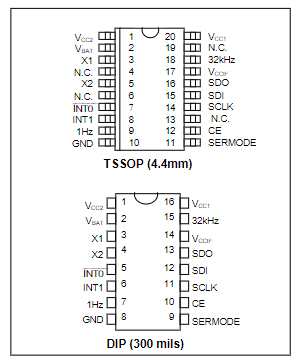

DS1305串行、带闹钟的实时时钟是全二进制编码的十进制(BCD)日历钟,可以通过简单的串行接口访问。该时钟/日历可以提供秒、分、时、日、月、年信息。对于少于31天的月份,到每月的最后一天会自动进行

2025-02-27 11:41:03 901

901

低压单/双路比较器-AiP331LV/AiP393LV

2025-02-25 10:20:26 803

803

关于 ADS1298,我想澄清下列问题:

1. 为什么 ADS1298 在初始化过程中 START 引脚的建立时间会有延迟?如果输入信号在该建立时间过程中 (tsettle) 发生变化,会出

2025-02-17 07:15:00

在设置好控制寄存器后,为了双路输出写两路的寄存器(不管00和02,还是01和02)都只有一路输出(后写的寄存器对应有输出),然后我试了每路重复写两次就可以双路输出,这是为什么。如何解决

2025-02-14 07:56:22

电子发烧友网站提供《74LVC2G00双路2输入与非门规格书.pdf》资料免费下载

2025-02-13 17:14:46 1

1 电子发烧友网站提供《74AUP2G02低功耗双路2输入或非门规格书.pdf》资料免费下载

2025-02-11 14:12:57 0

0

tpl0401的I2C读写应该follow什么样个格式。有没有具体的寄存器地址。

write:

char tmp[2]={0x0,0x0};

tmp[1] = writevalue

2025-02-11 06:24:10

电子发烧友网站提供《74AUP2G00低功率双路2输入与非门规格书.pdf》资料免费下载

2025-02-10 14:06:22 0

0 4G/5G 路由器通过模块拨号上网,链路检查功能是拨号链路的一种辅助监测手段,通过对指定的⽬标IP进⾏Ping检测,判断链路是否正常,⼀旦监测到链路异常且达到最⼤失败次数可执⾏相应的恢复操作。

2025-02-10 10:11:44 1408

1408

双北斗时钟服务器是一种基于北斗卫星导航系统的时间同步设备,通过接收双路北斗卫星信号,为各种设备和系统提供精确的时间校准和同步服务。以下是关于它的详细介绍: 适用于对时间精度要求极高的企业级应用,如

2025-01-22 16:35:41 963

963

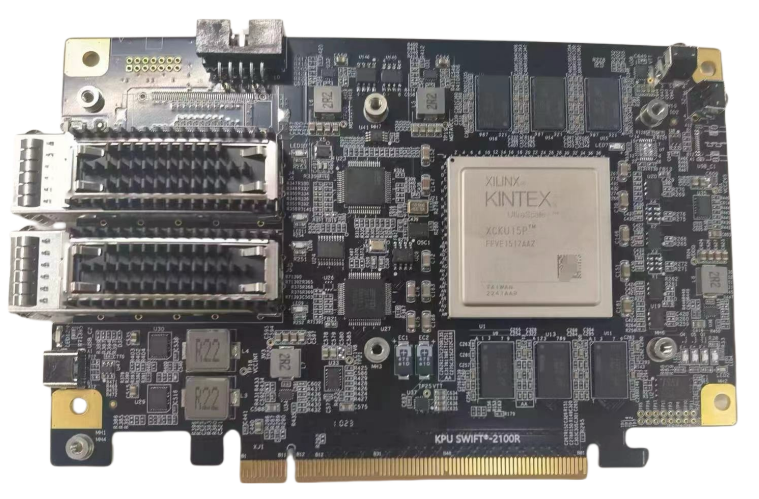

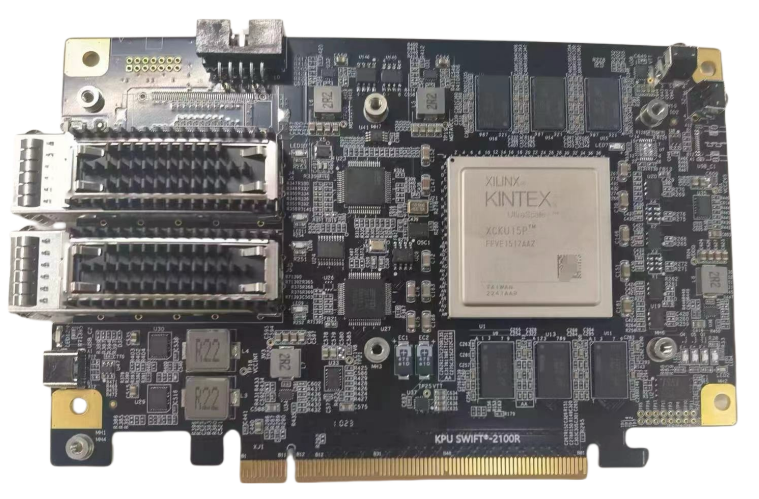

,每组容量达 4GB,可稳定运行在 2666MT/s,支持 2 路 QSFP28 接口,支持 2x100G 数据传输速率,板卡设计满足工业级要求,可用于数据中心、智能网卡、DPU 等领域。 Kintex

2025-01-15 10:11:54 1110

1110

HT25Q20D是由深圳市华芯邦科技有限公司研发,适用于物联网,5G,汽车,计算机,消费品,HT25Q20D(2M位)串行闪存支持标准串行外围接口(SPI),并支持双SPI:串行时钟、芯片选择、串行

2025-01-10 14:30:12 933

933

电子发烧友App

电子发烧友App

评论