为0xFF,目的地址后64kb全部初始化为0,传输64kb数据,发现目的地址传输到数据有部分丢失,隔10几个地址就全是0(猜测未传输成功)

2、源地址:0x30000000(D2域 SRAM

2024-03-19 07:32:40

电子发烧友网站提供《具有可编程SRAM的TPS23880 4 型4线对8通道PoE PSE控制器数据表.pdf》资料免费下载

2024-03-15 10:17:20 0

0 电子发烧友网站提供《具有SRAM和200mΩ RSENSE的TPS23881 4型4线对8通道PoE PSE控制器数据表.pdf》资料免费下载

2024-03-15 10:07:03 0

0 电子发烧友网站提供《具有SRAM和200mΩ RSENSE的TPS23882 3型2 线对8通道PoE PSE控制器数据表.pdf》资料免费下载

2024-03-15 10:04:45 0

0 通过外部引脚可配置BOOT从SRAM中启动,上电过程SRAM没有初始化,BOOT从SRAM启动的作用是什么,这个我不能理解。

我想实现所有程序都在SRAM中运行,有没有实现的方法?

2024-03-12 07:30:49

我将一个数组定义在SRAM2中,另一个数组定义在CCM中,我可以利用memcpy这个函数来将SRAM2里的数据拷贝到CCM中吗。

因为我看总线矩阵图,CCM的D-BUS和SRAM2并无交集,是不是也就意味着这两块内存互相无法进行交互呢?

2024-03-06 08:21:14

你好,我使用的是CYTVII-B-H-8M-176开发板,IAR 9.50.1

我在CM0工程中加入了自己的程序,其中会定义一些大数组,用来给程序运算使用。目前我已经修改了icf文件下图三行。

但编译还是遇到SRAM不够的问题,麻烦看下该如何解决,谢谢。

2024-03-05 06:01:47

FX3自带SDK中的例程GPIF ii sram-master:读写sram指令中的地址由状态机中的地址计数器来决定,请教一下如何在FX3固件代码中指定读写sram的地址,可否提供一个例程或相关文档

2024-02-27 07:20:24

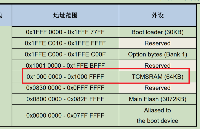

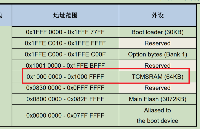

如下图所示,GD32F4系列内部SRAM分为通用SRAM空间和TCMSRAM空间,其中通用SRAM为从0x20000000开始的空间,TCMSRAM为从0x10000000开始的64KB空间。大家

2024-02-24 09:43:16 186

186

赛普拉斯的NV-SRAM将标准快速SRAM单元(访问时间高达20 ns)与基于硅氧化物和亚硝酸盐,氧化物硅(SONOS)的非易失性存储元件相结合,可提供快速的异步读写访问速度,并在其整个工作范围内具有20年的数据保留。

2024-02-19 10:52:40 191

191

我正在与 SafetPack 为 TC38x 调试的无损测试 (MBIST) 合作。 但我找不到 Geth Tx/Rx RAM 和 gtm_mcsxslow/Fast-DPLL RAM 的正确的 SRAM 初始化过程。

你能否给我一些关于上面提到的 RAMS 的初始化过程的提示。

2024-02-01 07:09:22

你好 tms570能够直接跑在sram上吗?

从flash加载程序1之后,程序1把程序2搬移到sram中,然后在sram中运行程序。TMS570支持这样运行不?

2024-01-19 09:24:49

您能告诉我 PSoC™ 4中SRAM阵列的数据保持电压吗?

我想知道在 VDD 电源电压下降或上升时 SRAM 可以保留数据的最小电压。

MPN: PSoC™ 4100S Max/CY8C4148AZI-S555

2024-01-19 06:08:12

现在准备 用21489的SRAM接口与FPGA通信,怎么利用MS0/1实现地址数据线的连接使用??MS0/1怎么用也不太理解?是地址译码?

2024-01-12 07:40:17

赛普拉斯的NV-SRAM将标准快速SRAM单元(访问时间高达20 ns)与基于硅氧化物和亚硝酸盐,氧化物硅(SONOS)的非易失性存储元件相结合,可提供快速的异步读写访问速度,并在其整个工作范围内具有20年的数据保留。

2024-01-09 10:54:28 171

171

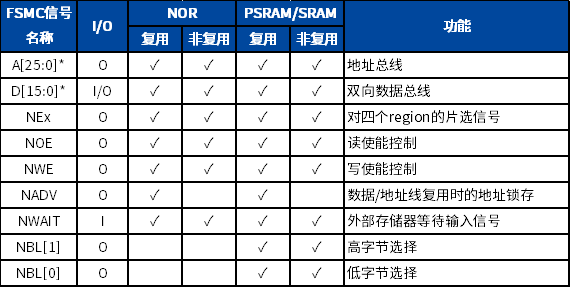

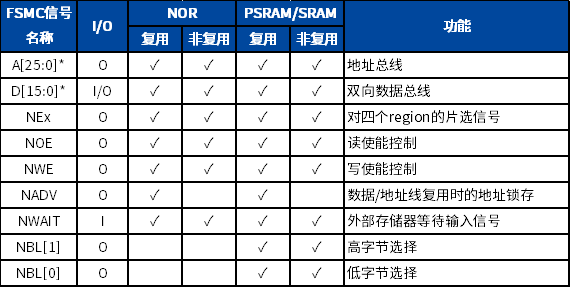

描述:AT32F403A引脚比较紧张,XMC(类似于STM32 FSMC)只支持复用模式,就是A0-A15和D0-D15都用一个引脚,如果要用,只能用锁存器将地址锁存,实现地址线和数据线的分离,目前

2024-01-04 10:46:19

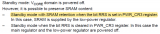

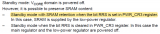

某客户使用 STM32G071 芯片从 standby 模式下唤醒,想要 SRAM 的数据在退出 standby模式后得以保持。根据手册的描述,配置了相应的比特位,但是发现数据仍然保持不了。

2023-12-20 09:31:27 374

374

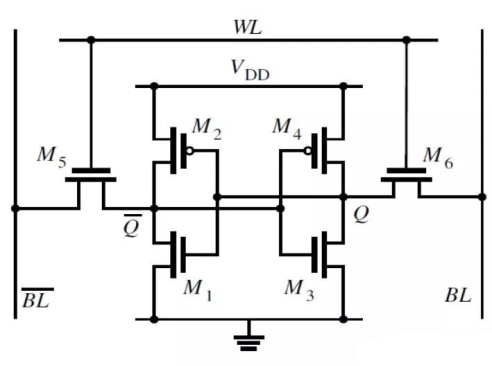

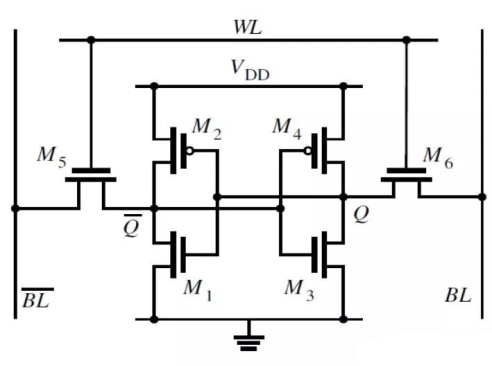

,从基本原理到电路设计的细节。 SRAM是一种基于存储双稳态的存储器技术,它使用触发器来存储数据。一个典型的SRAM单元由6个传输门(传递门)组成,其中包括两个传输门用于存储和读取数据,以及两个传输门用于写入和刷新数据。 SRAM的读取操作是通过将地址输入到SRAM中来完成的。当地址输入到

2023-12-18 11:22:39 496

496 西门子 EDA的内存技术专家Jongsin Yun说, SRAM 的微缩滞后于逻辑收缩,主要是由于最新技术中严格的设计规则。过去,我们对 SRAM 有单独的设计规则,这使我们能够比基于逻辑晶体管

2023-12-15 09:43:42 175

175 SRAM是采用CMOS工艺的内存。自CMOS发展早期以来,SRAM一直是开发和转移到任何新式CMOS工艺制造的技术驱动力。

2023-12-06 11:15:31 635

635 ADSP-BF533执行完BOOT-ROM中的加载程序后,将复位的程序起始地址设为 0ffa08000 ,即内部L1 Instruction SRAM的起始地址,那么是不是就意味着必须将main函数文件放置在L1 Instruction SRAM中?如果想要将所有程序放置在外部扩展的SRAM怎么办?

2023-11-29 07:12:04

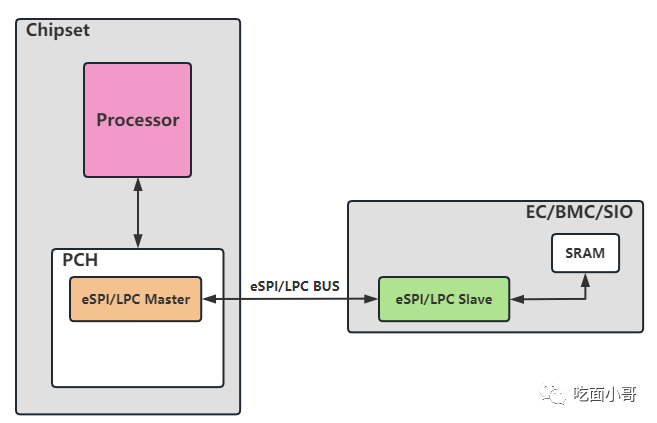

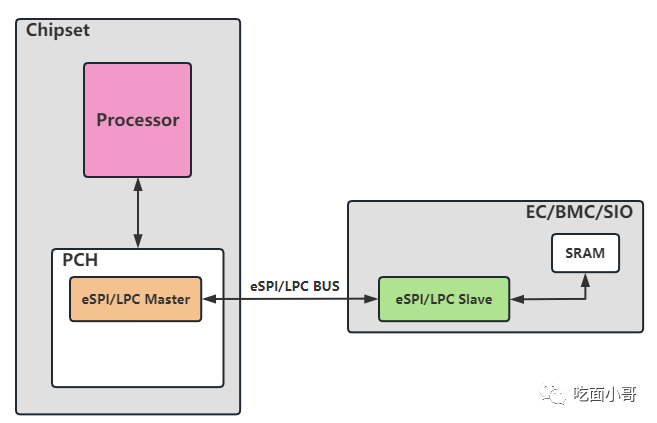

ShareMemory,顾名思义就是共享内存。这个概念在很多计算机系统中都存在,本文特指 EC SRAM 映射到 CPU Memory 空间的共享内存设计。

2023-11-18 15:11:36 599

599

SRAM 的数量是任何人工智能处理解决方案的关键要素,它的数量在很大程度上取决于您是在谈论数据中心还是设备,或者是训练还是推理。但我想不出有哪些应用程序在处理元件旁边没有至少大量的 SRAM,用于运行人工智能训练或推理。

2023-11-12 10:05:05 452

452 AT32F系列 使用DMA将数据从FLASH传输到SRAM

2023-10-27 07:58:50

EPM1270F256C4N,ALTERA/阿尔特拉,即时开启非易失性CPLD,处理器EPM1270F256C4N,ALTERA/阿尔特拉,即时开启非易失性CPLD,处理器

2023-10-24 15:38:16

AVR对片内SRAM的访问需要多久?

2023-10-24 07:49:15

如何查看MDK编译后程序所占用的Flash和SRAM资源的大小?

另外在.s启动文件中堆和栈的大小又该如何分配?

2023-10-24 07:25:10

PSRAM/SRAM与XMC硬件连接的推荐方法描述了在AT32系列100引脚封装芯片上以XMC连接PSRAM的硬件推荐方法,达到器件容易取得及价格合理的目标。

2023-10-24 06:17:32

如何修改AT32的SRAM空间大小如何修改SRAM大小?

2023-10-20 07:39:21

AT32 部分型号有零等待闪存和非零等待闪存,程序在零等待闪存执行速度比在非零等待闪存执行速度快,如果有函数对执行速度有要求,可以将该函数加载到零等待区执行。当零等待闪存使用完后,如果还有函数对执行速度有要求,可以将该函数加载到 SRAM 执行,前提是SRAM 还有足够的空间存放该函数代码。

2023-10-20 06:10:59

掉电后还能读取到SRAM的数据吗

2023-10-15 09:24:03

STM8可以实现从SRAM启动程序吗

2023-10-09 07:38:29

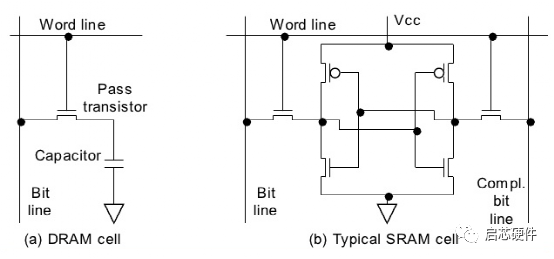

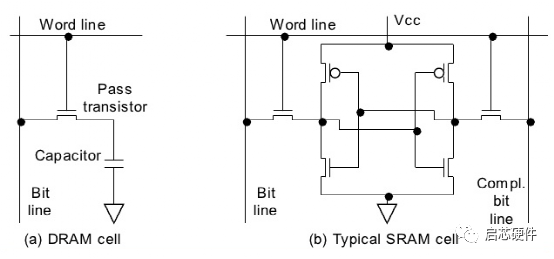

硬件面试的时候,看到应聘者简历上写着,有过AMD工作或实习经历,熟悉CPU和内存。于是我问,那请你画一下SRAM和DRAM的基本cell出来,然后简要说一下工作原理及特点,但是没能说出来。

2023-10-01 14:08:00 2382

2382

如何提高SRAM的读取速度

2023-09-28 06:28:57

FSMC外扩SRAM数据之间是怎么传送的?先保存在FSMC再传送外扩SRAM

2023-09-27 06:03:22

使用MM32F3270 FSMC驱动SRAM

2023-09-18 16:29:50 918

918

应用程序: 此示例代码使用 M032 在 SRAM 中运行 ISR 。

BSP 版本: M031_Series_BSP_CMSIS_V3.03.000

硬件: NuMaker-M032SE

2023-08-31 09:21:19

应用程序: 此示例使用 M487 SPIM 接口访问 DMM 模式的外部 SRAM 。

BSP 版本: M480_BSP_CMSIS_V3.05.001

硬件: NuMaker-PFM-M487

2023-08-29 07:42:17

NUC472/NUC472/NUC442系列装有外部连接设备的外部公交界面(EBI)。 NUC472/NUC442 EBI便利连接控制界面由地址、数据、芯片选择和读/写斯特罗贝组成的设备,例如NOR闪光

2023-08-23 06:35:44

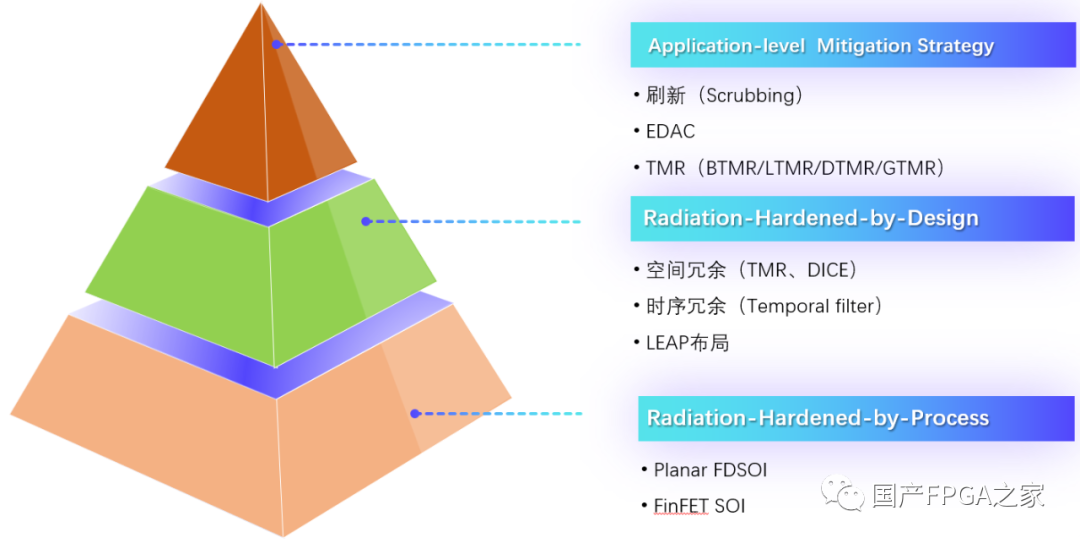

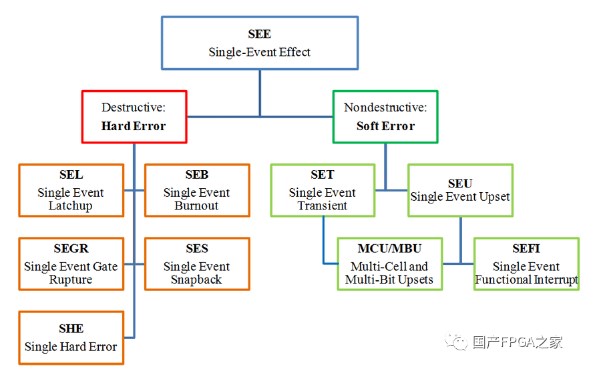

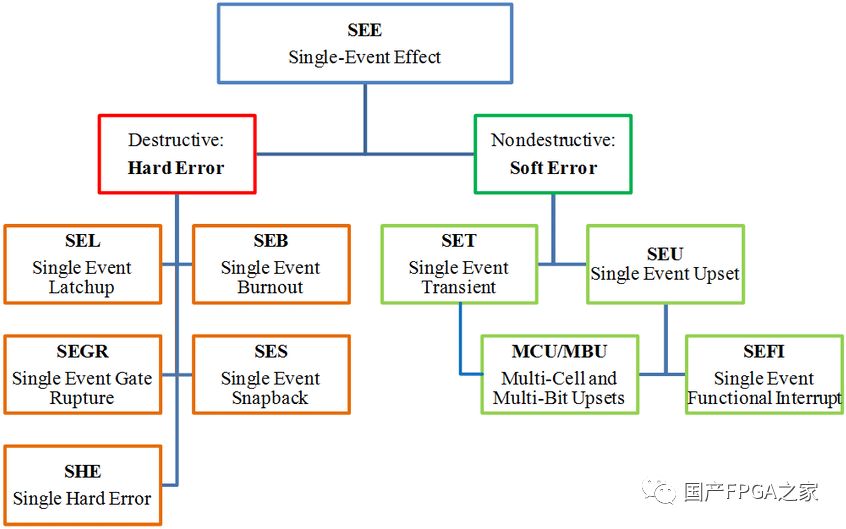

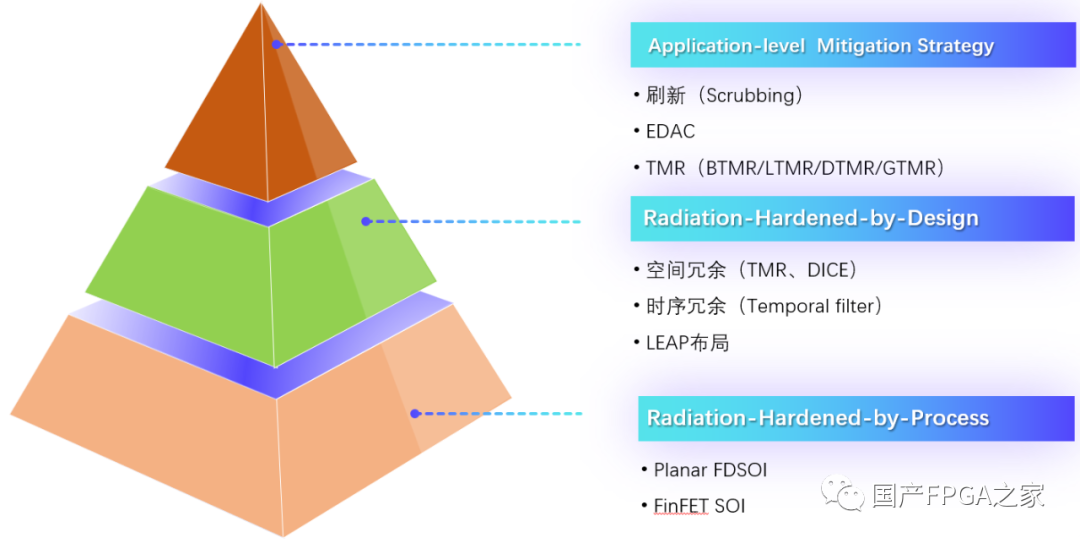

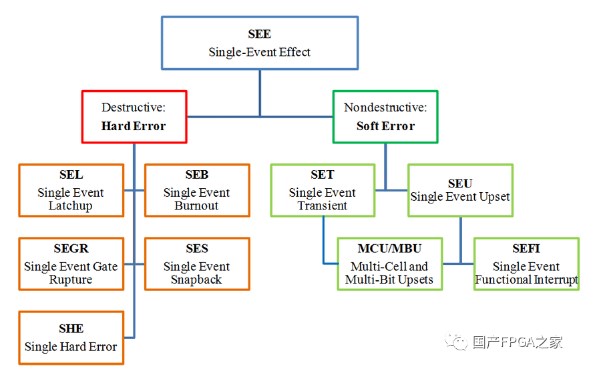

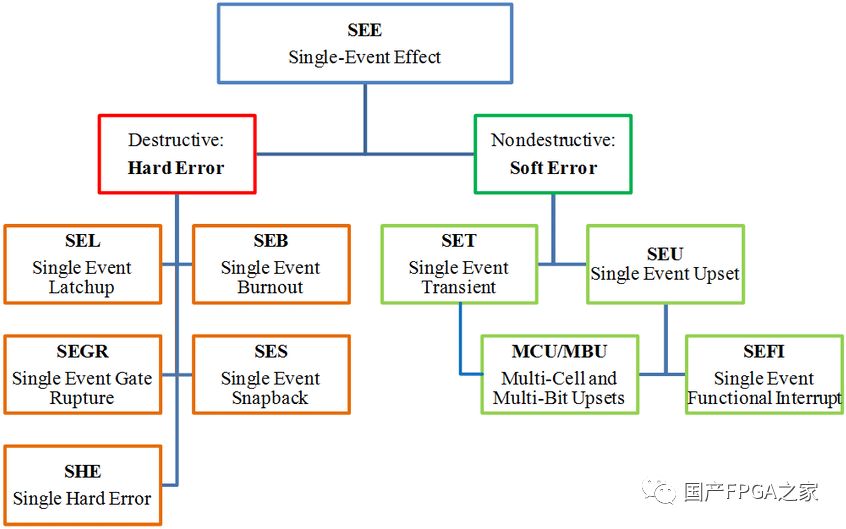

让一颗SRAM型FPGA在太空长期稳定运行的难度,就类似练成独孤九剑的难度。

2023-08-15 10:36:08 1898

1898

SRAM型FPGA属于核心元器件,因此对SRAM型FPGA进行抗辐照加固设计非常必要。今天贫道主要给大家布道一下SRAM型FPGA在轨会遇到的问题及其影响。

2023-08-11 10:32:46 1086

1086

SRAM型FPGA属于核心元器件,因此对SRAM型FPGA进行抗辐照加固设计非常必要。今天贫道主要给大家布道一下SRAM型FPGA在轨会遇到的问题及其影响。

2023-08-11 10:30:45 1264

1264

为0xFF,目的地址后64kb全部初始化为0,传输64kb数据,发现目的地址传输到数据有部分丢失,隔10几个地址就全是0(猜测未传输成功)

2、源地址:0x30000000(D2域 SRAM

2023-08-07 13:02:00

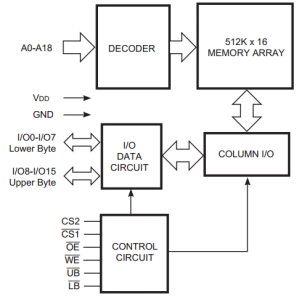

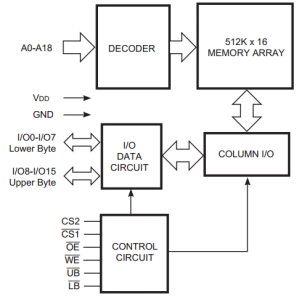

本次操作的SRAM的型号是IS62WV51216,是高速,8M位静态SRAM。它采用ISSI(Intergrated Silicon Solution, Inc)公司的高性能CMOS技术,按照512K个字(16)位进行组织存储单元。

2023-07-22 14:58:56 1092

1092

DS1250 4096k、非易失SRAM为4,194,304位、全静态非易失SRAM,按照8位、524,288字排列。每个完整的NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出容

2023-07-21 15:41:00

DS1245 1024k非易失(NV) SRAM为1,048,576位、完全静态的非易失SRAM,按照8位、131,072字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否

2023-07-21 15:38:54

DS1230 256k非易失(NV) SRAM为262,144位、全静态非易失SRAM,按照8位、32,768字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出容差范围

2023-07-21 15:37:16

DS1225AB及DS1225AD为65,536位、全静态非易失(NV) SRAM,按照8位、8192字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出容差范围,一旦

2023-07-21 15:29:48

DS1220AB及DS1220AD 16k非易失(NV) SRAM为16,384位、全静态NV SRAM,按照8位、2048字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC

2023-07-21 15:28:06

DS1345 1024k非易失(NV) SRAM为1,048,576位、全静态非易失SRAM,按照8位、131,072字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出

2023-07-21 15:23:14

DS1330 256k非易失(NV) SRAM为262,144位、全静态非易失SRAM,按照8位、32,768字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出容差范围

2023-07-21 15:20:44

DS1270 16M非易失SRAM为16,777,216位、全静态非易失SRAM,按照8位、2,097,152字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出容差范围

2023-07-21 15:18:27

DS1265 8M非易失SRAM为8,388,608位、全静态非易失SRAM,按照8位、1,048,576字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出容差范围

2023-07-21 15:13:33

DS1249 2048k非易失(NV) SRAM为2,097,152位、全静态非易失SRAM,按照8位、262,144字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视VCC是否超出

2023-07-21 15:11:06

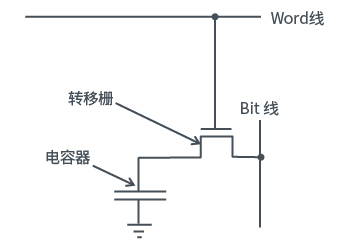

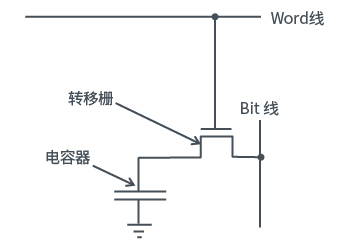

元器件原理<DRAM> 由1个晶体管、1个电容器构成 数据的写入方法 <“1” 时> Word线电位为 high Bit线电位为 high Word线电位为 low 元器件原理<SRAM> 存储单元

2023-07-12 17:29:08 754

754

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是从功耗测试角度了解i.MXRTxxx系列片内SRAM分区电源控制。

2023-07-07 09:58:03 666

666

IP_数据表(M-1):SRAM and TCAM

2023-07-06 20:12:09 0

0

************************************************* *************************************

* 详细说明:

* 这个例子的目的是展示如何保存数据在 SRAM 存储器中通过

2023-06-05 09:47:48

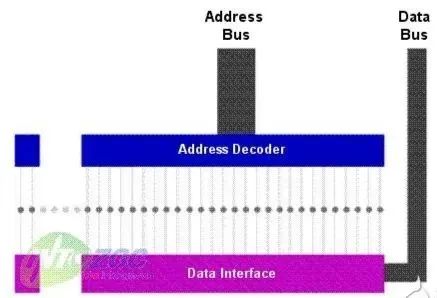

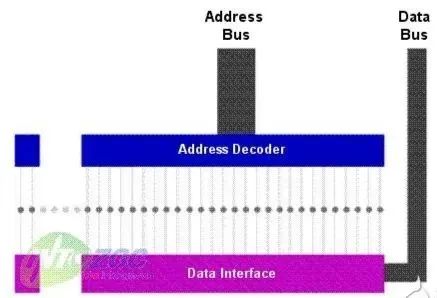

(Flexible Memory Controller)模块,将SRAM地址范围映射到外部地址线上,然后通过外部总线访问SRAM,实现对该区域的访问。需要注意的是,还需要在代码中正确配置FMC控制器和外部存储器的类型、时序等参数,才能保证数据的正确读写。

2023-06-01 18:18:45 382

382 我们正在构建一个设备来测量消耗。电路 ACS712 读取那一刻的消耗量,所以,我需要做一个每秒累加的方法。问题:非易失性内存有写入限制,所以我需要使用易失性内存。写入易失性存储器是否有一些限制?我们的想法是每秒读取一次 ACS712 并写入易失性存储器,每 10 分钟写入一次非易失性存储器。

2023-05-30 08:48:06

: *** [makefile:266: main.elf] 错误 1

在查看数据表后,我已经将 sram 区域从默认的 28KB 扩展到 34KB。如果我将另一个 1KB 扩展到 35KB,我会

2023-05-19 08:31:12

SRAM(Static RAM)不需要刷新电路即能保存它内部存储的数据?其中的“刷新电路”什么意思?谢谢~

2023-05-10 14:56:06

到了FSMC的NE3端口,地址为19位,数据为16位,设置一下cubemx,时序配置为0;4;0

生成代码,我这里是用的Makefile

把显存放在SRAM中,代码如下

static uint16_t

2023-05-08 20:01:14

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用户手册

2023-04-27 20:25:40 6

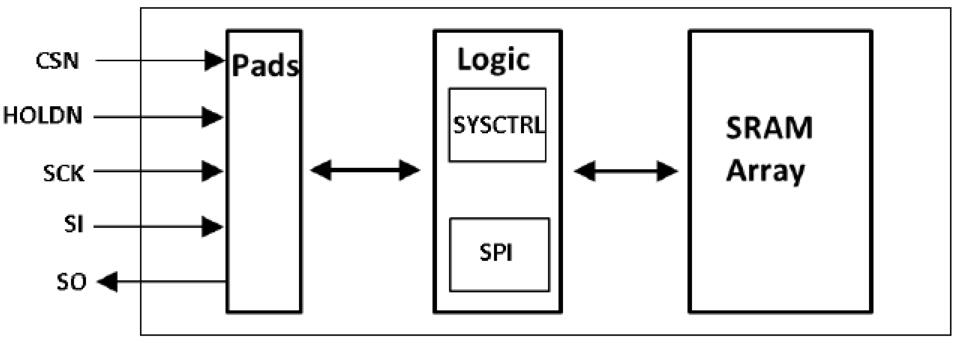

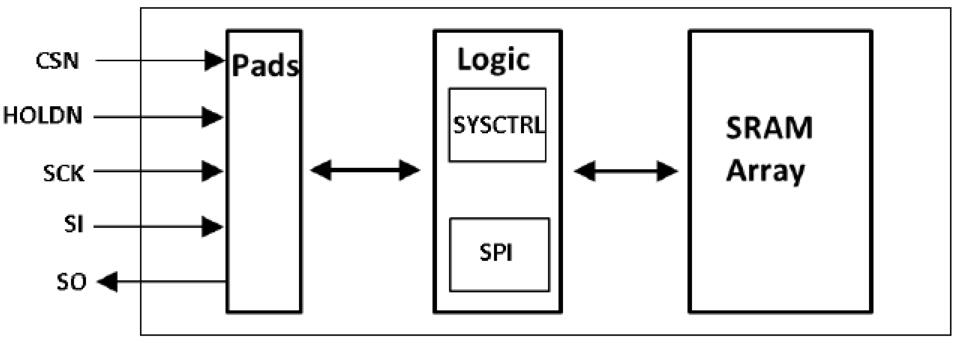

6 EMI Serial SRAM是为串行接口的SRAM,外扩SRAM可以通过使用SPI的接口来将外部RAM添加到几乎所有应用中。串行访问的静态随机存取存储器采用先进的CMOS技术进行设计和制造,以提供高速性能和低功耗。

2023-04-27 17:37:44 615

615

用FPGA往SRAM芯片中写数据重复写多次才能写是怎么回事呢?

2023-04-23 11:46:44

FPGA重复读取同步SRAM所有地址数据,一定时间后随机出现某个或者某些地址为数据永久性出错,期间写控制位一直为无效状态,可能是哪些原因?

2023-04-23 11:45:30

我正在使用 S32k358 uC,我想禁用内存区域的数据缓存。在框图中,我看到树形 SRAM 块 SRAM0、SRAM1、SRAM2。是否可以禁用 SRAM2 的数据缓存并保留 SRAM 0 和 SRAM1 的数据缓存?

2023-04-23 08:01:09

IMXRT1064 外部 SRAM - 同步和异步模式的 CLK 使用差异

2023-04-21 08:31:29

[Build 9221] [2023-03-28] SDK 是 SDK_2.x_LPC55S06 2.13.0.201911251446如果我启动并设置一个新项目,编译后,我没有任何错误,SRAM

2023-04-20 09:06:04

为0xFF,目的地址后64kb全部初始化为0,传输64kb数据,发现目的地址传输到数据有部分丢失,隔10几个地址就全是0(猜测未传输成功)2、源地址:0x30000000(D2域 SRAM1),目的地

2023-04-14 15:25:19

内存放入 SRAM_OC2,SRAM_ITC_cm7 的内存使用从 150% 减少到 140% .顺便说一句,在应用程序链接到RAM时是否需要将SRAM_ITC_cm7设置为第一个?我已经将具有512KB的SRAM_OC1设置为第一个,调试器无法重置并且通过DMA传输的数据是错误的。为什么?

2023-04-14 08:01:47

我目前正在使用 YOCTO sumo linux 内核 L4.14.98-2.3.1 和 imx6ul。在我的应用程序中,我们需要将安全数据(例如密钥)存储在安全非易失性存储 (SNVS) 区域

2023-04-14 07:38:45

/ld.exe:LPC5516_Project.axf 部分“.bss”不适合区域“SRAM” c:/nxp/mcuxpressoide_11.6.0_8187/ide /plugins

2023-04-11 06:04:20

我想用非易失性密钥获取CMAC值(仅验证甚至可以)。我正在使用修改后的“csec_boot_protection_s32k148”项目。初始化 CSEc 模块后,我使用给定的指令加载密钥 ROM

2023-04-10 06:34:32

SRAM可以分为低速、中速、高速。===========================================================16位宽的SRAM//16BITSRAM指针

2023-04-06 15:13:03 554

554

前两期,我们分别对OTP和MTP,RAM和ROM进行了比较。这一次,我们来谈谈Memory Compiler,以及通过它生成的Register file和SRAM。

2023-03-31 10:56:37 8516

8516 在了解SRAM之前,有必要先说明一下RAM。RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用书架摆放书籍一样,不但要放进去还要

2023-03-30 14:15:53 3184

3184

今天就带你详细了解一下到底什么是SRAM,在了解SRAM之前,有必要先说明一下RAM:RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。

2023-03-30 14:11:51 587

587

我正在寻找一些与 IMXRT1064 的外部 SRAM 使用相关的信息。例如,EVK 有 256Mbit 166MHz SDRAM。166MHz与使用过的SDRAM有关。我试图找到 SEMC 控制器

2023-03-30 07:11:18

我在LPC4357FET256的EMC上有一个外部SRAM,型号是IS61WV5128EDBLL-10TLI。写完驱动调试的时候发现一个很奇怪的问题。如图所示,我写了一个功能验证程序。外部SRAM

2023-03-28 08:13:08

亲爱的社区,我有几个关于 SRAM ECC 的问题。1) SRAM 上的ECC 是否默认启用?哪些代码使 SRAM 上的 ECC 启用?2) 我试图从 M7 内核启动 A53 内核,所以我必须

2023-03-27 09:15:16

电子发烧友App

电子发烧友App

评论