: EVAL_PASCO2_SENSOR 供应商给出的确切值 -> 我相信我无法更改

数据通道:摄像机有 4 个数据通道连接到其序列化器。 我匹配的 Deserializer 子 COOLDIM_PRG_BOARD

2024-02-26 08:41:06

众所周知,序列发送模块可以不需要脚本代码实现测试中特定控制报文序列的发送,该模块多用于循环顺序控制的测试案例中。序列发送模块的常用场景,主要是针对一些新开发的产品需要通过该模块来验证产品功能等等

2024-02-19 14:00:11 111

111

脉冲信号和单位采样序列有何区别? 脉冲信号和单位采样序列是数字信号处理中两个重要的概念。在本文中,我们将详细介绍这两个概念的定义、特点以及它们之间的区别。 一、脉冲信号的定义和特点 脉冲信号是一种

2024-02-06 09:25:24 277

277 Aurix系列单片机时钟系统有哪些特点

2024-02-04 06:48:15

ADAS3022设置为基本序列器模式,CFG设置为0xE0FF,最后数据读出一直为IN6/IN7的电压值,没有其它通道的值,序列器没有启动,连续读数,在IN6/IN7的数值后为CFG的设置值0x60FF,由读出的CFG的值可以确认CFG已经设置成功,但是不知道为什么序列器没有启动,请大家帮忙解决一下

2023-12-18 06:07:15

我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是[时钟周期]() 约束。

2023-12-04 15:44:02 352

352

的答案:

(1)总的建立时间就等于两级运放的建立时间之和,即90 ns + 90 ns =180 ns

(2)总的建立时间还是90 ns

(3)认为两级运放相互独立,总的建立时间等于两级运放建立时

2023-11-27 06:54:56

在为ad7610选择一个单电源的驱动放大器,手册中推荐的ad8021是双电源,建立时间参数为:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2023-11-17 06:22:37

Evilparcel漏洞可以导致Bundle在多次序列化和反序列化过程中内容发生改变。结合LAW跳板,可以实现权限提升,严重影响系统安全

2023-11-16 14:43:35 132

132

各位前辈好,

最近碰到一个棘手问题,研究了好几天了,一直没有搞好:

一个变频器同时带动3个热继电器,每个热继电器下方都有一个电机。电机、热继电器的型号都一样。其中一个提升电机用的热继电器,运行时

2023-11-13 07:54:34

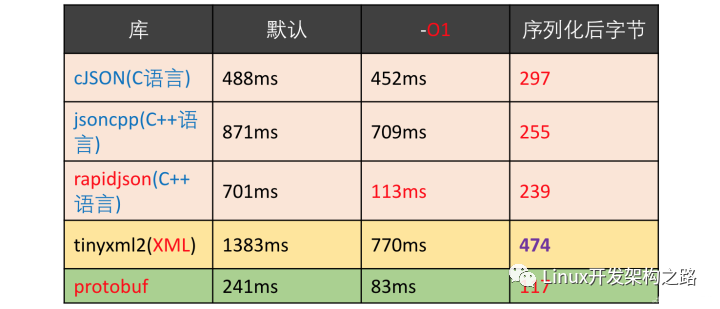

程序开发中,序列化是经常需要用到的。像一些相对高级语言,比如JAVA, C#都已经很好的支持了序列化,那么C++呢?当然一个比较好的选择就是用Boost,这个号称C++准标准库的东西。 什么时候需要

2023-11-10 10:14:30 180

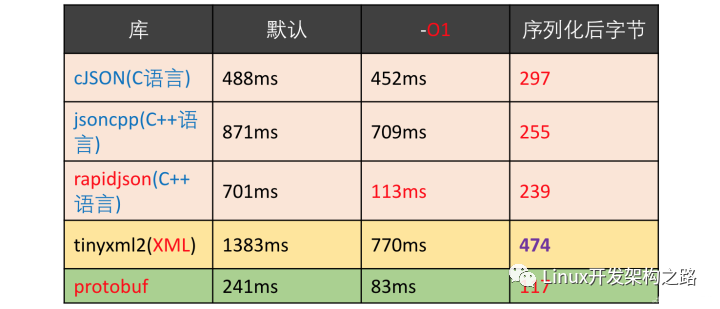

180 一、protobuf简介: 1.1 protobuf的定义: protobuf是用来干嘛的? protobuf是一种用于 对结构数据进行序列化的工具,从而实现 数据存储和交换。 (主要用于网络通信

2023-11-09 09:27:42 378

378

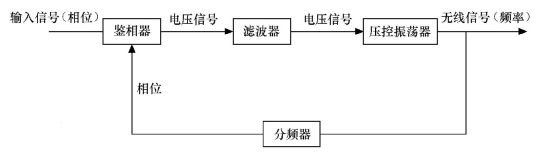

m序列简介

m序列是一种常用的伪随机序列,由具有反馈函数的移位寄存器电路产生,具有周期性,一旦反馈表达式及移位寄存器的初值(又称为种子)给定,就可以重复实现某组确定的序列值。该特点使得m序列在数

2023-11-06 17:03:26

晶振在电路中起到提供稳定的时钟信号的作用。时钟信号是电子设备中非常重要的信号之一,它用于同步各个电路模块的工作,确保它们按照正确的时间序列进行操作。

2023-11-01 18:14:41 378

378 Pydantic 是一个使用Python类型注解进行数据验证和管理的模块。安装方法非常简单,打开终端输入: pip install pydantic 它类似于 Django DRF 序列化器的数据

2023-10-30 11:40:04 259

259 如何用VHDL设计同步序列发生器与检测器

2023-10-18 08:07:04

STM32的独立看门狗用的时钟是内部时钟还是外部时钟呢

2023-10-15 11:58:05

STM8的独立看门狗可以直接用内部低速时钟吗

2023-10-11 06:04:40

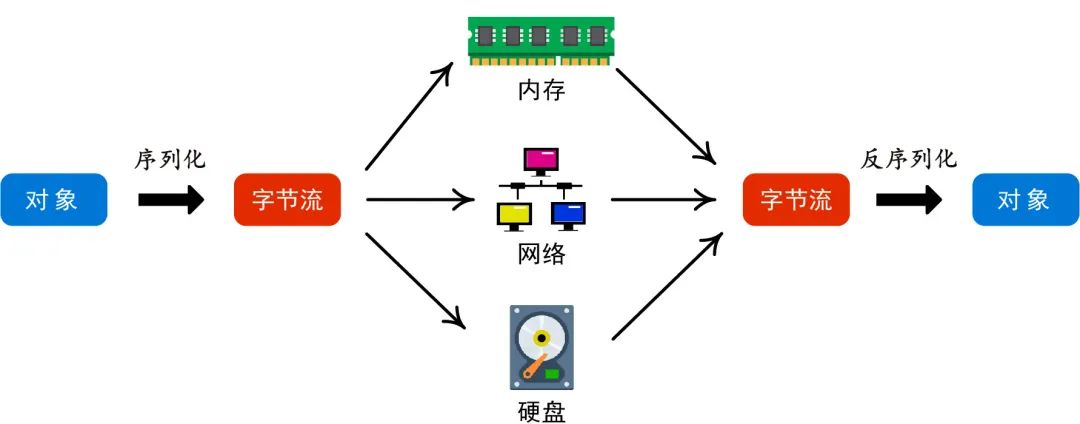

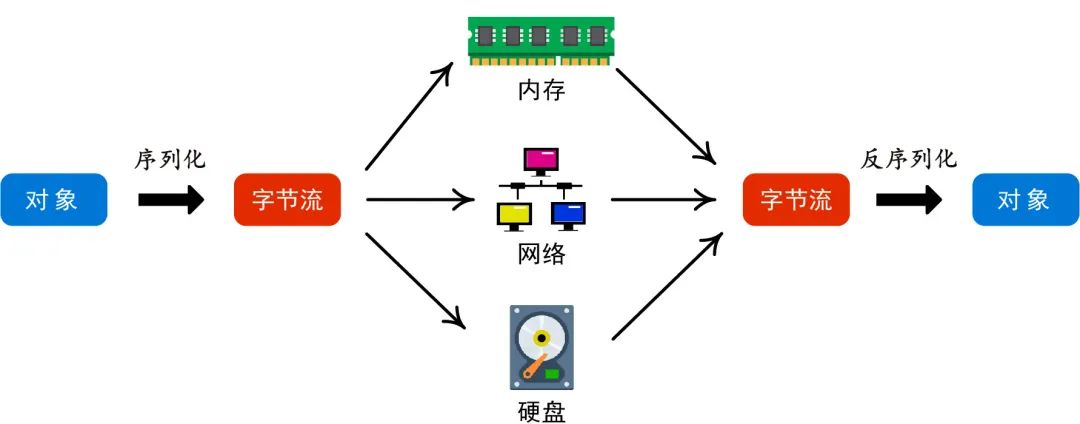

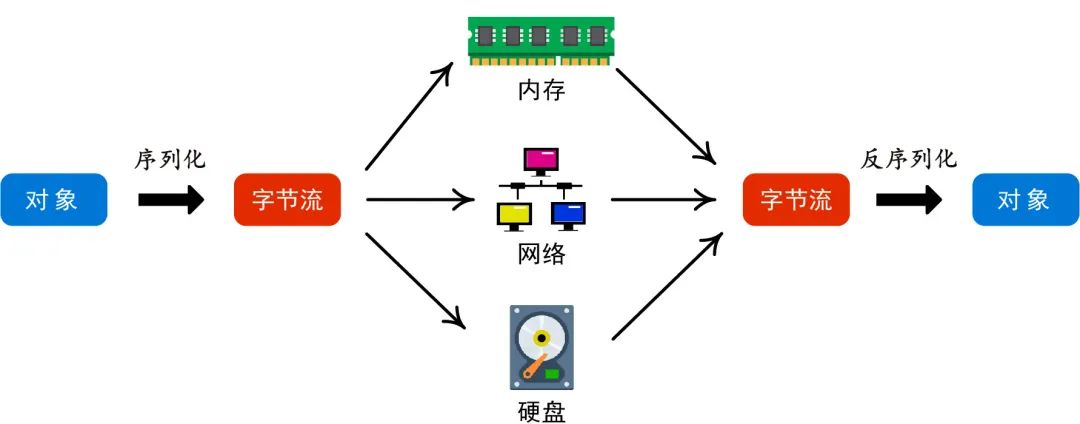

转换方式就叫做序列化。将文件或者网络传输中得到的 byte[] 数组转换为 java 对象就叫做反序列化。 怎么使用 如果一个 Java 对象要能被序列化,必须实现一个特殊

2023-10-10 14:19:25 217

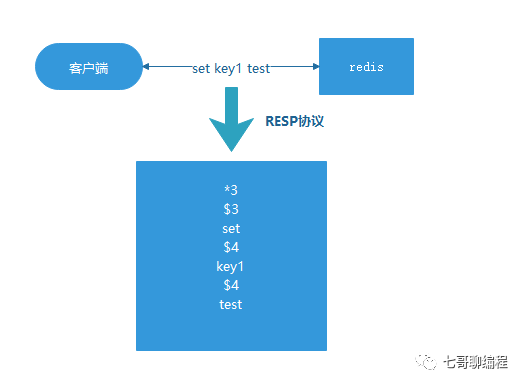

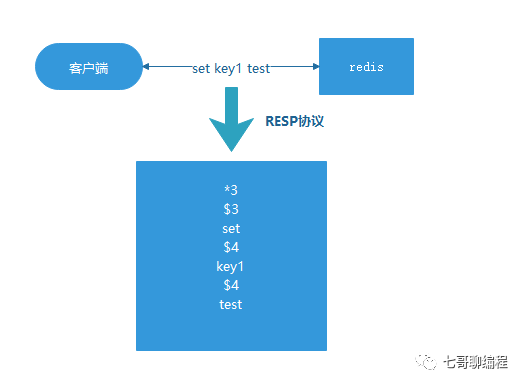

217 原理 在学习AOF原理前,我们首先要了解 RESP (Redis的序列化协议) 从图中可以看到客户端在调用redis服务端时,传入的命令和 key、value 都会通过 RESP 协议序列化为文本

2023-10-09 15:02:38 169

169

在Spring Boot Web 项目中,当使用JSON格式接收数据和返回数据的时候,Spring Boot 默认使用一个ObjectMapper实例来序列化响应和反序列化请求。 在本文中,我们

2023-10-09 10:26:57 1136

1136 json是目前最为流行的文本数据传输格式,特别是在网络通信上广泛应用,随着物联网的兴起,在嵌入式设备上,也需要开始使用json进行数据传输,那么,如何快速简洁地用C语言进行json的序列化和反序列化

2023-10-07 11:05:34 738

738 在顺序功能图中除了前面使用过的单序列和循环序列外,还有并行序列、选择序列、跳转序列和混合序列,本期主要介绍并行序列和选择序列。

2023-10-01 10:53:00 917

917

Serde 是一个用于序列化和反序列化 Rust 数据结构的库。它支持 JSON、BSON、YAML 等多种格式,并且可以自定义序列化和反序列化方式。Serde 的特点是代码简洁、易于使用、性能高效

2023-09-30 17:09:00 730

730 。Worker子线程和宿主线程之间的通信是基于消息传递的,Worker通过序列化机制与宿主线程之间相互通信,完成命令及数据交互。

5.TaskPool注意事项

● 实现任务的函数需要使用装饰器

2023-09-25 15:23:54

buffers. 它是由 Google 研发的,一种可跨语言、可跨平台、可扩展的序列化数据的机制。类似于 XML ,但是它更小、更快、更简单。你只需要定义一次你希望的数据如何被结构化,然后你可以使用它的生成工具,生成包含一些序列化和反序列化等操作的源代码。可以轻松地从各种数据流和使用各种编

2023-09-25 11:26:22 239

239 Prost是一个用于序列化和反序列化协议缓冲区数据的Rust语言库。它使用Google Protocol Buffers语言来定义协议,并生成Rust代码以便使用该协议。 Prost具有高性能的特点

2023-09-20 11:09:16 661

661 景,帮助您更好地了解这些材料的热缩性能。 热缩测试仪的工作原理是基于材料的热胀冷缩特性。当材料受热时,其分子链会运动并产生膨胀,导致尺寸增大。当材料冷却时,

2023-09-18 11:17:54

、PCB设计、到PCB制造、BOM配单、电子装联(PCBA)和测试验证等多个环节,不同的环节的特点和需求不同,对电子供应链企业有不同的要求。整体来说,电子供应链呈上游集中、下游分散、品类繁杂之态势。

机会

2023-09-15 11:37:37

很多应用场合需要检测系统时钟是否在正常范围内,以保证MCU能正常工作,CLASS B功能安全实现系统时钟自检的方法是采用两个独立时钟源交叉检查来进行测量

2023-09-14 17:30:49 945

945

理解了序列化,再回到ROS。我们发现,ROS没有采用第三方的序列化工具,而是选择自己实现,代码在roscpp_core项目下的roscpp_serialization中,见下图。这个功能涉及的代码

2023-09-14 17:26:28 557

557 什么是序列化? “序列化”(Serialization )的意思是将一个对象转化为字节流。 这里说的对象可以理解为“面向对象”里的那个对象,具体的就是存储在内存中的对象数据。 与之相反的过程是“反序列化

2023-09-14 17:22:29 1239

1239

电子发烧友网站提供《基于反序列化过采样数据的时钟和数据恢复单元.pdf》资料免费下载

2023-09-13 10:41:34 0

0 可通过option byte来选择是否使能硬件IWDG功能 更先进的安全功能 IWDG使用独立的低速时钟LSI作为时钟源并在主时钟无效时仍然保持运行 一旦使能了IWDG该功能就不能被禁止(LSI也

2023-09-13 07:46:59

耗电与频率成正比最低为1.5μA。如果有32.768kHz的振荡器连接到LSE精度可达0.5% 复位和从停止/待机模式退出后MSI将作为默认的系统时钟其建立时间的最大值为2us。 低速内部振荡器

2023-09-12 08:25:02

信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间;

2023-09-04 15:16:19 391

391

业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

530 点击上方 蓝字 关注我们 一、前言 在数字电路中,序列检测器(Sequence Detector)是指一种特殊类型的电路,用于寻找输入信号中一定模式的子序列。该模式可以是任意模式,包括重复模式、连续

2023-08-29 10:20:02 514

514

Fury 是一个基于 JIT 动态编译和零拷贝的多语言序列化框架,支持 Java/Python/Golang/JavaScript/C++ 等语言,提供全自动的对象多语言 / 跨语言序列化能力,和相比 JDK 最高 170 倍的性能。

2023-08-25 17:05:00 701

701

打印机的工作原理是打印头上安装有半导体加热组件,热打印机有选择地在热敏纸的确定位置上加热,由此就产生了相应的图形。加热是由与热敏材料相接触的打印头上的一个小电子加热器提供的。加热器排成方点或条的形式由

2023-08-25 08:02:25

,在很多应用场景中都可以用来构建序列发生器。本文将介绍使用D触发器设计序列发生器的方法和步骤。 首先,我们需要了解D触发器的基本原理和性质。D触发器是一种时序电路,它可以存储和延迟一个输入信号,并在时钟信号到来时输出

2023-08-24 15:50:17 2729

2729 建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44:55 388

388 那个有M0518系统时钟寄存器版本的初始化程序,库函数的太大了,

系统时钟实现的功能是使用外部晶振而不是内部

2023-08-22 07:00:34

50 MHz或100 MHz输入时钟

8K或64K字纠错码(ECC)RAM,具有内置自检(BIST)功能

所有终端的独立时间标签计数器,监视器终端有48位选项

简单监控终端(SMT)分别记录命令和数

2023-08-17 17:45:41

的配置篡改。

主要特性:

自由运行的12位向下计数器

如果看门狗定时器被使能,那么当向下计数器的值达到0时产生系统复位;

独立时钟源,独立看门狗定时器在主时钟故障时仍能工作;

独立看门狗

2023-08-16 08:13:59

新的体系结构功能:

·可扩展的矢量长度。

·每个车道的预测。

·集中加载和分散存储。

·容错推测性向量化。

·水平和序列化向量运算。

此版本的ARM编译器工具链允许您:

·汇编包含SVE指令的源代码

2023-08-16 06:51:27

时钟电路是一种用于产生稳定、可靠的时间基准信号的电路。它在电子系统中起着非常重要的作用,用于同步和定时系统的各种操作。时钟信号主要用于控制数据传输、指令执行、操作序列和各种时序事件。

2023-08-14 16:02:58 2004

2004 今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。

2023-07-30 10:26:02 648

648

QSpan II User 手册

2023-07-14 09:42:44 0

0 初版的代码在序列化时没有考虑到MCU小容量内存设备,需要一次性完成序列化,内存开销较大等等其他问题。

2023-07-03 09:25:40 175

175 在时序电路设计中,建立时间/保持时间可以说是出现频率最高的几个词之一了,人们对其定义已经耳熟能详,对涉及其的计算(比如检查时序是否正确,计算最大频率等)网上也有很多。

2023-06-27 15:43:55 4582

4582

如果大家看过或者实现过序列化反序列化的代码,这个问题就不难回答了,今天碰到的这个问题其实是发生在大家可能最常用的`fastjson`库里的,所以如果大家在使用这个库,请务必检查下你的代码,以免踩到此坑

2023-06-27 15:22:32 305

305 NUC100、NUC200、Nano100与NUC442/NUC472系列芯片支持的实时时钟控制器,其他系列芯片则无。

多数NuMicro™ 家族芯片的实时时钟控制器是不需要独立的电源,而是与芯片

2023-06-27 06:08:18

本文主要介绍了建立时间和保持时间。

2023-06-21 14:38:26 1079

1079

建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持时间是进行时序分析的基础。

2023-06-21 10:44:01 881

881

运算放大器建立时间是保证数据采集系统性能的关键参数。为了实现精确的数据采集,运算放大器输出必须在A/D转换器能够准确数字化数据之前建立。然而,建立时间通常不是一个容易测量的参数。

2023-06-17 10:37:54 366

366

NUC100、NUC200、Nano100与NUC442/NUC472系列芯片支持的实时时钟控制器,其他系列芯片则无。

多数NuMicro™ 家族芯片的实时时钟控制器是不需要独立的电源,而是与芯片

2023-06-15 12:41:05

上述类型的内存马在tomcat7(支持Servlet API 3.0)以后可以通过动态注册方式向中间件注入,也因其可以动态注册的特点所以可以在反序列化等可任意执行代码的漏洞点进行利用。

2023-06-05 17:29:35 534

534

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2023-06-02 14:26:23

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

参考时钟独立,参考时钟不需要穿越背板和连接器,从而使PCB设计变得更为简单,使得架构更加的灵活。

2023-05-29 12:49:49 5089

5089

众所周知,序列由几个数据项组成,它们共同构成了一个有趣的场景。序列可以是分层的,从而创建更复杂的方案。在最简单的形式中,序列应该是 uvm_sequence 基类的派生,方法是指定请求和响应项类型参数,并使用要执行的特定方案实现 body 任务。

2023-05-29 09:50:40 376

376 测试将使用此序列器来处理序列(如上一篇博客文章中所述)。在这里,我们可能不需要虚拟序列(或虚拟序列器)。

2023-05-29 09:46:18 444

444 本文介绍ROS机器人操作系统(Robot Operating System)的实现原理,从最底层分析ROS代码是如何实现的。

**1、序列化**

把通信的内容(也就是消息message)序列化是通信的基础,所以我们先研究序列化。

2023-05-19 17:42:01 803

803 本文介绍ROS机器人操作系统(Robot Operating System)的实现原理,从最底层分析ROS代码是如何实现的。

**1、序列化**

把通信的内容(也就是消息message)序列化是通信的基础,所以我们先研究序列化。

2023-05-19 17:41:47 730

730

基站的内部,都有自己独立的时钟模块:晶振(晶体振荡器),在没有外部时钟源时,就处于自由震荡状态。

可想而知,在自由震荡状态的各个基站间的时钟没有同步,每个基站都只是一个孤岛,只能独立运行无法协同

2023-05-10 17:09:50

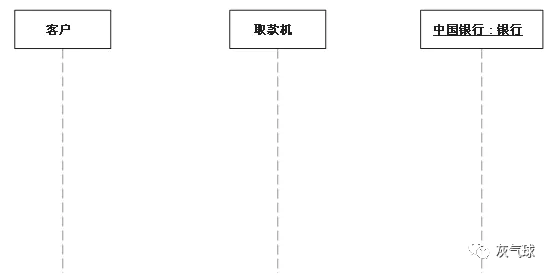

序列图将交互关系表示为一个二维图。纵向是时间轴,时间沿竖线向下延伸。横向轴代表了在协作中各独立对象的类元角色。类元角色用生命线表示。当对象存在时,角色用一条虚线表示,当对象的过程处于激活状态时,生命线是一个双道

2023-05-05 10:28:01 355

355

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用户手册

2023-04-27 20:25:40 6

6 ,给企业的利润带来了较大的压力。为应对上述问题,企业不断加强自身管理能力。

工程项目管理具备计划性、临时性、系统性、复杂性以及约束性的特点。项目物资的供应链管理贯穿工程项目始终,从项目计划伊始直至最终

2023-04-25 11:28:10

PowerSpan II User 手册

2023-04-20 18:51:26 0

0 我读到 SMP 特性:“对称内存(有一些小例外)。如果多个内核访问相同的内存地址,它们的访问将在内存总线级别序列化。通过原子比较实现对相同内存地址的真正原子访问-ISA 提供的交换指令。”那么这是否意味着我可以创建全局变量而不用担心多线程访问?

2023-04-14 08:40:57

、传感器等。 总之,配电自动化系统是一种综合的技术体系,其实现离不开监测、保护、控制、智能化集成和各种配电设备的有机组合。 配电自动化系统的特点 配电自动化系统是一种利用新兴科技独立开发并应用于

2023-04-10 17:04:59

最终启动序列错误,芯片初始化失败 Ef(34) 初始化闪存超时这些是我被卡住的错误,任何人都可以建议我解决请尽快回复我

2023-04-10 08:29:06

序列化对象:将对象转换为可以存储或传输的形式。

(1) 用于存储:将对象的字节序列存储到文件中,程序退出后不会消失,便于后续使用。

(2) 用于传输:发送方把对象转换为字节序列,接收方字节序列恢复为对象。

2023-04-06 15:08:44 465

465 会退出总线繁忙状态和失败。 出于好奇,我尝试将时钟频率配置为 400MHz 并使用分频器 2 来获得 200M 的值。 我想知道 RFDR 中的这个值表示什么以及谁负责更新? 如果我使用分频器值 3,则操作成功,RFDR[0] 值为 0x80,依此类推各种循环序列的变化。

2023-04-03 09:01:11

QSpan II User 手册

2023-03-31 19:31:54 0

0 几乎稍微复杂的数字设计都离不开时钟。时钟也是所有时序逻辑建立的基础。前面介绍建立时间和保持时间时也涉及过时钟偏移的概念。下面将总结下时钟的相关知识,以便更好的进行数字设计。

2023-03-28 13:56:41 978

978

“序列号为“AH06IOXS”的 TED-Kit 2 初始化失败。此 TED-Kit 2box 无法使用且未显示在硬件视图中。”

2023-03-24 06:24:00

分辨率吗?最大值是多少?我们的案例支持的决议?其中一个显示器将靠近电路板,另一个将相距几米。所以我们打算使用TI的序列化程序。您建议使用哪一种 i2c(用于触摸屏功能)?或者您对我们的案例有任何其他解决方案吗?

2023-03-23 07:22:41

电子发烧友App

电子发烧友App

评论