1、平台芯片STM32H7A3,外挂2片Octo-SPI SRAM作为数据缓存,操作系统threadx文件系统filex。

2、数据在ram中读写都没问题,缓存80kB以内的数据写入sd卡文件中也

2024-03-08 07:16:33

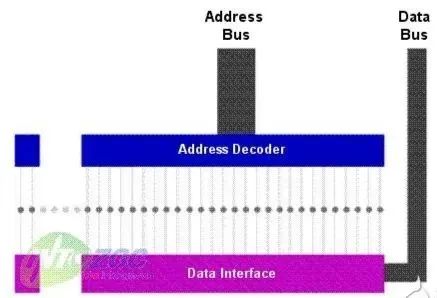

我将一个数组定义在SRAM2中,另一个数组定义在CCM中,我可以利用memcpy这个函数来将SRAM2里的数据拷贝到CCM中吗。

因为我看总线矩阵图,CCM的D-BUS和SRAM2并无交集,是不是也就意味着这两块内存互相无法进行交互呢?

2024-03-06 08:21:14

我在使用 UART FIFO 缓冲区时遇到了以下问题。

问题描述:

当通过两个 UART 通道使用完整的 UART FIFO 缓冲区并通过两个通道进行通信时,缓冲区中的数据有时会损坏,例如,UART

2024-03-06 06:59:31

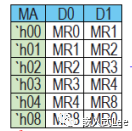

FX3自带SDK中的例程GPIF ii sram-master:读写sram指令中的地址由状态机中的地址计数器来决定,请教一下如何在FX3固件代码中指定读写sram的地址,可否提供一个例程或相关文档

2024-02-27 07:20:24

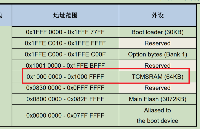

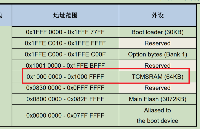

一般使用的均为通用SRAM空间,这部分SRAM使用的时候没有限制,作为堆栈、变量、DMA使用等都可以,但TCMSRAM一般不使用,有的时候可能会被大家遗忘,如果大家

2024-02-24 09:43:16 186

186

PSOC6如何把变量定义在外部串行SPI SRAM中,并且在使用时可以跟内部SRAM变量使用方法类似

2024-02-01 06:33:40

我们将 XMC4500 用于功能安全应用。 有几个用户安装了 1000 个或更多控制器。

在这些现场安装中,我们每月在 PSRAM 和/或 DSRAM 中会遇到大约 1-2 个奇偶校验错误。 错误

2024-01-26 06:30:34

我把这个函数放进了 PSRAM 地址,我检查了地图,它起作用了。

但是十六进制文件不包括 PSRAM地址。

我怎样才能配置 lsl 或工具来获取 HEX 文件中的 PSRAM 地址?

2024-01-22 06:05:00

可以使用 DMA 进行自动缓冲区管理,从而启用直通模式。 有人估计过使用BULK端点可以给我的最大数据速率吗? 我不能使用等时端点,因为已经定义了 OpenJTAG 接口。

有人有通过 psoc5LP

2024-01-19 08:19:10

您能告诉我 PSoC™ 4中SRAM阵列的数据保持电压吗?

我想知道在 VDD 电源电压下降或上升时 SRAM 可以保留数据的最小电压。

MPN: PSoC™ 4100S Max/CY8C4148AZI-S555

2024-01-19 06:08:12

ADUC360 I2Cmaster.c中 master handler 与实际传送的数据什么关系,需要传送的数据是要放在数组里吗?

2024-01-15 08:26:01

。 SDRAM是一种集成电路存储器,可以通过同步钟信号进行数据读写。与传统的静态随机存储器(SRAM)相比,SDRAM具有更高的存储密度和更低的成本。扩展SDRAM接口使得微控制器能够使用外部

2024-01-04 14:09:23 339

339 已用这种模式成功驱动了一些psram,但是SRAM始终驱动不了。

SRAM驱动架构

XMC复用模式读时序,其中一个HCLK=4.16ns(240Mhz)

SRAM读时序参数

SRAM读时序图

XMC

2024-01-04 10:46:19

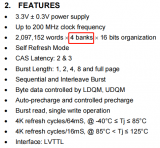

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 xRMS最大值为 52,702,092)。

但波形缓冲器(Waveform buffer)以 固定数据速率波形(SINC4或LPF) 读取的数据是24位ADC数据,但我按照24位最大值0xFFFFFF

2023-12-25 07:21:24

请教一下DAC的问题。MCU向DAC的DIN引脚输入数据后,DAC转换到我们所希望的电压值,DAC中锁存器的作用是不是说当完成一次DAC转换后,如果不再向DIN引脚中输入数据,那么DAC的电压输出会

2023-12-19 08:13:51

,从基本原理到电路设计的细节。 SRAM是一种基于存储双稳态的存储器技术,它使用触发器来存储数据。一个典型的SRAM单元由6个传输门(传递门)组成,其中包括两个传输门用于存储和读取数据,以及两个传输门用于写入和刷新数据。 SRAM的读取操作是通过将地址输入到SRAM中来完成的。当地址输入到

2023-12-18 11:22:39 496

496 1:请问下BF592 用于做音频处理RAM不够用可以外挂SDRAM或者SRAM吗?如果可以有没有相关的原理图和软件下载?

2:592是定点DSP,那对音频采样数据存储时要定义成float类型好呢

2023-11-30 07:20:36

电子发烧友网站提供《参数在数据转换器中的应用.pdf》资料免费下载

2023-11-27 11:46:03 0

0 中心的基建和运维中具有无可替代的重要意义。 首先,预端接光缆系统能够大大提高工程的安装效率。在数据中心中,需要大量的光纤跳线来实现设备的连接,而预端接光缆系统可以提前将光纤跳线做好,到现场直接安装,无需现场

2023-11-10 09:47:31 160

160 单片机可以替代PLC吗?

2023-11-01 06:54:57

串口接收的数据 存在数组里 采取覆盖的方式 第二次接收的时候要是还没接收完就处理主函数的东西 不是会产生错误 这种情况应该怎么办呢

2023-10-27 07:53:23

AT32F系列 I2S DMA双缓冲替代实现方法演示AT32F系列I2S使用DMA半传输及传输完成中断来达到DMA双缓冲存储接收数据的方法。

2023-10-27 06:21:27

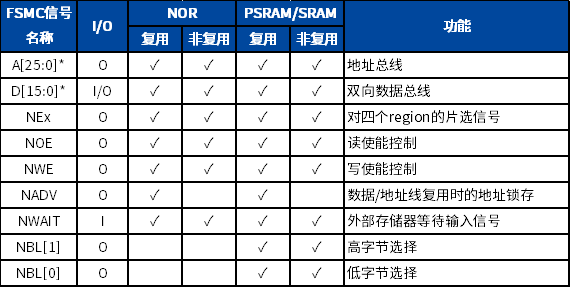

PSRAM/SRAM与XMC硬件连接的推荐方法描述了在AT32系列100引脚封装芯片上以XMC连接PSRAM的硬件推荐方法,达到器件容易取得及价格合理的目标。

2023-10-24 06:17:32

电感的兼容替代在近几年的确是一个讨论度比较高的问题,关于不同品牌电感替代的案例谷景也分享了很多。本篇我们我们探讨另外一个关于电感替代的问题——同样0805贴片电感封装尺寸的是否可以直接替代

2023-10-23 14:40:47 314

314 AT32 部分型号有零等待闪存和非零等待闪存,程序在零等待闪存执行速度比在非零等待闪存执行速度快,如果有函数对执行速度有要求,可以将该函数加载到零等待区执行。当零等待闪存使用完后,如果还有函数对执行速度有要求,可以将该函数加载到 SRAM 执行,前提是SRAM 还有足够的空间存放该函数代码。

2023-10-20 06:10:59

掉电后还能读取到SRAM的数据吗

2023-10-15 09:24:03

STM8可以实现从SRAM启动程序吗

2023-10-09 07:38:29

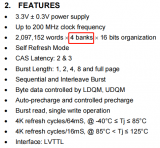

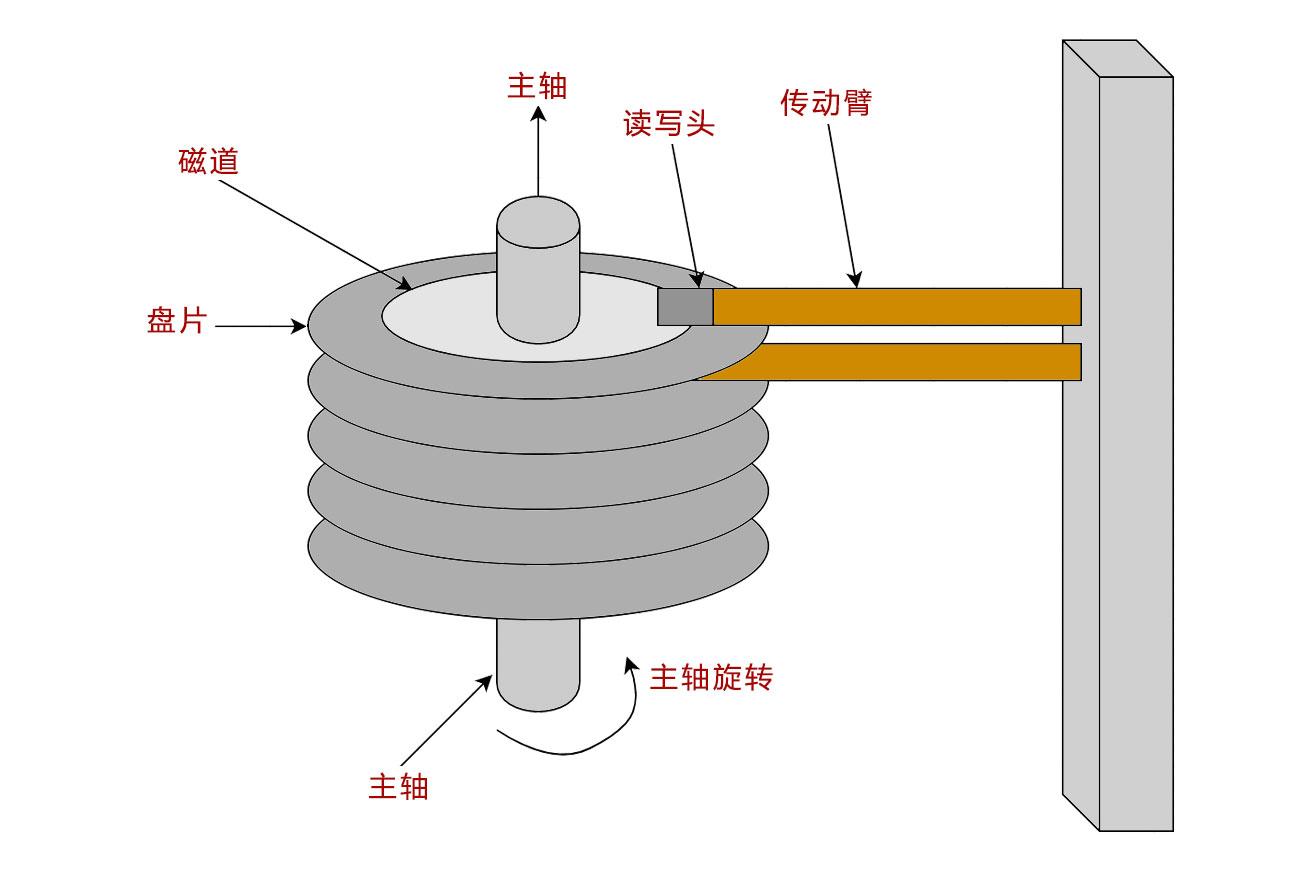

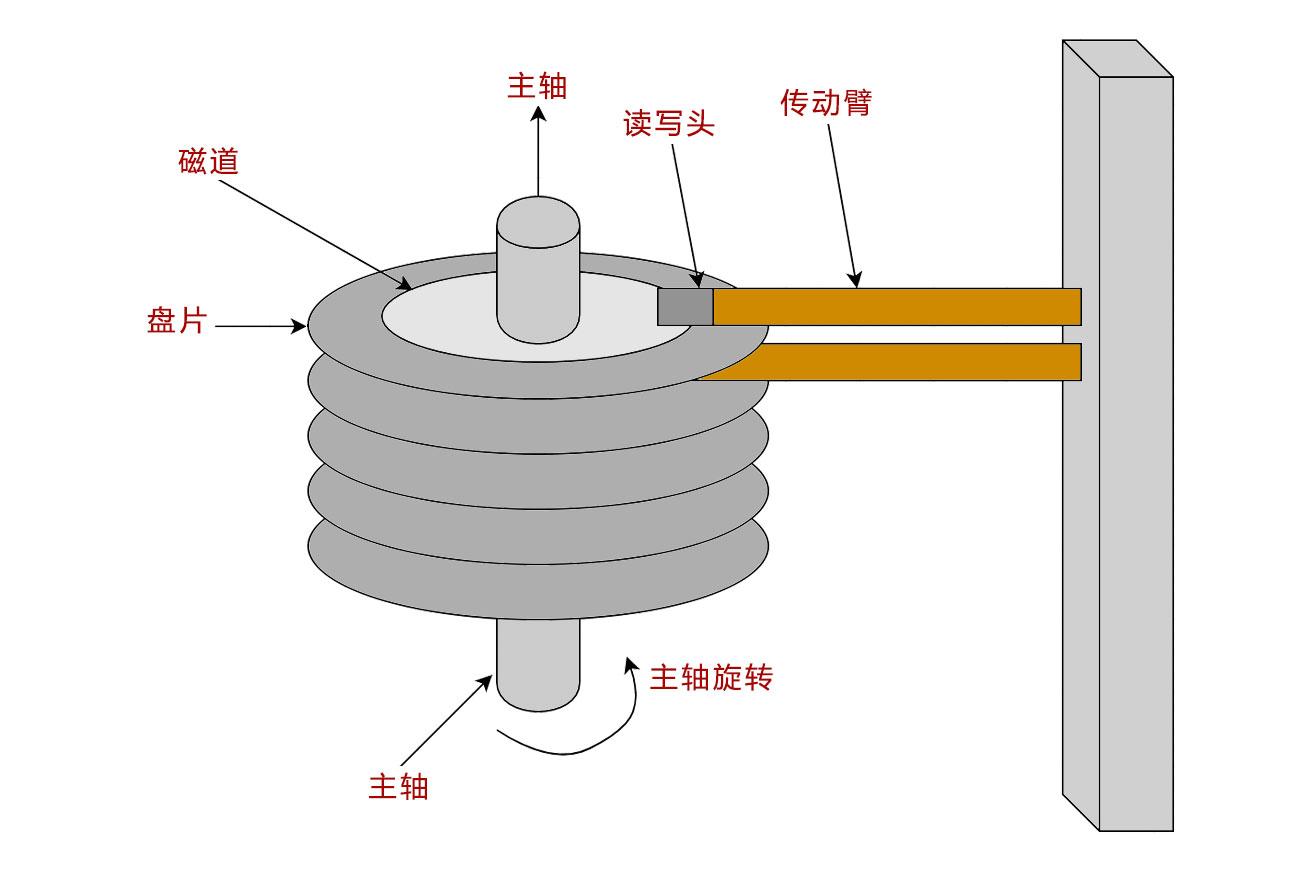

SDRAM的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

2023-09-28 17:26:29 637

637

FSMC外扩SRAM数据之间是怎么传送的?先保存在FSMC再传送外扩SRAM

2023-09-27 06:03:22

使用MM32F3270 FSMC驱动SRAM

2023-09-18 16:29:50 918

918

内部闪存高达2MB

•高达512KB的内部SRAM

•用于帧缓冲的外部存储器

•16位或32位SDRAM/SRAM

•封装:LQFP 144引脚,最高可达208。

2023-09-11 08:09:15

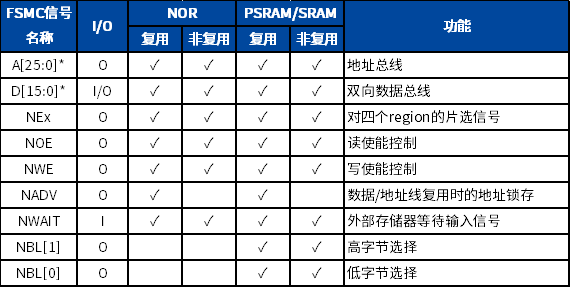

频率可达216MHz/2(fCLK = HCLK /2)• 支持的存储器类型• 静态存储支持• SRAM• PSRAM• NOR/ONENAND• ROM• LCD接口• 支持8080和6800模式

2023-09-11 06:58:26

应用程序: 此示例代码使用 M032 在 SRAM 中运行 ISR 。

BSP 版本: M031_Series_BSP_CMSIS_V3.03.000

硬件: NuMaker-M032SE

2023-08-31 09:21:19

应用程序:本示例代码演示如何使用Nanopb在M252中执行协议缓冲。 Nanopb是ANSI-C执行Google协议缓冲数据格式。

BSP 版本:M251/M252/M254/M254/M256

2023-08-29 06:07:42

QSPI0可以映射到512Mb(0x2000_0000开始)地址空间直接访问,其他QSPI是怎样映射的?不是很清楚8M的psram对应的地址空间是什么

2023-08-16 06:43:18

SDRAM全称Synchronous Dynamic RAM,同步动态随机存储器。首先,它是RAM,即随机存储器的一种。

2023-08-08 15:10:46 896

896

电子发烧友网站提供《STM32U5 HexaSPI总线到PSRAM的PCB布线规则.pdf》资料免费下载

2023-08-01 09:06:33 0

0 IP_数据表(M-1):SRAM and TCAM

2023-07-06 20:12:09 0

0 我咨询下 用N3290X 只在外围挂一颗SPI flash (比如16M)可以将画面 在下载时 直接下载到SPI flash 中(比如通过串口)还是需要先通过下载器将画面下载到SPI flash 中?在运行时 可否直接将SPI flash 中画面数据拷贝到内部sdram中 ?

2023-06-27 06:30:13

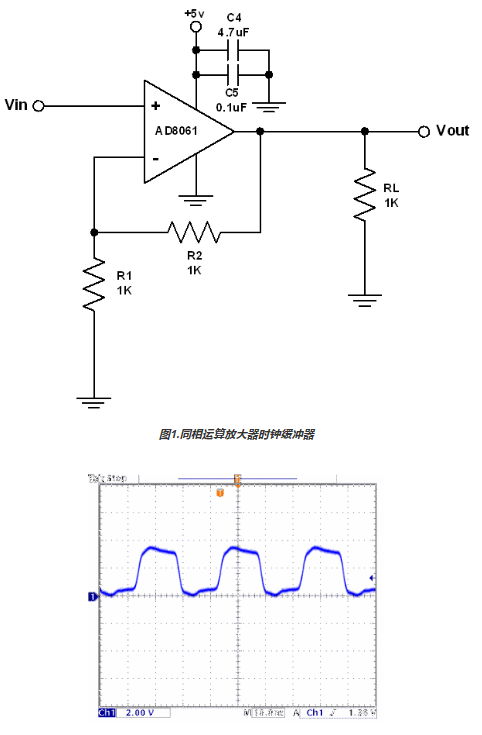

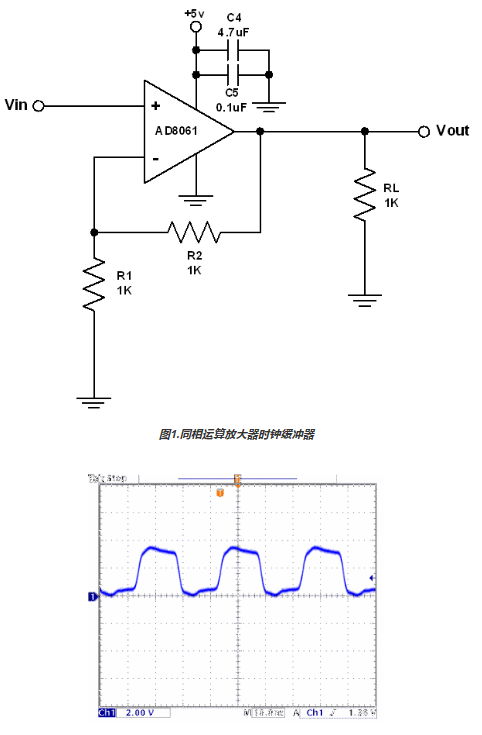

在消费电子应用中,与典型的时钟缓冲应用相比,其频率往往较低,要求也更低,廉价的高速运算放大器(~100 MHz带宽)可以为传统时钟缓冲器提供有吸引力的替代方案。高速放大器可能比传统时钟缓冲器便宜,但它们可以适应各种设计配置。

2023-06-17 17:29:14 704

704

我们正在破坏 RT1170 evkit 上的一些性能测试,我们正在使用 dev_msc_ramdisk_bm_cm7 示例。由于存储缓冲区受内部 DTCM 大小的限制,我们希望将其移动到外部 SDRAM 上。我们找不到一种简单的方法来做到这一点。任何人都可以帮助我们吗?

2023-06-12 07:51:04

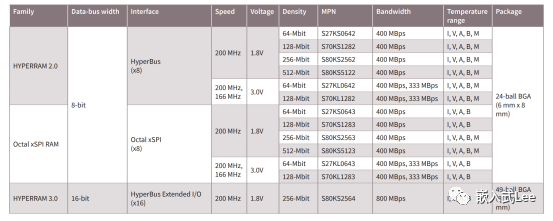

PSRAM的时序比较简单,主要根据各个时序图理解每个时序阶段,及其参数。重点要理解DQS/DM是谁驱动的,代表什么意思, 数据采样的时间即DQS上升沿延迟数据建立时间之后采样。

2023-06-08 11:30:55 19837

19837

以上分享了PSRAM接口一些关键的知识点,大部分是容易理解错误,且导致问题的点,基本上理解这些点就能解决大部分问题了,作为入门参考也可以先看这篇,先有个大概了解。作为遇到问题不知如何解决时也可以参考这篇文章,基本上能解决大部分问题。

2023-06-08 11:25:04 3795

3795

我正在尝试使用 RT1176 为我的 SDRAM 组配置 SEMC 的参数。

在各种参数中,EVB 设置值

“ sdramconfig.tPrescalePeriod_Ns ”为“160

2023-06-05 10:31:50

************************************************* *************************************

* 详细说明:

* 这个例子的目的是展示如何保存数据在 SRAM 存储器中通过

2023-06-05 09:47:48

我正在尝试使用 MCUXpresso 配置工具版本 13.1 为 SRAM 配置 RT1172 SEMC。

我只将 SDRAM 视为一个选项:

在此处的类似帖子中有回复 (2022-08-30),这将在下一版本中通过“模式”设置提供:

是否有关于此功能可用性的状态更新?

2023-06-02 08:28:39

GRANDMICRO有容微在数据中心方案应用

2023-05-30 14:11:05 414

414 我正在寻找有关如何配置 FlexIO 以模拟 RT1176 和 FPGA 之间的 SRAM 接口的示例。我有一个 16 位并行数据总线,用于读取和写入 FPGA 上的内存映射寄存器。我有 CLK

2023-05-29 07:41:53

=debug_flash_sdram_xip,则每次烧写到NOR FLASH 太慢,等待消耗太长时间。

2)如果使用 -DCMAKE_BUILD_TYPE=debug,则镜像写到 ILM中,但又受限与 ILM的大小。

因此手撸了一个

2023-05-26 07:39:23

现在,我正在使用带有 SDRAM 的 imxrt1052。所有变量都在 SDRAM 中。但我想要 SRAM 中的一些变量,以及 SDRAM 中的其他变量。怎么做 ?

2023-05-12 08:23:11

到了FSMC的NE3端口,地址为19位,数据为16位,设置一下cubemx,时序配置为0;4;0

生成代码,我这里是用的Makefile

把显存放在SRAM中,代码如下

static uint16_t

2023-05-08 20:01:14

.icf

2) flexspi_nor_sdram.icf

使用 sdram.icf,代码可以正常工作,但它是从 RAM 内存中执行的,因此在按下复位后它无法保留代码。而

2023-05-05 06:38:08

本公司目前MCU系列,到目前为止, SWM34x 支持外接8M16M SDRAM,SWD34S系列已经把SDRAM合封入芯片,合封的SDRAM大小根据芯片型号不同,具体见官方手册。

2023-04-28 09:30:22 1496

1496

使用 MIMXRT1024CAG4B 并计划在我们的设计中连接一个 8 位 SDRAM ( IS42S86400F-7TLI )。我可以从 A0 配置 8 位 SDRAM 的地址引脚吗?或者在配置这些地址引脚时是否有任何特定的限制?

2023-04-28 08:58:11

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用户手册

2023-04-27 20:25:40 6

6 极高的运动定位精度和稳定性,在数据存储中具有着非常广泛的应用。在数据存储的领域,通常需要压电纳米定位台来实现纳米甚至亚纳米级别的运动控制精度。 压电纳米定位台用于读写头的高精度调节 压电纳米定位台可以在光盘数据存储

2023-04-26 16:23:02 431

431

我正在使用 S32k358 uC,我想禁用内存区域的数据缓存。在框图中,我看到树形 SRAM 块 SRAM0、SRAM1、SRAM2。是否可以禁用 SRAM2 的数据缓存并保留 SRAM 0 和 SRAM1 的数据缓存?

2023-04-23 08:01:09

。Bank1只能通过片选信号NE1以复用模式支持NOR/PSRAM 存储器。Bank2只能通过片选信号NE2支持16位或8位NAND Flash。SPI2和SPI3接口可以在SPI模式和I2S音频模式

2023-04-19 21:13:57

的 ITCM 和 DTCM)。我们的问题是:1- 没有 SDRAM,我们是否可以增加 CM4 的代码和数据空间?如果可以的话,CM7如何加载大于256KB的代码到0x20200000呢?请指出

2023-04-19 07:17:13

SEMC接口支持4种设备,我想确认以下问题:1、是否支持在同一个工程中通过SEMC接口访问两个不同的设备,比如外接SDRAM插件,外接SRAM,同一个工程中需要与两个外设进行数据交互。2、如果支持,两个设备切换时延迟多少?

2023-04-17 08:23:31

SEMC接口支持4种设备,我想确认以下问题:1、是否支持在同一个工程中通过SEMC接口访问两个不同的设备,比如外接SDRAM插件,外接SRAM,同一个工程中需要与两个外设进行数据交互。2、如果支持,两个设备切换时延迟多少?

2023-04-17 06:51:39

我正在使用带有为 MCUXpresso IDE 生成的 SDK 的 FRDM-K66F 板。我看到当我生成 SDK 时,CMSIS DSP 库的包含版本是 V1.4.5 b。在 SDK 构建过程中如何将其更新到最新版本或选择替代版本?

2023-04-14 07:10:52

我有一些 AiThinker Esp32cam 在这里工作。如果将它们与开发板连接到arduino 控制台中的 USB,则会出现此错误:E (60) psram:PSRAM ID 读取错误

2023-04-12 06:33:56

在FPGA中,FIFO一般是使用RAM存储器作为缓冲区,可以分为同步FIFO或异步FIO,一般用于数据缓冲,或者不同时钟域之间的数据传递。

2023-04-10 09:30:10 539

539 SRAM可以分为低速、中速、高速。===========================================================16位宽的SRAM//16BITSRAM指针

2023-04-06 15:13:03 554

554

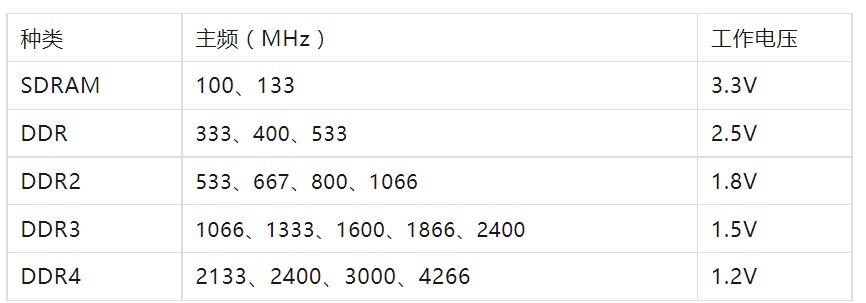

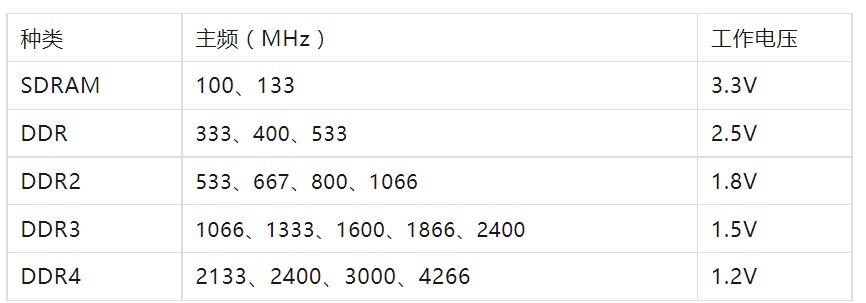

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

AVTP 时间同步/非时间同步控制格式。打包为 ACF CAN Brief /Full 消息)或打包成UDP 数据包. • LLCE 打包消息并将其放在SRAM 的缓冲区中。数据包长度由缓冲区大小的配置

2023-04-03 08:48:58

今天就带你详细了解一下到底什么是SRAM,在了解SRAM之前,有必要先说明一下RAM:RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。

2023-03-30 14:11:51 587

587

SDRAM SLICE CARD

2023-03-30 12:05:53

RMII,这也可以让我们更有效地进行一些屏蔽/同步字检测。我对物理层之上的以太网非常不熟悉,我不确定在场景 1 中我们是否可以充分禁用 MAC 的功能,使 FIFO 数据与传输到 PHY 或从 PHY 接收

2023-03-30 08:36:13

我正在寻找一些与 IMXRT1064 的外部 SRAM 使用相关的信息。例如,EVK 有 256Mbit 166MHz SDRAM。166MHz与使用过的SDRAM有关。我试图找到 SEMC 控制器

2023-03-30 07:11:18

嗨恩智浦专家,我知道 MIMXRT1xxx 能够在 ITCM 中运行 hello_world 但是 MIMXRT595 中没有 ITCM 只有 SRAM。MIMXRT595-EVK是否可以在SRAM中运行hello_world zephyr示例?

2023-03-30 06:38:30

ESP-12K-PSRAM-IPEX

2023-03-29 16:27:53

;=32,改变这个地址的数据也会改变这个地址的数据-32。这导致我写的所有错误数据。我检查了我的 EMC 配置、数据宽度、时序,尝试关闭缓冲区,但没有解决问题。我在想的是,如果我的EMC配置错误,那么一开始直接

2023-03-28 08:13:08

我无法使用 SDRAM 启动代码。我正在使用 lwip_dhcp_freertos_cm7 示例。以下是我的设置:单片机设置单片机设置预处理器设置:预处理器设置链接器设置链接器设置但是,代码启动正常

2023-03-28 07:26:51

工程代码可以登录叁芯智能科技官方技术论坛下载。 在一些工程设计中,SDR SDRAM作为中间数据缓存器,往往需要接收上游传输过来的数据,并且还要输出下游所需的数据。为了能够解决下上游传输数据的需要

2023-03-27 17:09:14

将 u-boot 代码复制到 SRAM。但我知道我必须在链接器中启用 __RAM_INIT 标志才能初始化 ECC。如果不是,则在我将u-boot代码复制到SRAM时出现异常。那是正常症状吗?3) 启动时

2023-03-27 09:15:16

到此FIFO中,然后写入到SDRAM中。输出缓冲器为一个FIFO,SDRAM的数据输入到此FIFO中,然后被VGA模块读出输出给VGA接口。SDR SDRAM驱动为控制接口模块,完成对SDRAM的写入

2023-03-24 19:29:11

控制器的系统时钟频率相同,并且内部命令的发送与数据传输都是以该时钟为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失。

SDR SDRAM中的SDR是指单数据速率,即每一根数据线上,每个时钟只传输

2023-03-23 17:40:58

电子发烧友App

电子发烧友App

评论