DDR应用的一般注意要点

上周的文章我们介绍了应用 DDR 时需要先从电源、时钟两个方面必须遵循的固定法则,以保证存储的正常使用。本次文章,我们主要围绕DDR的PCB设计保证DDR的正常使用来展开描述。首先从DDR的相对摆放位置做介绍,即根据使用的DDR个数和类型以及实际布板格局做拓扑选择。拓扑结构的选择主要还是看其芯片的时序要求。目前常见的有以下几种拓扑:一对一拓扑、菊花链拓扑(改进类型为Fly-by拓扑结构)、星型拓扑(部分改动后也叫T型拓扑)。

我们首先来一个一个看看这些拓扑的应用特点。一对一拓扑是比较简单的Driver to Rceiver,结构简单,整个网络的阻抗特性容易控制,时序关系也容易控制,常见于高速双向传输信号线,常在源端加串行匹配电阻来防止源端的二次反射。接下来所有的拓扑都是一对多的拓扑结构,需要分门别类进行介绍。

星型拓扑

星型拓扑是多负载时常用的拓扑结构,驱动器位于星形的中央,呈辐射状与多个负载相连,星型拓扑可以有效避免信号在多个负载上的不同步问题,可以让负载上收到的信号完全同步。

但这种拓扑的问题在于需要对每个支路分别端接,使用器件多,而且驱动器的负载大,必须驱动器有相应的驱动能力才能使用星形拓扑,如果驱动能力不够,需要加缓冲器。 相对来说,星型拓扑只能用在相对低速信号上,而且是在各接收芯片需要同步接收的情况,只有在非常严格的时序要求下会采用星形拓扑,其中重要的原因是布局布线实现起来比较困难。

T型拓扑

T型拓扑结构是树型拓扑,又叫对称型的远端簇型拓扑结构、等臂分支拓扑。实际上是星型拓扑的一个改进,它将星型拓扑中位于Driver端的分支节点移动到与Receivers最近的远端,既满足了各个接收器上接收信号的同步问题,又解决了阻抗匹配复杂和驱动器负载重的问题,因为远端簇形拓扑只需要在分支节点处终端匹配就可以了。

远端簇型拓扑要求各个接收器到分支点的距离要尽量近,分支线长了会严重影响信号的质量,如果各个接收器芯片在空间上不能摆放在一起,那么就不能采用远端簇型拓扑即T型拓扑。

T型拓扑结构各个分支的端接负载和走线长度要尽量保持一直,如此才能更好的保证每个分支的接收端负载接收到的信号尽量同步,并且,每个分支电路中都需要有端接电阻,通过端接电阻与走线的特性阻抗更好的匹配来减小信号反射干扰的问题;T型拓扑结构可以让时钟、地址、控制等信号得到更好的同步效果。

布线布局时,T型拓扑结构要求从驱动端Driver到交叉T点的PCB布线长度要远远大于交叉T点到各个接收端Receiver的PCB布线长度,同时交叉T点到各个接收端Receiver的距离要尽量等长,信号匹配设计可以做在交叉T点处。如果是一拖二的,可以把两片芯片贴在PCB的正反两面,对贴减小分叉的长度。

菊花链拓扑

菊花链是把所有的负载串起来,没有等长要求,菊花链一般适用较低速的信号,它比星型在布局布线上更容易实现,所以是最常见的一种拓扑结构。

但随着芯片制造技术的更替,就是低速驱动器的上升沿也随着变陡,这使得低速不低频,更多的高频分量使反射也变成低速信号要考虑的问题了,尤其是多负载菊花链的多重反射,所以菊花链的信号完整性问题比星形拓扑负载复杂多了。菊花链最差波型总是出现在第一个接收器,因为后面每个阻抗不连续点的反射都会影响这里。

fly-by拓扑

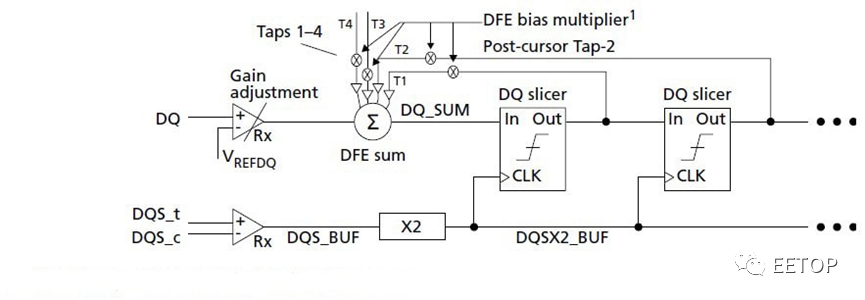

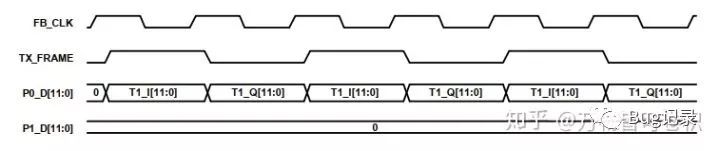

相比T拓扑,fly-by拓扑在传输较高速率信号时更占优势一些,但是使用fly-by拓扑,负载之间有延时差,导致信号不能同时到达接收端。为解决这个问题,DDR3引入了read and write leveling。也就是,只有在主控芯片有读写平衡功能,也就是有Write Leveling,Read Leveling功能,才能采用这个拓扑结构。

此外,fly-by由于分支结构的存在,通道本身就存在一些缺点。例如:通道阻抗不连续;容性突变对时序的影响等等。信号通道中只要有分叉就会存在阻抗的不连续,fly-by结构处处是分叉,阻抗不连续问题就很突出。至于为什么要在最后一级增加端接电阻,是因为从Driver到最后一颗DDR的电流是这一串所有DDR当中最大的;根据△I=△Q/△T的原理,电流加大了, △T减小了,故在一定程度上补偿了因线长导致的延时问题。

以上就是本次介绍的所有拓扑结构。那么,根据所使用的DDR,如何选择拓扑呢?

我们先看一个结论:(1)当信号速率比较高时,使用T型拓扑结构信号明显比使用FLY-BY拓扑结构的信号质量差。(2)当颗粒较多时,不论是采用T型拓扑结构还是FLY-BY的拓扑结构,容性负载补偿对信号有明显的改善。又根据DDR、DDR1、DDR2、DDR3、DDR4的特性以及对应的Driver的特点、板层的规划,有以下结论:

一般而言,DDR1/2采用星型结构,DDR3采用菊花链结构【不是所有的DDR3都可以用Fly by结构,如果主控芯片不支持读写平衡(Read and WriteLeveling)功能,则不能使用Fly by拓扑结构】。Fly by结构的DQS和CK不等长,没有write leveling就没法调整DQS和CK之间的偏斜。拓扑结构只影响地址线的走线方式,不影响数据线。星型拓扑就是地址线走到两片DDR中间再向两片DDR分别走线,菊花链就是用地址线把两片DDR“串起来”。

DDR2是采用T形拓扑结构,是因为时序要求信号要同时到达。那DDR3采用的Fly by结构,其实就是stub较短的菊花链,之所以采用此种结构是因为DDR3多了读写平衡的新技能,即使你们不同时到达,也能把它调过来。所以采用何种拓扑结构首先要看时序要求。选定了拓扑结构,在布局时元器件的摆放,有以下几个原则需要遵守:

一,考虑拓扑结构,查看Driver地址线的位置,使得地址线有利于相应的拓扑结构;

二,地址线上的匹配电阻靠近Driver(发送端);

三,数据线上的匹配电阻靠近DDR;

四,将DDR芯片摆放并旋转,使得DDR数据线尽量短,DDR芯片的数据引脚靠近Driver;

五,如果有VTT端接电阻,将其摆放在地址线可以走到的最远的位置。一般来说,DDR2不需要VTT端接电阻,只有少数Driver需要;DDR3都需要VTT端接电阻。

六,DDR芯片的去耦电容放在靠近DDR芯片相应的引脚。

然后是处理端接问题,DDR常用的端接技术有两种,分别如下:

串行端接,主要应用在负载DDR颗粒不大于4个的情况下。对于双向I/O信号来说,例如DQ,串行端接电阻Rs放置在走线的中间,用来抑制振铃,过冲和下冲。对于单向的信号来说,例如地址线,控制线,串行端接电阻放置在走线中间或者是信号的发送端,推荐放置在信号的发送端。

并行端接,主要应用在负载SDRAM器件大于4个,走线长度》2inch,或者通过仿真验证需要并行端接的情况下。并行端接电阻Rt取值大约为2Rs,Rs的取值范围是10~33ohm,故Rt的取值范围为22~66ohm。并行端接电压为VTT。

对于没有ODT功能的DDR,所有的数据线,地址,命令,控制线都需要使用single-ended Parallel Termination端接。

以上就是应用DDR时布局和端接的一些介绍总结。除了技术人员的处理之外,选择合适的或者有过批量生产的DDR型号也不错。在工业级应用当中, Alliance 公司的 DRAM 产品具有工业级的品质,抗干扰性强,则需要很强的稳定性,具有从16M、64M、128M、256M、512M到1G的完整的DRAM生产线。这些存储器被使用于主流的数字信号处理器(DSP)和微控制器,主要发现在数字消费电子、网络、移动通信、工业、医疗和汽车电子市场。

fqj

电子发烧友App

电子发烧友App

评论