高速ADDA模块开箱,FPGA专用,高速信号输出,数模信号转换,8Bit高速低功耗DA转换,DA速率高达125MSPS,10BitAD转换,AD速率35MSPS,模块含SPI串口屏幕显示、PMOD扩展口,同时支持高速ADDA转换,可搭配盘古22K、盘古50K开发板使用

2024-03-13 18:25:46

元件引脚和电路板上的焊盘之间的间隙,使元件与电路板连接起来。

5、热风刀

在焊接之后,用热风刀将多余的焊锡吹走,使焊接点更加光滑、均匀。

6、冷却

将焊接后的PCB冷却到室温,以固化焊接点,确保其强度

2024-03-05 17:57:17

你好,

什么是 5 V / 3.3 V 可切换焊盘?

这些端口在AURIX™ MCU 中吗?

2024-03-05 07:54:27

请问CY7C65621封装的焊盘如何接,多谢!

2024-02-28 07:10:51

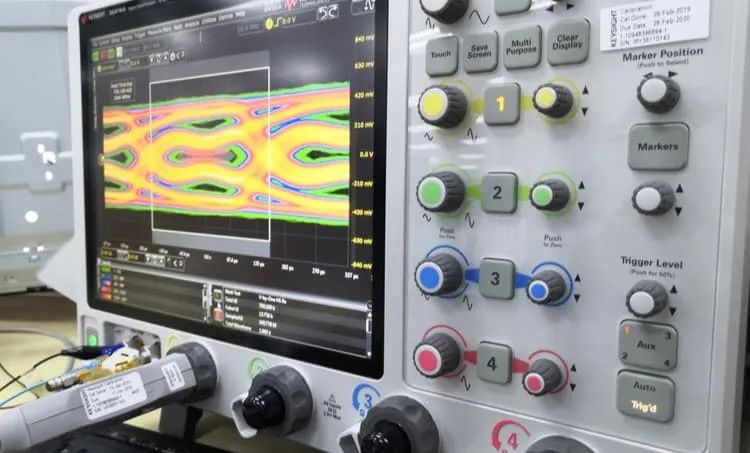

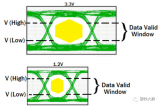

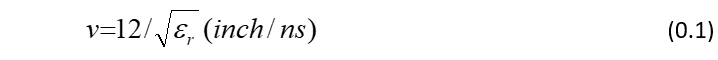

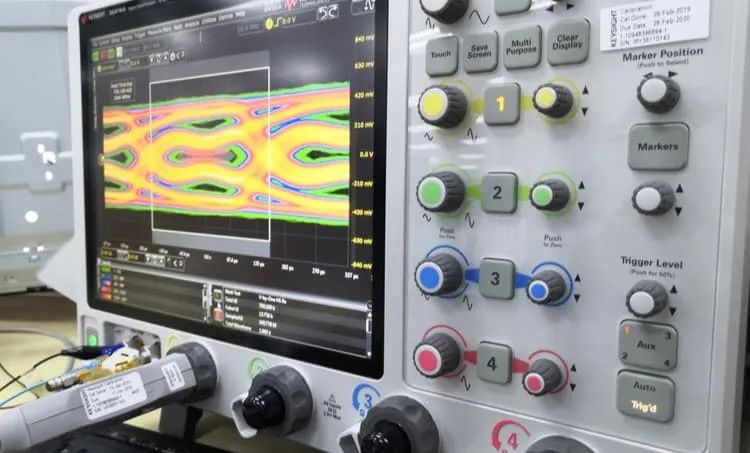

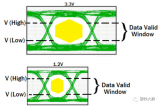

高速信号眼图测试的基本原理 高速信号眼图测试是一种用于衡量和分析高速数字信号的测试方法。在电子通信领域,高速信号是指传输速率较快的数字信号,例如10 Gbps或更高的速率。 高速信号眼图测试

2024-02-01 16:19:49 140

140 正如标题所说,CY8C4025AZI-S413的推荐焊盘模式是什么?

该设备的软件包名称为 PG-TQFP48-800,但 软件包页面 没有关于推荐的着陆模式的信息。

2024-01-31 07:13:49

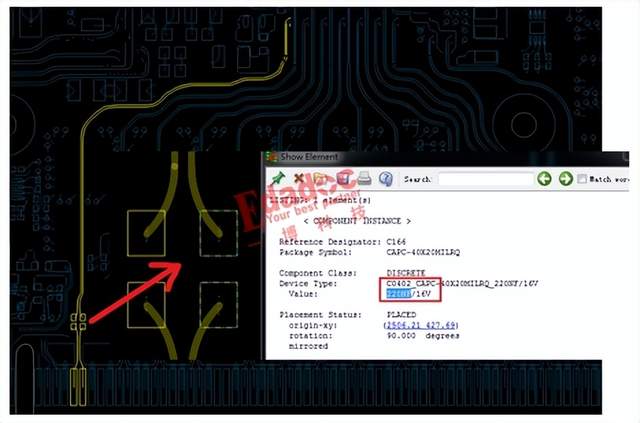

PADS DRC报焊盘之间距离过小,焊盘间距为7,但是规则的安全间距为5

2024-01-25 13:50:38

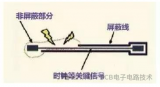

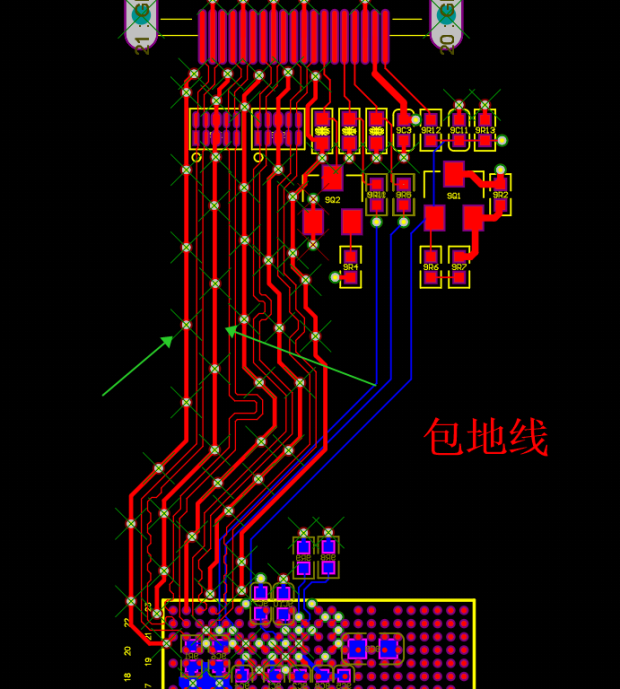

在高速的 PCB 设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成 EMI 的泄漏。

2024-01-10 16:03:05 369

369

1.ADE7858A裸露焊盘exposed pad应不应该接AGND?(英文手册说一定要接AGND,中文手册说不要有任何电气的连接那只是加强机械强度和散热的?)

2.ADE7858A采用的晶振一定

2023-12-26 06:50:08

。

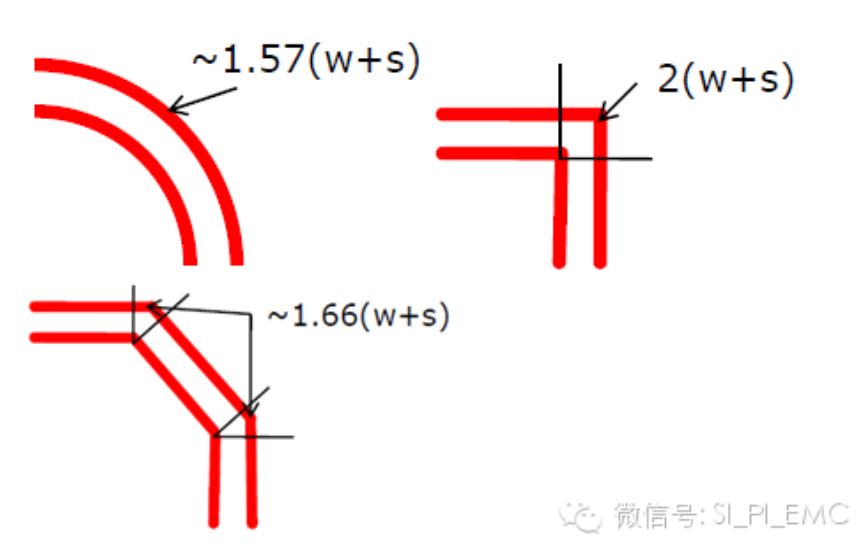

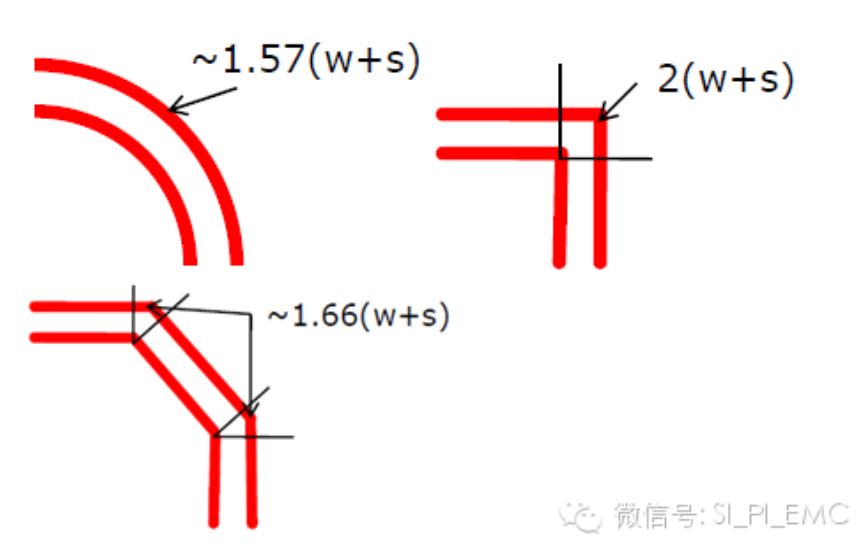

布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。

布线避免直角或者锐角布线,导致转角位置线宽变化,阻抗变化,造成信号反射,如下图所示。

布线应从焊盘的长方向出线,避免从宽方向或者

2023-12-25 11:58:53

。

布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。

布线避免直角或者锐角布线,导致转角位置线宽变化,阻抗变化,造成信号反射,如下图所示。

布线应从焊盘的长方向出线,避免从宽方向或者

2023-12-25 11:56:32

在高速信号传输中,信号传输线上的反射是一个重要的问题。当信号从信号源发送到终端设备时,信号在传输线上会遇到线路特性不连续的变化,如端口、接口或连接器的变化。这种变化导致信号的部分能量被反射回传输线

2023-12-23 08:12:29 464

464

需要选择一款带宽在2MHz以上、采样率在20MSPS、位数最好是16位的高速ADC,对于有正有负的正弦脉冲信号应选择怎样的ADC进行采样?

2023-12-21 07:40:09

过分计较布局布线的每一个细节。

裸露焊盘

裸露焊盘(EPAD)有时会被忽视,但它对充分发挥信号链的性能以及器件充分散热非常重要。

裸露焊盘,ADI公司称之为引脚0,是目前大多数器件下方的焊盘

2023-12-20 06:10:26

请问ADL5310的底部焊盘是不是应该接地?

2023-12-18 06:51:32

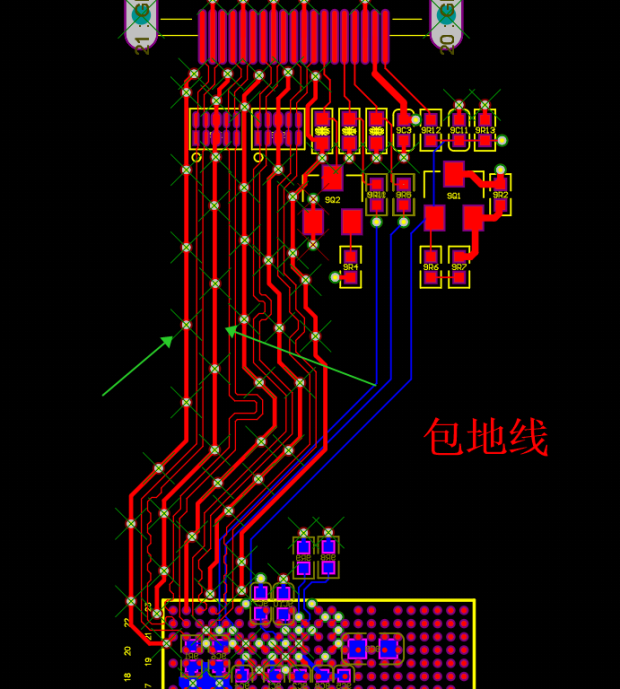

高速信号是否需要包地处理

2023-12-14 18:33:55 548

548

沉积到PCB焊盘表面的一种工艺。这种方法通过在焊盘表面用银( Ag )置换铜( Cu ),从而在其上沉积一层银镀层。

优点与缺点并存,优点是可焊性、平整度高,缺点是存储要求高,易氧化。

沉金板

沉金

2023-12-12 13:35:04

高速信号为啥要走表层?

2023-12-05 15:16:20 214

214

网络搜索“什么是高速信号”或“低速信号与高速信号的区别”,出现一堆解释,例如:

2023-12-01 17:44:41 747

747

电子发烧友网站提供《影响高速信号链设计性能的机制.pdf》资料免费下载

2023-11-28 11:08:02 0

0 如何在高速信号中降低符号间干扰

2023-11-27 15:29:49 187

187

高速信号是否需要走圆弧布线

2023-11-27 14:25:06 514

514

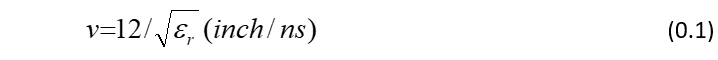

高速电路:数字逻辑电路的频率达到或超过50MHz,而且工作在这个频率之上的电路占整个系统的1/3以上,就可以称其为高速电路

2023-11-27 09:55:26 241

241

大家好,关于ADA4899-1芯片设计的缓冲器,我设计的电路如下:

采用+-5V供电,将10V电压用两个47K的电阻分压,两电阻中间作为地,两边分别是+-5V,焊好电路后用示波器检测输出端的信号

2023-11-27 08:26:39

在PCBA生产中,经常容易在器件的尾端产生连锡现象,在生产中为了避免这种缺陷,设计时需要在器件的尾部加一对无电气属性的焊盘,即为偷锡焊盘。其作用是在焊接过程中,引导锡膏或焊锡流向正确的位置,从而

2023-11-24 17:10:38

在PCBA生产中,经常容易在器件的尾端产生连锡现象,在生产中为了避免这种缺陷,设计时需要在器件的尾部加一对无电气属性的焊盘,即为偷锡焊盘。其作用是在焊接过程中,引导锡膏或焊锡流向正确的位置,从而

2023-11-24 17:09:21

在高速设计中,如何解决信号的完整性问题? 在高速设计中,信号完整性问题是一个至关重要的考虑因素。它涉及信号在整个设计系统中的传输、接收和响应过程中是否能够维持其原始形态和性能指标。信号完整性问题可能

2023-11-24 14:32:28 227

227 在差动放大电路实验中怎样获得双端和单端输入差信号?怎样获得共模信号? 在差动放大电路实验中,我们可以通过多种方式来获得双端和单端输入差信号以及共模信号。以下是一种可能的方法: 首先,让我们了解

2023-11-20 16:28:52 1213

1213 请教如何给高速运放差分信号提供偏置电压?有相关偏置电压的文章吗

2023-11-17 08:13:25

我在使用ADA4898-2时,封装为SOIC-8-EP。中心有个焊盘,布线时惯性思维接到了GND上去。但自己阅读DATASHEET发现说焊盘建议接到VS-或者浮空。但是因为电路板已在使用,请问焊盘

2023-11-16 06:05:11

在器件过波峰时,经常容易在器件的尾端产生连锡现象,在生产中为了避免这种缺陷,设计时需要在器件的尾部加一对无电气属性的焊盘,即为偷锡焊盘。其作用是在焊接过程中,引导锡膏或焊锡流向正确的位置,从而

2023-11-07 11:54:01

对于高速信号,pcb的设计要求会更多,因为高速信号很容易收到其他外在因素的干扰,导致实际设计出来的东西和原本预期的效果相差很多。 所以在高速信号pcb设计中,需要提前考虑好整体的布局布线,良好的布局

2023-11-06 10:04:04 340

340

如何检测复杂的超高速调制光信号? 1. 背景介绍 随着通信技术的不断发展,越来越多的通信系统采用了超高速调制光信号传输数据。超高速调制光信号的传输速度非常快,可以达到每秒数十亿次甚至数百亿次。然而

2023-10-30 11:01:09 212

212 有想过吗,高速信号隔直电容为什么是几百NF量级的? 高速信号隔直电容是一种电子元件,用于隔离高速信号和直流信号之间的干扰。在电路设计中,它常常被用于解决共模噪声和地回路噪声的问题。 在实际

2023-10-24 10:32:29 363

363 关于高速串行信号隔直电容的PCB设计注意点 在高速串行信号传输中,隔直电容是一种常见的解决信号干扰问题的方法。由于高速信号传输时会产生电磁干扰和相邻信号交叉干扰,隔直电容可以将交流信号通路隔离

2023-10-24 10:26:08 490

490 我们知道,常用的一些高速串行信号在设计上都需要加上交流耦合电容,0.1uf、0.22uf是常用的容值。那大家有想过为什么是这个量级呢,容值大了或者小了对高速信号到底会不会有影响呢?

2023-10-13 16:26:03 261

261

脉冲信号怎么产生?怎样才算一个脉冲信号? 一、脉冲信号的产生 脉冲信号是电子电路非常常见的一种信号,其特点为信号的幅度在很短的时间内突然变化,然后迅速恢复原来的状态。脉冲信号通常有两种产生方式

2023-09-28 16:36:24 3553

3553 的可靠性。

缺陷二:立碑

小封装的电阻或电容,如果其中一个焊盘与大面积的铜箔相连,另一个焊盘只与信号线相连,在过炉时,由于一个焊盘散热过快,会因时间差而导致两边的湿润力不平衡,从而致立碑。

缺陷三:拒焊

2023-09-28 14:35:26

的可靠性。

缺陷二:立碑

小封装的电阻或电容,如果其中一个焊盘与大面积的铜箔相连,另一个焊盘只与信号线相连,在过炉时,由于一个焊盘散热过快,会因时间差而导致两边的湿润力不平衡,从而致立碑。

缺陷三:拒焊

2023-09-28 14:31:10

。

2、缺陷二:立碑

小封装的电阻或电容,如果其中一个焊盘与大面积的铜箔相连,另一个焊盘只与信号线相连,在过炉时,由于一个焊盘散热过快,会因时间差而导致两边的湿润力不平衡,从而致立碑。

3、缺陷三:拒

2023-09-26 17:09:22

非常实用,对多种封装类型的引脚推荐焊盘给出查表。本表遵循IPC-2221标准,很多大公司也是在用的,绝对超值。

2023-09-25 07:14:15

元器件,当PCB布局无法满足单面焊接时,会使用双面混装布局,这时需考虑波峰焊的组装制程及组装过程的整个成本。

贴片元件与插件元件管脚距离

由于波峰焊的治具开孔需大于插件元件焊盘,如果治具开孔比较

2023-09-22 15:58:03

元器件,当PCB布局无法满足单面焊接时,会使用双面混装布局,这时需考虑波峰焊的组装制程及组装过程的整个成本。

贴片元件与插件元件管脚距离

由于波峰焊的治具开孔需大于插件元件焊盘,如果治具开孔比较

2023-09-22 15:56:23

电路板显得更加美观;

2、焊接上,可以保护焊盘,避免多次焊接时焊盘的脱落,生产时可以避免蚀刻不均,或者钻孔偏向导线时,避免出现连接处的裂缝而开路,且易于清洗蚀刻药水,不留清洗死角;

3、信号传输时平滑阻抗

2023-09-19 11:44:16

PCB高速信号在当今的一个pcb设计中显然已成为主流,一名优秀的PCB工程师,除了在实战项目慢慢积累设计PCB高速信号的经验外,还需通过不断学习来提升自己的知识储存和专业技能。本文捷多邦小编就给大家科普一下PCB高速信号的一些相关布线知识。

2023-09-15 10:19:18 720

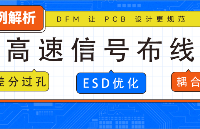

720 今天给大家分享的是:高速信号、14条高速信号布局设计规则。

2023-09-07 09:19:57 454

454

pcb上的高速信号需要仿真串扰吗 在数字电子产品中,高速信号被广泛应用于芯片内部和芯片间的数据传输。这些信号通常具有高带宽,并且需要在特定的时间内准确地传输数据。然而,在高速信号传输的过程中,会出

2023-09-05 15:42:31 472

472 一起就一目了然了。

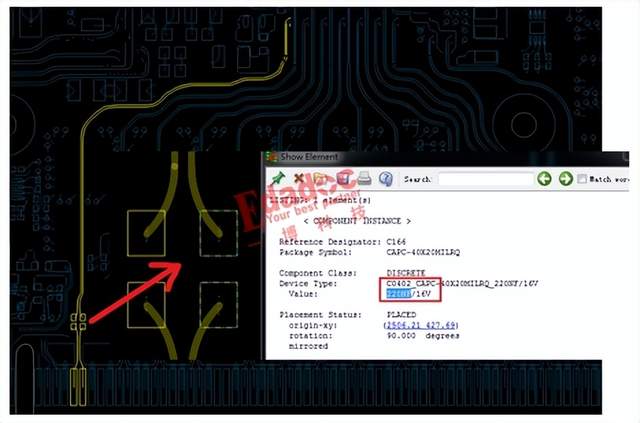

高速信号的布线关注阻抗的连续性,而途经SMD元器件管脚位置的阻抗通常偏小,与走线的特征阻抗不一致,为了尽量提高这些地方的阻抗,元器件管脚下方的参考平面需要进行反焊盘处理,增加管脚到

2023-08-28 18:03:20

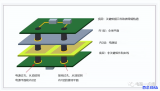

打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

01

BGA焊盘区域挖

2023-08-03 18:18:07

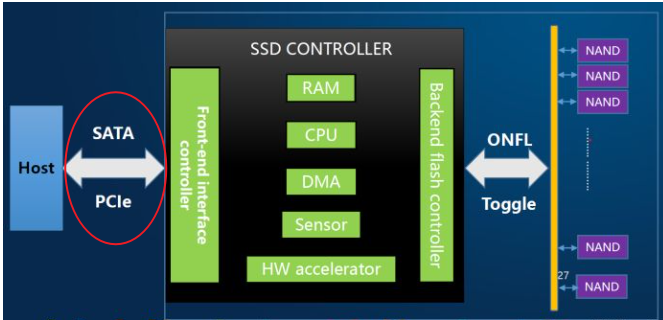

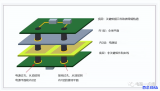

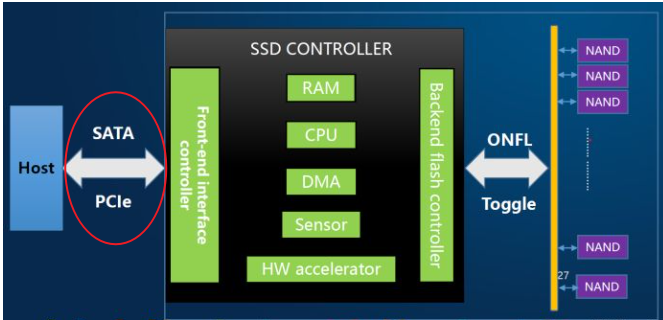

如下表所示,接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。高速信号布线时尽量少打孔

2023-08-03 17:31:07 662

662

如下表所示,接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。 高速信号布线时尽量

2023-08-01 18:10:06 1263

1263

打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

一、BGA焊盘区域挖

2023-08-01 18:02:03

的作用就是绝缘,在焊接工艺中,防止因桥连产生的短路、导体电路的物理性断线,如走线因灰尘、水分等外界环境因素造成绝缘恶化、腐蚀等。

阻焊桥是元件焊盘的一个开窗到另一个开窗之间的绿油部分,一般指比较密集的IC

2023-06-27 11:05:19

PCB焊盘设计缺陷

某些PCB在设计过程中,因空间比较小,过孔只能打在焊盘上,但焊膏具有流动性,可能会渗入孔内,导致回流焊接出现焊膏缺失情况,所以当引脚吃锡不足时会导致虚焊。

2

焊盘表面氧化

被

2023-06-16 14:01:50

PCB焊盘设计缺陷

某些PCB在设计过程中,因空间比较小,过孔只能打在焊盘上,但焊膏具有流动性,可能会渗入孔内,导致回流焊接出现焊膏缺失情况,所以当引脚吃锡不足时会导致虚焊。

2

焊盘表面氧化

被

2023-06-16 11:58:13

请教N76S003 QFN20封装的mcu底部的散热焊盘是GND吗? 有哪位用过的给指点一下感谢感谢啊!

2023-06-14 06:03:13

“ 阻焊层俗称绿油,覆盖在铜箔表面上防止铜线的氧化;同时阻焊桥也可以防止焊接时临近焊盘之间焊锡的流动。了解阻焊的应用方式以及阻焊在KiCad中使用规则,可以帮助我们更好地实现设计目标。 ”

阻焊

2023-06-12 11:03:13

PCB焊盘与孔径设计一般规范(仅参考)

2023-06-09 22:40:24

随着高速串行信号的数据速率的越来越高,如PCIE6.0的数据速率已经达到64GT/s,USB4.0 V2的信号速率已经达到80Gb/s。高速信号的趋肤效应和传输线的介质损耗,使高速信号在传输

2023-06-07 17:27:02 832

832

随着集成电路技术的发展,高速信号的设计技术指标不断更新,系统中的数据传输速率已经提高到数十 Gbit/s 乃至数百 Gbit/s,这就给测试系统、测试硬件设计、测试信号传输质量等带来了新的挑战和更高

2023-06-02 13:43:05 1045

1045

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎90%的EMI问题可以通过高速PCB来控制

2023-05-22 09:15:58 834

834

请教一下,有部分工程师使用的0402以上阻容件封装焊盘呈子弹头设计(焊盘内测导圆),这样设计走什么优缺点呢?

2023-05-11 11:56:44

SMT的组装质量与PCB焊盘设计有直接的关系,焊盘的大小比例十分重要。如果PCB焊盘设计正确,贴装时少量的歪斜可以再次回流焊纠正(称为自定位或自校正效应),相反,如果PCB焊盘设计不正确,即使贴装

2023-05-11 10:18:22

在现代电子设计中,高速信号的传输已成为不可避免的需求。高速信号传输的成功与否,直接影响整个电子系统的性能和稳定性。因此,PCB设计中的高速信号传输优化技巧显得尤为重要。本文将介绍PCB设计中的高速信号传输优化技巧。

2023-05-08 09:48:02 1143

1143 pads 2007 layout中如何加固焊盘,如我想单独把某个焊盘周围的铜皮加得很大,该如何操作,谢谢!

2023-04-28 16:38:40

器件,球引脚间内部信号只能使用更窄的导线布线(图 2)。

图 2 板面走线的焊盘图形设计

阵列最外边行列球引脚间的空间很快被走线塞满。导线的最小线宽与间距是由电性能要求与加工能力决定

2023-04-25 18:13:15

为0.127mm(5mi1)/0.127mm(5mi1)。常用布线密度设计参考表9。

1.3焊盘与线路的连接

11.3.1表面线路与Chip元器件的连接线路与Chip元件连接时,原则上可以

2023-04-25 17:20:30

就是绝缘,在焊接工艺中,防止因桥连产生的短路、导体电路的物理性断线,如走线因灰尘、水分等外界环境因素造成绝缘恶化、腐蚀等。阻焊桥是元件焊盘的一个开窗到另一个开窗之间的绿油部分,一般指比较密集的IC管脚

2023-04-21 15:19:21

就是绝缘,在焊接工艺中,防止因桥连产生的短路、导体电路的物理性断线,如走线因灰尘、水分等外界环境因素造成绝缘恶化、腐蚀等。阻焊桥是元件焊盘的一个开窗到另一个开窗之间的绿油部分,一般指比较密集的IC管脚

2023-04-21 15:10:15

,必须识别高速通道中的这些不连续,并提供减轻其影响的方法,以实现更好的信号传输。其中,元器件封装焊盘,连接器和信号打孔换层都会会造成阻抗不连续及回流路径的变化,这时需要为信号的过孔提供额外的接地过孔为其

2023-04-18 14:52:28

...................21.2 关键信号.......................22 通用高速信号布线........................... 32.1 PCB 纤维编织缓解

2023-04-14 15:47:37

膏可以比较容易地流过小孔,从而顺利印刷到PCB板上。钢网的设计1设计文件的钢网层钢网层(Paste mask)业内俗称“钢网”或“钢板”,这一层并不存在于印制板上,而是单独的一张钢网,在SMD焊盘

2023-04-14 10:47:11

在电子元器件贴片中,经常会用到回流焊,波峰焊等焊接技术。 那么回流焊具体是怎样的呢? 回流焊是通过重新熔化预先分配到印制板焊盘上的膏状软钎焊料,实现表面组装元器件焊端或引脚与印制板焊盘之间

2023-04-13 17:10:36

。 高速电流无法应对信号迹线中的不连续性。最常见和有问题的不连续性是如图A所示的直角拐角。虽然直角拐角在低频下工作没有问题,但在高速时它们会辐射。相反,直角可以用斜角90º角(图B)或两个间隔45°角

2023-04-12 15:20:37

对于高速信号,pcb的设计要求会更多,因为高速信号很容易收到其他外在因素的干扰,导致实际设计出来的东西和原本预期的效果相差很多。 所以在高速信号pcb设计中,需要提前考虑好整体的布局布线,良好

2023-04-12 14:22:25

PCB设计中焊盘孔径与焊盘宽度设置多少?

2023-04-12 11:34:11

PCB自动布线时过孔和焊盘靠得太近怎么解决呢?

2023-04-11 15:28:39

高速pcb的信号完整性问题主要有哪些?应如何消除?

2023-04-11 15:06:07

在高速板layour,为什么要求高速信号线(如cpu数据,地址信号线)要匹配? 如果不匹配会带来什么隐患?其匹配的长度范围(既信号线的时滞差)是由什么因素决定的,怎样计算?

2023-04-11 11:33:43 541

541 数据表没有对 PCB 上焊盘图案的建议。如果我们遵循组件焊盘布局,回流焊期间会出现错位问题,因为一个焊盘较大会导致不同的拉力。

2023-04-11 06:16:10

PCB板上的高速信号需要进行仿真串扰吗?

2023-04-07 17:33:31

PCB板过波峰焊时,板子上元件引脚岀现连焊是什么原因?怎样在波峰焊过程中解决?

2023-04-06 17:20:27

的控制 要想焊接好,设计时就要控制好,还有焊接的火侯也是很关键的,以下是流水作业长遇到的问题及解决方法,抛砖引玉!关键是要实践中了解。 一、焊接前对印制板质量及元件的控制 1.1 焊盘设计 (1

2023-04-06 16:25:06

正确的PCB焊盘设计对于有效地将元件焊接到电路板至关重要。对于裸焊盘组装,有两种常见的焊接方法 -阻焊层定义(SMD)与非阻焊层定义(NSMD),每种方法都有自己的特点和优势。 SMD

2023-03-31 16:01:45

还需要焊接电子元器件,就需要有部分的铜层裸露方便焊接元件,这部分铜层就是焊盘。前文提到铜层裸露容易发生氧化反应,因此焊盘也需要有保护层,防止被氧化;因此出现了焊盘的喷镀,也就是我们常说的PCB表面处理

2023-03-31 15:13:51

高速DAP仿真器 BURNER

2023-03-28 13:06:20

高速无线调试器HSWLDBG BURNER 3.3,5

2023-03-28 13:06:20

封装技术 ,采用BGA技术封装的内存,可以使其在体积不变的情况下,容量提高2-3倍,BGA与TSOP相比,体积更小、散热和电性能更好。BGA封装焊盘走线设计1BGA焊盘间走线设计时,当BGA焊盘 间距

2023-03-24 11:51:19

电子发烧友App

电子发烧友App

评论