网络测试 NetWork 分析仪

2024-03-14 22:30:52

ADXRS910AWBRGZ-RL 特性高性能、层内滚动速率陀螺仪温度补偿,高精度偏移和灵敏度性能陀螺仪噪声:2°/s rms(最大值)16位数据字串行端口接口(SPI)数字输出静态功耗:

2024-02-26 11:06:37

目前用到以下的电源芯片,请问以下的芯片thermalpad 是否需要加过孔到gnd层呢,还是直接在top层直接连接到地网络:

如果在thermalpad 上打过孔,应该打几个

LT3042

2024-01-05 08:25:19

薄TEM薄片+TEM观察分析对于芯片膜层很薄的结构层,一般是几个纳米的芯片膜厚,透射电镜TEM分辨率比SEM高,透射电子显微镜的分辨率比光学显微镜高的很多,可以达到0.1~0.2nm,放大倍数为几万

2024-01-02 17:08:51

厚度建议全部采用1oZ,厚度为1.6mm。

板厚推荐叠层如下图(上)所示(8层通孔1.6mm厚度推荐叠层),阻抗线宽线距如下图(下)所示(8层通孔1.6mm厚度各阻抗线宽线距)。

10层1阶HDI

2023-12-25 13:48:49

厚度建议全部采用1oZ,厚度为1.6mm。

板厚推荐叠层如下图(上)所示(8层通孔1.6mm厚度推荐叠层),阻抗线宽线距如下图(下)所示(8层通孔1.6mm厚度各阻抗线宽线距)。

10层1阶HDI

2023-12-25 13:46:25

具体分析,我们来看看以下两个只设计1个接地层的6层板分层方案,分析只有1个接地层时,会带来哪些不好的影响。

方案一: 该方案的问题是电源层和地层相隔较远,中间隔了两个信号层。所以其电源与地的耦合比较

2023-12-08 10:49:19

具体分析,我们来看看以下两个只设计1个接地层的6层板分层方案,分析只有1个接地层时,会带来哪些不好的影响。

方案一: 该方案的问题是电源层和地层相隔较远,中间隔了两个信号层。所以其电源与地的耦合比较

2023-12-08 10:34:06

AD9164 JESD204B接口的传输层是如何对I/Q数据进行映射的

2023-12-04 07:27:34

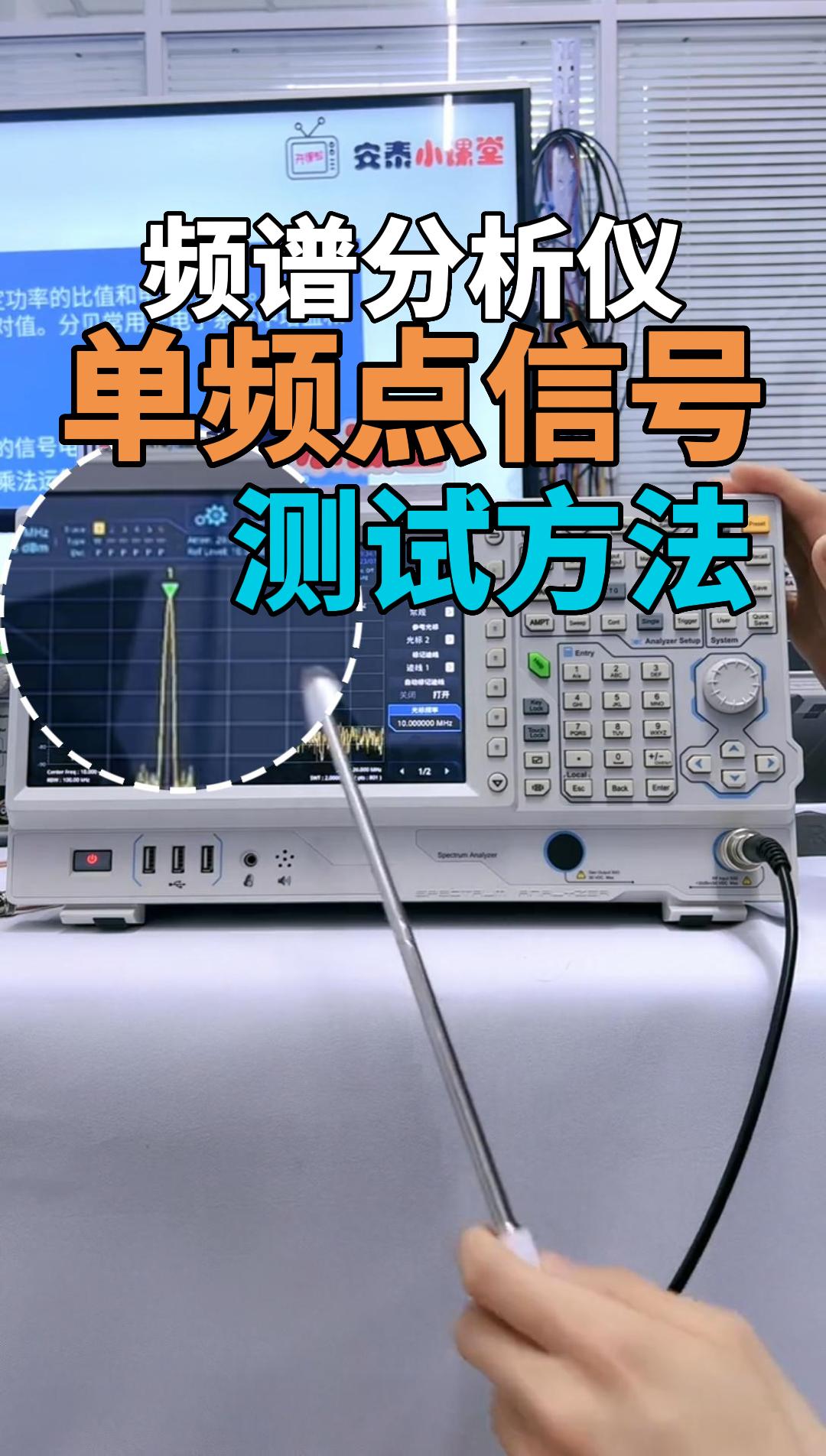

想画出设计的电路THD值,随频率增益变化的曲线,怎么用分析仪测量。

2023-11-17 06:05:15

最近改了几组电机线(3相线+接地线+屏蔽层):

1、地线电机与变频器端都已经接地;

2、屏蔽层入柜处接地;

运行一天下来,发现以下几个现象:

1、如果将屏蔽层在入柜处接地,电机在运行过程中,间隔

2023-11-13 07:50:31

PCB设计时,在那种情况下会使用跨层盲孔(Skip via)的设计?一般叠构和孔径怎么设计?

2023-11-09 16:21:10

请问带显示的和不带显示的USB逻辑分析仪的原理是什么 有没有开源的资料分享?上位机分析软件都是专用的吗?

2023-11-09 06:48:01

在以TCP/IP5层模型中,应用层是如何与传输层连接的 “封装”又是指什么?显示全部

2023-10-28 06:53:10

OPVXG便携式网络综合协议分析仪 1-7层网络全面透视,有线、无线集成式测试,网络负载、压力、吞吐量。。。全面的网络故障诊断和数据包捕捉,现货库存。产品型号说明

2023-10-16 09:41:49

pcb裸铜的logo放在哪一层?

2023-10-16 07:29:19

纸张层间剥离强度试验仪层间结合强度是指纸或纸板抵抗层间分离的能力,是纸张内部粘结能力的反映。强度较低会导致纸张和纸板,在使用粘性油墨印刷时出现拉毛问题,强度过高会给纸张的生产加工带来难度,同时加大了

2023-10-12 16:40:13

逻辑分析仪测的波形是乱的

2023-09-27 07:07:13

复合膜层间剥离试验机 复合膜剥离力测试仪是一款专业用于测试复合膜、薄膜等相关材料剥离强度的仪器。该仪器采用先进的电子测量技术,能够快速、准确地测定复合膜或薄膜材料的剥离力。该设备主要由主机

2023-09-20 15:29:25

4层蓝牙产品PCB设计素材

2023-09-20 07:43:16

我们的应用层和内核层是不能直接进行数据传输的。我们要想进行数据传输,要借助下面的这两个函数。

static inline long copy_from_user(void *to, const

2023-08-29 09:54:29

如烟笑着说讨厌。

赵理工,在七夕前一天投了一个板,一个8层,2.0mm的软硬结合板。软板2层,硬板是6层,内层铜厚1OZ,线宽线距没有走极限,且都满足工艺能力,叠层如下:

从叠层中,我们可以看出

2023-08-22 16:48:12

的分析方法。利用干涉仪图样的分析,可以直接获得相关参数(如膜层厚度、表面粗糙度、膜层折射率等),从而得到准确的测量结果。

2、对于非同质材料,由于其光学特性的差异性,分析方法相对更为复杂,通常需要借助

2023-08-21 13:46:12

在两个 tensorflow 模型上运行模型优化器,其中包含一个ctc_greedy_decoder和tf.keras.backend.ctc_decode的 CTC 层

这两个错误均未

2023-08-15 08:26:07

在 OpenVINO™ 工具套件 2021.4 中使用 IENetwork.层 。

收到错误:openvino.inference_engine.ie_api。IENetwork 对象没有属性“层”

2023-08-15 06:41:56

类型的不同,各参数的最佳工艺存在差异。 在恒压模式下,随电压的升高,氧化膜生长速率增大,膜层厚度、表面孔隙率及防腐性均增加,

2023-07-19 16:45:41

使用NUC970 官网自带的mtd层nuc970_nand.c 驱动,硬件BCH ECC 已正确开启,如何制造一个nandflash 层ECC错误,并触发数据纠错,有什么办法? 有没有谁做过类似测试的。

2023-06-27 15:09:52

“ 不同EDA对于PCB中物理层的定义基本相同,比如信号层、丝印、阻焊、助焊等。但对于工艺层(辅助层)的定义会略有不同,比如Altium Designer没有专门的板框层及Courtyard层,通常

2023-06-21 12:13:20

“ 使用Allegro的小伙伴应该很清楚Courtyard层的用法,但使用Altium Designer的小伙伴可能对Courtyard层完全没有概念。Courtyard层到底是什么?在KiCad

2023-06-13 13:01:24

)。

添加Logo或其他图形(也可以在丝印层)。

在阻焊层上添加文本或图形,可能不如丝印层引人注目。露铜的文字或图形看起来是不是很酷,取决于铜的表面处理方式。与丝印层相比,阻焊层可以做到更高的分辨率

2023-06-12 11:03:13

我的客户需要在 i.MX8mini ( iMX8MMINI ) 上有一个可用的 AVS SDK,我发现了以下可能适合的元层:

https://github.com/nxp-imx-support

2023-06-08 06:45:15

频域上去分析。时域的话,雷豹已经在信号眼图上有对比过了,那么想继续分析这个串扰的改善的话,就有在频域上去做文章了。

Chris对雷豹调整叠层前后的走线结构进行建模,利用cadence的3D

2023-06-06 17:24:55

“ 经常看到小伙伴们询问KiCad中的Margin层有什么用,和板框层Edge.Cut有什么区别?虽然实际实际中可以完全忽略Margin层,但理解它并合理的加以使用,可以为设计带来一定的便利

2023-06-06 09:46:43

。内层的加工成本相同,但敷箔/核结构明显的增加外层的处理成本。

奇数层PCB需要在核结构工艺的基础上增加非标准的层叠核层粘合工艺。与核结构相比,在核结构外添加敷箔的工厂生产效率将下降。在层压粘合以前

2023-06-05 14:37:25

为了比demo板有更好的成本优势,在设计上使用了相邻层走线的这个方法,也就是我们所说的GSSG的叠层结构,这样的话的确在层数上可以省下几层,但是就会带来其他方面的一些坏处。雷豹一直都是在关注走线

2023-06-02 15:32:02

电解质支撑,但是欧姆电阻很大,正常在1以内,我的欧姆电阻4-15甚至更多,开路电压可以达到1V,集流层采用银乙醇,想知道怎么改进?谢谢,这个是烧后的SOFC

2023-05-20 16:46:05

的PCI Express Gen6,也开始采用了多通道技术。 安立的信号质量分析仪-R MP1900A系列是一款具备8个模块插槽的高性能BERT,通过PPG/ED、及抖动/噪声发生器等扩展测量

2023-05-17 17:59:55

的PCI Express Gen6,也开始采用了多通道技术。 安立的信号质量分析仪-R MP1900A系列是一款具备8个模块插槽的高性能BERT,通过PPG/ED、及抖动/噪声发生器等扩展测量

2023-05-17 17:57:44

的PCI Express Gen6,也开始采用了多通道技术。 安立的信号质量分析仪-R MP1900A系列是一款具备8个模块插槽的高性能BERT,通过PPG/ED、及抖动/噪声发生器等扩展测量

2023-05-17 17:54:39

由于运输 SAM 要求高性能,客户希望在做出决定之前看到一些预测试。我们与唯冠 DFAE 合作开发 SW 小程序。SAM卡中的这个小程序可以按照客户算法进行办理和充值交易。

交易时间是客户可以接受的。所以客户研发团队已经完成了JCOP4.5 中的applet 移植。

2023-05-08 08:28:35

在多层电路板里是不是所有电源都必须放在内电层呢?

2023-05-06 10:20:36

PCB四层板的电源和地的内层到底怎么布线?

2023-05-06 10:19:18

PCB 四层板里面的电源层和地层是什么意思,或者多层板里面的电源层和地层是什么意思?

我只是把四层板里面的中间两层当做是装换的或连接的,为什么教材里面说是电源层和地层呢?

2023-05-06 10:15:14

1.PCB中,两个不同电压的电源层可以共用一个地层吗?

2.如果可以共用地层的话,对于两个不同电压的电源层是各自用一个地层好,还是共用一个地层好?

3. “两个电源层:3.3V,2.1V; 两个信号层 ;地层” 怎样布局最好?

2023-05-06 10:12:52

我们正致力于为基于 IMX8MPlus 的定制板开发 Windows IOT 支持。我们使用 DP83867 以太网物理层代替 IMX8MPlus 板中使用的 RTL8211F 以太网物理层。

我们

2023-05-06 07:34:35

我建板s32g274ardb2,它可以制作图像。现在我想向项目添加新层,所以我设置了新的 layaer meta-mylayer,我创建了 .bb .c 和 makefile。

然后我将

2023-04-25 09:59:34

层将再次被“百分比覆盖率”方法,假设的50%的铜覆盖和1盎司/ ft2(35µm)厚度。第4层仍然和以前一样不连接到任何一个器件。 因此,4层结构总结在图8中。层4仍然是一个覆盖整个底面的固体平面

2023-04-21 15:04:26

4.3.6 实验设计6:一个4层的PCB板与热散热过孔 为了完整性,“4层+散热过孔”结构也被实验设计为1层铜的几个尺寸,并再次叠层,如图8所示。结果如图13所示。 (1)单层板。 (2

2023-04-21 14:51:37

SDK 软件组件和抽象层文档

2023-04-21 07:18:06

走线组成,而不是大型连续面积。对这些层进行详细的实验设计显然是不可行的,因此采用了“百分比覆盖率”方法。采用这种方法,计算出结构的平均电导率,以铜层厚度占总面积的百分比计算。这些实验设计的目的,我们将

2023-04-20 17:10:43

我遇到了一个与 meta-rust 层相关的 I.MX yocto 构建错误,这是我之前在 bitebake 构建过程中没有看到的。在它下面是错误线, 错误:任务(虚拟:本机:/home/dand

2023-04-20 08:49:07

4层PCB是一种常见的多层PCB类型,具有多种用途。您是否有兴趣了解更多关于它们的信息,特别是它们的堆栈设计和类型?它们的优点是什么,与2层PCB相比如何?

2023-04-14 15:38:20

功率分析仪进行谐波测试是采用FFT算法还是其他算法呢?

2023-04-13 11:09:35

PCB四层板中我将中间两层设置成了信号层,能否给点实用的布线的经验???当布完线后该怎么进行敷铜呢?需要在哪层进行敷铜,最好是能说说为啥。如果将中间层设置成电源层和地层,那中间层还能走信号线吗???需要注意些什么???在此谢过。。。。

2023-04-11 17:33:46

多层PCB如何定义叠层呢?

2023-04-11 14:53:59

请教一下大神PCB多层板为什么都是偶数层呢?

2023-04-11 14:52:31

将BLE抽象层添加到新项目的正确方法是什么,应该从哪里下载抽象。

2023-04-11 07:06:33

PCB板阻抗设计:阻抗线有无参考层阻抗如何变化?生产PCB时少转弯的阻抗线的阻抗更容易控制稳定性?

2023-04-10 17:03:31

矢量网络分析仪串扰如何测试,设备如何设置

2023-04-09 17:13:25

看到有f.cuf.adhes f.paste f.silks f.mask dwgs.user cmts.user eco1.user margin 有这些预定义的层,分别代表什么意思呢?分别在什么时候用呢?

2023-04-02 17:58:34

FPC基本结构材料介绍 从挠性印制线路板的基本结构分析,构成挠性印制线路板的材料有绝缘基材、胶粘剂、金属导体层(铜箔)和覆盖层 。 01.铜箔基板(Copper Film) 铜箔:基本分

2023-03-31 15:58:18

大家好,我正在研究 VAR-SOM IMX8,我正在构建 Qt5 图像,yocto 版本是dunfell-fslc-5.4-2.1.x-mx8-v1.5。当我尝试将 meta-webkit 层添加到

2023-03-30 07:45:15

我正在研究 MBDT 中 BMS 与新 S32K344 和 MC33775 与先前版本 BMS MC33771 和 MC33664 的集成。我发现最新的 MBDT 使用 MCAL 层通过

2023-03-30 07:05:40

PADS设计4板,第一层基板挖一个大矩形槽,露出第二层基板,再在第二层基板挖一个小矩形槽,嵌套的。请问怎么实现?

2023-03-24 11:16:33

电子发烧友App

电子发烧友App

评论