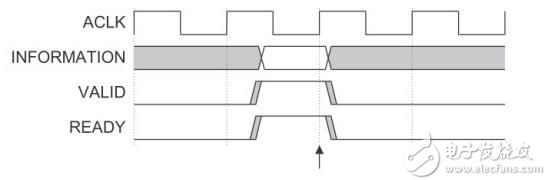

ZYNQ 、AXI协议、PS与PL内部通信 三种AXI总线分别为: AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址

2018-01-09 14:10:42 7060

7060

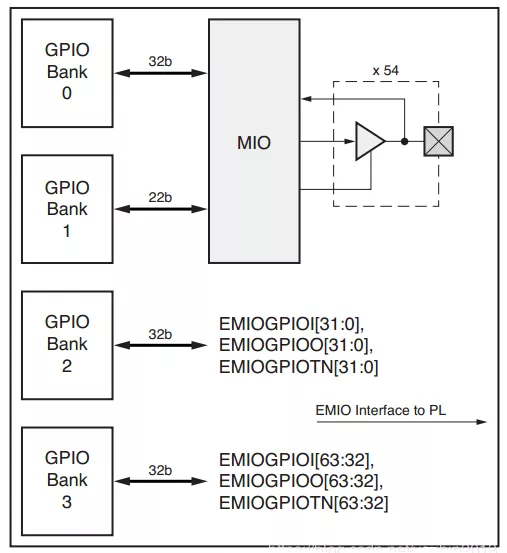

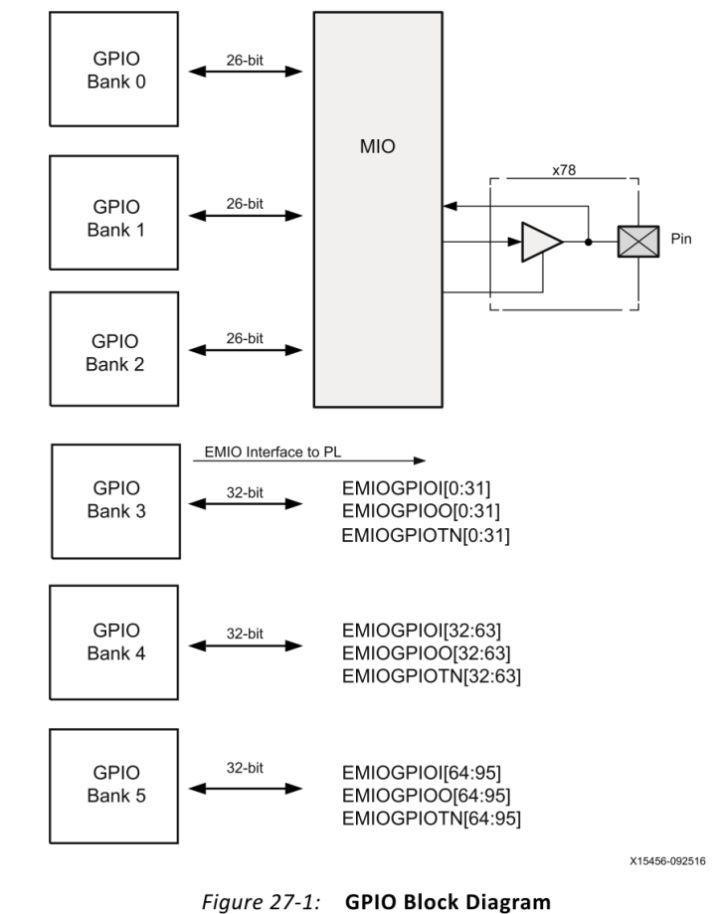

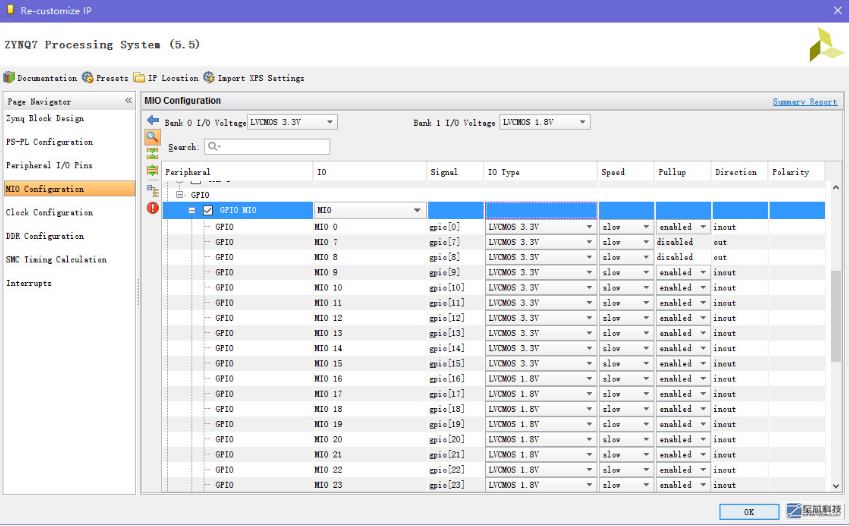

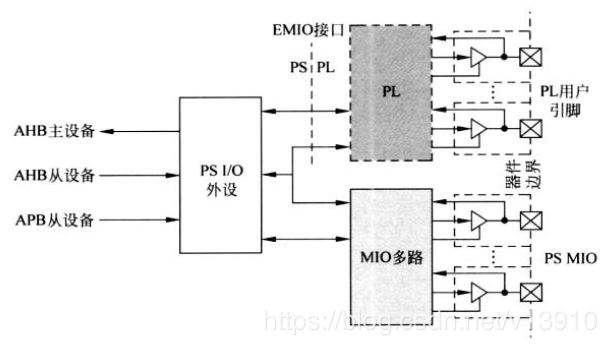

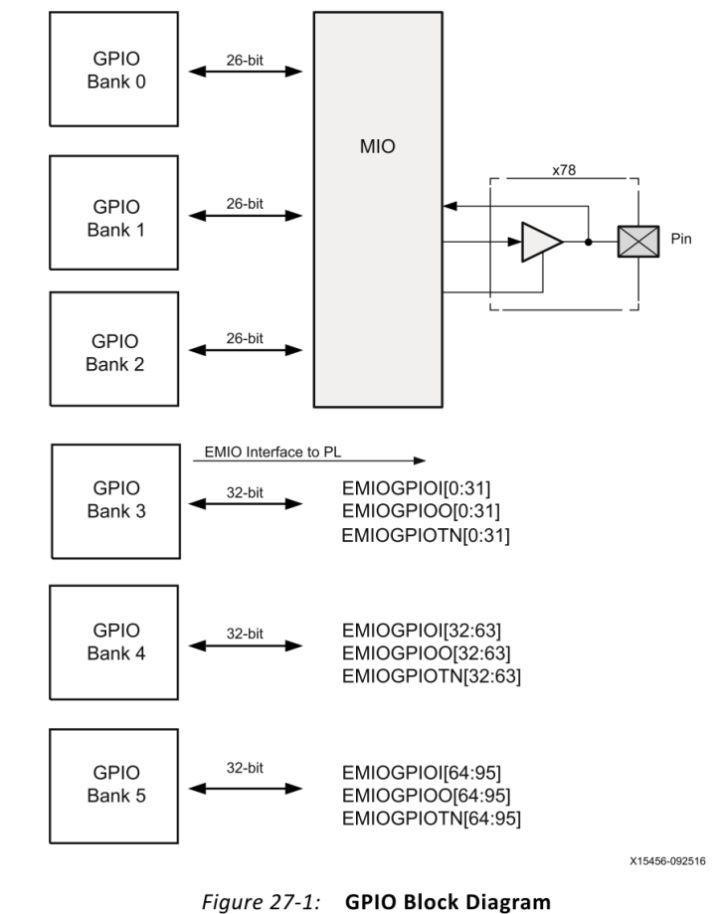

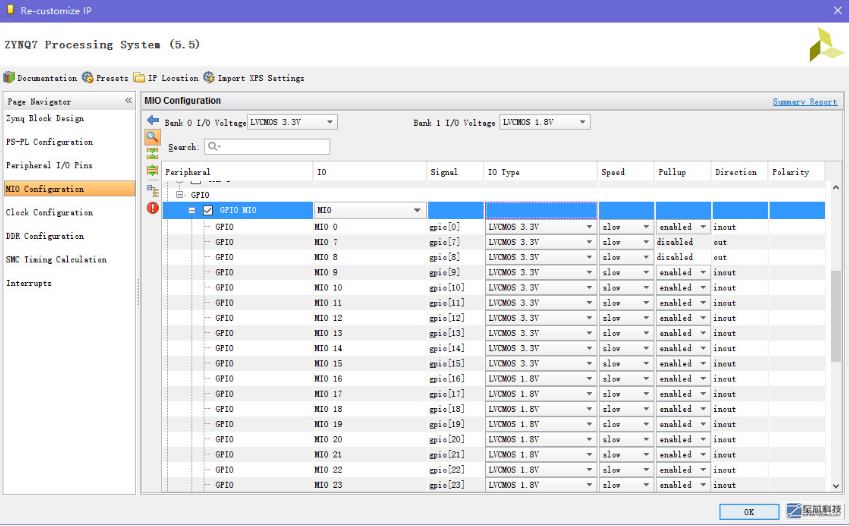

通过AXI点亮PL端LED。 1. MIO与EMIO 首先来理清楚MIO与EMIO的关系。MIO是PS的I/O引脚,一共有54个,分为Bank0与Bank1,可以接许多外设比如UART、SPI或GPIO

2020-11-24 14:32:33 20365

20365

的逻辑部分,PS侧为arm端以及一些AXI接口控制部分,二者实际上通过AXI接口实现通信和互联。PS可以通过AXI来对PL逻辑部分进行配置和控制,PL侧通过AXI和PS进行数据交互。本章

2020-11-30 11:56:01 3490

3490

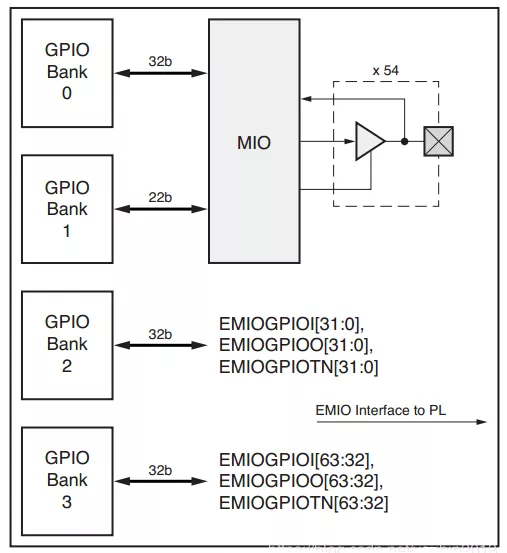

直接连接在PS上,像其他普通ARM一样,不需要通过XPS进行硬件配置,直接通过SDK编程即可。 Bank2和Bank3通过EMIO接口将CPU的GPIO连接到PL部分的引脚上,其中每个Bank各有32个

2020-12-09 11:41:46 3054

3054

。 Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。 本部分的学习

2020-12-25 14:11:50 6842

6842 FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门开发

2020-12-25 14:07:02 2957

2957

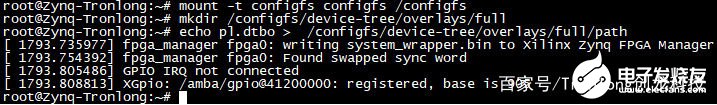

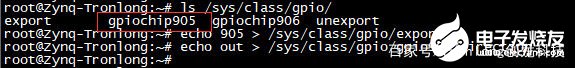

前言: ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源

2020-12-26 10:12:57 3306

3306

一、AXI DMA介绍 本篇博文讲述AXI DMA的一些使用总结,硬件IP子系统搭建与SDK C代码封装参考米联客ZYNQ教程。若想让ZYNQ的PS与PL两部分高速数据传输,需要利用PS的HP

2020-12-31 09:52:02 7164

7164

如果想用PS点亮PL的LED灯,该如何做呢?一是可以通过EMIO控制PL端LED灯,二是通过AXI GPIO的IP实现控制。本章介绍如何使用EMIO控制PL端LED灯的亮灭。同时也介绍了,利用EMIO连接PL端按键控制PL端LED灯。

2021-01-30 10:05:00 6729

6729

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 6182

6182

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00 12916

12916

/p/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 13958

13958

MPSoC有六个PL侧高性能(HP)AXI主接口连接到PS侧的FPD(PL-FPD AXI Masters),可以访问PS侧的所有从设备。这些高带宽的接口主要用于访问DDR内存。有四个HP AXI

2022-07-22 09:25:24 2501

2501 本帖最后由 何立立 于 2018-1-9 15:03 编辑

ZYNQ 、AXI协议、PS与PL内部通信 三种AXI总线分别为:AXI4:(For high-performance

2018-01-08 15:44:39

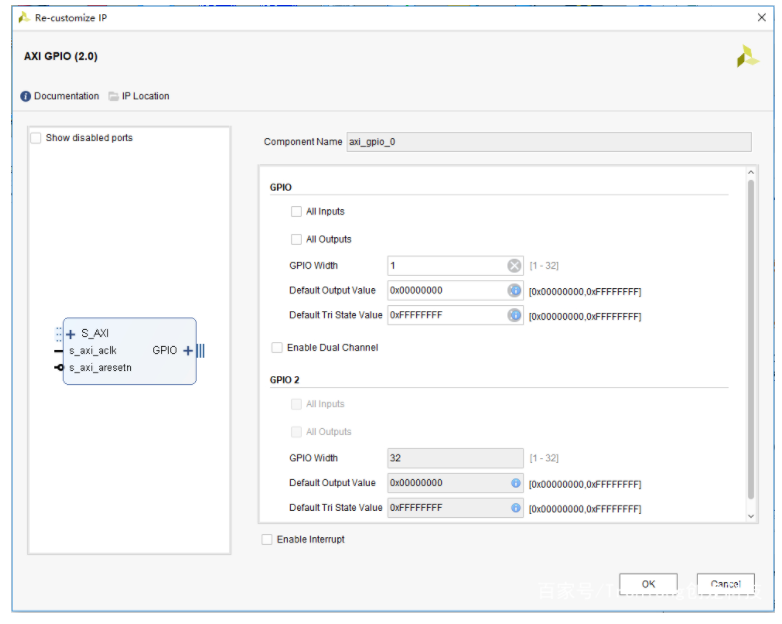

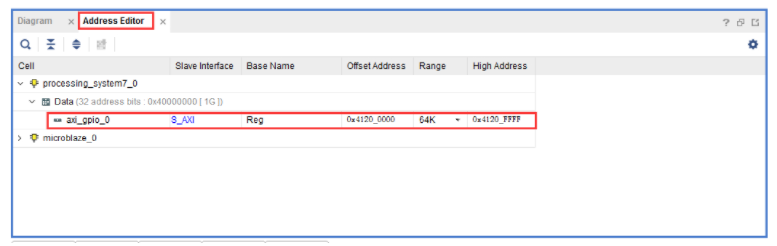

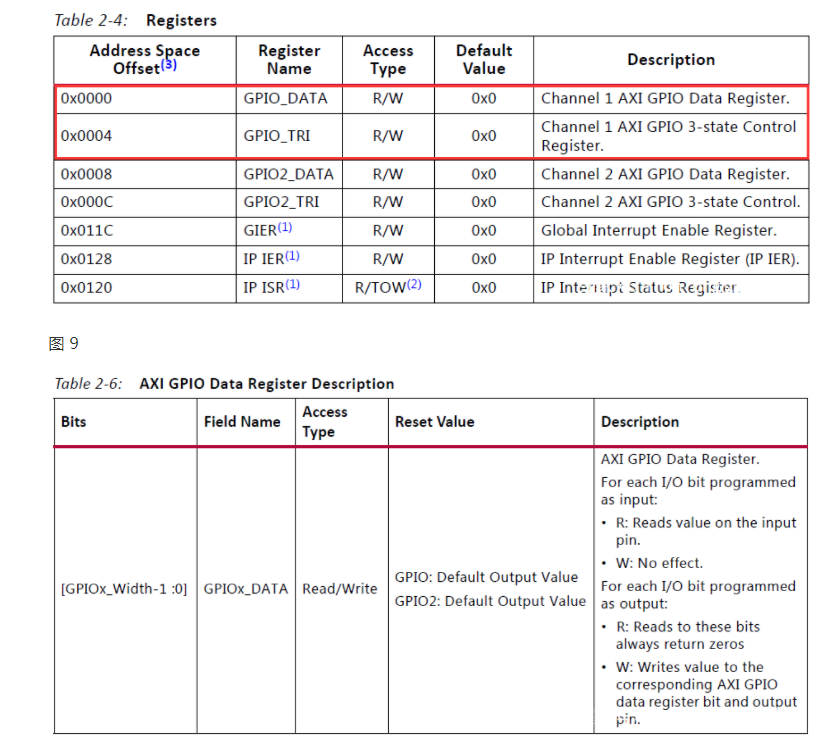

。1 axi_gpio_led_demo案例1.1 案例功能案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI GPIO IP核,IP核再根据命令控制评估底板PL端LED5的状态图

2021-05-28 14:28:28

不同类型的DMAHigh performance w/DMA几种DMA的总结ZYNQ中不同应用的DMA几个常用的 AXI 接口 IP 的功能(上面已经提到):AXI-DMA:实现从 PS 内存

2022-03-31 11:39:10

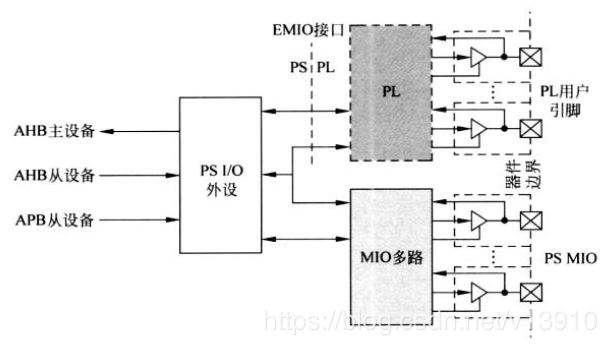

ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚

2022-02-08 07:27:16

使用AXI4_Lite)总线把数据写入RAM中,PS端从RAM中读取数据。

3.PL端

(1)首先创建一个Block Design,加入以下IP核:

IP核的设置为

2023-11-03 10:51:39

ZYNQ学习笔记_ZYNQ简介和Hello WorldZYNQ介绍PS和PL的连接ZYNQ开发工具链在PS端编写Hello World程序ZYNQ介绍ZYNQ-7000系列是基于Xilinx开发环境

2022-02-17 07:37:36

PS和PL互联技术ZYNQ芯片开发流程的简介

2021-01-26 07:12:50

例程位置ZYNQ例程保存在资料盘中的Demo\\ZYNQ\\PL\\FPGA_DSP_GPIO文件夹下。DSP例程保存在资料盘中的Demo\\DSP\\XQ_GPIO_FPGA文件夹下。1.1.2

2023-06-16 16:02:47

开发应用,这一款基于Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板,处理器集成PS端双核ARM Cortex-A9 + PL端

2021-06-30 09:56:45

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

进行编程的初步PS和PL。如果上面有必要的信息,请提供。7.请提供ZYNQ 7Z020-CLG484芯片的所有I / O文档8.如何在没有AXI的情况下将处理器(PS)地址,数据,WRB,RDB连接到PL)。如何使用emio PINS来PL和PL到PS)。请提供必要的信息

2020-03-12 14:39:42

zynq的PS如何向一个基于AXI4-FULL协议的自定义IP批量传输数据?

2017-02-22 12:05:35

。适用于无人机蜂群、软件无线电系统,基带信号处理,无线仿真平台,高速图像采集、处理等领域。一、软件目录1、ZYNQ与DSP之间通信例程SRIO通信 EMIF16通信 uPP通信 GPIO通信2、DSP单独例程3、ZYNQ PL单独例程4、ZYNQ PS单独例程

2022-12-27 15:42:44

TMS320C6678 ZYNQ的开发手册详细资料将围绕8大板块,分别有cameralink_loopback、sdi_capture_display、fmc_tw2867_display

2021-05-24 11:12:40

项目名称:基于stm32mp1的异构多核研究试用计划:申请理由:本人从事嵌入式研究多年,一直在工控领域开发工业产品。目前单位准备采用STM32MP1完成新产品的开发,刚好论坛的活动,因此积极参与本次

2020-03-25 16:50:11

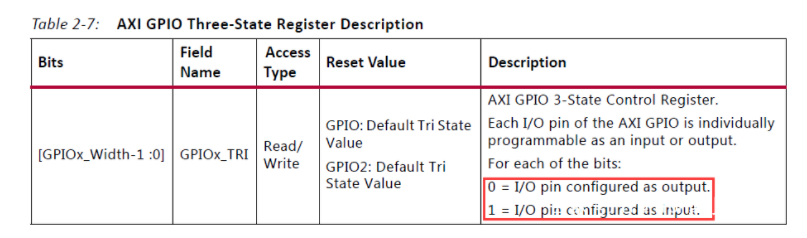

区别的,两者在很多地方不同,比如关于引脚方向设置,PL的GPIO是0设置为输出,PS的GPIOPS是1设置为输出。关键代码:int led_gpiops(){int led

2015-06-14 14:27:17

持PS+PL的架构,灵活使用PL。Zynq上的存储器接口也很丰富,包括DDR控制器,Quad-SPI控制器、Nand/NOR/SRAM控制器等。通用IO(GPIO)在Zynq上,我们可以通过MIO引出最多54个

2015-07-07 20:22:49

本帖最后由 mytom520 于 2015-6-12 00:04 编辑

AXI总线是Zynq PS、PL的桥梁,想要发挥好Zynq的优势,AXI总线IP是不可或缺的。首先讲解一下IP的工作原理

2015-06-11 23:52:23

的双核ARM Cortex-A9处理系统(PS)和Xilinx可编程逻辑(PL)。在我的设计中充分利用了Zynq的软硬件协同优势,因为软硬件系协同设计能够最大程度地发挥了异构多核处理器的优势,软更加拓宽

2015-07-07 20:41:04

了它对我满满的敌意。 原来主逻辑只有一个PS,PL这边就是简单的管教驱动和LED送显之类的,我突然明白了,原来,这个开发板的目标是玩ARM啊,不然为啥是个Z7010撒,我感觉离目标又远了一步,不管怎么样

2015-05-27 21:27:17

输入到PL的管脚上一个时钟信号,另一种方法则是使用PS提供给PL的时钟信号。从ZYNQ的技术手册里我们得知,PS部分可以提供给PL四路相对独立的时钟信号(它们之间不保证时序上的关系),因此我们的任务就是

2015-06-01 11:54:12

1)实验平台:正点原子领航者ZYNQ开发板2)平台购买地址:https://item.taobao.com/item.htm?&id=6061601087613)全套实验源码+手册+视频下载

2020-09-20 17:28:02

到ZYNQ的PL端,PS_KEY0和PS_KEY1连接到ZYNQ的PS端。在《领航者ZYNQ之FPGA开发指南》中,我们只使用PL端的外设。PL端的按键没有按下时,对应的IO端口为高电平;当按键按下时,对应

2020-09-21 16:57:52

熄灭。然后再按下底板上PL端的用户按键PL_KEY0,可以看到核心板上PS端的LED2(红色)在按键按下时点亮,释放后熄灭。说明我们通过EMIO扩展GPIO接口,使用PL端按键控制PS端LED的实验在领航者ZYNQ开发板上面下载验证成功。实验结果如下图所示:图 3.5.5 下载验证

2020-08-29 16:20:36

教程《领航者ZYNQ之FPGA开发指南》的3.1.2节表3.1.2领航者ZYNQ PS端IO引脚分配总表中,我们摘录部分如下图,可以看到领航者开发板有5个GPIO_MIO连接到外设LED和KEY上,这些

2020-08-29 16:17:15

1)实验平台:正点原子领航者ZYNQ开发板2)平台购买地址:https://item.taobao.com/item.htm?&id=6061601087613)全套实验源码+手册+视频下载

2020-09-21 16:42:52

连接到ZYNQ的PS端。在《领航者ZYNQ之FPGA开发指南》中,我们只使用PL端的外设。PL_LED0和PL_LED1的阴极通过 470 欧姆的电阻连到地(GND)上,阳极由ZYNQ PL的IO管脚

2020-09-21 16:52:41

原子公众号,获取最新资料第十四章基于BRAM的PS和PL的数据交互在ZYNQ SOC开发过程中,PL和PS之间经常需要做数据交互。对于传输速度要求较高、数据量大、地址连续的场合,可以通过AXI DMA来

2020-09-04 11:08:46

1 核心板简介创龙科技SOM-TLZ7x是一款基于Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业核心板,处理器集成PS端双核ARM

2023-06-21 15:19:22

源码、文件系统源码,以及丰富的Demo程序;(3) 提供完整的平台开发包、入门教程,节省软件整理时间,让应用开发更简单;(4) 提供详细的PS + PL SoC架构通信教程,完美解决异构多核开发瓶颈

2023-06-25 09:56:01

和M_AXI_HPM0_LPD。 位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xilinx在Vivado开发环境里提供现成IP如AXI-DMA,AXI-GPIO

2021-01-07 17:11:26

错误。然后,我在SDK中编程PS端,led闪烁正确的频率!我的问题,当锁定Zynq PL时钟? PS程序之后?需要多长时间?是不是意味着,PL配置期间LED闪烁错误,在非易失性Flas Boot中编程PS期间(或之后)闪烁?谢谢的Berker

2020-08-27 15:09:19

1.什么是异构多核SoC处理器顾名思义,单颗芯片内集成多个不同架构处理单元核心的SoC处理器,我们称之为异构多核SoC处理器,比如:TI的OMAP-L138(DSP C674x + ARM9

2020-09-08 09:39:19

1.案例说明PL端接入CameraLink相机,通过Base模式采集图像(1280*1024),然后通过VDMA缓存到PS端DDR。使用AXI4-Stream Switch IP核将图像复分成两路

2020-09-17 09:48:13

`本次测试使用广州创龙开发板 TLZ7x-EasyEVM(基于Xilinx Zynq-7000 SoC高性能低功耗处理器,集成PS端单核/双核Cortex-A9 ARM + PL端 Artix-7

2018-06-08 10:13:57

Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。4 matrix_demo 案例案例功能: 实现 32*32 浮点矩阵乘法运算功能

2023-01-01 23:50:04

龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。

4 matrix_demo 案例案例功能: 实现 32*32 浮点矩阵乘法

2023-08-24 14:52:17

案例使用到本案例 IP 核,因此请参考 PS + PL 异构多核案例开发手册的 camera_edge_display 案例说明进行 IP 核测试。

2023-08-24 14:54:01

参考 PS + PL 异构多核案例开发手册的 camera_edge_display 案例说明进行 IP 核测试。

2023-01-01 23:46:20

下的camera_edge_display案例使用到本案例IP核,因此请参考PS + PL异构多核案例开发手册的camera_edge_display案例说明进行IP核测试。

2021-11-11 16:02:09

我想在ZYNQ上的PS也就是ARM上跑linux系统,然后PL中有加入一个AXI4的IP,IP中有多个寄存器,我不知道该如何开发驱动程序来对这个寄存器列表进行读写。然后单个寄存器在Embedded

2015-07-22 19:11:29

`玩转Zynq连载2——Zynq PS的GPIO外设更多资料共享 链接:https://share.weiyun.com/5s6bA0s1 概述 Zynq的GPIO外设控制最多54个MIO引脚,也

2019-04-18 16:33:51

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取码:ld9c 1 Zynq的GPIO概述参考文档《玩转Zynq-基础篇:Zynq PS的GPIO外设.pdf》。 2

2019-10-10 11:21:06

zstar.bit文件和GPIO_EMIO_project.elf文件烧录到Zynq中运行起来。程序运行起来后,我们就可以看到Zstar板上PL侧的3个LED指示灯D3、D2和D1逐个闪烁起来。 腾讯微云链接

2019-10-12 17:35:16

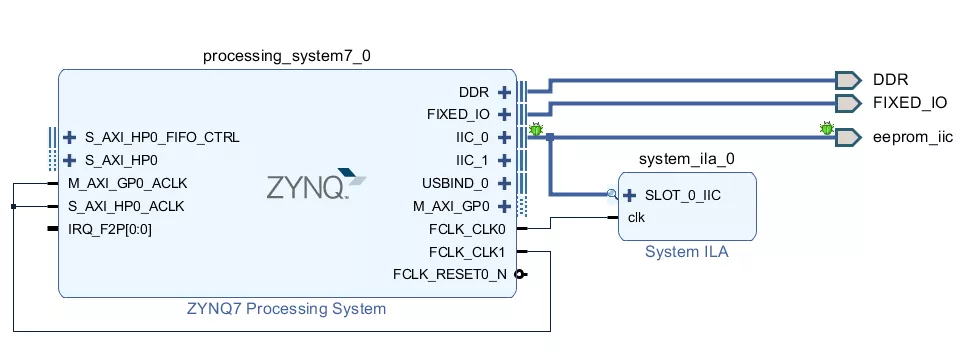

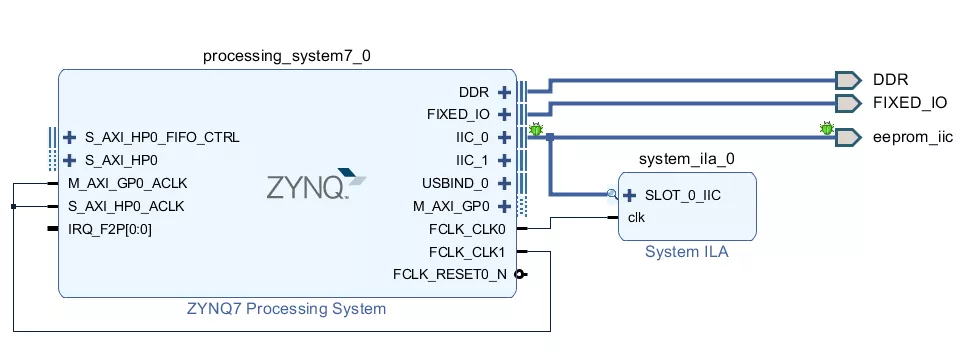

Interface,勾选M AXI GP0 interface,相当于开启PS系统的AXI GP0的主机功能。注意下面还有一个M AXI GP1 interface,也就是说Zynq最多可以有2个AXI

2019-11-12 10:23:42

1概述AXI HP总线是Zynq芯片非常重要的一个功能,它可以实现Cortex A9与PL之间大吞吐量的数据通信。可以说,Zynq芯片最大的卖点恐怕就是这条总线。对不起,不是1条,是4条这样的AXI

2019-11-26 09:47:20

.pdf》。3 Zynq PS的AXI HP与VIO IP配置如图所示,在ZYNQ7Processing System在,点击Page Navigator --> PS-PL

2019-11-28 10:11:38

/XC7Z020高性能低功耗处理器设计的异构多核SoC评估板,处理器集成PS端双核ARM Cortex-A9 + PL端Artix-7架构28nm可编程逻辑资源,评估板由核心板和评估底板组成。核心板经过专业

2021-11-11 15:54:48

案例Ø PCIe、双千兆网口开发案例Ø 图像处理开发案例Ø DSP算法开发案例ZYNQ端开发案例Ø 基于Linux的开发案例Ø 基于裸机的开发案例Ø 基于FreeRTOS的开发案例Ø 基于PS + PL的异构

2021-03-16 17:35:46

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

的Linux的xdevcfg设备来编程PL部件。有趣的解决方案是通过在同一芯片的PS部分运行的XVC远程调试基于Zynq的设计。假设我将XAPP1251中描述的AXI-JTAG控制器添加到我的设计中,是否

2020-07-30 13:51:19

北京革新创展科技有限公司目前已经拥有基于嵌入式Linux系统的STM32MP157、AM4378、FPGA开发板和异构多核综合创新实验平台。GX-ARM-STM32MP157XAA-SOM核心板

2022-03-08 16:57:10

本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 53204

53204

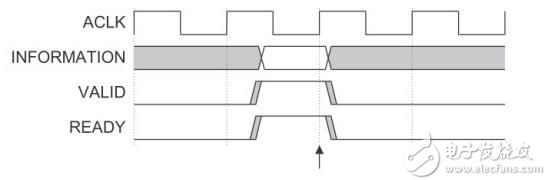

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、PL端接口为FIFO接口; PS到PL的数据传输流程: PS

2017-02-08 01:00:11 1431

1431

上周的博客中我们学习了Zynq SoC的AXI DMA,我解释了怎样利用AXI DMA控制器将数据从PL搬运到PS。在本期博客中我们将学习怎样完成硬件的搭建。 首先我们要更深入的了解一下AXI

2017-02-08 08:10:39 286

286 GPIO的博客说的有一些不一样呢。 我们先看有哪三种GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接挂在PS上的GPIO。而AXI_GPIO是通过AXI总线挂在PS上的GPIO

2017-02-08 10:23:12 2710

2710

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 956

956

《一步一步学ZedBoard & Zynq》系列第二篇,目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 3749

3749 Zynq芯片中,PS(ProcessorSystem)和PL(Programmable Logic)之间提供了一共9个双向读写的通信端口,他们分别是: M_GP0 M_GP1 S_GP0 S_GP1

2017-11-17 10:03:39 11543

11543 我们先看有哪三种GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接挂在PS上的GPIO。而AXI_GPIO是通过AXI总线挂在PS上的GPIO上。

2018-07-07 08:23:00 4944

4944 GPIO功能,PS部分通过M_AXI_GP接口来控制该GPIO IP模块;另外EMIO模块虽然使用PS部分GPIO但也使用了PL部分的管脚资源。MIO方式实现GPIOvivado中zynq设置如下图由图中

2018-08-07 10:16:49 2708

2708

Zynq在PS和PL之间有9个AXI接口。

2018-12-30 09:45:00 6907

6907 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4284

4284

不同类型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 几种

2020-10-09 18:05:57 6388

6388

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3879

3879

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 2046

2046

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 上,也可以通过 EMIO 连接到 PL 端的引脚。Zynq-7000 系列芯片一般有 54 个 MIO,个别芯片如 7z007s 只有 32 个。GPIO 是英文“general purpose I/O”的缩写,即通用的输入/输出。是 ZYNQ PS 中的一个外设,用于观测和控制器件引脚的状态。图 1

2021-12-04 18:51:06 16

16 通过MIO(Multiuse I/O)模块对器件的引脚做观测(input)和控制(output)。ZYNQ的PS端上的GPIO也可以通过EMIO(Extra MIO)模块对PL端的IP以及引脚实现上述操作。GPIO可以独立且动态地编程,作为输入/输出以及中断模式。如上图所示,ZYNQ将GPIO分为了4

2021-12-04 19:36:10 10

10 核心板简介创龙科技SOM-TLZ7x-S是一款基于Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板,处理器集成PS端双核ARM

2021-12-22 19:00:38 15

15 ZYNQ学习笔记_ZYNQ简介和Hello WorldZYNQ介绍PS和PL的连接ZYNQ开发工具链在PS端编写Hello World程序ZYNQ介绍ZYNQ-7000系列是基于Xilinx开发环境

2021-12-22 19:11:29 10

10 的协议,可用于寄存器式控制/状态接口。例如,Zynq XADC 使用 AXI4-Lite 接口连接到 Zynq PS。

2022-05-10 09:52:12 1949

1949 前面简单学习了关于GPIO的操作,本次将使用PL 端调用 AXI GPIO IP 核, 并通过 AXI4-Lite 接口实现 PS 与 PL 中 AXI GPIO 模块的通信。

2022-07-19 17:36:52 3224

3224 这篇文章记录ZYNQ7020的PS端的基本开发流程,关于PL端的开发流程,参考之前文章,这里放个超链接。

2022-07-24 18:12:57 5859

5859 MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线

2022-08-02 09:45:03 676

676 PL端和PS端一般通过AXI4总线通信,使用AXI4的PL模块会有相应c驱动文件,用于PL端模块的控制。这些驱动文件有裸机版本,也有linux版本,linux运行时,如果调用pl端模块就使用这些驱动即可。

2022-11-04 10:51:57 13842

13842 电子发烧友网站提供《将Zynq PS和PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29 2

2 S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53 1708

1708 ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,虽然 PS 端的 ARM 是硬核,但是在 ZYNQ 当中也要将 ARM 硬核添加到工程当中才能使用,FPGA

2023-08-11 09:36:34 4801

4801

/XC7Z100 SoC处理器设计的高端异构多核评估板,由核心板与底板组成。TMS320C6678每核心主频可高达1.25GHz,XC7Z045/XC7Z100集

2021-09-14 14:09:10 15

15 以axi_gpio_led_demo案例为例,演示基于PL端MicroBlaze软核裸机工程的编译与加载方法。适用开发环境:Windows7/1064bit、XilinxVivado2017.4、XilinxSDK2

2021-10-22 10:20:14 19

19 前言本文主要介绍PS+PL端异构多核案例的使用说明,适用开发环境:Windows7/1064bit、XilinxVivado2017.4、XilinxSDK2017.4。案例位于产品资料“4-软件

2023-01-03 15:50:37 18

18

正在加载...

电子发烧友App

电子发烧友App

![ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例 [图片]](https://file.elecfans.com/web2/M00/13/C2/poYBAGE3KSKAe6tQAAKow32f7wo059.png)

评论