Bypass电容的大小和计算方法 Bypass电容是一种常见的电子元件,用于绕过或降低电路中的噪声、干扰或漏磁磁通。它能够有效地将高频噪声或漏磁磁通通过一个低阻抗路径绕过,从而保持电路的稳定性和信号

2024-02-14 17:56:00 2974

2974 有人说用这个公式U=4.44f*kN*phi,其中U是相电压额定值,f是额定频率,kN是定子绕组每相有效匝数,phi就是磁链。这里的问题是定子绕组每相有效匝数我不知道呀,是不是有个大概的范围呢?向各位请教了。

另外,还有没有其他的方法来计算磁链给定值呢?

2024-01-10 07:38:54

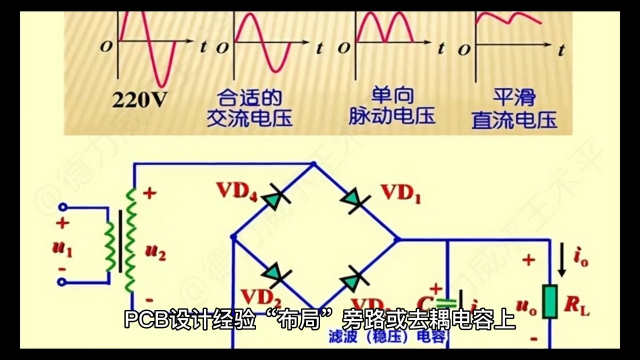

我们在电源滤波电路上可以看到各种各样的电容,100uF,10uF,100nF,10nF不同的容值,那么这些参数是如何确定的?

数字电路要运行稳定可靠,电源一定要”干净“,并且能量补充一定要及时

2024-01-09 08:25:59

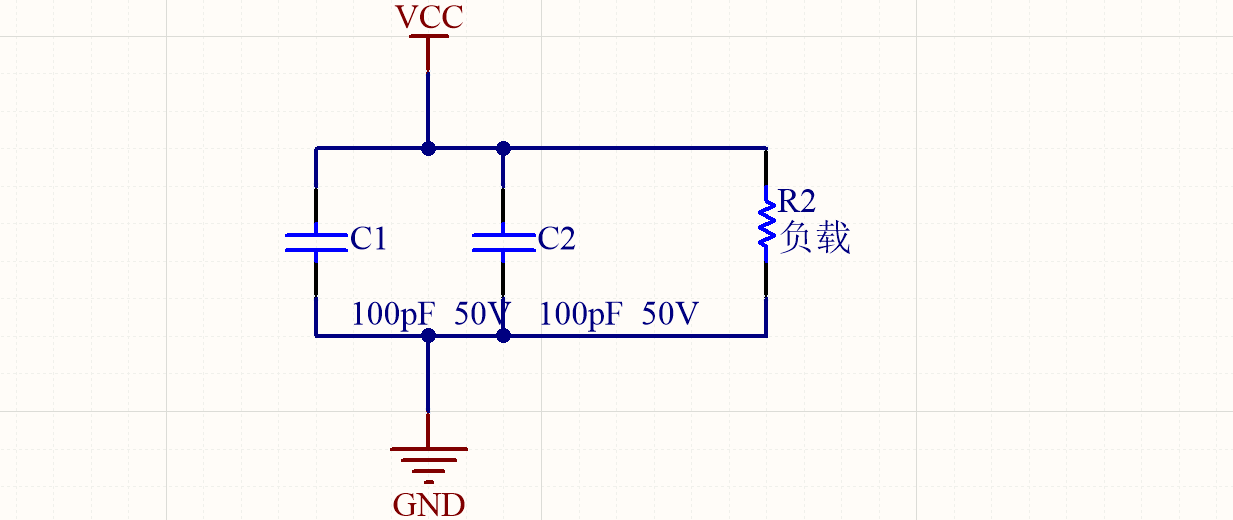

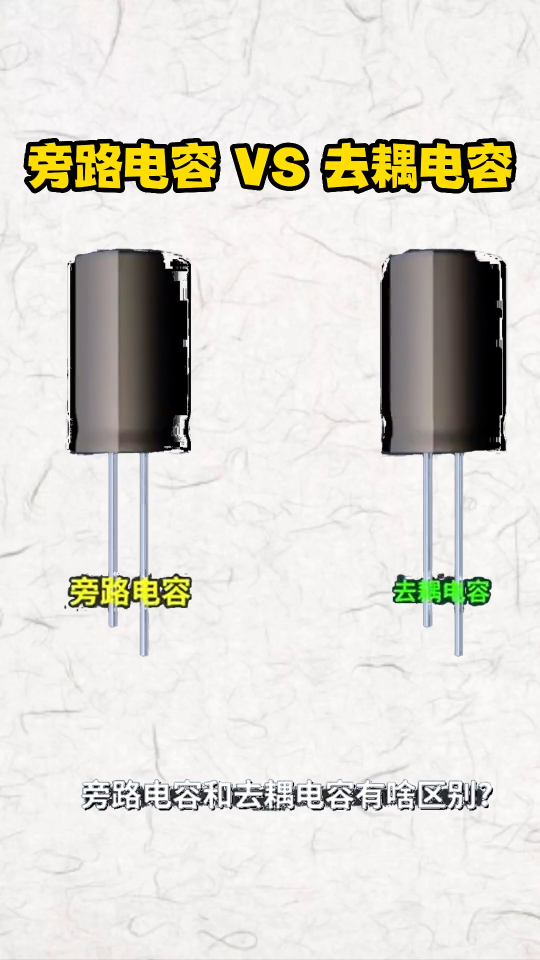

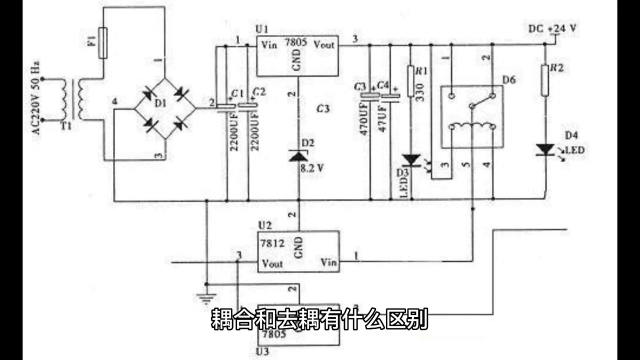

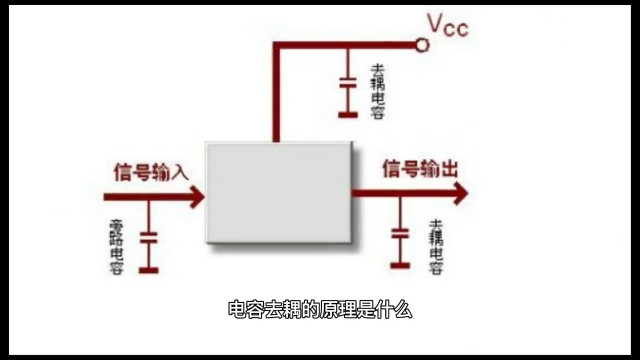

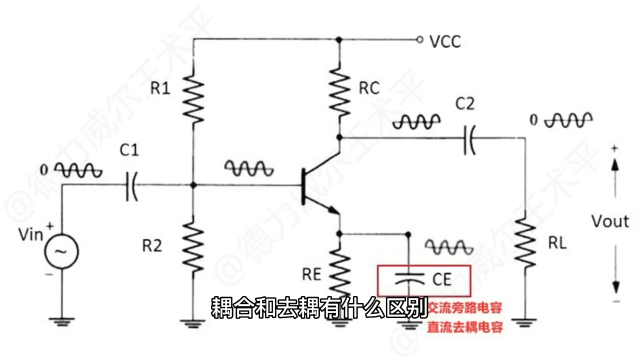

我知道在电源设计中,电源输入与输出都要滤波和去耦合,请问下怎么叫去耦电容?什么叫旁路电容啊??我知道概念,它们两者区别在于:旁路电容是把输入信号中的干扰信号去掉,而去耦电容是把输出信号中的干扰信号去掉;但是我不知道具体怎么区分?难道左边的是旁路电容,右边的是去耦电容吗?

2024-01-08 11:30:57

请较一下LDO(比如LT3045)和普通三端稳压(比如LT1083)输入电容与输出电容正确的计算方法,用书上的方法计算都感觉不对,我感觉用去耦的方式计算应该比较对一下,请教一下具体怎么配置吗

比如

2024-01-04 08:04:43

LTC4364规格书里的典型应用,低压输入VCC都是直接接VIN;36~72输入是通过电阻接VIN, 但是图上没有显示有接VCC的去耦电容,请问这种情况下VCC是否不需要去耦电容?谢谢

2024-01-04 07:55:12

电容充电时间计算是计算一个电容器从初始电压充电到目标电压所需的时间。这个时间可以由一个简单的公式来计算。在本文中,我将详细解释电容充电时间的计算公式,并提供一个详实和细致的说明,以确保你理解电容充电

2023-12-28 16:49:44 2317

2317

如上述截图(UG-1098 51页),有以下几点不明白:

1)IcalibrationFSP 0.0002这个值是怎么计算出来的,最好说明下推导过程,这个值和ADE9000的动态范围及互感器的比值

2023-12-25 08:14:39

如何计算安规电容漏电流?

2023-12-15 16:54:55 524

524

AD7173-8的评估板上的ADC输入端电容均未给出容值,还有其它部分电路的电容也未给出容值,有没有对应的参考值呢?谢谢!

截图如下:

2023-12-15 07:01:47

怎样设计和验证TRL 校准件以及TRL 校准的具体过程

2023-12-14 09:40:37 0

0 在使用AD5546做精密衰减的参考电路中,有一个反馈电容C6。这个电容值的大小应该如何随频率变化呢?

在参考输入是正弦波频率是150KHZ~1750KHZ频段的时候适合用多大容值的电容呢?

2023-12-14 06:07:39

请问AD7192噪声 和精度是怎样计算的?例如4.7HZ128倍时12NV有效值噪声怎么算出的精度22.5(20)

2023-12-06 08:03:41

为什么要计算电容器寿命?

2023-12-04 14:06:00 185

185

LTC7545按照下面的电路连接,这个是非官方标准的接法,想问下具体的增益计算公式是什么,VOUT和VIN以及数字code值之间的关系。

2023-12-04 07:27:12

请问怎样才能将SharcAudioToolbox导入SigmaStudio?具体如何操作?

2023-11-30 07:47:12

。

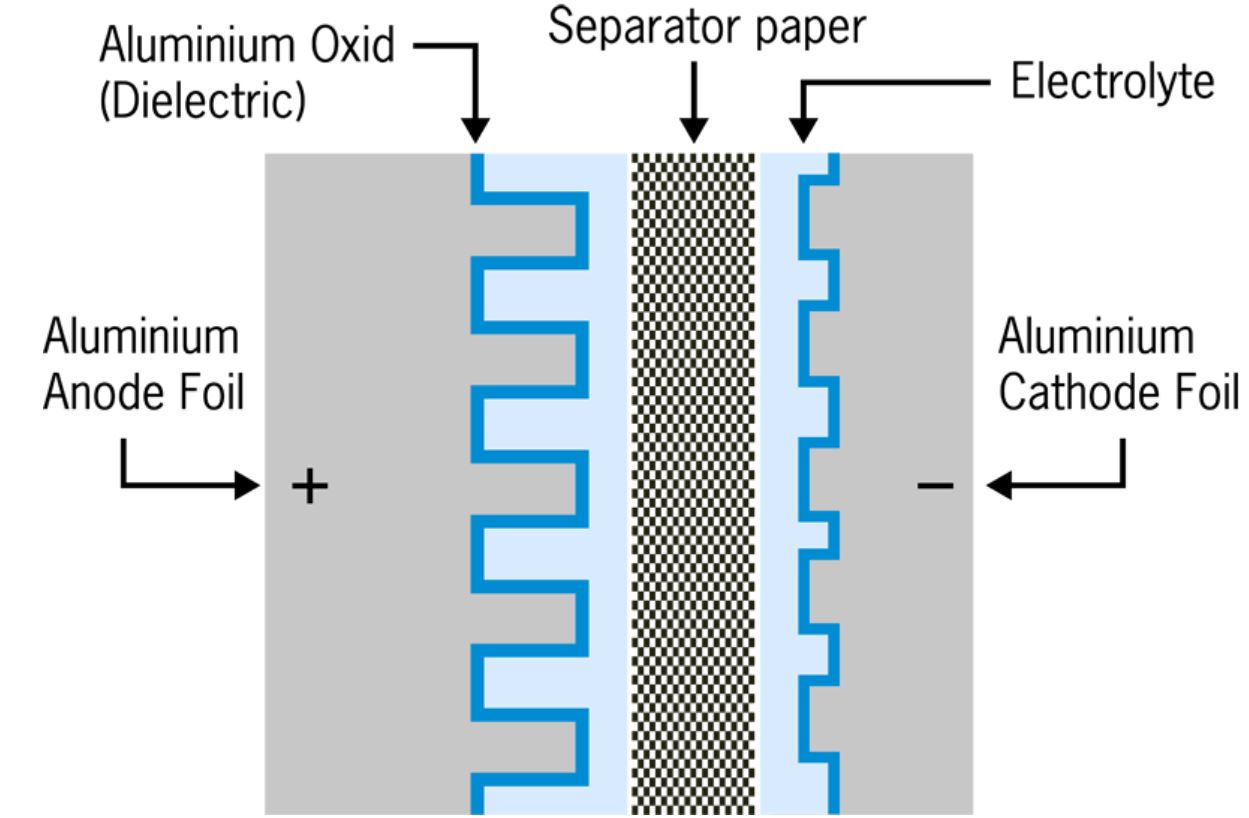

其实,这是容值不同的电容并联谐振的结果,也是本文要说的第二“振”。

分析起来也很简单,当一个电容的感性区遇上另一个电容的容性区,谐振峰就出现了。

综合考虑VRM和芯片内去耦,如果说第一“振”决定

2023-11-28 15:12:01

来至网友的提问:为什么IC需要自己的去耦电容?

2023-11-24 07:50:02

。

其实,这是容值不同的电容并联谐振的结果,也是本文要说的第二“振”。

分析起来也很简单,当一个电容的感性区遇上另一个电容的容性区,谐振峰就出现了。

综合考虑VRM和芯片内去耦,如果说第一“振”决定

2023-11-21 09:38:08

ADA4807-2的数据手册有关于容性负载的描述,其中图69可以看到,对于较大的电容,无需串联电阻来维持稳定性。

同时,图68可见,电容越小,需要的串联电阻越大

但是,按照之前学习的理论,运放

2023-11-17 12:14:36

去藕电容的容值该怎么去计算呢?

2023-11-01 07:29:30

贴片电容测试以后发现贴片电容的容值就有偏低的现象,是什么原因,是不是老化了,有什么解决的方法?

2023-10-30 08:12:15

什么时候会选择1uf的电容作为去耦电容

2023-10-30 06:45:40

CMRR(Common Mode Rejection Ratio)的绝对值越大对共模电压的抑制能力越强,本文主要讨论在实际应用中OPA关于CMRR的计算具体案例。

2023-10-25 10:36:00 1067

1067

去耦电容的容值是否有固定的标准,自己选择其他的容量会有影响吗

2023-10-23 07:21:33

高速先生成员--黄刚

当然这篇文章也还是针对高速信号的交流耦合电容,并不是用于电源的去耦电容,同时文章的灵感也来源于上一篇文章讲不同容值电容对高速信号原理上的效果差异。为什么我们在做高速设计的时候

2023-10-17 16:39:41

电容有移相作用,那移相具体是什么作用? 关于电容的移相作用,其实可以从三个方面来进行详细解析: 1. 从物理学角度来说,电容储存电荷,当电压变化时,电容器中的电荷会发生变化,这种变化会导致电容器产生

2023-10-17 16:15:46 1615

1615 会有隔直电容,做过类似硬件原理的朋友都知道,电容的容值一般就是100到几百nf级别的,有的用100nf,有的用220nf,差不多就是这个量级了。

大家用着也很习惯,只要链路的阻抗损耗等PCB参数优化

2023-10-13 16:28:01

首先大概说一下结论,两个相同容值和耐压值的电容,并联之后:耐压值不变,容值增加。C=C1+C2.串联之后:耐压值为两电容之和,容值减小1/C=1/C1+1/C2.

2023-09-26 10:14:45 1673

1673

在EMC设计中,电容是应用最广泛的元件之一,主要用于构成各种低通滤波器或用作去耦电容和旁路电容。大量实践表明∶在EMC设计中,恰当选择与使用电容﹐不仅可解决许多EMI问题﹐而且能充分体现效果良好

2023-09-20 08:22:28

相互光电隔离的数字地和模拟地之间要考虑到地点位平衡,采用电容连接,容值为1-10nf,对于这个结论,相信大部分情况是正确的。但是,有例外如下:产品是大概是把极其微弱模拟信号放大后让单片机ADC可以

2023-09-20 06:48:36

怎样选择合适的电容 电容是电子元件中的一种重要元器件,用于储存电荷和调节电压。电容的原理是根据介质电容比空气电容大的特性进行设计的,当电容器两端之间存在电势差时,电荷便会在两端之间积聚,形成电场

2023-09-08 11:28:50 1401

1401 在电源管脚上加电解电容可能会引发一些情况,具体影响取决于电容的性质、电源的特点以及电路的设计。

2023-09-05 09:36:56 223

223 y电容与漏电流的计算 电容是电学中的一种重要的元件,它可以在电路中储存电荷,并在需要时将其释放。在许多应用中,电容被用来滤波、稳压,以及作为时序电路的元件。然而,电容也会引起漏电流的问题,影响电路

2023-08-27 16:43:33 2961

2961 电容的电量如何计算 电容的电量是电学中的一项重要指标,指的是电容器内存储的电荷量。电子学的发展也促进了电容的广泛应用,电容器在直流还是交流电路中都有着重要的作用。在这篇文章中,我们将详细讨论电容

2023-08-27 16:43:31 6474

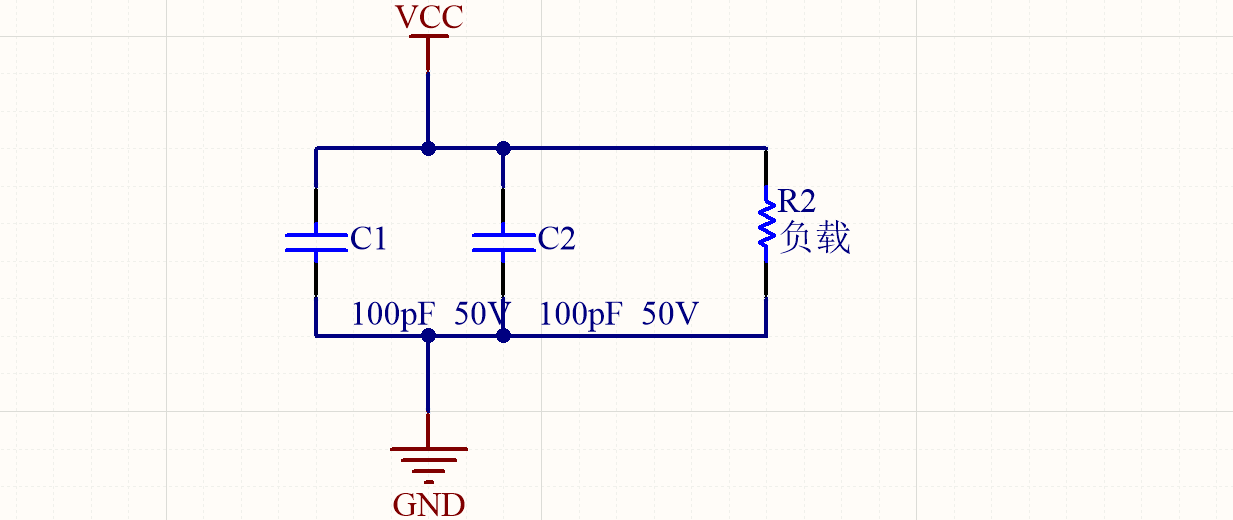

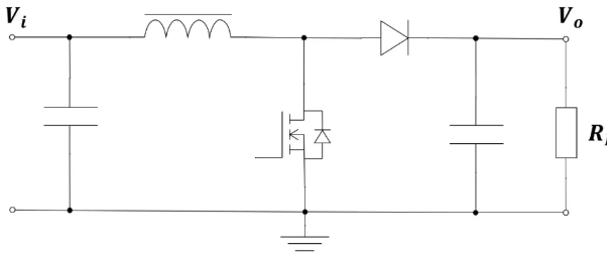

6474 我们之前了解过电容的作用,不外乎储能、滤波等作用。那么在Boost电源中又该怎样去选择电容的型号和电容容量呢?

2023-08-14 15:44:43 1052

1052

llc谐振中,的感性区域和容性区域是根据什么区分的呢,大多数论文中只是说不能工作工作于容性区域,这是为啥呢?

感性区域是谐振电感电流滞后于谐振电容的电压,为何就能实现zvs?

2023-08-01 10:48:44

DAB的输出滤波电容怎么计算?

2023-07-31 14:45:19

信号,输入到此引脚。用于控制输出电流。如何选型电流采样电阻?

4.RT/CT引脚(4脚):通过外部RT、CT两个电阻器连接到地线,用于设置内部振荡器的频率。如何计算4脚电阻和电容的值?

5.电感如何计算?

以上,假如从11.1V升压到56V

2023-06-08 13:57:41

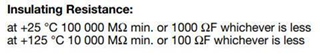

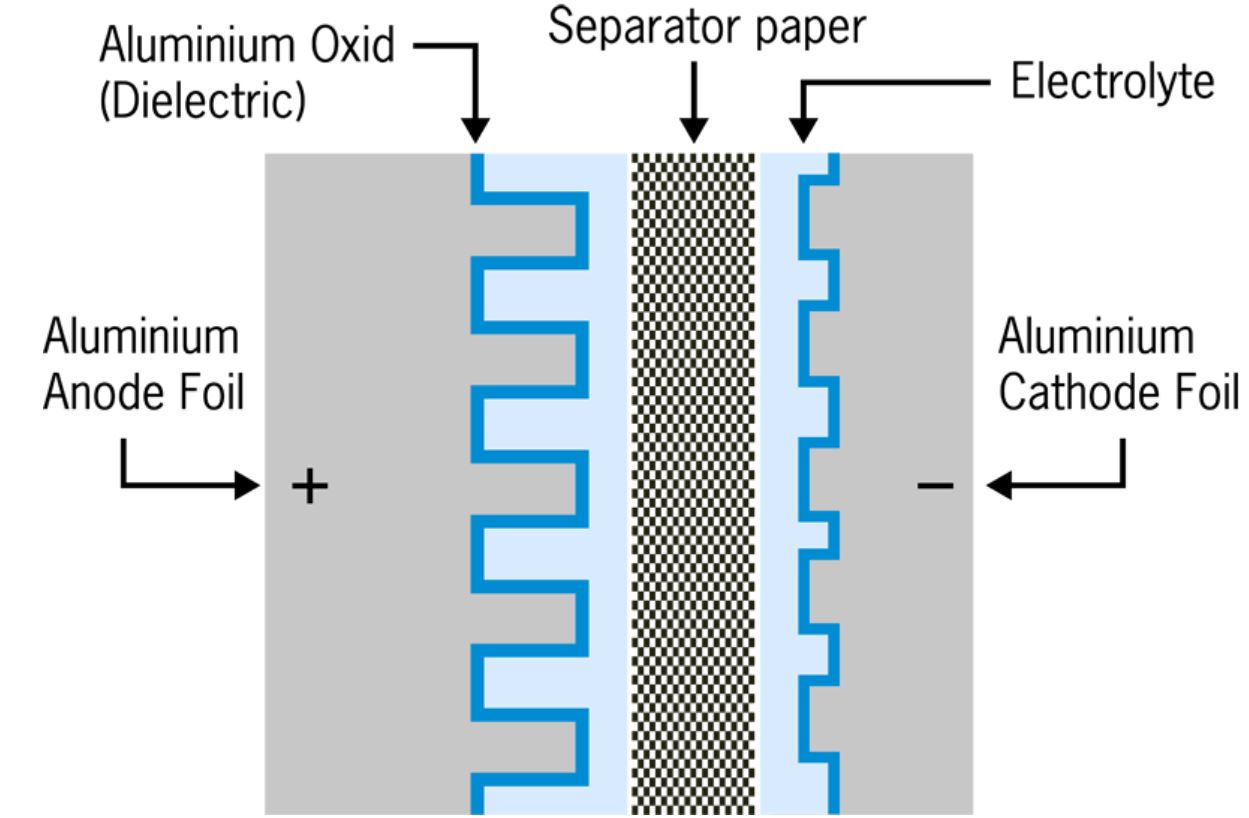

的结构

电容的结构组成可以简单分为三部分:电极+介质+电极,以下是片状多层陶瓷电容和铝电解电容的基本结构示意图:

电容的容值计算公式为:

C为电容值,单位法拉F,ε为介质介电常数,S为电极的面积,d

2023-06-07 09:02:22

高速先生成员--孙小兵

我们先来了解一下容性负载和感性负载对链路阻抗的影响。仿真链路模型如下图所示。链路中有三段50Ω的理想传输线,第一段和第二段之间增加一个电容模拟容性负载,第二段和第三段之间增加

2023-05-16 17:57:26

电容为什么能过滤波?多大的电容滤掉怎样的波呢?

2023-05-15 14:32:56

如输入为5V的电源,并联10个0.1u的电容后接地。为什么不是直接接一个1u的电容而是接10个0.1u电容。论容值 1u=0.1u*10 。求解!!

2023-04-21 18:09:28

去耦陶瓷电容在电源和地引脚的作用是什么?

2023-04-21 18:07:13

请问电源去耦和电源滤波是一回事吗?

2023-04-21 17:42:23

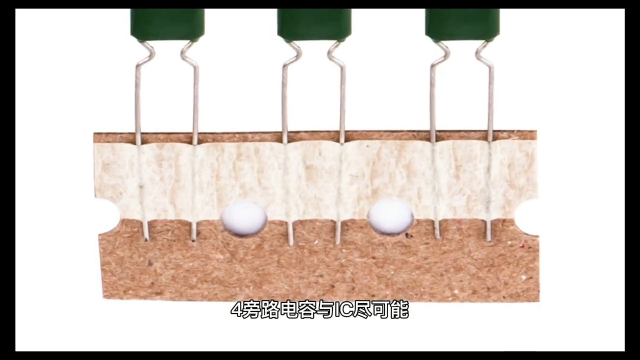

电源去耦电容为何要接近IC电源引脚?是什么原因呢?

2023-04-21 17:36:30

封闭环路可能造成干扰问题。 选择正确类型的去耦电容低频噪声去耦通常需要用电解电容(典型值为1F至100F),以此作为低频瞬态电流的电荷库。将低电感表面贴装陶瓷电容(典型值为0.01F至0.1F)直接

2023-04-21 17:27:59

通过遵循一些在PCB布局中放置去耦电容器的准则,了解如何减少二次谐波失真。 在上一篇文章中,我们讨论了需要对称的PCB布局以减少二次谐波失真。 在本文中,我们将看到,如果没有适当的去耦,我们

2023-04-21 15:24:03

电容为什么能过滤波?多大的电容滤掉怎样的波呢?

2023-04-20 17:28:44

删减。 IC 电源引脚的去耦电容的容值通常会比较小,如 0.1μF、0.01μF 等;对应的封装也比较小,如 0402封装、0603封装等。在摆放去耦电容时,应注意以下几点。 (1)尽可能靠近电源

2023-04-20 10:32:14

距离。 现在计算出的电感仅为0.12 nH,我们可以看到一对通孔可以提供远远优于走线的性能。 结论 我们已经讨论了在去耦电容器和位于同一PCB层上的高速数字IC之间建立高性能连接的一项重要技术。原作者:booksoser 汽车电子工程知识体系

2023-04-14 16:51:15

常用到的电感就是“贴片功率电感”,那大家如何保证选择的“贴片功率电感”是可靠的? 假设通过计算也好还是参考原厂设计也好,我们已经知道了电感值。那我们怎么去选型呢?下面是村田的“贴片功率电感”关键参数

2023-04-14 14:56:28

MHZ的区域造成阻抗。适合用于中频范围内(KHZ到MHZ)。也常用于去耦电路和高频率波。 特殊的低损耗陶质电容和云母电容适合与甚高频应用和微波电路。 为了得到最好的EMC特性,电容有更低的ESR(等效

2023-04-12 16:42:43

的交流干扰,但并不是使用的电容容量越大越好,因为实际的电容并不是理想电容,不具备理想电容的所有特性。 去耦电容的选取可按C=1/F计算,其中F为电路频率,即10MHz取0.1uF,100MHz取

2023-04-11 16:26:00

我现在正在制作一个新的原理图并放置旁路电容器。我正在查看设计指南文档 AN5426,它对 S32K144 的 100 针版本提出了以下建议:而具有相同微控制器的开发板具有用于去耦电容的功能:S32K148EVB 更进一步: 这 3 个中的最佳实践是什么?

2023-04-11 06:33:39

在RTT的ADC驱动框架里,adc只读回原始值,上层在根据adc的最大量程电压去换算成实际电压。这会带来一个问题:应用需要知道所使用的ADC通道的量程信息才能做具体换算。我的疑惑是,既然这个量程

2023-04-07 16:15:05

旁路电容,一般也被叫做去耦电容,在我们的布局中往往是紧靠着IC的电源和地脚,而且往往他的容值为0.1uF,今天我们就来说说为什么要这样做和这样选型。 一、为什么旁路电容紧盯着IC不放 电线

2023-04-03 14:42:53

BGA放置在PCB顶层,退耦电容放置在BGA下面的底层,如何移动退耦电容?

2023-03-29 17:24:49

电源端为什么要加那么多去耦电容,而不是用一个等效的大电容代替!如输入为5V的电源,并联10个0.1u的电容后接地。为什么不是直接接一个1u的电容而是接10个0.1u电容。论容值 1u=0.1u*10 。求解!!

2023-03-28 16:12:56

设计中最常用到的电感就是“贴片功率电感”,那大家如何保证选择的“贴片功率电感”是可靠的? 假设通过计算也好还是参考原厂设计也好,我们已经知道了电感值。那我们怎么去选型呢?下面是村田的“贴片功率电感”关键

2023-03-27 16:22:01

数字电路的直流供电,正负极之间为什么并联若干个不同电容值的解耦电容呢?

2023-03-24 17:23:57

正在加载...

电子发烧友App

电子发烧友App

评论