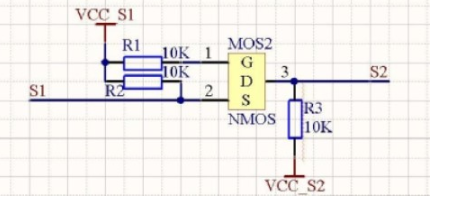

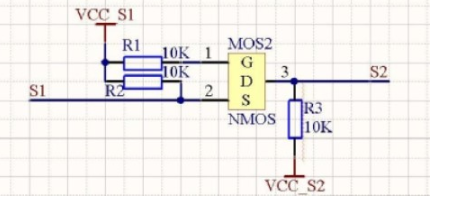

当你使用3.3V的单片机的时候,电平转换就在所难免了,经常会遇到3.3转5V或者5V转3.3V的情况,这里介绍一个简单的电路,他可以实现两个电平的相互转换。

2020-05-03 16:00:00 21469

21469

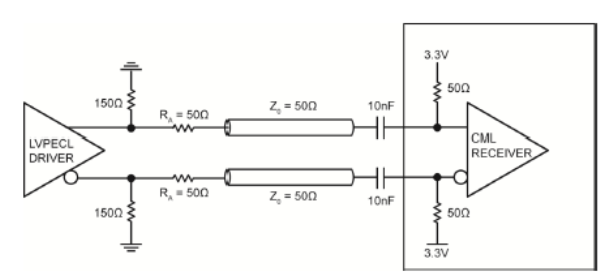

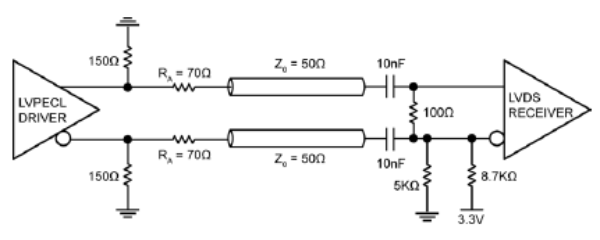

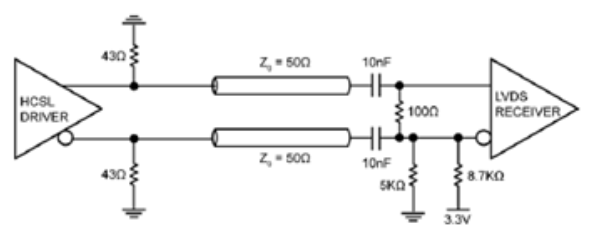

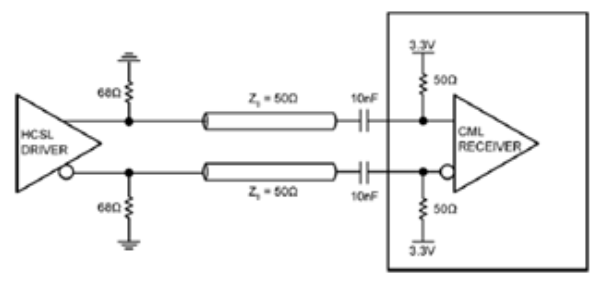

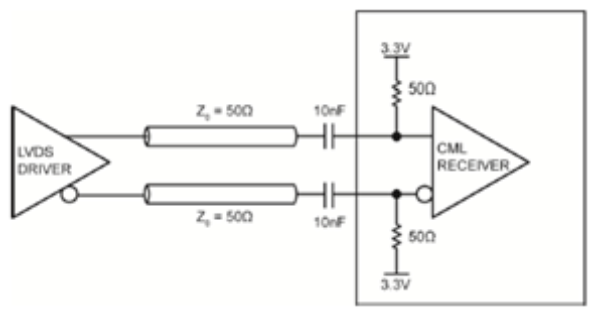

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。 下面详细介绍第二部分:不同逻辑电平之间的互连。 1、LVPECL的互连 1.1、LVPECL到CML的连接 一般情况下

2020-12-20 11:49:31 20435

20435

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。 下面详细介绍第一部

2020-12-20 11:39:59 35577

35577

协议转换器设计中使用 TLK10232 的方法。本文我们将回过头来了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之间转换。系统当前包含 CML 与 LVDS 等各种接口标准

2018-09-13 14:28:38

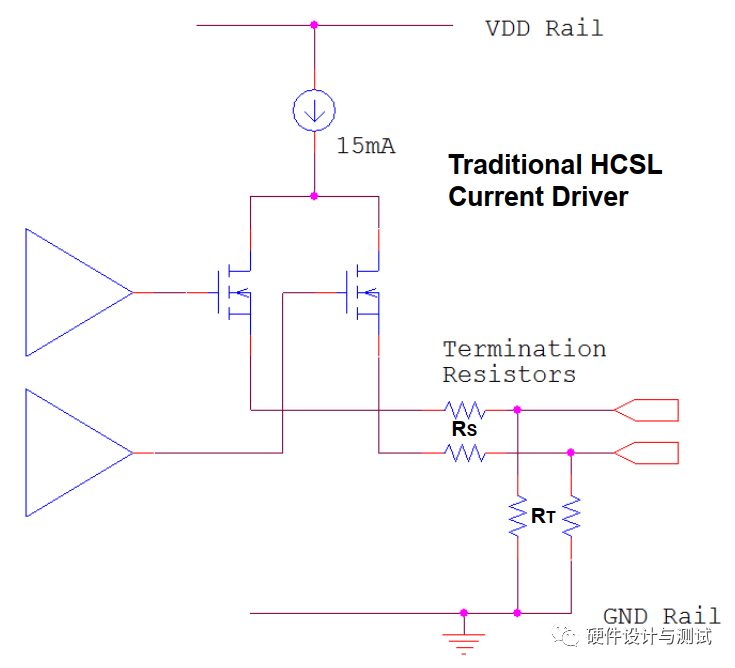

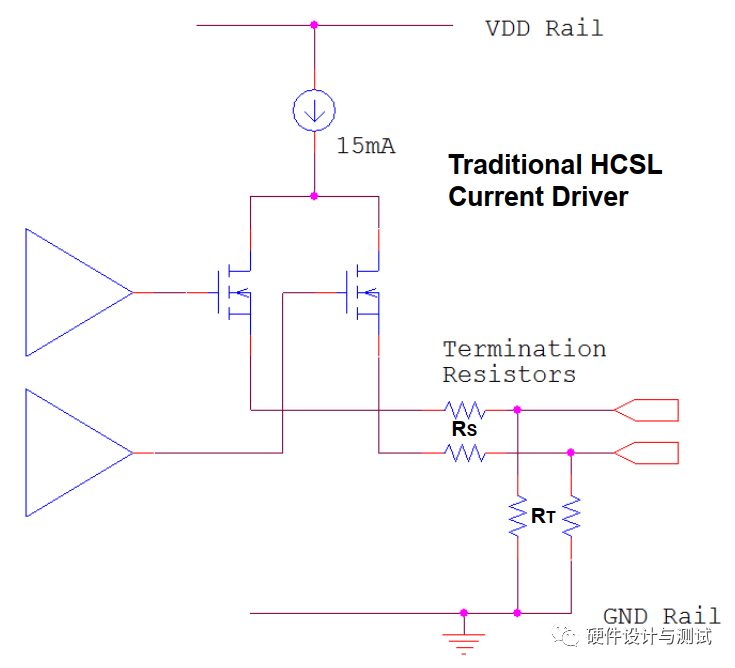

LVPECL(低压正射极耦合逻辑)是一种输入输出(I/O)技术,从半导体工艺无法集成高性能P 型设备与高性能N 型设备起就已出现。因此,在随后的HCSL 和LVDS等高速接口中,需要外部无源器件来

2019-07-08 07:05:43

SiTime晶振采用全硅的MEMS技术,由两个芯片堆栈起来,下方是CMOS PLL驱动芯片,上方则是MEMS谐振器,以标准QFN IC封装方式完成。封装完成之后,进行激光打标环节,黑色晶振表面一般打

2017-04-06 14:22:11

SiTime的产品包括高性能差分振荡器、扩频振荡器、压控振荡器和多组输出式时脉产生器,服务于容错云端储存器、企业服务器、10兆以太网交换机等高性能电子系统,及数码相机、LCD高清晰电视、多功能打印机等大批量消费电子。

2019-10-29 09:01:18

模式之外,剩下的参数就和普通有源晶振差不多了.目前市场主流差分晶振都是6脚贴片封装,常见的尺寸有7050和5032,当然SiTime还可以提供更小的3225封装体积.3,差分晶振的好处:①能够很容易

2016-07-16 16:08:15

需要用到固定差分晶振的可以下载哦

2017-02-08 14:52:49

本篇主要介绍常用的差分逻辑电平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。

2021-07-17 19:37:39

NB7V33MMNGEVB,差分时钟分频器评估板。 NB7V33M是一个4分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-21 09:44:22

及特点,通分为以下几类:普通晶振、温补晶振、压控晶振、温控晶振等。 晶振用一种能把电能和机械能相互转化的晶体在共振的状态下工作,以提供稳定,精确的单频振荡。在通常工作条件下,普通的晶振频率绝对精度

2013-10-25 15:56:33

我在使用AD7768的过程中,clk_sel拉高,使用外部晶振或者LVDS,使用LVDS的时候采样正常,但是用无源晶振的时候晶振无法起振,是不是除了clk_sel拉高之外还需要什么设置才会使用外部晶振

2023-12-11 08:22:54

我需要试用AD9106输出锯齿波,输出波形频率小于2KHz,原理图根据官网提供的Datasheet来设计的,只是将时钟源改为了180MHz的LVDS晶振,该晶振所输出的差分信号幅度大约为80mV左右

2018-08-20 06:30:21

各位专家好:近期在用AD9680做设计,资料中有提及时钟输入两种耦合方式:差分CML或者差分LVDS,现请问如果时钟为差分LVPECL的话,交流耦合如何接入呢,外部器件参数如何选择,盼复为谢!!!

2023-12-01 15:25:52

ADCLK946输出为LVPECL,是否可以直接给AD9739作为时钟驱动LVDS,在LVPECL转至LVDS电路设计上有需要注意的么?目前调试过程中,DAC失锁,怀疑时钟的输入幅度不满足

2019-01-03 10:41:18

比较器ADCMP606是CML差分电平输出,这里我只想用到CML的正极作为输出,负极接地,请问这样做是否可行?

2023-11-23 08:05:04

ASCII-十六进制相互转换 VI源码,仅供参考,如有错误欢迎指正!

2020-10-26 10:59:27

NB7V32MMNGEVB,差分时钟分频器评估板。 NB7V32M是一个差分2分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-20 09:41:47

PADS9.5 LOGIC 与 OrCad 原理图相互转换,可以么?前面有看到pads2004和orcad的转换,不过,9.5的不知道怎么转换?那位高人,帮需要此相关信息的新手,指点一下啊~~~最好是图字说明一下,如果一些辅助软件,最好有下载地址~~跪求~~~~~~~~~~~~~~~~~~

2013-06-04 12:19:13

经常会有朋友由于各种因素需要将PADS文件和PROTEL文件相互转换,下面介绍一下转换方法:一、PROTEL文件转换PADS使用Protel PCB TO PADS Layout

2011-09-21 11:03:34

SiT9122是一个高度灵活,高频率,可编程的 差分振荡器,支持LVPECL和LVDS输出信号类型。

2019-09-12 09:12:25

UNICODE与GBK的相互转化,在一些应用场景可能只有UNICODE编码然后中文形式显示在LCD屏上,这时可能需要转换为GBK编码。GBK与UNICODE没有直接对应的关系,通过查表方式将两者联系起来,具体实...

2022-01-12 06:58:13

的元器件也随之向小型化方向发展。而晶振作为电路的“心脏”,首当其冲要小体积、高精度,高性能、低成本,抗震好,品质一致性强,而这些特性恰恰是SiTime晶振自身的特点:1、灵活配置性—1-625MHz任意频率

2017-09-07 14:44:24

ADC转换过程:取样保持、量化和编码。 1) 采样保持:模拟电子开关S在采样脉冲CPS的控制下重复的开关。S接通时,ui(t)对C充电,为采样过程;S断开时,C上的电压保持不变,为保持过程

2023-03-16 18:06:43

有源差分晶振(LVDS/LVPECL输出)专业提供各类石英晶体频率元件;1,SPXO可提供SMD7050,5032,3225,全尺半尺型,频率不限,可根据客户要求定制;2,TCXO专注推广GPS

2011-03-29 21:10:52

采用的差分晶振电路,原理图如图所示。在上电测试中,晶振供电3.3V没问题,地也没问题。但是在放上晶振SIT9102后,引脚的电压发生变化,用万用表测得不再是原来的3.3V,而是1.258V。有哪位

2018-12-19 16:16:37

晶帆电子【CBEC】: 低压差分信号传输晶体振荡器(LVDS,LV-PECL输出),频率范围:30MHz~2000MHz;工作电压:1.8V,2.5V,3.3V,Low JitterSTM32专用

2012-10-13 13:34:13

您好,千兆以太网转与HSPI接口相互转换的范例有没?UDP下转换带宽有多少?能否跑满千兆以太网,谢谢!

2022-06-20 06:05:46

:

由于不希望增加时钟管理芯片增加成本,可否直接使用低抖动的有源晶振 2v5/3v3的输出如图连接?

或者 ,可否直接使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚?

2023-12-22 06:29:38

本文我们将回过头来了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之间转换。系统当前包含 CML 与 LVDS 等各种接口标准。理解如何正确耦合和端接串行数据通道或时钟通道

2022-11-21 07:59:56

如何实现了SPI/ASI的相互转换?

2021-06-08 06:32:48

请问一下如果ad9680的clk和sysref信号采用lvpecl格式输入,交流耦合的话前端网络如何设计。查看官方文档发现只介绍了cml和lvds的交流耦合模式,并没有提到lvpecl的交流耦合问题,希望版主或者设计过的大能给解决解决!!

2023-12-06 06:31:06

很惭愧,俺对基础的东西不是很了解,数字 1和字符 ‘1’ 怎么相互转换 ,因为在LCD1602和TFT彩屏显示涉及到相互转换,总是弄不清楚,请大虾给科普下,‘0’是代表字符 0 吗?

2014-05-26 11:22:18

很惭愧,俺对基础的东西不是很了解,数字 1和字符 ‘1’ 怎么相互转换 ,因为在LCD1602和TFT彩屏显示涉及到相互转换,总是弄不清楚,请大虾给科普下,‘0’是代表字符 0 吗?为什么 1+‘0’ 就转换为字符1了呢?字符1又怎么转换为数字1呢

2020-03-13 03:59:39

射频信号与蓝牙信号和wifi信号两者间是否可以相互转换

2018-05-19 16:07:22

晶振用一种能把电能和机械能相互转化的晶体在共振的状态下工作,以提供稳定,精确的单频振荡。松季电子介绍在通常工作条件下,普通的晶振频率绝对精度可达百万分之五十。高级的精度更高。有些晶振还可以由外加

2013-11-25 16:19:10

LVDS扩频输出。RS2CG5705B被配置为选择扩展和时钟选择。使用锁相环(PLL)技术,该电路采用25MHz的晶体输入,并在100MHz和200MHz的时钟频率下产生4对差分输出(HCSL)。它还

2024-01-24 17:31:16

本帖最后由 eehome 于 2013-1-5 10:03 编辑

大家都在用什么晶振呀?有用sitime硅晶振的吗,给小弟介绍一下,听说不错,谢谢。

2011-07-18 15:54:46

专业提供各类石英晶体频率元件;1,SPXO可提供SMD7050,5032,3225,全尺半尺型,频率不限,可根据客户要求定制;2,TCXO专注推广GPS产品应用的产品3,差分有源晶体振荡器,专注

2011-03-29 20:50:35

初步设想是LVDS输出端AC耦合,HCSL输入端用端接电阻加偏置。目前HSCL的供电端是0.8V。想问一下这个电平转换电路具体怎么实现呢,还有LVDS的差分峰峰值是能够满足HCSL的输入要求的吧?

2021-08-19 14:50:00

本文将详细讨论USB总线信号与 RS485总线信号是如何相互转换的?及PC机终端应用软件对USB接口芯片的各种操作。在此基础上用户可以根据不同需求,在终端应用软件中自行设计通信协议。

2021-04-09 06:07:52

采用的差分晶振电路,原理图如图所示。在上电测试中,晶振供电3.3V没问题,地也没问题。但是在放上晶振SIT9102后,引脚的电压发生变化,用万用表测得不再是原来的3.3V,而是1.258V。有哪位

2019-01-09 18:14:47

采用的差分晶振电路,原理图如图所示。在上电测试中,晶振供电3.3V没问题,地也没问题。但是在放上晶振SIT9102后,引脚的电压发生变化,用万用表测得不再是原来的3.3V,而是1.258V。有哪位

2019-03-08 09:21:37

我在使用AD7768的过程中,clk_sel拉高,使用外部晶振或者LVDS,使用LVDS的时候采样正常,但是用无源晶振的时候晶振无法起振,是不是除了clk_sel拉高之外还需要什么设置才会使用外部晶振

2018-08-03 08:05:09

请问ADF4350输出能直接驱动LVDS吗,或者和别的电平能匹配吗,能不能用DC耦合驱动CML或者LVPECL 或者LVDS的电平?

2018-12-12 09:10:29

CAD EAGLE和protel的电路图能相互转换吗?怎么转换? 会对电路有影响吗?谢谢!

2011-04-02 18:00:44

增加时钟管理芯片增加成本,可否直接使用低抖动的有源晶振 2v5/3v3的输出如图连接? 或者 ,可否直接使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚?

2018-11-02 09:25:09

。在选用晶振时,要考虑到电路需要的晶振输出类型,一般分电平输出和差分输出;电平输出:CMOS是最常用的一种输出类型,而差分输出:LVPECL,LVDS常用差分输出类型。不同的输出类型之间可不随便变换

2016-07-01 14:34:10

SJK-S7B0000M3C0420F5-7050HCSL输出差分晶振200mhz

2022-06-27 10:07:38

YSV220PR 压控差分晶振VCXO*10-1500MHz超宽频率范围,频率任意编程,并精确输出到小数点后6位*可编程晶振不仅交期具有优势,就频率而言,可编程晶振更是拥有灵活的可编程性质*应用于

2022-10-20 18:01:37

HEX文件和BIN文件相互转换的软件:

2009-09-13 15:28:40 374

374 1. 说明 Lontium LT2911R-D 是一款高性能转换器,可在 MIPI DSI/CSI-2/双端口 LVDS 和 TTL 之间相互转换,LT2911R-D 不支持 24 位

2022-12-26 15:39:59

可编程差分振荡器1.150-2100MHz超宽频率范围,频率任意编程,并精确输出到小数点后6位2.交期灵活3.超低抖动:0.15ps typ.4.输出类型丰富(LVDS、LVPECL、HCSL

2023-07-14 13:42:20

有源晶振(新品)1.可兼容多种电压(1.8V-3.3V)2.适用于高温环境(-40~+85℃) 可选+125℃3.输出类型丰富(LVDS、LVPECL、HCSL)4.超低抖动(0.15ps typ. ),抗震性强

2023-07-14 13:42:21

可编程压控晶振(新品)1.可兼容多种电压(1.8V-3.3V)2.宽牵引范围3.输出种类丰富(LVDS、LVPECL、HCSL、CML)4.超低抖动,抗震性强

2023-07-14 13:42:22

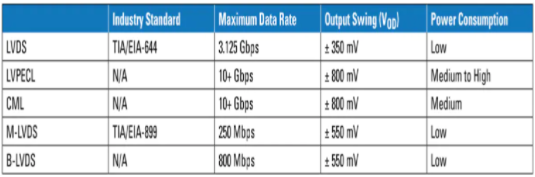

LVDS、PECL和CML介绍随着高速数据传输业务需求的增加,如何高质量地解决高速IC芯片间的互连变得越来越重要。低功耗及优异的噪声性能是有待解决的主要问题。芯

2010-04-10 10:02:54 34

34 (0 V to 4 V) receivers, allowing for the receipt of LVDS, LVPECL, and CML signals. The dual outputs are LVPECL drivers to provide high-spee

2010-08-26 16:06:59 27

27 LVDS/LVPECL/HCSL DXO13.5 to 200MHzPhase Jitter: 0.1ps(typ.)±25ppm @ -40~﹢85℃

2024-03-21 18:29:42

LVDS/PECL/HCSL/CML DXO150 to 2100MHzPhase Jitter: 0.15ps(typ.)可编程特色系列、快速交付

2024-03-22 17:15:27

LVDS/PECL/HCSL/CML VCXO15 to 2100MHzPhase Jitter: 0.16ps(typ.)可编程特色系列、快速交付

2024-03-22 17:57:55

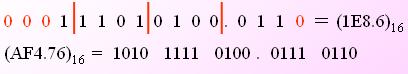

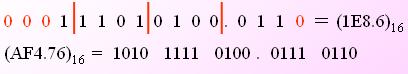

二进制数与八进制数的相互转换

(1)二进制数转换为八进制数: 将二进制数由小数点开始,整数部分向左,小数部分向右,每3位分

2009-09-24 11:27:30 18375

18375 二进制数与十六进制数的相互转换

二进制数与十六进制数的相互转换,按照每4位二进制数对应于一位十六进制数进行转换。

2009-09-24 11:28:58 9461

9461

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器

概述

The MAX9376 is a fully differential

2009-12-19 12:11:39 1566

1566

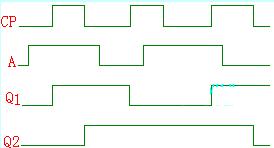

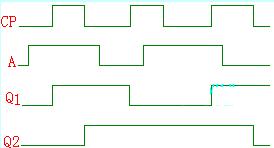

触发器的相互转换 基本触发器之间是可以互相转换的,JK触发器和D触发器是两种最常用的触发器,别的触发器可以通过这两种触发器转化得来,它们

2010-09-18 08:56:19 3941

3941

各种进制相互转换

1、其它进制转换为十进制 方法是:将其它进制按权位展开,然后各项相加,就得到相应的十进制数。

2010-09-19 11:29:50 3677

3677

数模、模数相互转化数模、模数相互转化数模、模数相互转化

2016-01-15 15:07:17 8

8 Delphi教程实现多线程IP和DomainName相互转换,很好的Delphi学习资料。

2016-03-16 14:58:46 7

7 本文档介绍了了TI有关电平转换芯片选型,包括5v,3.3v,1.8v等电压相互转换

2016-04-18 10:28:46 156

156 高速转换器三种最常用的数字输出是互补金属氧化物半导体(CMOS)、低压差分信号(LVDS)和电流模式逻辑(CML)。ADC中每种数字输出类型都各有优劣,设计人员应根据特定应用仔细考虑。这些因素取决于ADC的采样速率和分辨率、输出数据速率、系统设计的电源要求,以及其他因素。本文将讨论每种输出类型的电

2017-11-17 20:08:48 15264

15264

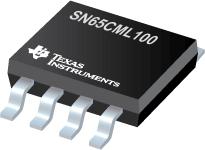

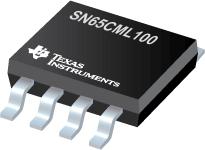

电子发烧友网为你提供TI(ti)SN65CML100相关产品参数、数据手册,更有SN65CML100的引脚图、接线图、封装手册、中文资料、英文资料,SN65CML100真值表,SN65CML100管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 10:08:54

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

2021-01-07 16:30:00 36

36 电子发烧友网为你提供详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-09 08:45:44 90

90 Labview中字符串和ASCII之间的相互转换的VI源码分享

2021-12-01 10:13:35 90

90 获得连接:LVPECL、VML、CML、LVDS 与子 LVDS 之间的接口连接

2022-11-04 09:52:13 3

3 延迟时间慢,功耗较低,噪声容限大等优点。差分晶振我们常见的输出模式有LVDS,LVPECL,HCSL,CML。那么LVCMOS属于差分晶振的输出模式吗?答案是否定的,

2022-07-07 14:29:12 1023

1023

手机、广播,电视等方式接收信息。而在远离地球的地方,比如在船上、飞机上、山区或者荒凉的地区,网络通话就无法使用,而只能使用卫星通话。 下面将分别介绍卫星通话和网络通话的原理和特点,以及如何实现相互转换。 卫星通话

2023-08-30 17:27:10 1123

1123 HCSL:高速电流控制逻辑(High-speed Current Steering Logic)是Intel为PCIe参考时钟定义的差分时钟,用于PCIe2.0电气规范中定义对RefClk时钟所定义

2023-09-15 14:39:54 2446

2446

电子发烧友App

电子发烧友App

评论