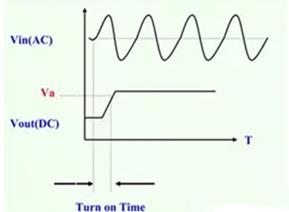

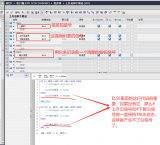

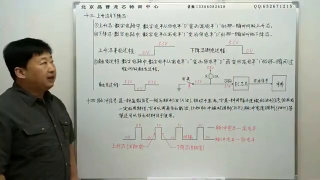

从字面上理解上升沿和下降沿是一个变量变化的时刻和一个无穷小的时间。但是plc程序中最小的时间单位是扫描周期,所以所谓的边沿就是一个扫描周期。

上例中使用的bTrig变量都是用来让下面的程序执行一个扫描周期的,也可以理解为执行bTrig的上升沿,和下面的编程效果一样:

上升功能块R_TRIG的功能实际上是检测输入变量,当输入变量从低电平变为高电平时,在第一扫描周期输出高电平,然后输出低电平。即,输出一个扫描周期。

与上升沿相同,下降沿检测输入变量从高到低变化的第一个扫描周期。

为了理解的上升沿和下降沿的含义,我们可以灵活地将其应用到程序中,比如让程序执行一个扫描周期,检测一个变量的上升/下降沿,通过设置我们上面例子中的IF语句来重置一个变量,或者在案例中执行一个条件后立即更改判断变量的值,等等。

本文原创首发 www.elecfans.com 源自 www.jcpeixun.com 转载请注明出处,谢谢。

编辑:ymf

上升沿和下降沿是什么意思?

- plc(453901)

- 高电平(20884)

相关推荐

stm32外部中断的边沿检测时,对上升沿或者下降沿是否有要求?

请问各位大佬,stm32外部中断的边沿检测时,对上升沿或者下降沿是否有要求,必须小于或者大于多少时间,或者在多少时间内必须上升或者下降多少V才算触发。在spec中只看到了最小是10ns就可以,同时边沿检测的电平是GPIO的VIH和VIL吗?

2024-03-20 08:31:04

使用HAL库配置TIM2采集PWM测量频率和脉冲宽度,如果将边沿极性配置为上升+下降沿?

使用HAL库配置TIM2采集PWM测量频率和脉冲宽度,如果将边沿极性配置为上升+下降沿,就可以一个通道测量频率和占空比了,但是如何在HAL_TIM_IC_CaptureCallback中分辨此次中断是由上升沿产生的,还是由下降沿产生的呢?

2024-03-12 06:52:38

HMC955LC4B

HMC955LC4B是一款1:2解复用器,支持高达32 Gbps的数据传输速率。该解复用器使用半速率时钟的上升沿和下降沿对01-02序列中的数据进行采样,并在上升沿上将数据锁存到差分输出。该解复用器

2024-03-03 13:22:40

示波器探头的工作原理与多功能应用详解

容性负载相当于在被测电路上并联了一个电容,对被测信号有滤波的作用,影响被测信号的上升下降时间,影响传输延迟,影响传输互连通道的带宽。

2024-02-26 10:23:59 621

621

621

621

串行通信协议的带宽是指什么?

在SPI和I2C等串行通信协议,两者带宽不一样,这里的带宽是指什么,传输速率还是其他什么?如果要求很高的传输速率,那么要求发送端要能很快的发送数据,要有很短的上升沿下降沿时间,高低位电平也维持很短

2024-02-08 18:04:50

上升沿和下降沿是什么意思 上升沿和下降沿有何作用

上升沿和下降沿是什么意思 上升沿和下降沿有何作用 上升沿和下降沿是在数字电路和信号处理中常用的概念,用于描述信号从低电平到高电平或从高电平到低电平的过程。 在数字电路中,信号通常是以离散的高电平

2024-02-06 14:50:04 1231

1231

1231

1231为什么脉冲数字信号的波形中其上升沿和下降沿展开后会有边沿震荡

为什么脉冲数字信号的波形中,其上升沿和下降沿展开后会有边沿震荡,求解释 脉冲数字信号的波形中,上升沿和下降沿展开后会出现边沿震荡的现象。这个现象通常是由信号传输过程中的反射、传导和辐射等因素产生

2024-02-06 14:49:41 245

245

245

245d触发器有几个稳态 触发器上升沿下降沿怎么判断

的上升沿和下降沿。 一、SR触发器 SR触发器是最基本的触发器之一,通过它可以实现存储器、寄存器等功能。 SR触发器有两个输入:S和R,以及两个输出:Q和Q'。在SR触发器中,有四种不同的输入组合,分别是: S=0,R=0:保持状态,稳态

2024-02-06 13:36:55 366

366

366

366plc中常用的编写程序的语言有哪些 plc中上升沿和下降沿怎么用

梯形图是PLC中最常用和最广泛支持的编程语言。它以线图的形式展现,使用继电器逻辑图形符号来表示逻辑关系和控制流程。

2024-01-10 15:04:17 143

143

143

143关于雅特力AT32F403A XMC复用模式驱动SRAM芯片

复用模式写时序图

SRAM写时序参数,看-55的

SRAM写时序1,有删减

.SRAM写时序2

锁存器74LVC273参数,算上上升沿和下降沿,延迟至少11ns

其中sram

2024-01-04 10:46:19

使用LT8705过程中上下功率MOS管的死区时间最小是多少?

您好!

我请教一个关于LT8705死区时间的问题:客户在使用LT8705过程中想确认上下功率MOS管的死区时间最小是多少?目前客户测试结果只有30ns左右。而根据MOS的上升沿和下降沿从20ns到40ns不等,有直通的风险,请问LT8705是怎么调节死区时间防止直通的?谢谢!!

2024-01-03 06:23:18

AD9266输出数据的沿和时钟的沿为什么是对齐的?

AD9266输出数据是在输出时钟的上升沿和下降沿处都有数据,我的电路的是二进制补码输出,10k的偏置电阻选用0.1%,电压0.5v,输出的DCS的时钟没有任何问题,频率和沿都很稳定,但是输出的数据的沿和时钟的沿是对齐的,这个和数据手册的说明不同!!!纠结了很久,跪求可能的原因!!!

2023-12-22 08:12:03

怎么确定AD9923A的VPAT_NUM和VSEQ_NUM这两个寄存器的值呢?

本人刚接触关于CCD的知识,正在利用AD9923A调试ICX209AK,但在配置寄存器时遇到了一些问题,想问问各位做过类似项目的:

1.对于CCD所需的H1、H2、RG等信号,怎么确定它的上升沿

2023-12-22 07:58:47

使用AD9266遇到的问题求解

使用?2.ad9266是CMOS DDR数据输出,通过管脚配置成二进制补码形式,DDR数据送到fpga,fpga选用xilinx的XC6SLX75,fpga内部在ad9266输出的ad_dco时钟的上升沿和下降沿

2023-12-22 06:59:24

ad9942 Hcounter在VD_X下降沿的后第七个cli上升沿置0,这里的作用是是什么?

问题1 如下图,Hcounter 在VD_X下降沿的后第七个cli上升沿置0,这里的作用是是什么,为什么在第七个位置置0?Hcounter 在ad9942内部那些信号或者序列会使用到? 有没有VD

2023-12-21 06:08:03

AD9781或是AD9783芯片的DCOP/DCON信号有什么用?

/DCON信号是AD给FPGA发信数据使用的,如上升沿时FPGA发送I路信号,下降沿时FPGA发送Q路信号,此时上升沿与下降沿需要在I或Q路信 号的中间位置么,就是保证上升沿与下降沿时,I和Q路信号有

2023-12-18 06:41:34

AD7764启动采样的时钟是MCLK还是SCO,如果是SCO,是上升沿启动还是下降沿启动?

最近在使用AD7764,有几个不懂的地方想请教一下:

1.AD7764启动采样的时钟是MCLK还是SCO,如果是SCO,是上升沿启动还是下降沿启动?

2.根据datasheet操作指引,上电后

2023-12-15 07:05:23

关于AD6688采样单音信号时比较奇怪的现象

的2211.84MHz,当我给一个2211.84MHz的正弦信号时,我期待得到的是一条直线,因为频率被移动到了DC了。但是采集回来的数据却很奇怪,在一段时间会是固定的,但是另一端时间会有上升沿和下降沿

2023-12-01 07:09:14

AD8561单+5V供电,方波输入,仿真下降沿比上升沿延时大是为什么?

AD8561单+5V供电,方波输入,仿真下降沿比上升沿延时大,如果双电源则延时则一样,实际应用是否也是这样?官网的pspice模型

2023-11-24 06:17:21

i.MX-6ULL --ElfBoard SPI接口介绍

主设备。一主多从情况如下图:

SPI 具有 4 种工作方式,时钟极性(CPOL)和相位(CPHA)共同决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据,并且一个片选信号可以设置一种模式

2023-11-21 10:19:05

ada4870是否可以用作直流线性电源?

100pf-10nf。

目前,我们已经验证的电路采用了类似于线性电源的结构,如图所示。

现在存在的问题是:图1中,三极管射级输出的直流电平存在较大的纹波,同时推完电路输出方波的上升沿和下降沿存在

2023-11-17 14:10:15

用AD8009放大500uv的方波,电压抬升怎么优化?

您好:

我希望放大一个500uv的1PPS方波,需要比较好的上升沿和下降沿性能,选用了AD8009,放大了300倍,测试后发现电压被抬高很多,是否是Vos引起的?

阅读相关帖子,我现在觉得我的设计有

2023-11-14 06:07:04

ADL5303光电二极管放大电路,低输入光抖动如何消除?

您好!

我使用ADL5303做光电二极管放大电路,因为响应速度的原因使用RC滤波电路会导致信号上升沿和下降沿时间变长,所以C118和C122都不能焊接,在低输入光时Vlog端有出现520KHZ、1MHZ、1.5MHZ的抖动,使用多种方法仍然无法消除,想寻求解决抖动的方法,谢谢!

2023-11-13 06:30:13

SPI的MISO管脚的波形上升沿和下降沿都有很大的弧度是什么原因?

示波器测量SPI通讯的CS,CLKMOSIMISO四颗线的信号,发现其他都很好,只有MISO的信号上升沿和下降沿都是有很大弧度的,是什么原因,如何解决?

2023-11-08 06:19:01

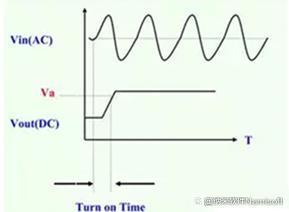

纳米软件电源模块测试之启动延迟和上升/下降时间

电源模块的启动延迟指从施加启动输入电压到输出电压达到电压额定值时所需的时间,上升时间是指电源模块从归零待机状态到启动状态所需的时间,下降时间指的是电源模块从工作状态到归零待机状态所需的时间。

2023-10-09 15:50:04 307

307

307

307

STC8系列单片机技术参考手册

、增强型 PWM、增强型 PWM 异常检测、ADC 模数转换中断、LVD 低压检测、SPI 中断、I2C 中断、比较器中断唤醒。STOP 模式可以由 INT0/INT1 端口上升沿/下降沿、INT2

2023-09-26 07:36:13

求分享K210裸机开发的寄存器手册

K210芯片使用PWM时,无法指定对齐下降沿或者上升沿,从0计数到loadcount2翻转为低,然后从0计数到channel[N].loadcount再翻转为高,无法通过current_value

2023-09-15 07:36:14

异步时钟同步疑惑

?也就是说采样异步时钟域信号时不打拍有什么后果?

另外,当高速时钟采样慢速上升沿或下降沿时,采样结果抖动怎么处理?比如DS18B20长线驱动时,波形上升沿和下降沿被长线的线间电容牵制导致波形边沿变化缓慢 ,采用打2拍方式能否有用?

此图采样到缓慢上升沿时,采样结果抖动波形。

2023-09-12 20:39:18

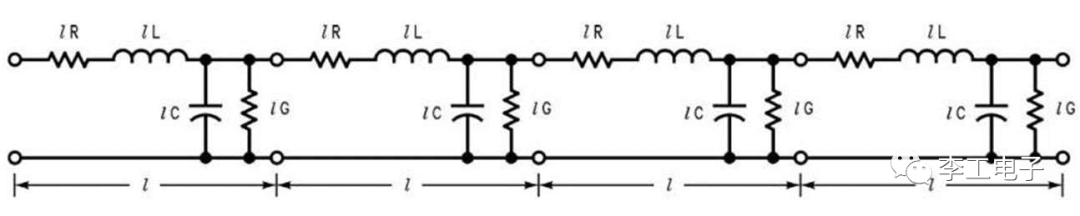

走线什么时候必须作为传输线考虑?

简单地说,传输线是由两条有一定长度的导线组成。如果信号在导线上的传输时间大于信号的跳变沿(上升沿/下降沿)时间的一半,则该走线判定为传输线。

2023-09-06 14:49:28 215

215

215

215

N9H20K51 gpio触发后一直未进中断是为什么?

输入模式

gpio_setintmode (GPIO_PORTE, BIT11, 1, 1);//设置中断模式上升沿 和下降沿

gpio_setsrcgrp(GPIO_PORTE,BIT11

2023-09-04 07:40:57

求助,在STM32上RTT可以使用IO中断模拟I2C从机接收数据吗?

使用IO中断在SCL上升沿和下降沿接收解析SDA的状态读取IIC数据,RTT的IO中断可以及时响应吗?

2023-09-03 09:49:08

有源晶振的电气参数:波形上升下降时间

晶振的输出波形为单端输出(Sine/Clipped Sine, CMOS/TTL) 和差分输出(LVPECL, LVDS, HCSL)。差分输出可以满足高速数据传输,应用于高速计算机,数字通信系统,雷达,测量仪器,频率合成器等。

2023-08-25 11:01:08 619

619

619

619

RTL设计规范有哪些?一个RTL用例设计介绍

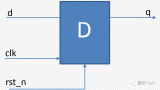

D触发器结构如下图所示,先有时钟上升沿,然后才有D的值赋给Q,没有上升沿Q值保持不变,时序逻辑在时钟上升沿/下降沿后才变化

2023-08-18 10:23:36 1149

1149

1149

1149

M0518LD2设置上升沿中断,但却也相应了下降沿中断是为什么?

M0518LD2 外部中断初始化时设置PD6为上升沿中断,但经查看波形发现 PD6在下降沿时也触发了中断,不知为何?

2023-08-18 06:13:40

ARM MultiTrace用户指南

·支持4位、8位和16位的数据端口宽度。

·支持半速率跟踪时钟,可在时钟上升沿和下降沿捕获数据。

·SoC电压可以在1.0至3.3V的范围内。

·轨迹信息以10 ns的分辨率进行时间标记。

·多重跟踪

2023-08-16 06:11:46

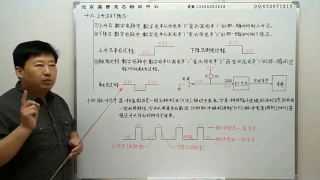

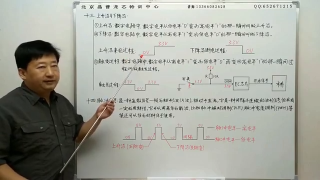

浅析PLC的上升沿与下降沿

有网友留言说:上升沿就是在信号从断开到接通的那一瞬间接通,下降沿就是在信号从接通到断开的那一瞬间接通。但是现在的问题它的实际用处是用在哪一些情况。我身边也有PLC可以做个什么实验来体验一下呢?

2023-07-26 09:24:30 1470

1470

1470

1470HMC855LC5是一款串行器

HMC855LC5是一款1:4解复用器,设计用于高达28 Gbps数据解串应用。 该器件使用半速率时钟的上升沿和下降沿来采样输入数据序列D0-D3,并将数据锁存至差分输出。 片上生成1/4速率时钟

2023-07-11 09:43:06

HMC854LC5是一款串行器

HMC854LC5是一款4:1多路复用器,设计用于28 Gbps数据串行应用。 多路复用器在输入时钟的上升沿锁存四个差分输入。 该器件使用半速率时钟的上升沿和下降沿来串行传输数据。 片上生成1/4

2023-07-11 09:39:21

HMC955LC4B是一款串行器

HMC955LC4B是一款1:2解复用器,支持高达32 Gbps的数据传输速率。该解复用器使用半速率时钟的上升沿和下降沿对01-02序列中的数据进行采样,并在上升沿上将数据锁存到差分输出。该解复用器

2023-07-11 09:32:57

HMC954LC4B是一款复用器

HMC954LC4B是一款2:1多路复用器,设计用于32 Gbps数据串行应用。 多路复用器在输入时钟的上升沿锁存两个差分输入。 该器件使用半速率时钟的上升沿和下降沿来串行传输数据

2023-07-11 09:30:01

关于N76E003的输入捕获的一些知识,不看后悔

的方式,支持双边沿,上升沿,下降沿,具体按照实际需求来

(5) 设置CAPCR,这个是关键的步骤,设置这个之后在发生了捕获事件之后就会直接将定时器的值清0,重新开始计时,这样的好处是我们完全可以不去

2023-06-25 08:42:33

ECSPI不是和标准的SPI重合吗?

根据 IMX6ULLRM,它读取当相位控制 (ECSPI_CONREG[PHA]) 位置位时,发送数据将在 SCLK 的上升沿移出,接收数据在 SCLK 的下降沿锁存。最高有效位在第一个 SCLK

2023-06-08 09:44:27

西门子1200上升沿和下降沿的操作流程

通过上面的这个程序,我们就得到了上升沿信号和下降沿信号。比如说,当形参“I_请求1”的实参”I0.0”从0变1时,那么形参“上升沿信号”就变为了1。此时,我们就可以用这个形参=1的信号来做事情了。

2023-06-01 16:49:57 2846

2846

2846

2846

如何从ISR的上升沿读取GPIO?

我在 GPIO_INTR_ANYEDGE 上配置了一个 GPIO ISR。

我想在 ISR 中知道它是上升沿还是下降沿。

怎么做?

如果我只是在 ISR 中读取 GPIO 状态,它几乎总是 0,即使

2023-05-30 10:37:08

是否可以让FSYNC数据在上升沿而不是下降沿触发限定符?

31 位。我们计划使用限定符来同步 32 位数据和 FSYNC。是否可以让 FSYNC 数据在上升沿而不是下降沿触发限定符?

2023-05-24 10:30:57

IMX8MN如果我们配置GPT在上升沿/下降沿触发中断,如何知道中断是由下降沿还是上升沿触发?

以获得一个数组,其中包含每个 0 和 1 转换的持续时间

我的想法是在输入捕获模式下使用 GPT 1,配置为触发上升沿和下降沿的中断,并在中断中获取位 (0/1) 的持续时间并将其存储在数组中

2023-05-12 06:35:59

在时序电路里如何利用一个信号的上升沿和下降沿采样数据呢?

外部输入一个周期信号和一个数据,我要利用这个周期信号的上升沿和下降沿采样数据。除了利用高频时钟去检测周期信号的上升沿和下降沿变换外,还有什么方法?

2023-05-10 10:36:28

在时序电路里如何利用一个信号的上升沿和下降沿采样数据呢?

外部输入一个周期信号和一个数据,我要利用这个周期信号的上升沿和下降沿采样数据。除了利用高频时钟去检测周期信号的上升沿和下降沿变换外,还有什么方法?

2023-05-10 10:35:59

是否有可能在不添加/使用FTM1模块和其他通道的情况下为PWM的每个上升沿或下降沿束获得中断/回调?

我正在使用S32K32118 EVB和S32DS.3.5

通过S32 配置工具,我在 FTM0、CH0 上创建了一个 PWM 波形。

我想知道是否有可能在不添加/使用 FTM1 模块和其他通道的情况下为 PWM 的每个上升沿或下降沿(或至少在新周期开始/结束时)获得中断/回调 。

2023-05-04 08:27:26

安捷伦AFG3102波形发生器

长达128K的任意波形。在脉冲波形上可以单独设置上升沿和下降沿时间。可以将外部信号连接,并叠加到输出信号中。双通道型号输出可生成两个完全相同或截然不同的信号。所有

2023-04-18 10:05:02

CH32V103基础教程9-输入捕获

捕获可对输入信号的上升沿、下降沿或者双边沿进行捕获,其捕获原理为:当发生并捕获信号跳变沿之后,计数器(CNT)值将被锁存到捕获比较寄存器(CCR)中,将前后两次捕获到的CCR寄存器中的值相减,即可计算出频率或者脉宽。如果捕获脉宽时长超过捕获定时器的周期,会发生溢出,此时需要进行额外处理。

2023-04-14 16:17:39

KEA8 KBI下降沿和上升沿问题求解

我正在FRDM - KEAZ128 上开发新代码,我需要在下降沿和上升沿拦截单个引脚上的中断,但从文档来看,似乎只能使用下降沿或上升沿。它是否正确?如果没有办法在两个边缘设置 IRQ,唯一的其他方法是使用 ACMP 外围设备或“更智能”的方法可用?

2023-03-23 07:53:32

电子发烧友App

电子发烧友App

评论