。

**·**接地和电源分布:确保晶振附近的接地和电源分布合理,没有电源或地线过孔导致的信号干扰。

4. 软件程序配置检查

**·**时钟系统配置:查看软件程序中关于时钟系统的配置,确保晶振引脚被正确配置为

2024-03-06 17:22:17

如果晶振的外接电容值选择不当,可能会对电路产生以下影响 :

1.频率稳定性: 电容值过小可能导致频率稳定性下降,容易受到外界因素的干扰。电容值过大可能会使频率偏离标称值。

2.起振问题: 电容值

2024-03-04 11:33:16

上电USB接口识别不出,排查发现19.2M晶振未起振,请问这是啥原因,匹配电容更换了也不行。

2024-02-27 06:18:43

在使用PSOC 4000S系列 CY8C4025LQS-S411做汽车上的触控应用时,我需要使用外部晶振,外部有源晶振有两种类型的波形输出,正弦波和方波,我想请教一下应该选用什么样输出波形的晶振呢?我的系统是5V供电的,是否有推荐的外接有源晶振型号?

2024-02-21 07:36:07

的微波信号皆能传致载点的目的,不会有信号反射回来源点,从而提升能源效益。阻抗匹配关系着系统的整体性能,实现匹配可使系统性能达到最优。而阻抗匹配是针对射频等而言的,对于功率电路则不适用的,否则会烧掉东西。 为什么要测试阻抗?元件的阻抗受很

2024-01-24 10:23:30 148

148

我的应用场景是这样的,M487JIDAE有114个IO口,其中有两个需要外接晶振,这样只剩下112个IO口;正好项目需要用到114个IO,所以希望不外接晶振,然后使用内置晶振也能够跑USB例程。目前M487JIDAE的开发包里面也没有找到使用内置晶振跑USB例程的写法,小白刚入门,请教一下大家怎么处理,谢谢!

2024-01-16 06:15:15

无源探头的阻抗匹配 示波器的无源高阻探头具有非常广泛的使用度,工程师们经常会把探头接在不同的示波器上,或者给示波器接入不同的探头。而发生更换后的新系统中,示波器通道的输入阻抗与探头的阻抗往往不匹配

2024-01-12 11:11:35 136

136

最近在用这个芯片,注意到例程中使用的都是内部16Mhz的 HFOSC,那么如果我不想接外部晶振的话可以吗?外接的两个引脚应该如何处理呢?

2024-01-12 07:54:54

1、我在使用ADuC7020时,在外部晶振上是按照中文说明书上P88页 ,没有在晶振两头放匹配电容,现在使用时发现晶振有时候不能起振

想问下放不放匹配电容对起振是否有影响?

2、关于

2024-01-12 07:35:22

MCU的晶振下到底该不该铺铜,有些资料说最好铺铜,有些说最好不要铺铜??求各位高手解答!!!!

2024-01-12 06:56:40

对于电子工程师而言,晶体和晶振是电路中不可或缺的关键元件,尤其在涉及到时钟信号和同步操作时。虽然两者在功能上有着相似之处,但在实际应用、电路设计以及布局布线等方面却存在着显著的区别。本文将详细对比

2024-01-04 11:54:47

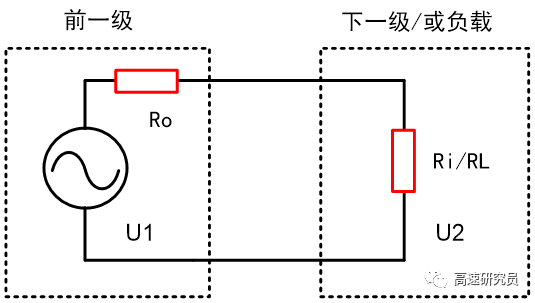

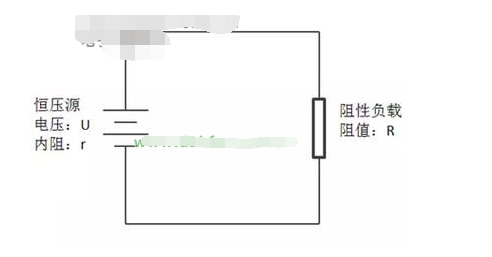

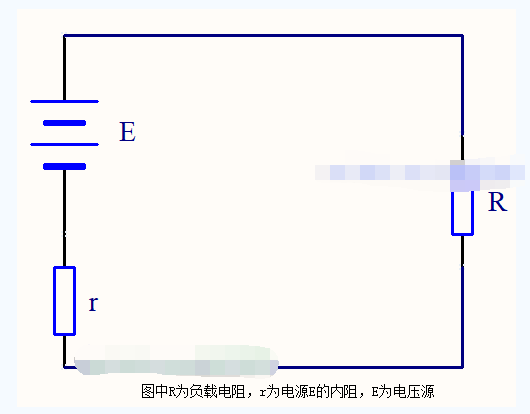

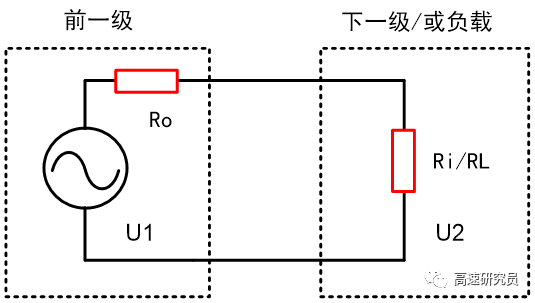

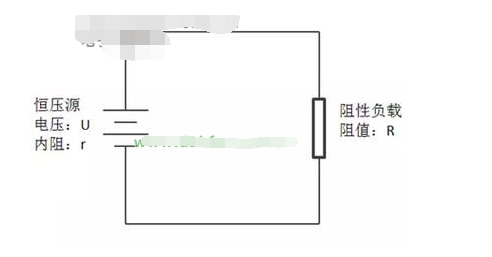

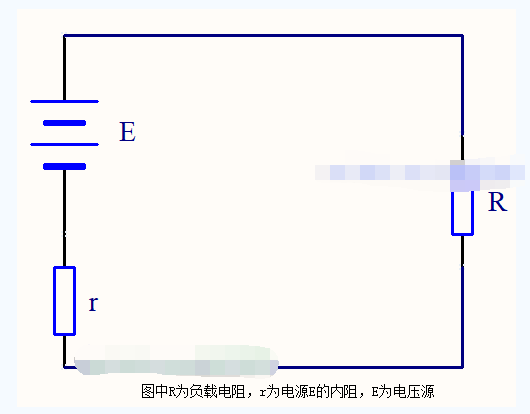

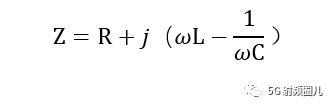

(虚部)。 其中电抗又包括容抗和感抗,由电容引起的电流阻碍称为容抗,由电感引起的电流阻碍称为感抗。 阻抗匹配的理想模型 射频工程师大都遇到过匹配阻抗的问题,通俗的讲,阻抗匹配的目的是确保能实现信号或能量从“信号源”到“负载”的有效传送 其最最理想模

2024-01-02 16:59:13 395

395

ADE7880最小系统:AVDD,DVDD,REF都正常,使用16.384MHZ晶振不起振,为什么换用5.9MHZ晶振起振,晶振电容都是20PF。另外换用其它频率晶振,ADE7880可以正常工作吗?

2023-12-26 07:53:01

AD2S1210需采用同一个晶振,有源晶振与无源晶振会有影响吗?

2、两片ad2s1210(粗机与精机)数据读取是先后对于数值的正确有影响吗?

3、就是下面这个电路(附件中)通过SPI总线读取数据的接法正确吗?

谢谢!

2023-12-22 06:23:59

什么是阻抗匹配?影响阻抗的因素? 阻抗匹配是在电子电路中为了提高功率传输效率而进行的一种电性特性调整方法。当能量从一个电路传输到另一个电路时,如果两个电路之间的阻抗不匹配,就会发生功率反射,这导致

2023-12-21 11:31:33 394

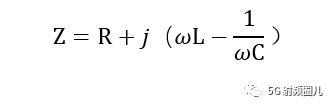

394 和输出端口的阻抗相匹配,从而最大程度地传输信号,并最小化信号的反射和损耗。 在了解阻抗匹配的概念和原理之前,我们首先需要了解一些基本的电路理论。阻抗(Impedance)是指电路中的电阻、电感和电容的整体特性,它包含了电路元件对电流和电压的阻

2023-12-18 13:39:56 479

479 晶振电路的并联电阻有什么用?

在晶振电路中,并联电阻是一个重要的元件,它与石英晶体谐振器并联连接。并联电阻的作用主要有以下几点:1.频率调节

并联电阻可以调节晶振电路的频率。当并联电阻的值发生变化

2023-12-13 09:38:27

请问AD9956如果选择直接用外部晶振时钟,对晶振的频率有要求吗?一定要400M,还是只要不超过400M就可以,比如20M。谢谢!

2023-12-13 08:55:39

我在使用AD7768的过程中,clk_sel拉高,使用外部晶振或者LVDS,使用LVDS的时候采样正常,但是用无源晶振的时候晶振无法起振,是不是除了clk_sel拉高之外还需要什么设置才会使用外部晶振

2023-12-11 08:22:54

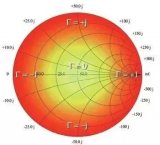

RF射频电路为什么选取50欧姆作为阻抗匹配的数值呢?这个数值是怎么确定下来的,背后有什么意义? 阻抗匹配是RF射频电路设计中非常重要的一个概念,它涉及到信号的传输效率和功率的最大化。通常情况下,RF

2023-12-07 13:37:52 1172

1172 设计时,AD2S1210的时钟输入采用8.192MHZ的有源晶振,选择晶振时对有源晶振的功率有什么要求???一个有源晶振能不能给两个AD2S1210芯片提供时钟输入???感谢!

2023-12-07 07:07:43

AD9249-65怎么外接晶振?有一个65M的晶振,如何接?问题二是差分信号线是否可以在VIVADO上面采集?问题三采集的时候是否需要input clk+和clk-?接多大的时钟信号?以及多大的电压?

2023-11-15 06:20:09

自制arduino最小系统,晶振必要加10k电阻来起振?

2023-11-07 07:34:03

我想问一下altera系列CPLD芯片支持的外接的晶振的最大时钟频率从手册的什么地方能查到,有那个高手能跟我讲一下的?

2023-11-06 07:49:34

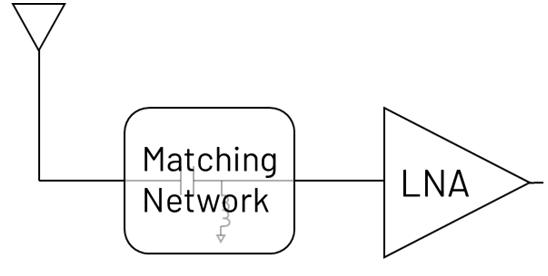

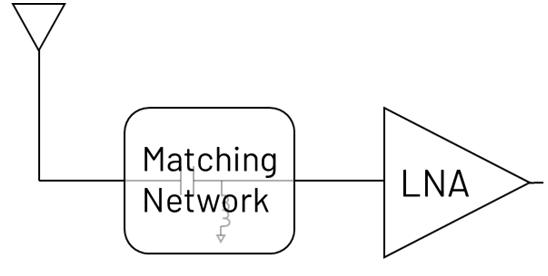

阻抗匹配是一个较大的话题,根据具体的频率和使用场景,大概可以分为4个模块讨论。分别是:电路匹配、传输线匹配、天线匹配、噪声匹配。

2023-11-03 11:50:07 696

696

外部晶振断电内部晶振是不是迅速起电

2023-11-03 08:02:15

非常重要,因为在高速数字和模拟电路中,信号频率通常在数兆赫或甚至更高的范围内运行。如果信号阻抗不匹配,就会导致信号反射、串扰、噪声等问题,从而影响信号稳定性和可靠性。 阻抗匹配的定义是在不同电路元件之间实现阻抗的匹配,

2023-10-30 10:03:25 919

919

晶振的作用是啥?只是为了提供时钟周期吗?

2023-10-25 07:19:37

AT32MCU时钟配置错误或晶振大小选择错误导致异常在时钟配置错误或晶振大小选择错误的情况下,下载代码到开发板导致无法继续进行debug或再次下载的一系列异常情况

2023-10-23 07:12:15

阻抗匹配网络有L型、派型、T型,各有什么优缺点? 阻抗匹配网络有L型、派型、T型,这些网络用于匹配源和负载之间的阻抗,以确保信号传输的最大功率。在阻抗匹配网络之前,如果源和负载之间的阻抗不匹配,则会

2023-10-22 14:25:30 3196

3196 低噪声放大器输入端和输出端匹配原则是什么?阻抗匹配的目的是什么? 低噪声放大器输入端和输出端匹配原则是什么? 低噪声放大器是电路系统中的一个非常重要的部分,利用它可以增强信号的弱度并减少噪声的干扰

2023-10-20 14:55:47 870

870 为什么高频小信号谐振放大器中要考虑阻抗匹配?如何实现阻抗匹配?常用有哪些连接方式? 一、高频小信号谐振放大器的介绍 高频小信号谐振放大器,是一种广泛应用于无线通信、雷达、卫星通信、微波通信等领域

2023-10-20 14:55:44 679

679 采用容感元件进行阻抗匹配,实测结果与理论仿真完全相反,可能是什么原因? 采用容感元件进行阻抗匹配时,理论仿真与实测结果完全相反,可能有以下几个原因: 1.元件本身参数误差 在使用容感元件进行阻抗匹配

2023-10-20 14:37:44 272

272 的可靠性也很高。

四、广泛应用

可编程晶振被广泛应用于各种通讯设备、网络设备、GPS接收器、频谱分析仪器等需要频率控制的设备中。它可以满足不同的频率需求,从而为这些设备的稳定运行提供了重要保障。

五、优点

2023-10-14 17:38:14

stm32有内部晶振,为什么还要用外部晶振?

2023-10-13 06:19:46

为什么高频小信号谐振放大器中要考虑阻抗匹配?如何实现阻抗匹配?常用有哪些连接方式? 高频小信号谐振放大器中要考虑阻抗匹配的主要原因是为了提高其性能和效率。阻抗不匹配会导致信号反射和损耗,影响谐振

2023-10-11 17:43:07 869

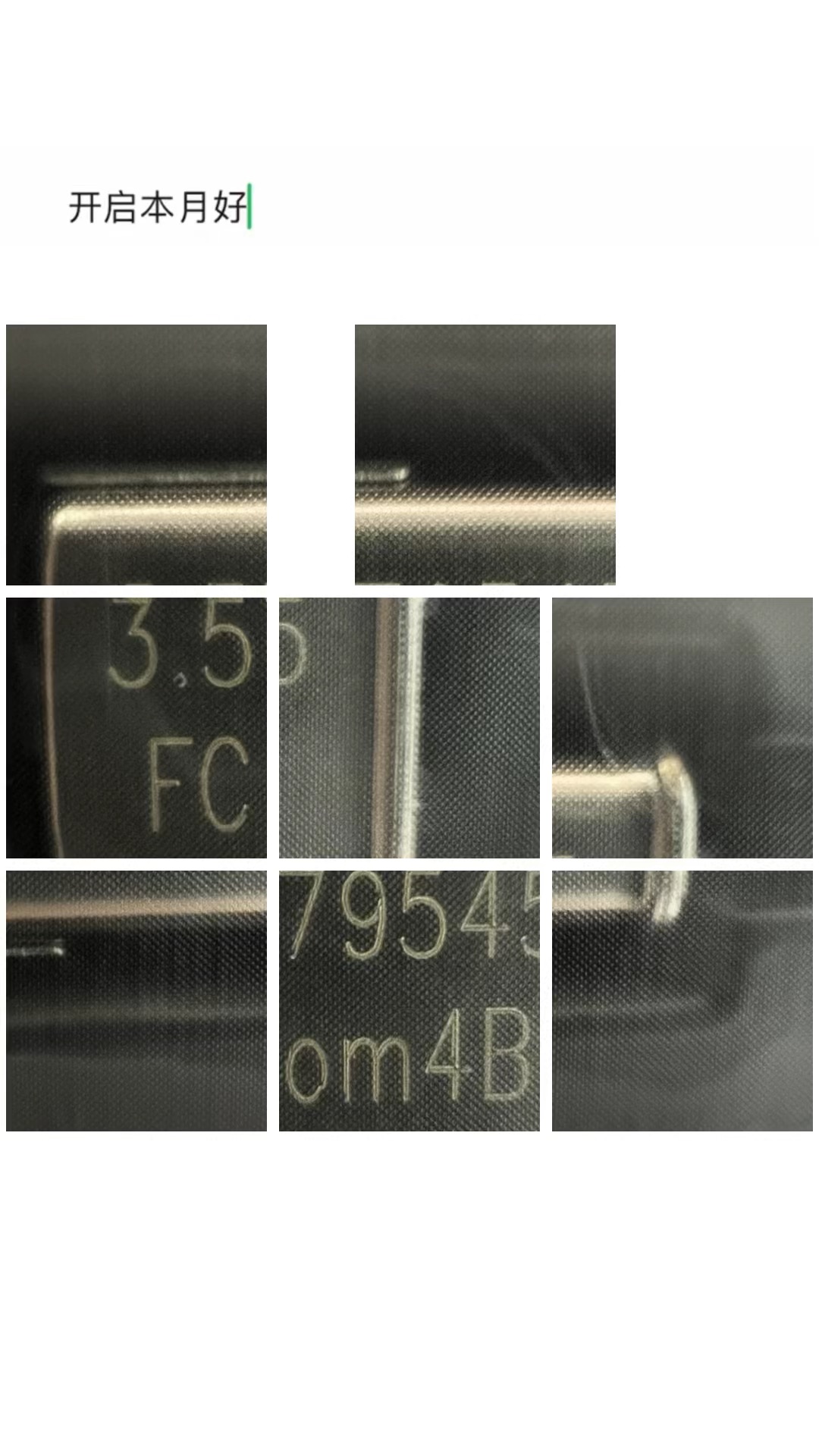

869 GD32的晶振和STM32的晶振连接有什么不同的地方

2023-10-11 07:58:05

u3000阻抗匹配问题是电子技术中的一项基本概念,通过匹配可以实现能量的最优传送,信号的 最佳处理。总之,匹配关乎着系统的性能,使匹配则是使系统的性能达到约定准则下的最优。其实,阻抗匹配的概念还可

2023-09-25 06:12:00

阻抗与频率成反比的元件有哪些? 阻抗与频率成反比的元件是指在电路中随着频率变化而阻抗发生变化,且变化的趋势是与频率成反比的元件。这些元件在电路中起着非常重要的作用,因为它们可以在电路中隔离高频噪声

2023-09-19 16:39:14 665

665 蓝牙天线阻抗匹配

阻抗匹配中,阻抗的测试是在板子供电的情况下测试还是在没有供电的情况下测试?比如蓝牙天线。是测试在板子工作的时候天线的阻抗,还是怎么测试?

2023-09-18 10:20:52

阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。

2023-09-03 11:06:09 1765

1765

阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。根据接入方式阻抗匹配有串行和并行两种方式;根据信号源频率阻抗匹配可分为低频和高频两种。

2023-08-30 09:47:00 480

480 一颗晶振和2个负载电容,但这些料件在PCBA加工过程中,常常造成良率下降,如在电容上件过程中产生冷焊的现象,容易造成起振失败;外挂晶振也必须增加电路板面积,增加终端产品的设计困难度。

新唐为解决外挂晶

2023-08-28 06:56:34

我的应用场景是这样的,M487JIDAE有114个IO口,其中有两个需要外接晶振,这样只剩下112个IO口;正好项目需要用到114个IO,所以希望不外接晶振,然后使用内置晶振也能够跑USB例程。目前M487JIDAE的开发包里面也没有找到使用内置晶振跑USB例程的写法,小白刚入门,请教一下大家怎么处理,谢谢!

2023-08-25 08:34:36

有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我们也会叫做阻抗失配。

2023-08-05 12:05:58 2795

2795

阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。

2023-07-04 14:44:02 521

521

阻抗匹配主要用于传输线上,以此来达到所有高频的微波信号均能传递至负载点的目的,而且几乎不会有信号反射回来源点,从而提升能源效益。信号源内阻与所接传输线的特性阻抗大小相等且相位相同,或传输线的特性阻抗与所接负载阻抗的大小相等且相位相同,分别称为传输线的输入端或输出端处于阻抗匹配状态,简称为阻抗匹配。

2023-07-04 14:38:36 4494

4494

在RF电路中,阻抗可以在很宽的频率范围内变化。RF匹配网络的主要目标是匹配源和负载的阻抗,以最大限度地提高功率传输,并在所需的工作频率范围内最小化反射。这需要了解源和负载的阻抗,并选择在该频率下产生匹配的组件。

2023-06-27 11:38:16 1000

1000

希望本文揭开了RF阻抗匹配的神秘面纱,并使RF功率放大器电路更易于理解。使用网络的负载Q值,我们可以在串联和并联网络之间切换,并将低值电阻转换为高值电阻。然而,与任何工程任务一样,对计算进行交叉检查总是好的,LTspice在绘制电路的输入阻抗和功率输出方面证明是无价的。

2023-06-15 16:36:54 1097

1097

在处理RF系统的实际应用问题时,总会遇到一些非常困难的工作,对各部分级联电路的不同阻抗进行匹配就是其中之一。一般情况下,需要进行匹配的电路包括天线与低噪声放大器(LNA)之间的匹配、功率放大器输出

2023-06-08 16:59:49 620

620

我有一块STM32U575的板子,没焊外部高速晶振,本来上面标着16兆晶振,四个脚的,我在淘宝上买了一些32M的晶振。

淘宝上写着匹配晶振8pF,我忘买了,搞了两个4.7pF的晶振,用STM32CubeMX生成代码,就是让一个灯闪。

可是灯一直不闪。我想会不会是匹配晶振的原因。请高手指教,谢谢!

2023-06-02 16:42:20

挑战。

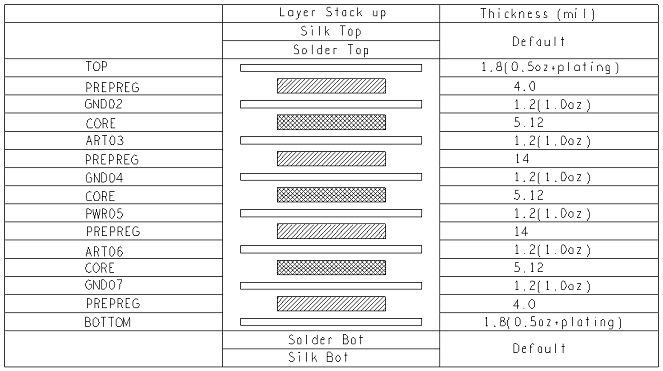

在高速PCB设计中,阻抗匹配显得尤为重要,为减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。

一般而言,单端信号线的阻抗取决于它的线宽以及与参考平面之间

2023-05-26 11:30:36

我这边的应用对MCU的时钟有要求,无法使用24M的晶振,只能提供一个10M的有源时钟。芯片手册中没有规定外部时钟的最大值和最小值,只是写了一个典型值24M。用户手册中提到了有几个模块是直接使用的外部时钟,像vad、ptmr、usb等。请问能否用10M有源时钟替换24M晶振?

2023-05-26 06:26:07

具有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫做阻抗。阻抗常用Z表示。阻抗由电阻、感抗和容抗三者组成,但不是三者简单相加。 阻抗的单位是欧。

2023-05-18 11:15:41 4843

4843

窄带阻抗匹配电路设计

2023-05-15 16:48:46 592

592

阻抗匹配,作为射频设计中最为重要的一个环节,每一个射频工程师都无法绕过去的。 今天我们再加以总结,把整个阻抗匹配,展现给大家。

2023-04-27 09:36:34 4477

4477

我正在使用带有 ESP32 WROOM 32 的 Arduino V1.0.6 SDK。当使用外部晶振时,我目前面临 IO25 深度睡眠中的错误中断问题。IO25是用来外接晶振,还是频率输出?如何禁用此功能,并使用 IO25 作为中断以从 ESP32 的深度睡眠中唤醒。

2023-04-11 09:07:05

FPGA外接50MHZ的晶振,里面的组合逻辑电路运行时刷新频率是多少呢?

2023-04-10 11:46:50

负载阻抗等于信源内阻抗的共轭值,即它们的模相等而辐角之和为零。这时在负载阻抗上可以得到最大功率。这种匹配条件称为共轭匹配。如果信源内阻抗和负载阻抗均为纯阻性,则两种匹配条件是等同的。

2023-04-08 10:30:14 2802

2802 除了使用阻抗匹配变压器外,设计人员还可以在 RF 放大器的输出端使用阻抗滤波器电路,它可以兼作滤波电路和阻抗匹配电路。有多种类型的滤波器电路可用于阻抗匹配,本文讨论了最常见的那些。

2023-04-06 09:03:38 2481

2481 负载阻抗匹配就是在传输线和负载之间加入一个阻抗匹配网络,阻抗匹配网络应该全部由无耗元件组成,其匹配原理就是通过阻抗匹配网络引入一个新的反射波,这个反射波与负载因其的反射波等辐反相,相互抵消,使传输线上没有反射波

2023-03-25 10:13:42 1250

1250 不用外接电容复位和外接晶振的单片机和外接复位和晶振的单片机使用的编程语言一样吗?单片机可以直接驱动场效应管控制电磁阀每秒动作1-200次吗

2023-03-24 11:13:46

电子发烧友App

电子发烧友App

评论