Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 214

214 你好, 如何清除 SPI通信中的 TX_FIFO 和 RX_FIFO?是否有任何 API 可以清除接收数据缓冲区。

2024-02-27 07:16:30

TI品牌ADS5474IPFP:宇航级14位400MSPS模数转换器的技术详解在数字化世界的浪潮中,模数转换器(ADC)发挥着至关重要的作用。作为将模拟信号转换为数字信号的关键组件,ADC的性能直接

2024-02-16 15:47:11

电子发烧友网站提供《异步FIFO结构设计.pdf》资料免费下载

2024-02-06 09:06:27 0

0 消息。(通过-->-->UART Printf)

[i][错误]:.... source user hw gccgfx_cmdseq.c: (698): (): FIFO

2024-01-23 08:33:42

V62/14609-01XE参数详解及应用探索当我们深入探索电子元件的世界,会发现每一个小小的芯片、每一个模块都承载着无尽的技术和智慧。今天,我们就来详细解读一款备受瞩目的电子元件——V62

2024-01-14 21:51:10

按照数据手册,FIFO中的数据最后一个bit是1.但是我们读出来是0.请问FIFO的读出顺序是不是X3,X2,X1,Y3,Y2,Y1,Z3,Z2,Z1?每次8bits.高位在前?谢谢。

2023-12-28 06:48:52

ADXL345设置FIFO中断,FIFO中断出现后,多字节读操作,读出的第一数据FIFO[0]和后边的数据有明显差别。

2023-12-27 07:39:44

断路器部分参数意义及选择详解 断路器是一种用于保护电路的装置,它能够在电路发生过载或短路时自动断开电流,以防止损坏电气设备、火灾或人身伤害的发生。断路器的参数是选择合适的断路器的关键因素,本文

2023-12-25 16:02:48 241

241 1.信号采集的过程。

自然界的各种信号都是模拟的,例如:温度,湿度等等。在物联网流行的今天,如何把各种模拟的信号转换为计算机所能识别的数字信号这确实是一个问题。一般来说,从模拟到数字的转换无非就是

2023-12-22 08:12:29

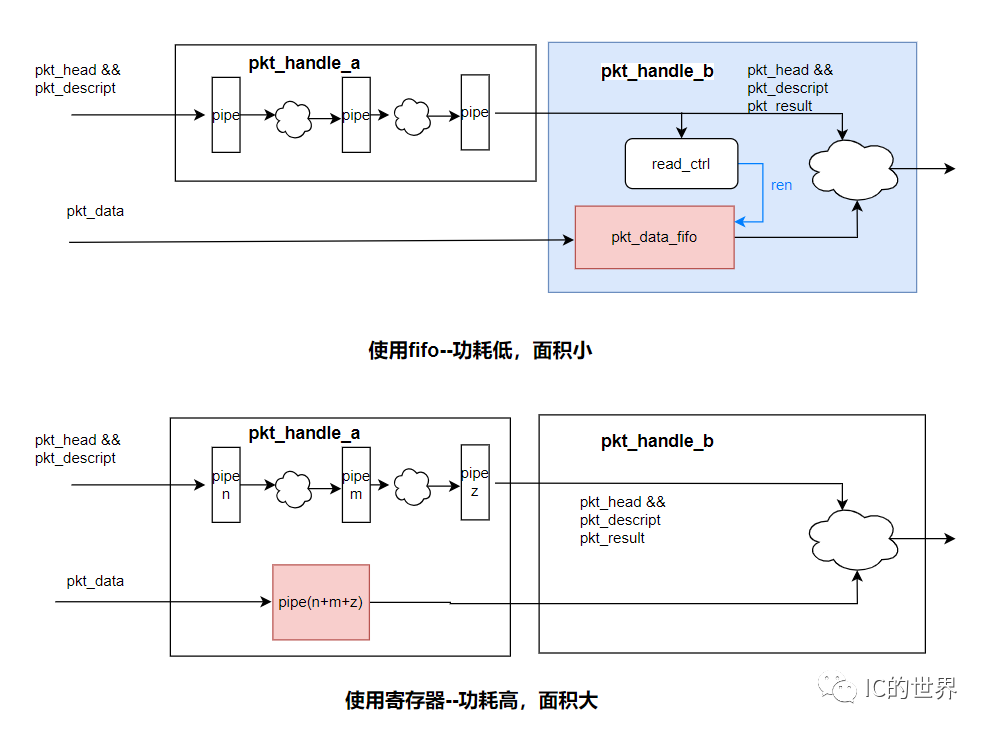

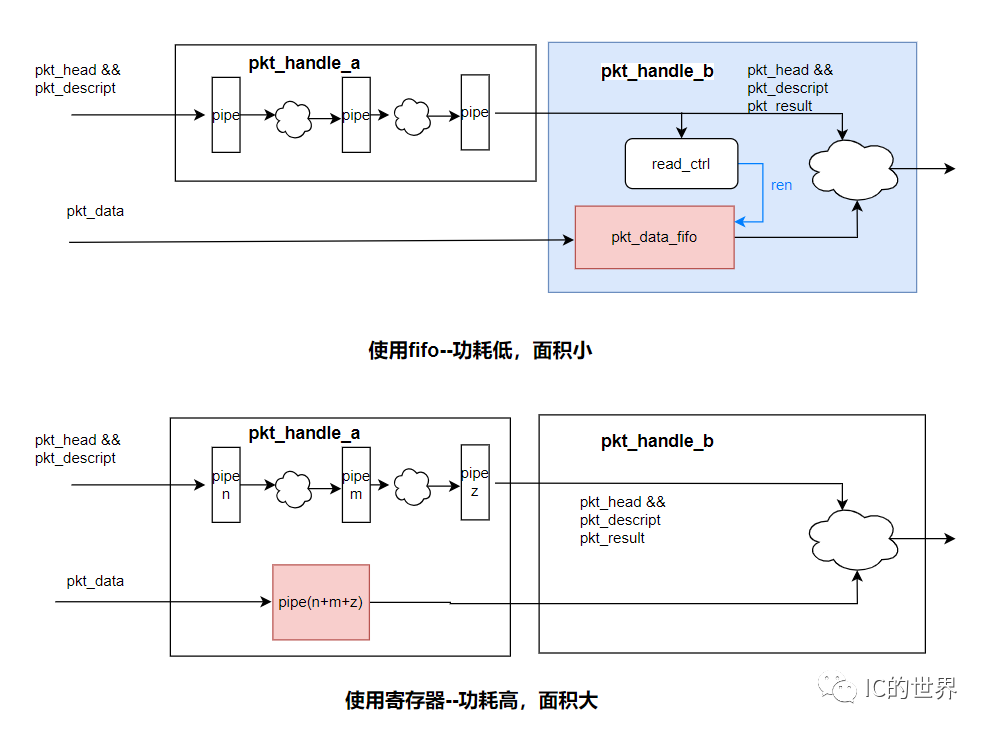

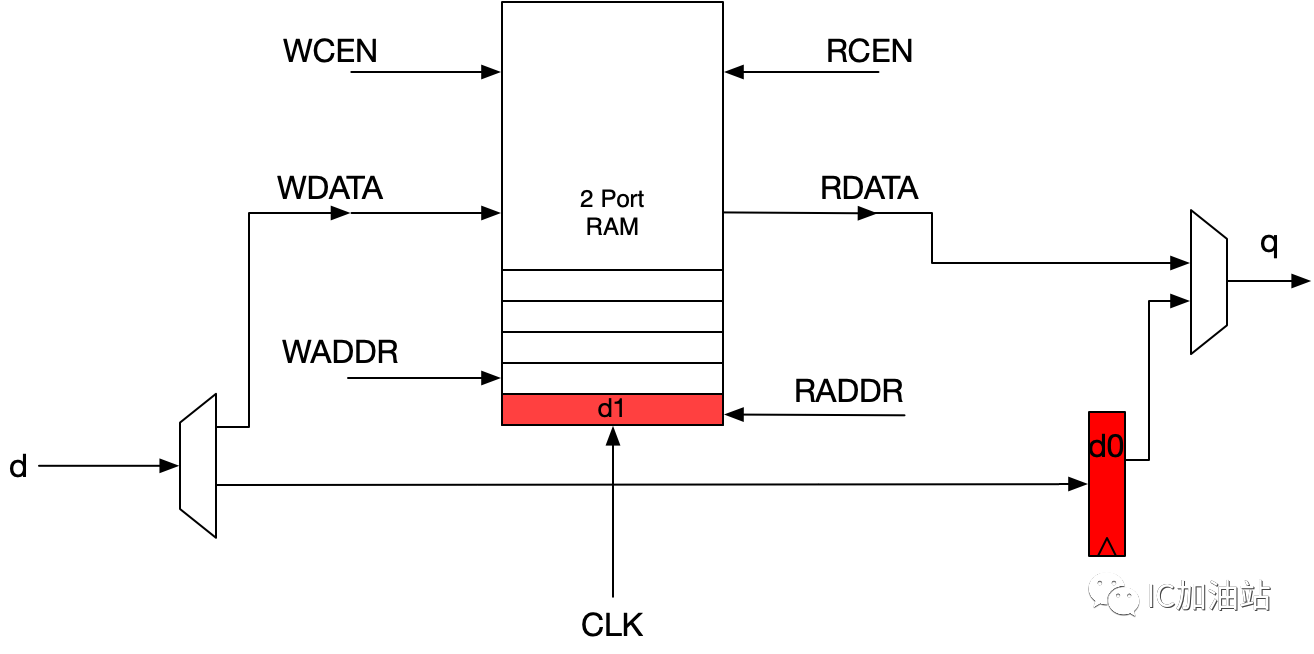

本案例中,我们讲解一种使用fifo节约资源,降低功耗的设计。

2023-12-15 16:34:11 234

234

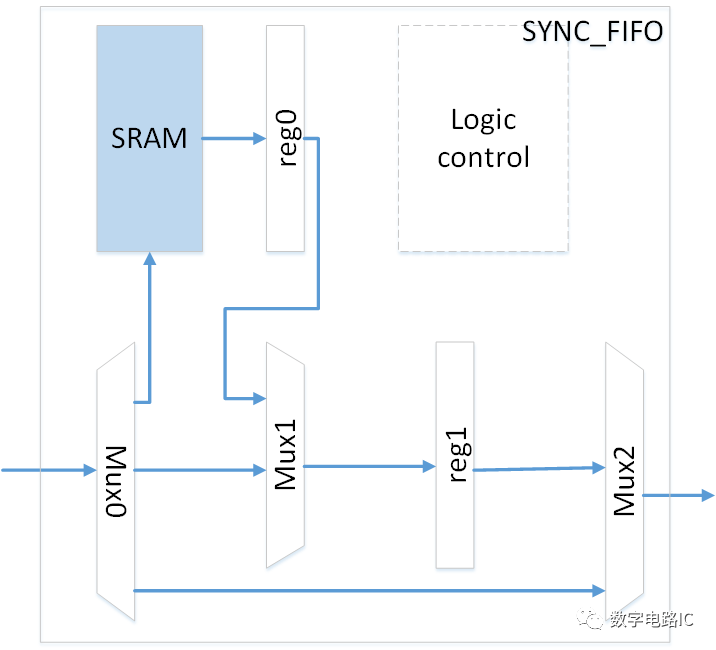

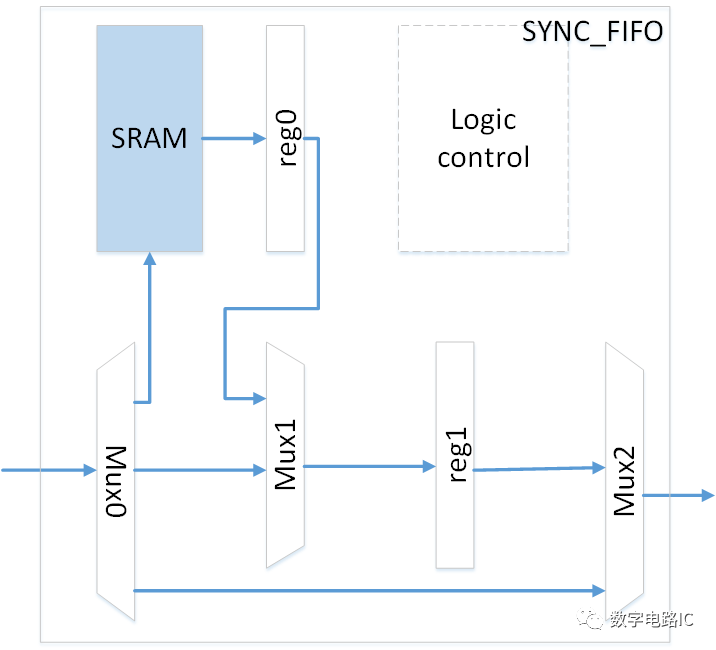

按照正常的思路,在前文完成前向时序优化和后向时序优化后,后面紧跟的应该是双向时序优化策略了,不过不急,需要先实现一下握手型同步FIFO。

2023-12-04 14:03:49 263

263

最近加的群里面有些萌新在进行讨论**FIFO的深度**的时候,觉得 **FIFO的深度计算比较难以理解** 。所

2023-11-28 16:19:46 347

347

自己的设计需求是什么,从而在运放参数表中来查找。一般来说在设计中需要考虑的问题包括1. 运放供电电压大小和方式选择;2.运放封装选择;3.运放反馈方式,即是VFA (电压反馈运放)还是CFA(电流反馈

2023-11-22 07:09:18

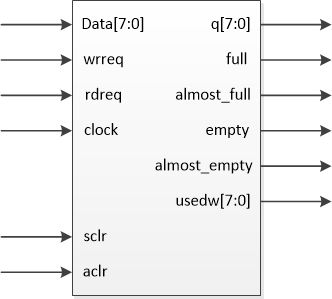

点击上方 蓝字 关注我们 第一节:fifo基础 内容: 1. 掌握FPGA设计中关于数据缓存的使用 2. 掌握FIFO工作原理

2023-11-17 14:00:02 179

179 罗彻斯特电子携手AMD/Xilinx,为Xilinx传统FPGA和相关配置PROM产品提供供货支持。

2023-11-07 09:04:42 250

250 文章目录

FAT32文件系统详细分析 (续FAT文件系统详解)

前言

格式化SD nand/SD卡

FAT32文件系统分析

3.1 保留区分析

3.1.1 BPB(BIOS Parameter

2023-11-03 17:55:26

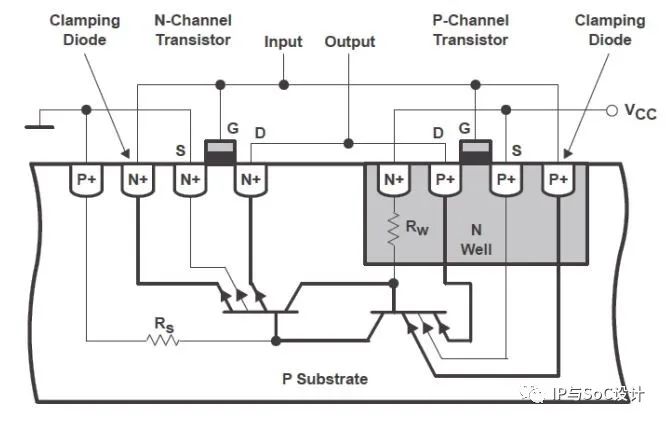

FIFO为什么不能正常工作?复位信号有效长度不够,接口时序不匹配,可看下面这篇文章。 本文将介绍: 非DFX工程如何确保异步FIFO自带的set_max_delay生效? DFX工程如何确保异步

2023-11-02 09:25:01 475

475

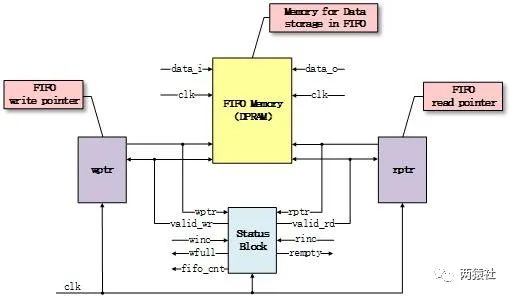

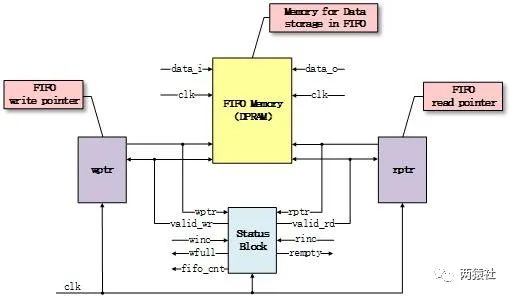

相邻的格雷码只有1bit的差异,因此格雷码常常用于异步fifo设计中,保证afifo的读地址(或写地址)被写时钟(或读时钟)采样时最多只有1bit发生跳变。

2023-11-01 17:37:31 779

779

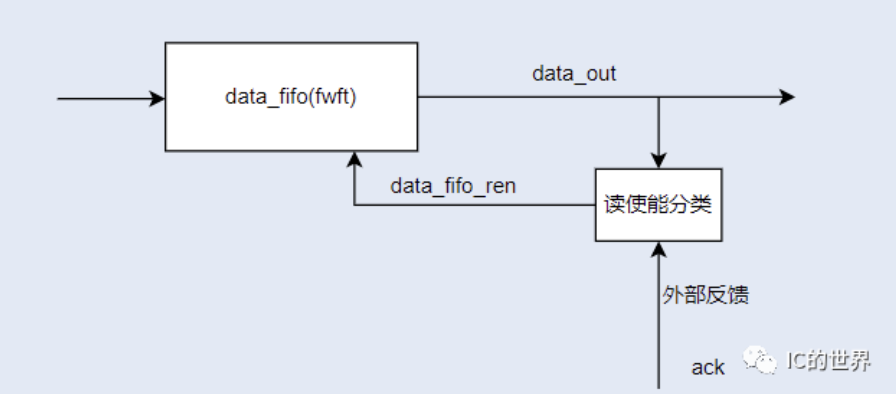

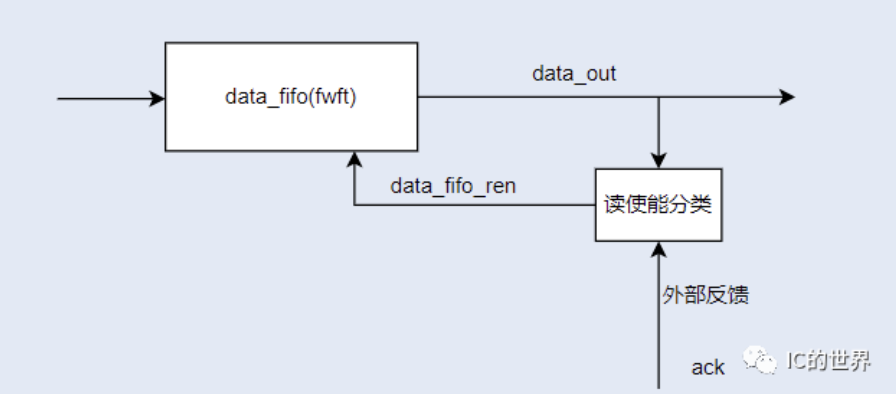

本文将简述一种fifo读控制的不合理设计案例,在此案例中,异常报文将会堵在fifo中,造成头阻塞。

2023-10-30 14:25:34 159

159

文章目录

FAT32文件系统详细分析 (续FAT文件系统详解)

前言

格式化SD nand/SD卡

FAT32文件系统分析

3.1 保留区分析

3.1.1 BPB(BIOS Parameter

2023-10-18 16:58:34

请问异步FIFO的溢出操作时怎么样判断的? 异步FIFO是数据传输的一种常用方式,在一些储存器和计算机系统中,常常会用到异步FIFO。作为一种FIFO,异步FIFO经常面临两种情况:溢出

2023-10-18 15:28:41 299

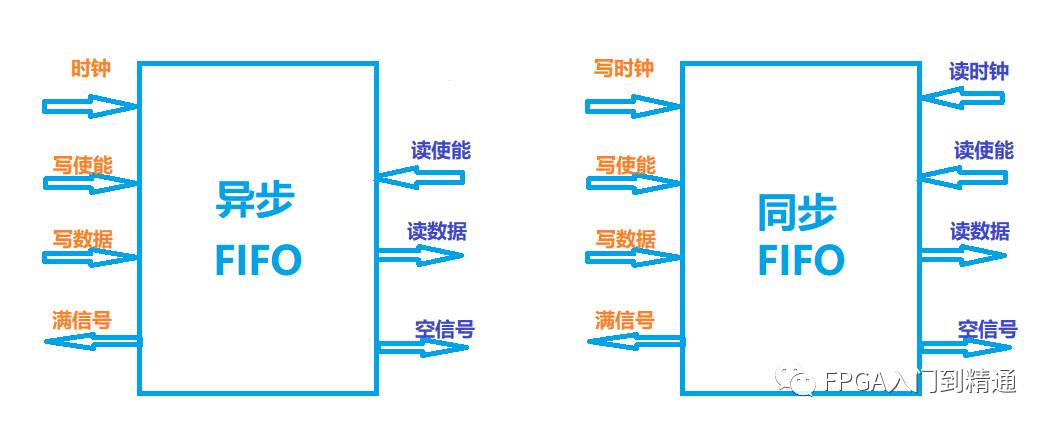

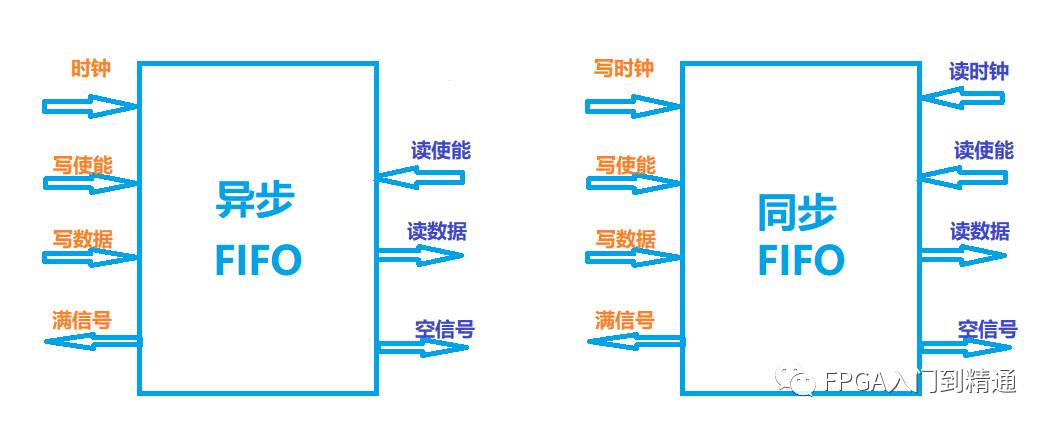

299 同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用? 1. 同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO在处理时序有明显的区别。同步FIFO相对来说是较为

2023-10-18 15:23:58 789

789 电子发烧友网为你提供ADI(ADI)AD4129-8:32 微A,超低功率,16-Bit Sigma-Delta ADC,综合PGA和FIFO数据表相关产品参数、数据手册,更有AD4129-8

2023-10-10 19:21:53

FIFO读后一定要清么

2023-09-22 06:31:18

异步FIFO包含"读"和"写“两个部分,写操作和读操作在不同的时钟域中执行,这意味着Write_Clk和Read_Clk的频率和相位可以完全独立。异步FIFO

2023-09-14 11:21:45 545

545

模块虽小但是要有新意,首先写一个同步FIFO,这是一个烂大街的入门级项目,但是我肯定不会写的那么简单

2023-09-11 17:11:07 333

333

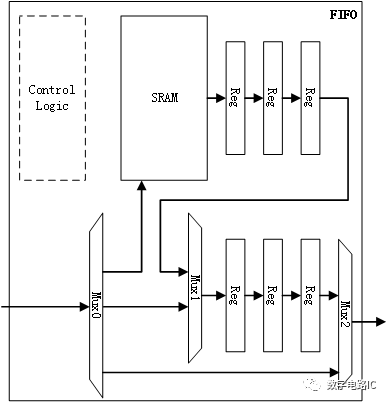

FIFO在设计是一个非常常见并且非常重要的模块,很多公司有成熟的IP,所以一部分人并没有人真正研究写过FIFO,本文仅简述FIFO中部分值得保留的设计思路。

2023-09-11 17:05:51 356

356

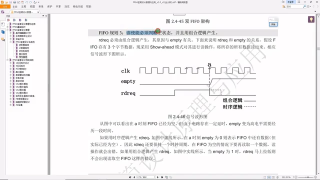

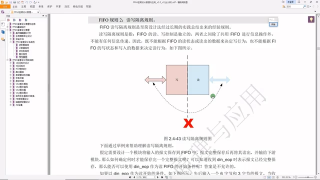

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作。当wr被插入时,输入的数据被写入缓存,此时读操作被忽视。FIFO缓存的head一般

2023-09-11 10:12:39 376

376

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作

2023-09-11 09:12:23 257

257

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作。

2023-09-08 09:06:18 237

237

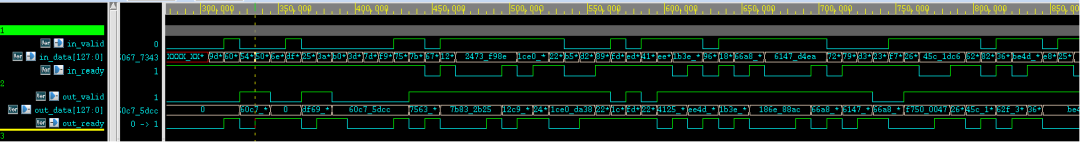

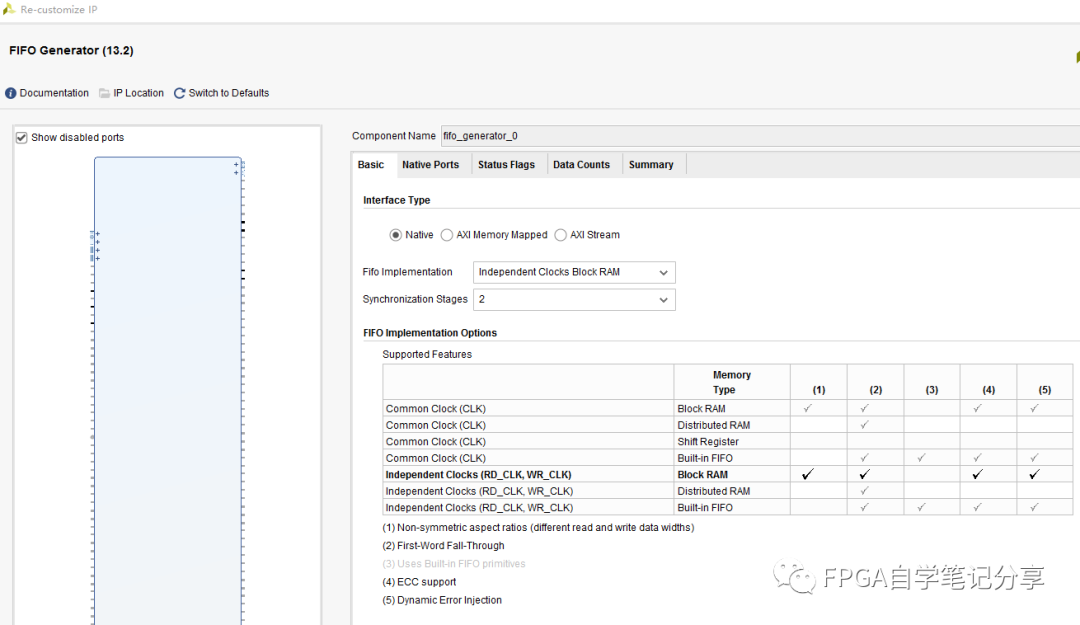

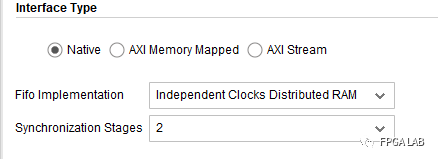

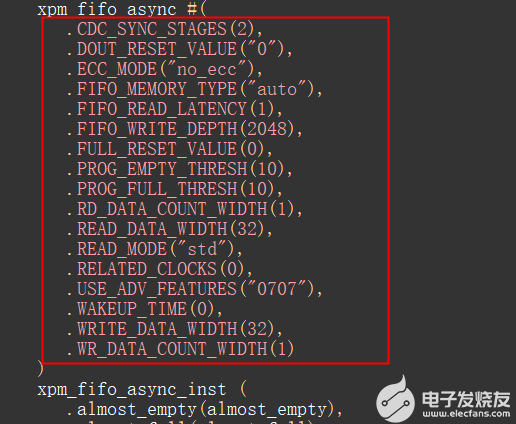

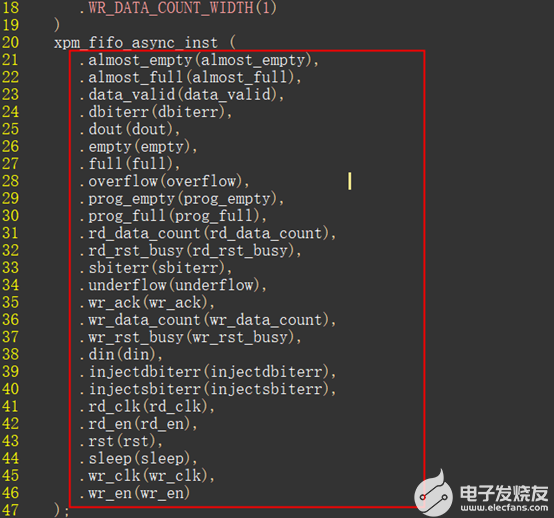

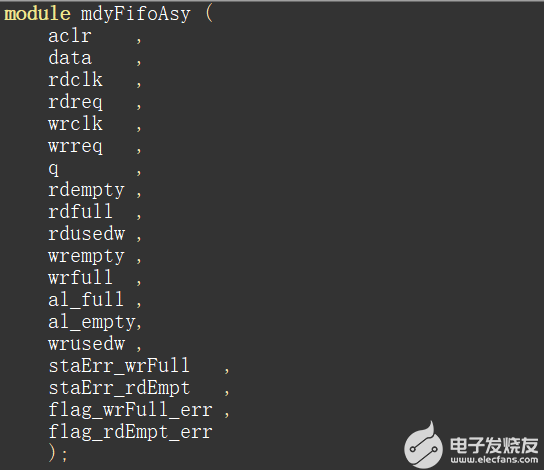

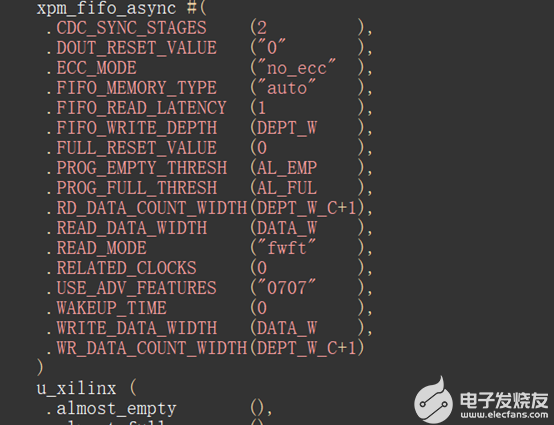

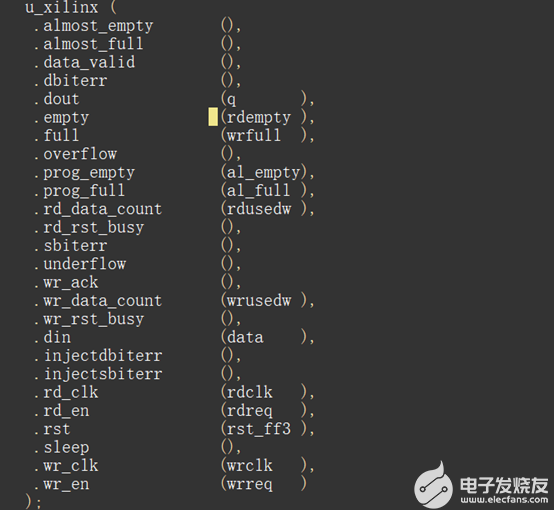

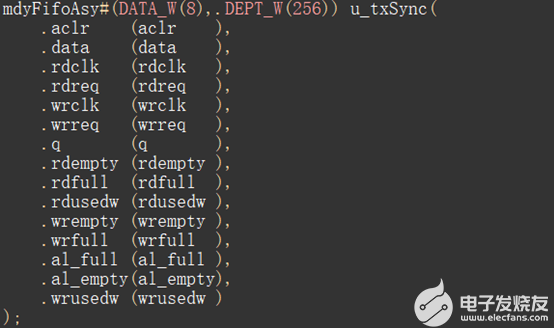

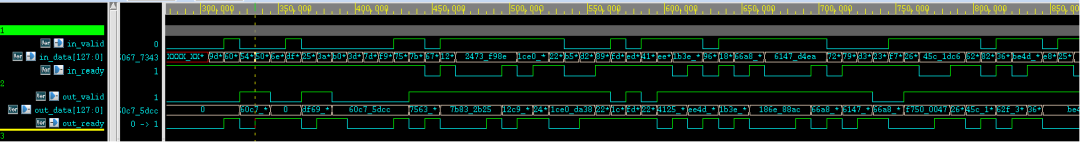

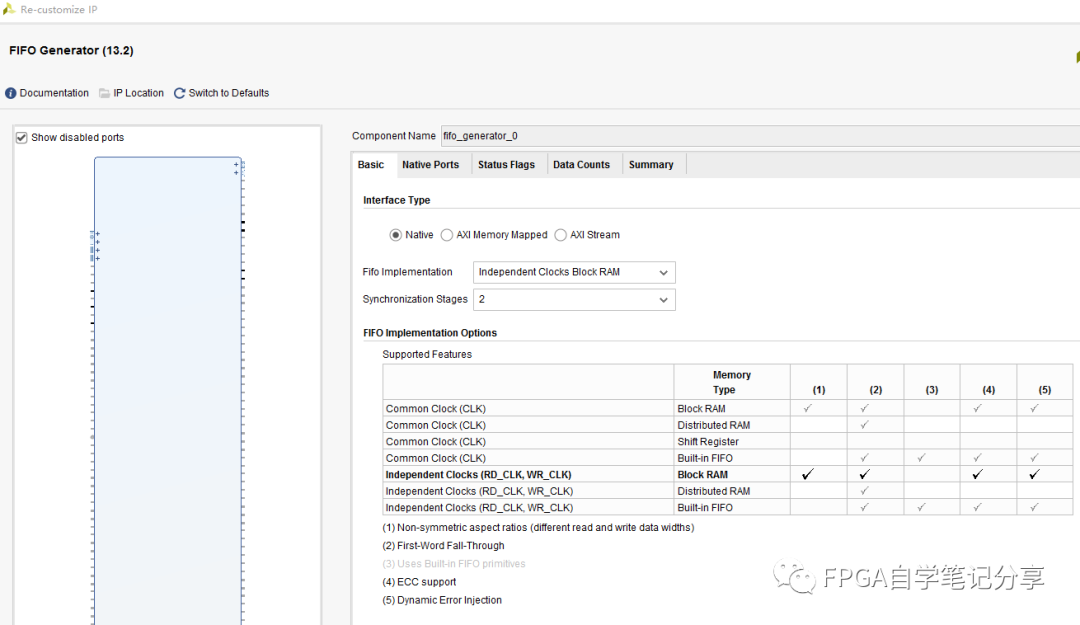

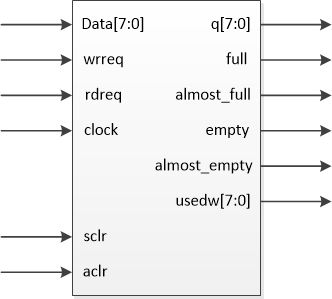

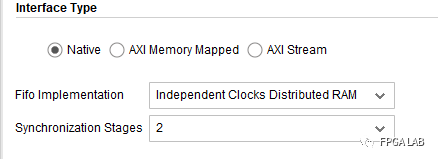

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

在数字设计中,fifo是数据操作任务所需的普遍结构,如跨时钟域、低延迟内存缓冲和总线宽度转换。

2023-09-07 18:31:19 578

578

FIFO(First In First Out, 先入先出 ),是一种数据缓冲器,用来实现数据先入先出的读写方式。数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线,有一个写端口和一个读端口。

2023-09-07 18:30:11 819

819

同步FIFO的设计主要包括读写地址的产生、数据的读写、以及状态的控制。下面我们将分别介绍这三个方面的设计。

2023-08-31 12:53:04 266

266 各位大大安安,我想请问在官方SPI FIFO Mode范例里,Tx 和 Rx都使用FIFO传输,其中enable \"SPI_FIFO_TX_INT_MASK\"这项中断功能主要

2023-08-31 11:03:25

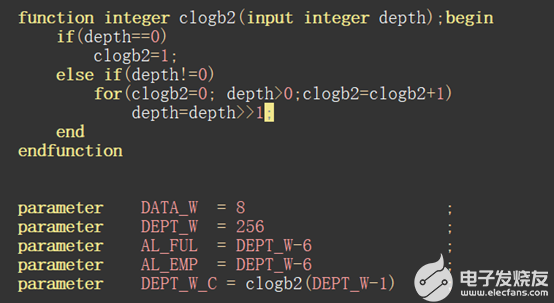

基于上一题目模块中定义的parameter参数,在例化该模块时实现参数传递

2023-08-30 11:23:51

很多人在面试时被问到为什么异步FIFO中需要用到格雷码,可能大部分的答案是格雷码可以消除亚稳态。这种回答比较模糊,今天我们就针对这个来深入探讨一下。

2023-08-26 14:20:25 573

573

rk3588参数详解 rk3588芯片参数 Rockchip官方已经推出了全新一代的高端芯片RK3588,作为旗舰芯片,其蕴含的高性能与先进科技引起了广泛关注。本篇文章将详细介绍RK3588芯片

2023-08-21 17:16:32 21695

21695 特征图(减少网络的参数),从而减小计算量,并且在一定程度上能控制过拟合。

常见的池化层为最大值池化层(max-pooling)与平均值池化层(mean-polling),

如下图所示,其stride为

2023-08-18 06:56:34

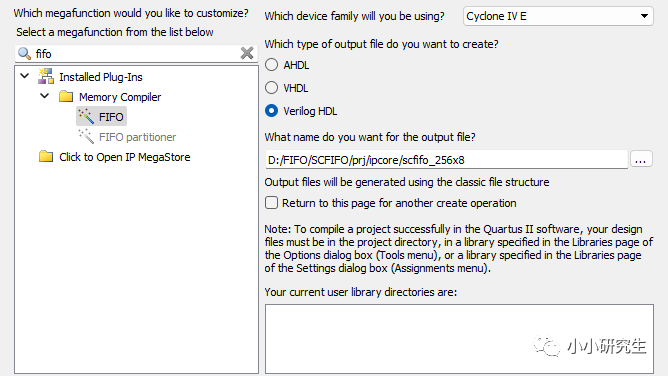

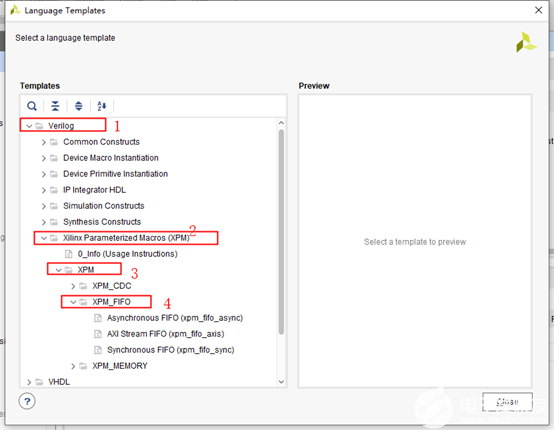

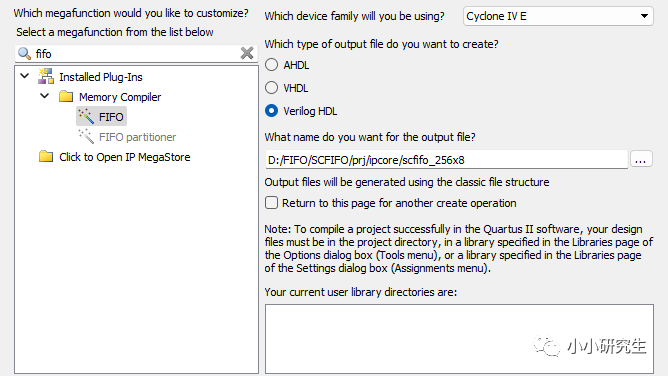

FPGA厂商提供了丰富的IP核,基础性IP核都是可以直接免费调用的,比如FIFO、RAM等等。

2023-08-07 15:41:28 1293

1293

FIFO(First In First Out)是一种先进先出的存储结构,经常被用来在FPGA设计中进行数据缓存或者匹配传输速率。

2023-08-07 15:39:50 445

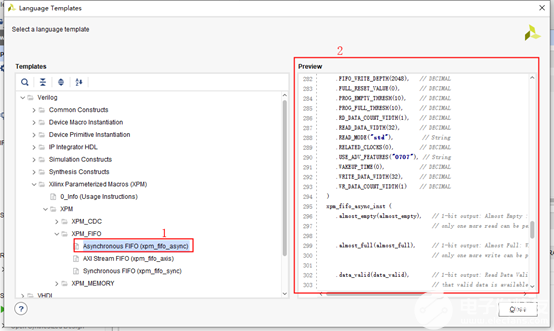

445 Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1617

1617

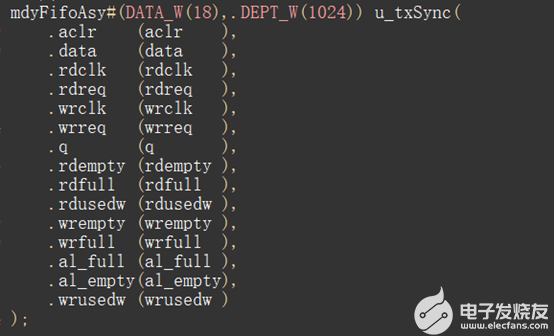

在ASIC设计或者FPGA设计中,我们常常使用异步fifo(first in first out)(下文简称为afifo)进行数据流的跨时钟,可以说没使用过afifo的Designer,其设计经历是不完整的。废话不多说,直接上接口信号说明。

2023-07-31 11:10:19 1220

1220

FIFO(first in first out)是一种用寄存器reg或者RAM实现的存储结构,常用于存储数据通道中的数据流,采用先入先出的数据,当下游模块无法及时处理上流模块输出的数据时,此时需要用FIFO暂存数据,防止数据丢失。

2023-07-26 12:40:44 738

738

FIFO,先进先出。在FPGA中使用的FIFO一般是指对数据的存储具有先进先出的缓冲器,FIFO与普通的存储器的不同在于它没有读写地址线。举个例子,当FPGA从外部传感器读取到一连串数据时,首先

2023-07-23 11:47:03 369

369

在FPGA的设计中的,内部的FIFO和RAM是两种非常常见的存储单元

2023-07-11 17:23:33 956

956 AMD Xilinx K26支持Ubuntu。从ubuntu amd-xilinx下载映像后,把image烧入到TF卡

2023-07-10 15:58:14 489

489 本文介绍广州星嵌DSP C6657+Xilinx Zynq7035平台下Xilinx Zynq7035算力指标。

2023-07-07 14:15:01 681

681

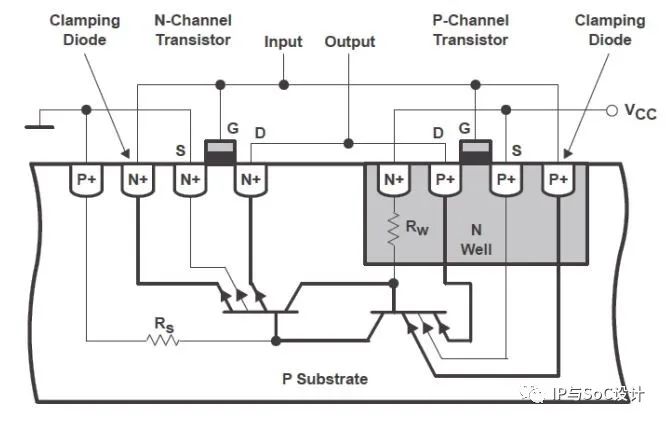

物理设计中的问题详解

2023-07-05 16:56:53 487

487

FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

2023-06-27 10:24:37 1199

1199

FIFO?还是FIFO IP核?这也需要写总结吗?太容易了吧。如果我是一个正在处于面试找工作中的年轻人,肯定关注的是如何手撕FIFO,这也是当时校招时候干过的事情。

2023-06-21 14:22:09 817

817

TX_FIFO 发送用一个16字节的FIFO做缓存来降低CPU的中断数量

RX_FIFO 接收用一个16字节(每个字节加3个比特的错误比特)的FIFO做缓存来降低CPU的中断数量.

TX移位寄存器

2023-06-20 10:00:36

的,这也是它的一大特点,通常用来做数据的缓存,或者用来解决高速异步数据的交互,即解决了跨时钟域的问题。此外,FIFO还有一个特点,就是数据被读出之后就不存在了,不像RAM和ROM一样,数据被读出后还存在

2023-06-16 17:50:31

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。 在这篇文章中,展示了一个简单的 RTL 同步

2023-06-14 09:02:19 461

461 FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。

2023-06-14 08:59:29 223

223 上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

有用过xilinx FIFO的first word fall through模式,然后write data count会少2个计数的吗?

2023-06-12 09:35:03 364

364

FIFO的英文全称叫做First in First out,即先进先出。这也就决定了这个IP核的特殊性,先写进去的数据优先被读出,所以,FIFO是不需要地址信号线的,这也是它的一大特点,通常

2023-06-09 09:38:02 2014

2014

FIFO( First Input First Output),简单说就是指“先进先出”。

2023-06-06 09:26:42 169

169

FIFO,First In First Out,先入先出队列,顾名思义,即第一个到达的数据也将会是第一个离开。

2023-06-05 14:39:33 535

535

AUTOSAR ComM模块的分享分为ComM模块概念详解和ComM模块配置及代码分析

2023-06-01 10:00:06 3306

3306

FIFO(First In First Out)是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。

2023-05-29 15:35:42 3924

3924

Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 我们使用的是 LPC5504,我们通过“TX BUFFER”(不是通过 TX-Fifo,不是通过 TX-Queue)发送 CAN 消息。

我们期望每次成功发送 TX BUFFER 时,都会将一个条目

2023-05-29 07:16:51

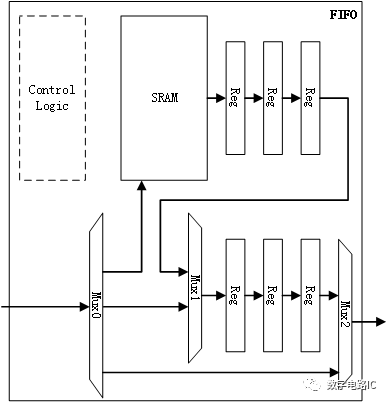

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 911

911

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

2023-05-26 16:12:49 978

978

工程监测无线中继采集仪的寄存器(参数)汇总详解 工程监测无线中继采集仪 一、 寄存器(参数)汇总 无线中继采集发送仪有很多参数(寄存器),对于一些简单的应用,用户无需关心这些参数,使用默认参数值即可

2023-05-19 10:39:29 330

330

关键字:S2-LP,FIFO,大数据透传 目录预览 1 引言 2 应用场景 3 实验结果 4 小结 1. 引言 众所周知,S2-LP 拥有两个数据 FIFO,一个用于数据传送,另外一个用于数据接收

2023-05-17 23:45:02 491

491

环天线属于闭合回路类型天线,也就是用一根导体弯曲成一圈或多圈并且导体两端闭合在一起。环天线可以分为两类:一类是导体的总长度以及一圈的最大线性尺寸相对于工作波长都非常小;另一类是导体的总长度和环

2023-05-16 15:23:46

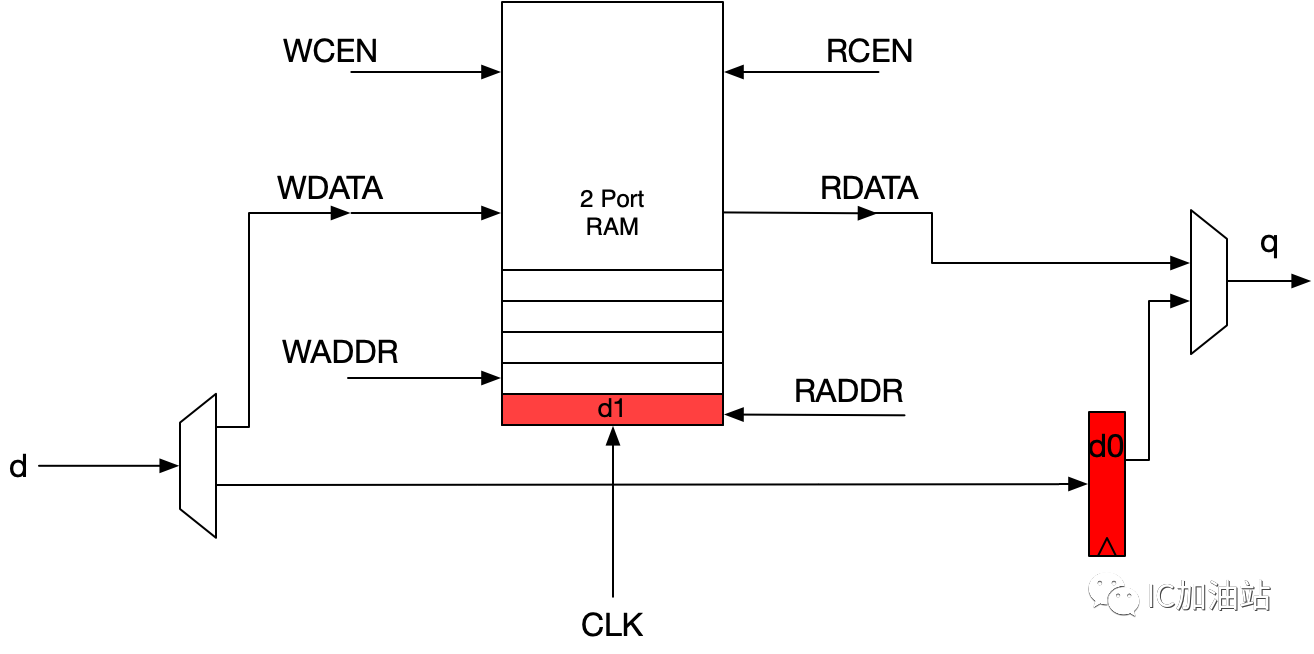

我们说这个结构之所以使得FIFO的输出Q在读完SRAM之后保持稳定,其实需要SRAM本身可以保持RDATA在读操作之后的多个周期保持稳定。即SRAM本身的读时序如下图所示:图中cycle 4,5,6都没有读操作,SRAM的RDATA依然保持D0不变。

2023-05-04 15:59:46 403

403

今天咱们开始聊聊FIFO的设计。FIFO是一个数字电路中常见的模块,主要作用是数据产生端和接受端在短期内速率不匹配时作为数据缓存。FIFO是指First In, First Out,即先进先出,跟大家排队一样。越早排队的人排在越前面,轮到他的次序也越早,所以FIFO有些时候也被称为队列queue。

2023-05-04 15:48:20 544

544 FIFO在嵌入式应用的非常广泛,可以说有数据收发的地方,基本就有FIFO的存在

2023-04-26 09:21:17 598

598

FIFO(First In First Out )先入先出存储器,在FPG设计中常用于跨时钟域的处理,FIFO可简单分为同步FIFO和异步FIFO。

2023-04-25 15:55:28 2892

2892

FIFO 是否正常工作,但在启用 FIFO 的情况下我无法收到任何消息。这是 CAN0 初始化代码, voidCAN_vInit ( CAN_Type *pstCan

2023-04-18 06:36:39

一、原理介绍FIFO即First in, First out。代表着先进的数据先出,后进的数据后出。FIFO实在RAM的基础上增加了许多功能,主要分为读和写两部分。与RAM最大的不同时,FIFO没有

2023-04-12 22:44:21

FIFO;Independent clock: 指的就是异步FIFO。本页需要设置数据参数,包括数据位宽以及数据深度。这一页的选项就是一些标志位,用来标记我们是否出现了读写溢出之类的。Almost

2023-04-11 20:50:21

TxLUT 中的搜索优先级以引用另一个参数(例如到达时间)而不是 CAN ID?如果不是,我想优先考虑表中间的另一条消息,这是否意味着我必须弹出消息并忽略它们,直到到达所需的消息?

2023-04-06 08:38:57

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

FIFO(First In First Out)是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。其实,多位宽数据的异步传输问题,无论是从快时钟到慢时钟域,还是从慢时钟到快时钟域,都可以使用 FIFO 处理。

2023-03-26 16:00:21 1821

1821

支持所有Xilinx器件下载 包括FPGA CPLD ISP Configuration PROM 下载接口电压:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

电子发烧友App

电子发烧友App

评论