七、综合项目实践课——千兆网项目专题课

【问题7.1】千兆网课程里的udp和百兆网通用的吗?

答:本课程讲述的是千兆网,对于百兆网来说,UDP IP MAC和ARP协议都是相同的,

本课程提供的是千兆网的工程,如果要使用百兆网,需要根据上面的内容来修改。

【问题7.2】千兆网课程有实现TCP协议吗?

答:本千兆网课程实现的是UDP协议,没有TCP协议。

【问题7.3】请问下,三速以太网IP核配置时,32bit对齐选项的意义在哪里?

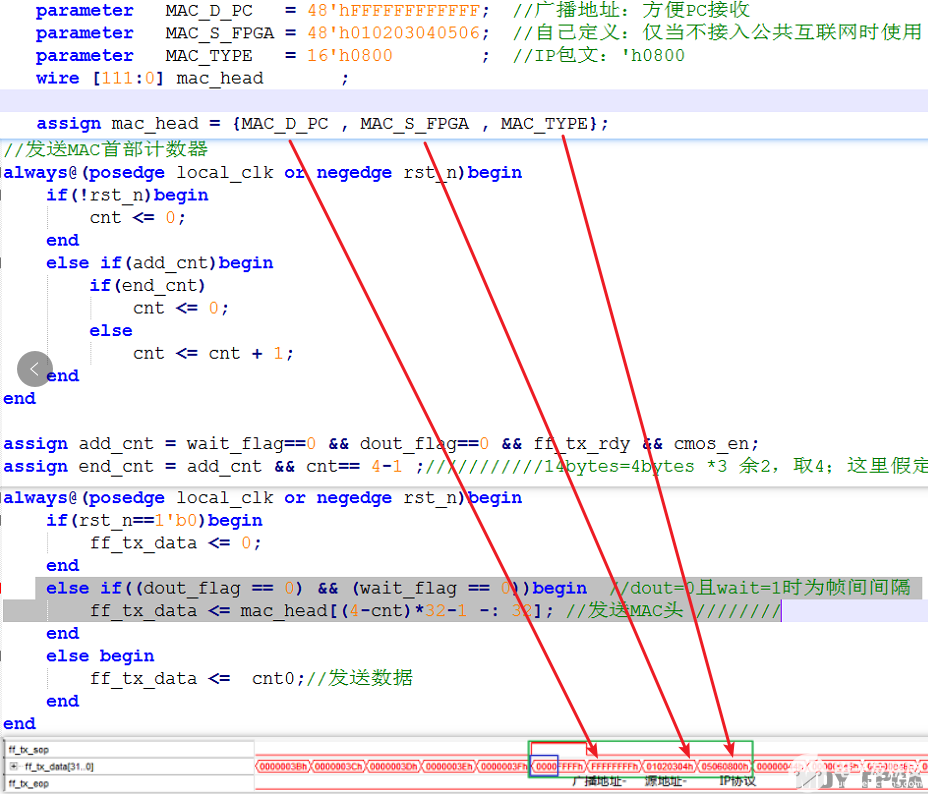

答:在接口为32bit时,每个VLD有效时的数量是4个字节。由于MAC头是14字节,不是4的整数倍,

在发送方向,在补上MAC头后,

必须调整数据(拿出2字节与MAC头最后2字节凑成一个4字节的有效数据),这样处理比较麻烦。

同时道理,接收方向,去掉14字节MAC头后,

会有一个VLD多出2字节的有效数据,这样调整也麻烦。为此,MAC IP核里有一个功能,

就是32位对齐功能。该功能决定,在SOP位置时,

最高2字节是否为无效数据。 当是无效数据模式时,发送方向插入2字节无效数据+14字节MAC头;

在接收方向,删除前16字节MAC头,剩下就是效数据。这样处理就方便很多了。

【问题7.4】 只要勾选了32bit对齐功能,IP核自动添加2字节的无效数据?

答:勾选对齐后,接收方向将删除无效数据,直接输出数据,即SOP位置的高2字节也是有效的,

一直到EOP位置。发送方向,认为从SOP到EOP的位置都是有效的。

不勾选的话,接收方向,IP核输出、SOP位置的高2字节是无效数据。

发送方向,进到IP核的数据里,将SOP位置的高2字节视为无效数据。

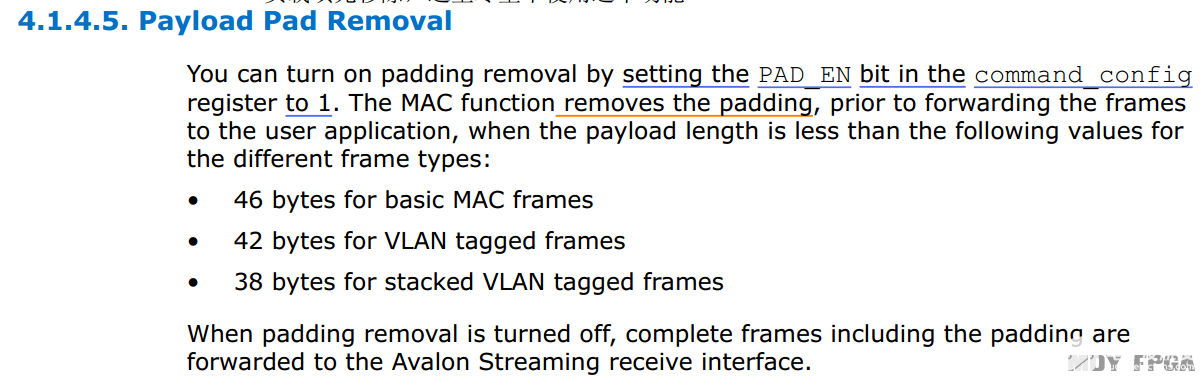

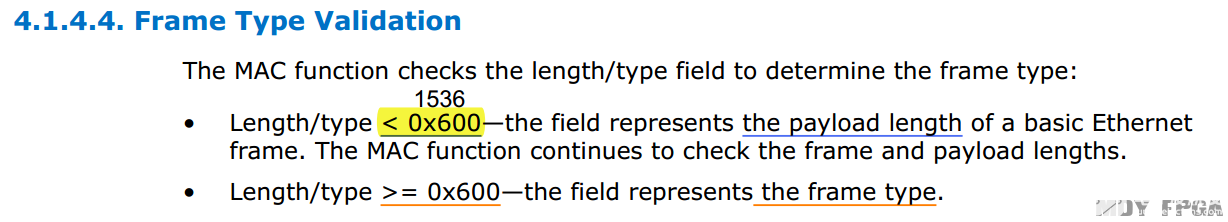

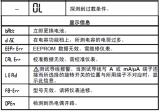

【问题7.5】如下图所示,当使用了PAD_EN功能时,接收方向,会将PAD去掉,但实际上没有去除,是怎么回事?

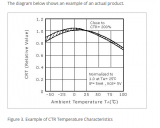

答:请看下面描述:第一段,当值小于600,该域反映的是长度,才会继续检查PAYLOAD长度,

进而才会有REMOVAL。

当值大于600时,该域反映的是类型而已,则不会REMOVAL。

【问题7.6】课程里会包含TCP协议吗?

答:TCP协议使用逻辑实现非常复杂,所以本课程不会包含此部分内容。

【问题7.7】RGMII支持10M/100M/1000M三种模式吗?

答:RGMII是"吉比特介质独立接口"的含义,即1000M的传输接口。其他几种接口包括GMII、MII等。

注意一下,10M/100M/1000M三种模式,指的是该“芯片”支持这三种接口,不是说RGMII支持。

当芯片采用了RGMII或GMII时,就传输1000M;当采用了MII 100M时,就是传输100M。

注意的是,RGMII和MII的部分管脚是可以复用的。

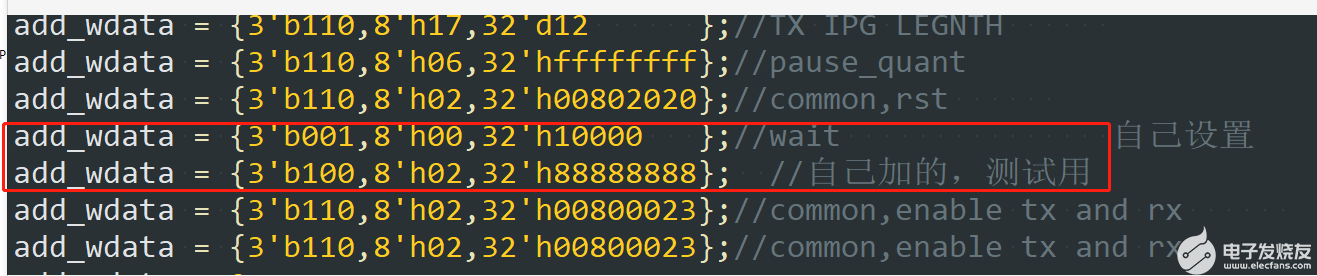

【问题7.8】千兆网配置寄存器的定义代码中,下面两个IP核数据手册中没有说明,是什么作用的?

答:第一行语句的作用是“等待10000个时钟周期”。目的是当完成前面的配置后,等待10000个时钟后,再去配置下面的寄存器。这是因为有时

候,配置完上面寄存器后,有可能要等一段时间才起作用,所以要等一等。这个“等待”功能是FPGA里面代码实现的。

第二句作用是测试使用的,可以删除,在调试时看看接口是否正确。

【问题7.9】本项目有没有配置外部的PHY芯片?

答:本项目是没有配置的,因为默认PHY芯片是不用配置就能正确使用的。

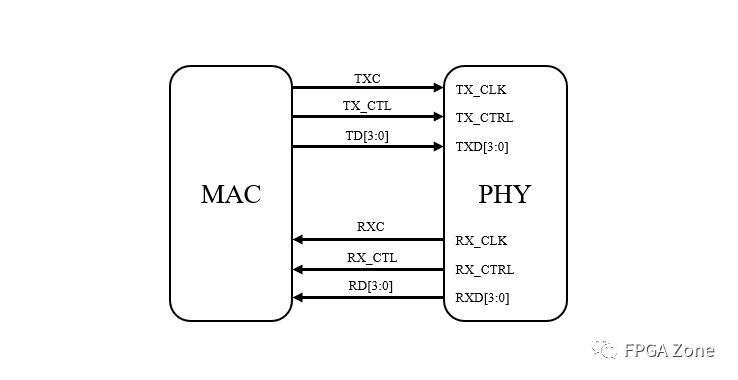

【问题7.10】、百兆网和千兆网的区别是什么?

答:1. IP核是一样的

2. 千兆网使用的是GMII接口,百兆网则是MII接口。gmii数据线是8位;MII接口使用是4位数据线,也就是TXD低4位和RXD低4位。

3. 时钟频率不同,千兆网是125M,百兆网是25M时钟。

4. 百兆网的TX时钟来自于PHY芯片,芯片管脚使用的是tx_clk,而不是gtx_clk。

5. MII接口的4位数据线,是先发1个字节的低4位,再发高4位。

【问题7.11】老师,咱们千兆网项目中,为啥用sharkwire抓包的时候 最大传输速率到不了千兆呢?

答:因为包文传输的时候,会有消耗的,例如包与包之间有帧间隙,并且每个包会有前导码和FCS部分。因此达不到理论的千兆。

【问题7.12】请问一下在千兆网工程里,初始化mac IP核时,signaltapii有些reg_cnt刚开始时,add_wdata会出现一小段莫名其妙的数据,是怎么回事 ?

答:请注意这个signaltap采样的时钟一定要跟代码模块的时钟一致。

SignalTap使用教程:http://www.mdy-edu.com/jishuwenz/2019/1210/107.html

【问题7.13】在千兆网的rx_filter模块中,读数据的时候为什么用add_cnt=m_empty==0,这个信息FIFO的不空作为读条件?

答:信息FIFO非空,表示数据FIFO中存有一个完整的包文,因为需要判断包文是否正确,所以需要数据FIFO中保存一个完整包文之后再读出。

由于本模块需要将32位的数据转成16位的,计数器cnt数两次,表示数据FIFO需要两个时钟读出一次,当遇到最后eop的时候,

由于可能存在无效字节,所以当无效字节为2个或者3个的时候,计数器只需要数一次就够了。

【问题7.14】在千兆网的rx_filter模块中,信息FIFO深度为什么设置为32,设置为1就可以了吧?

答:这里设置为32只是顺手而为,而且占用的资源也不是很多,所以就没有进行修改,深度改为1也是可以的。

【问题7.15】在udp发送的过程中,假设源端口为0x1234,目的端口为0x5678,那么发送的是12345678还是56781234?

答:发送的时候是按照12345678来发送的。

【问题7.16】为什么udp协议在发送和接收的时候,源端口和目的端口顺序会反?

答:包文的协议时固定的,只会按照源地址加目的地址的格式发送。

1. FPGA发送的时候,FPGA产生包文,端源端口是1234,目的端口是5678。然后发送格式是源+目,因此发送的是1234_5678

2. FPGA接收的时候,PC产生包文,源端口是5678,目的是1234,然后发送的是源+目,因此是5678_1234。

【问题7.17】请问一下,我编译千兆以太网的时候,为什么把这个clogb2文件添加进去就会报错,说是sv文件?还有这个文件有什么作用?谢谢

答:clogb2不是一个完整的module文件,它是被用include的方法加入代码中的。它不需要加到工程上,所以可以把它去掉。

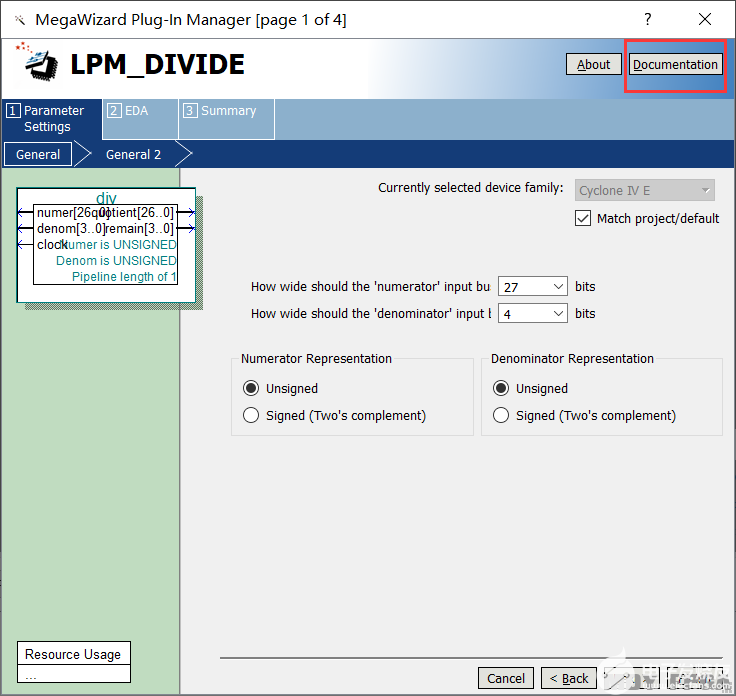

【问题7.18】请问下,在做练习工程的时候,需要自己设计MAC首部发送电路,MAC首部14字节,但数据位是4字节的,我需要定义 发送首部的计数器,这里4是不能被14整除的,我应该怎么处理?

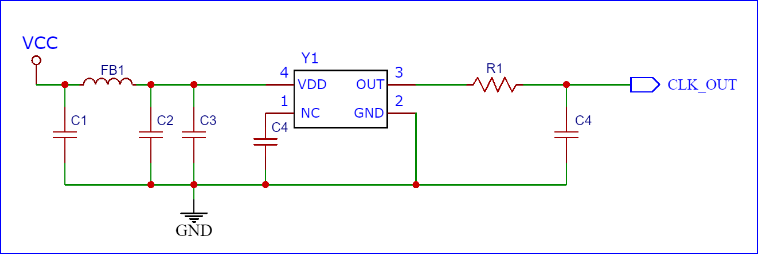

答:1、可以在设计代码的时,把产生的mac头、IP头、UDP头拼接起来的时候,在最高位补2字节的无效数据零。

2、或者在mac_ip核进行相关的设置,具体可以查看相关数据手册附:数据手册在打开IP核后如图所示位置查看

【问题7.19】千兆网转百兆网的时候,需要给phy芯片一个参考时钟,是怎么给的?

答:开发板上有一个12M的时钟芯片,是给phy芯片的。外部晶振的事,跟FPGA无关

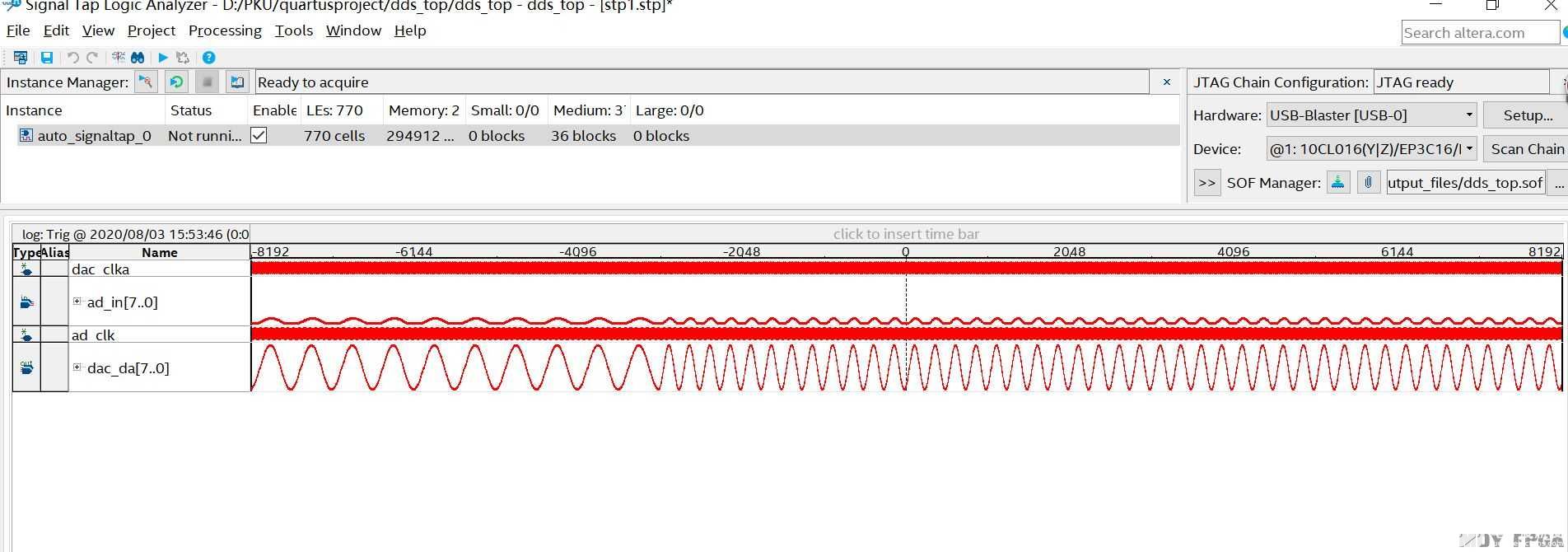

【问题7.20】我的采样时钟就是模块的工作时钟(always块里的);现在从MAC_IP核输出的数据不正确,根据常见问题PDF里问题1和6的解答,

有两种情况,如果时钟没问题那就有可能是IP核的输入信号有问题。我对应的代码和signaltap采集到的数据如图:

请问这种情况下,输入的数据算是正确的吗?

答:结果是正确的。原因同上【问题9】

【问题7.21】再设置好电脑的IP地址之后,把界面关掉,然后再打开就没有了,需要重新设置,怎么解决?

答:

1、点击左下角的WIN图标,输入CMD然后回车,打开DOS模式窗口。

2、在DOS命令行提示符下直接输入:“netsh winsock

3、reset”,然后回车,会提示需要重启,不要管它。

4、在DOS命令行提示符下直接输入:“netsh int ip reset

5、reset.log”,然后回车,提示重新启动计算机完成此操作。

6、关闭DOS窗口,重新启动计算机,问题解决。

【问题7.22】千兆网我们的和用mdio接口的有什么区别? 我们的教程是没有用到这个接口的

答:MDIO接口是用来配置外部的PHY芯片的,不是用来传输数据的,也就不是做网络协议使用的。 当您需要配置外部的PHY芯片时,可以使用MDIO接口,否则可以不用。

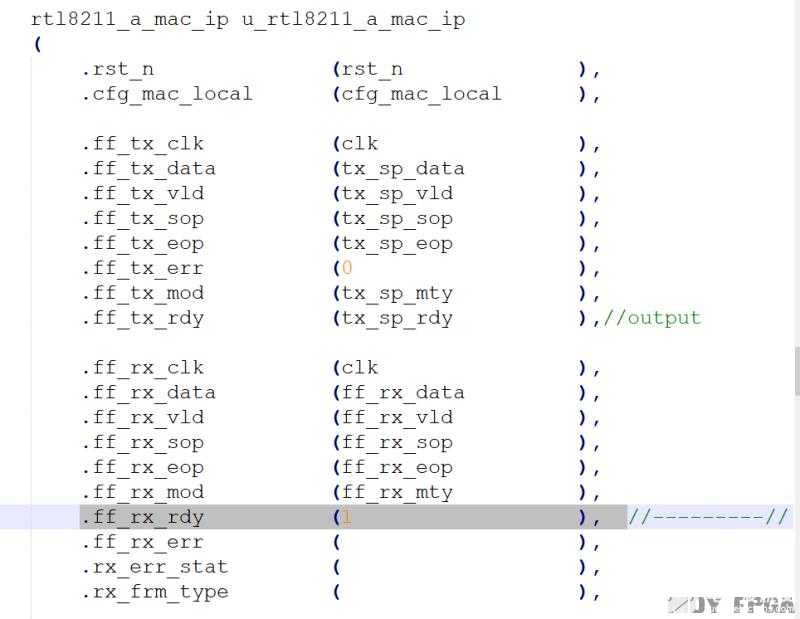

【问题7.23】请问千兆网工程里,输入给MAC_IP核的ff_rx_rdy信号为什么直接置1?跟速率和带宽有关吗?

答:rdy表示下游模块准备好指示信号,如果准备好了就为1,没准备好就为0。 在本案例中,下游模块是rx_mac_analy模块,该模块支持rtl8122_a_mac_ip模块任意速度的数据,

即无论怎么来,下游模块都能接收并正确处理,所以在此处置为1(时刻准备好)就可以了

【问题7.24】请问,一个基础问题,千兆网工程里多个模块都调用了FIFO,在不同模块里调用的fifo的例化名(比如:u_dfifo)能否重复?

答:可以试试操作,在不同模块是可以重复的。

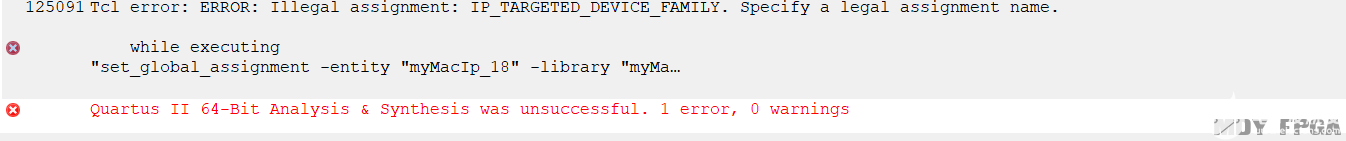

【问题7.25】这个是因为IP核没有破解吗?

答:这个错误就是高版本生成的工程在低版本中打开出现的编译错误,用高版本的quartus打开即可(如18版本的)

【问题7.26】千兆网课程使用的是哪个PHY芯片?

答:本课程使用的是MP801芯片,使用提RTL8211芯片。但课程中,几乎没有涉及到PHY芯片的内容,PHY芯片使用的是默认配置。对于其他PHY芯片,也是通用的。

【问题7.27】千兆网课程是ALTERA,是否与XILINX的通用?

答:本课程主要涉及到各个协议的RTL实现,这部分代码是通用的。但有一个MAC IP核,本课程的工程是使用ALTERA的,XILINX的亦有相同的IP,需要您移植。

总的来说,MAC IP占整个课程的比重不大,大概是5%的内容。

【问题7.28】您的UDP教程里面包不包含ARP和CRC328bit这两个地方的讲解?

答:有arp的讲解,但crc就不包括。

【问题7.29】千兆网课程的源码中有相应的tb仿真代码嘛?

答:没有,但如果要验证功能正确性可以上板验证和仿真文件

【问题7.30】请问下载程序后,电脑检测不到本地以太网,把程序删除又可以检测?

答:可能程序里有复位管脚,把这些PHY芯片复位了。

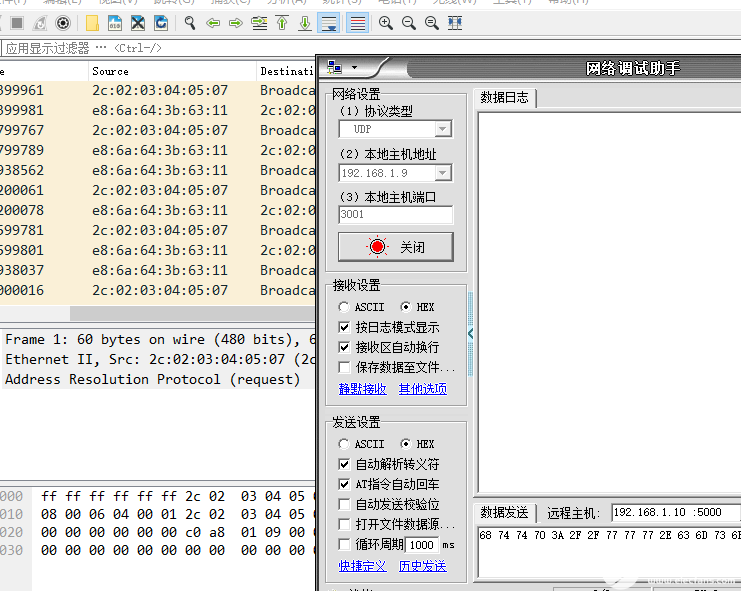

【问题7.31】以太网通信中,抓包工具wireshark能抓到 但网络调试助手收不到 是怎么回事?

答:可能性有如下几种,请逐一排除。

1. IP地址不正确,请检查IP地址,尤其注意目的IP和源IP的区别

2. 端口号不正确,请检查端口号,尤其注意目的端口和源端口的区分。

3. 目的MAC地址不正确,可以尝试发送广播包文(非ARP包文)测试。

4. 包文过短,小于60字节。

【问题7.32】工程仿真的前导码后为什么有两个字节的0呢? 按理说应该紧跟目的MAC地址 图中e8 6a就是目的MAC开头.

答:MAC IP核的有一个32bit对齐的功能,关于该功能意义,请看【问题7.3】。

如果出现上图中问题,有可能是MAC IP核中的32bit对齐功能设置有误。

【问题7.33】千兆网项目中,是否包括TCP协议实现?

答:千兆网项目是使用的UDP协议,而非TCP协议。

目前来说,TCP协议由于有握手机制、重发机制等功能,在逻辑上实现相当困难,暂未看到商用的案例。

【问题7.34】高速采集后的数据 是存到内存或者flash吗 ?

答:激光项目:采集到数据后,内部进行计算和处理,并将结果通过千兆网上传到上位机。

大数据采集项目:从光纤采集到数据后,保存到DDR3中,然后读出送到PCIE上位机。

【问题7.35】请问插上千兆网模块后,PING不通?

答:千兆网模块是一个基于PHY层的模块,不是完整的网卡,实现的是PHY层的协议,没有实现MAC层、TCP/IP层协议。

因此,不可能PING通(因为PING功能是在TCP/IP层实现的)。要实现PING功能,需要编写FPGA程序来实现。

【问题7.36】插上设备后,电脑识别成百兆网问题?

答:上电后,电脑与千兆网模块之间会开展自协商对话,根据双方的环境确定通信速率。如果希望工作在1G,而实质协商成100M,则依次按如下检查。

1. 检查电脑网卡是否支持1G,具体请看网卡设置

2. 检查网线是否支持1G,有类型的要求。

3. 换台电脑试试

4. 以上都测试过后还不行,请找指导老师确认。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论