嗨,我有一个4时钟域的原始设计。在添加第5个时钟域并将设计加载到芯片中后,该设计在硬件中不再起作用。我正在使用斯巴达3E 1600这是一个很大的设计,但作为一个例子,我有一个简单的计数器,如下所示

2019-06-17 14:32:33

文章目录前言时钟及时钟域时钟,时序逻辑的心跳时钟信...

2021-07-29 07:43:44

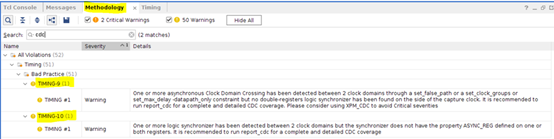

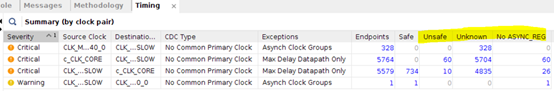

1、跨时钟域信号的约束写法 问题一:没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将

2022-11-15 14:47:59

程序,并检查寄存器的内容。我在rx和tx管脚上连接了作用域,用RS232解码器在作用域上告诉我接收和发送什么。当它工作时,我可以看到字节被发送和接收,当我在RX中断中设置断点时,我可以停止程序。我确认

2020-03-23 07:04:37

ATK-HSWLDBG无线调试器-带小接收端 BURNER 5V

2023-03-28 13:05:52

有线束工程师的学员反馈,在CHS的项目管理模块中新建项目后,无法进行域的选择。而他明明在Capital User模块中新建了域。这种情况该如何解决呢?问题描述:1.Captial User中已经

2021-01-12 17:06:22

的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的60MHz时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出

2021-03-04 09:22:51

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA开发中,遇到的最多的就是异步时钟域了。[size=11.818181991577148px]检查初学者的代码,发现最多的就是这类

2014-08-13 15:36:55

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理技术是IC设计中非常重要的一个

2022-06-24 16:54:26

MCU中怎么确定一个变量的作用域

2023-10-09 06:46:34

“跨域”、“混合域”分析、让工程师可以同时检测任何时间点上模拟、数字、总线与射频信号之间的交互作用,是当今的最佳系统级调试工具,它也将要大大改变你测试的方法。要知道MDO4000混合域示波器怎样有异于频谱分析仪加示波器,或怎样有异于示波器的FFT运算,我们首先从它的结构上阐述它的技术基础。

2019-06-06 06:51:35

的特色之一,但MDO4000 绝不是以上罗列的五种测试工具的简单组合,这五种功能工作在同一时钟、同一触发机制下,使得MDO4000 具有创新的时域、频域、调制域时间相关的跨域分析功能。为此,我们将

2019-07-19 07:02:07

系统,是MDO4000 系列混合域分析仪的特色之一,但MDO4000 绝不是以上罗列的五种测试工具的简单组合,这五种功能工作在同一时钟、同一触发机制下,使得MDO4000 具有创新的时域、频域、调制域时间

2019-07-19 06:43:08

STM32时钟树学习笔记六:有三种不同的时钟源可以用来驱动系统时钟(SYSCLK)1:HSI振荡时钟2:HSE振荡时钟3:PLL时钟用户可以通过配置多个域分频器配置AHB、高速APB(APB2

2021-08-02 07:39:44

SystemClock_Config(),其中配置了所有时钟。那里:启用备份访问(在 PWR->CR 中设置 DBP)重置备份域(在 RCC->BDCR 中设置然后清除 BDRST)将时钟源设置为HSI(BDCR

2023-01-13 06:04:15

1.当HSI被用于作为PLL时钟的输入时,系统时钟能得到的最大频率是64MHz。2.对于内部和外部时钟源的特性,请参考相应产品数据手册中“电气特性”章节。用户可通过多个预分频器配置AHB、高速APB

2021-08-19 08:56:15

,无需计算校验和,不要产生顺序号,无需发送确认报文。下图所示程序,main函数中创建了一些消息队列和UNIX域套接字,并为每个消息队列开启了一个新线程。然后它在一个无限循环中用poll来轮询选择一个

2016-09-02 11:59:01

在看u***,书上说u***数据包的同步域可以同步主机端和从机端的时钟,这个怎么理解u***接口没有时钟线,我又想到了单片机串口的波特率,不知道有没有关系,向大家请教了这个简单的问题,很想知道答案

2019-07-02 18:06:13

XP退域后怎么才能加回以前的域是这样一件事情,我的XP电脑是不连接网络的,但是它之前的用户一直连接那域, 这次我修改的工作组,结果那域不见了,用户也进不去了;请问还能加回以前的域吗?

2012-06-09 16:41:55

在matlab中对二值图像不同的连通域进行标写序号该用什么语句函数啊?

2016-10-13 20:26:21

python变量的作用域1. 作用域Python的作用域可以分为四种:L (Local) 局部作用域E (Enclosing) 闭包函数外的函数中G (Global) 全局作用域B

2022-03-03 16:50:37

双口RAM如何实现跨时钟域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

在调试是DS1302里面的时间时钟读不到LCD中,请各位看看

2012-07-18 09:55:04

的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的60MHz时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出

2021-02-21 07:00:00

60MHz的时钟上升沿变化,而FPGA内部需要使用100MHz的时钟来处理ADC采集到的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。 先利用ADC芯片提供的60MHz

2021-01-08 16:55:23

的主要目标是将该板与模拟器件AD9229 ADC接口,ADC具有串行LVDS接口,传输速率为480 Mbps。生成DDR数据时钟和帧时钟用于数据捕获。 ZESTET1板运行频率为125 MHz,但

2019-06-12 13:30:44

异步bus交互(一)— 两级DFF同步器跨时钟域处理 & 亚稳态处理1.问题产生现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率

2022-02-17 06:34:09

有谁知道为什么transcieverwizard会建立一个7位移位寄存器来跨越时钟域?此代码位于示例设计重置状态机* _sync.v块中。这是针对V7的吗?谢谢,Roopa

2020-07-29 10:52:06

目录一、什么是IO电源域配置?二、IO电源域配置方法三、RK809电源芯片dts配置一、什么是IO电源域配置?其实就是管理IO输出的电平;假如硬件上IO电源域配置为3.3V,则IO输出最大电平为

2021-12-27 06:44:14

什么是UPF功率域和域边界?

2021-09-29 06:08:09

ISE中编译为.bit文件。系统被设计为多重锁定域,其中第一个域只是获取数据并负责写入和重置共享FIFO,并且从相机计时(因此也以相同的时钟速度运行 - 大约8MHz) - 此信号用于Sys.gen。具有

2019-08-27 06:28:47

如何测量系统中时间相关的时域和频域信号?以RFID读写器系统为例,介绍MDO4000的跨域调试应用

2021-04-09 06:18:12

在支持位操作的单片机中,如C51,使用位域定义变量或者寄存器,操作方便并且节约空间。 问题1:但是很多单片机不支持位操作,仍然使用位域,那么汇编语言将如何执行?我理解的是,汇编间接实现位操作,但是

2016-09-16 22:25:32

c语言里规定的位域的方式进行比特位操作,可以对某一位进行操作;一般情况下,比如普通的存储数据的区域,位域没有任何意义。通常,位域可以用来进行对一些要进行比特位操作的场合,比如标志寄存器的标志位清零

2017-08-03 09:54:32

一、位域描述存放一个开关量或者其他开关状态时,用一位二进位即可。为了减少嵌入式内存资源的开销,可以使用位域进行定义,位域是C语言支持的一种数据结构,称为“位域”或“位段”。“位域”是把一个字节中

2021-12-15 07:47:52

#hello,JS:04作用域和作用域链

2019-09-10 10:21:18

关于cdc跨时钟域处理的知识点,不看肯定后悔

2021-06-21 07:44:12

关于异步时钟域的理解的问题: 这里面的count[25]、和count[14]和count[1]算是多时钟域吧?大侠帮解决下我的心结呀,我这样的理解对吗?

2012-02-27 15:50:12

解决了调试系统软/硬件协同验证中JTAG信号交互时的时序匹配问题。1 自适应时钟技术1.1 基本概念自适应时钟(Adaptive Clocking)是一种信号同步技术,其基本原理来源于异步电路设计中的自动

2019-05-21 05:00:22

你好,我在Viv 2016.4上使用AC701板。我需要同步从一个时钟域到另一个时钟域的多位信号(33位)。对我来说,这个多位信号的3阶段流水线应该足够了。如果将所有触发器放在同一个相同的切片

2020-08-17 07:48:54

在调试GD32芯片时遇到了时钟配置错误的问题,仔细研究文档和网上资料,认真调试之后做了以下总结,希望能帮到同样有类似困惑的你。**1.认识时钟HXTAL:高速外部时钟;LXTAL:低速外部时钟

2021-07-23 10:06:14

综合试验基地,主要从事雷电干扰防护和城市轨道交通安全的研究。客户研发方向为智能家居产品,使用无线传输数据,其中RF模块外购。要验证射频模块的功能和指标,以及联合调试在实际工作中的问题。射频模块于系统之间

2019-06-06 07:18:26

1、基于RK3399的Linux kernel中CPU时钟管理介绍绝大多数的电子器件都是由时钟驱动其工作的。而SoC芯片或电路板中的时钟以树状结构呈现,按时钟域进行划分,按照不同的时钟需求

2022-06-21 16:00:23

时钟域电路设计中由于不存在时钟之间的延迟和错位,所以建立条件和保持条件的时间约束容易满足。而在多时钟域里由于各个模块的非同步性,则必须考虑亚稳态的发生,如图1所示。 2 多时钟域数据传递方案 多时钟

2011-09-07 09:16:40

时钟)的逻辑。在真正的ASIC设计领域,单时钟设计非常少。2、控制信号从快时钟域同步到慢时钟域与同步器相关的一个问题是来自发送时钟域的信号可能在被慢时钟域采样之前变化。将慢时钟域的控制信号同步到快时钟域

2022-04-11 17:06:57

。为了获得更多,我使用时钟向导添加了较慢的时钟,以便在调试设置中使用它们,直到比特流生成一切正常,但是当涉及到调试时,我收到此警告:open_hw_targetINFO:[Labtoolstcl

2020-08-17 10:04:52

时钟域处理。先利用 ADC 芯片提供的 60MHz 时钟将 ADC 输出的数据写入异步双口 RAM,然后使用 100MHz 的时钟从 RAM 中读出。对于使用异步双口 RAM 来处理多 bit 数据

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

你好,我很难理解如何正确设计一个时钟使能信号,以促进两个同步时钟之间的时钟域交叉,其中一个是慢速,一个是快速。我所拥有的情况与下图所示的情况非常相似(取自UG903图5-18)。如何确保CLK2产

2019-04-15 08:36:30

如何通过Mstar平台对RTC时钟进行调试?

2021-10-13 07:34:03

对于仿真而言,与DUT打交道的无非是接口信号的驱动,而我们的设计往往是同步的,这就与避免不了与时钟信号打交道。时钟域在SpinalHDL中,时钟域的概念包含了时钟、复位、软复位、时钟使能等系列信号

2022-07-26 17:07:53

亲爱的朋友们, 我有一个多锁设计。时钟为50MHz,200MHz和400Mhz。如果仅使用400MHz时钟并使用时钟使能产生200Mhz和50Mhz时钟域。现在我需要将信号从一个时钟域传递到另一个

2019-03-11 08:55:24

把时钟变慢可以有效增加DFF的setup时间吗?时钟域A的多bit信号一定要经过同步才能被时钟域B采用吗?

2021-11-02 08:26:02

时钟域处理。先利用 ADC 芯片提供的 60MHz 时钟将 ADC 输出的数据写入异步双口 RAM,然后使用 100MHz 的时钟从 RAM 中读出。对于使用异步双口 RAM 来处理多 bit 数据

2020-10-20 09:27:37

理解UPF功率域和域边界一、介绍 在先进工艺技术的低功耗之争中,统一功率格式(UPF)在降低动态和静态功率方面起着核心作用。较高的流程节点绝对具有吸引力,因为在较小的die区域中可以以较低的成本

2021-07-26 06:23:19

上完成复杂的测量。 对嵌入式无线电,如图16所示的Zigbee设计.您可以触发 RF事件启动,观察微处理器控制器解码的SPI控制线的命 令行时延、启动过程中的漏极电流和电压以及发生的任何 频谱事件。您现在可以在一个画面中,以时间相关的方式 观察无线电的所有域:协议(数宇)、模拟和RF。

2017-08-31 08:55:59

电源域隔离是电压监控ADC系统的一个重要设计要点,不合理的电源域隔离可能导致芯片关不掉,芯片发生闩锁,甚至芯片损坏的后果。这些问题主要是由于芯片内部ESD保护二极管的限制,那么如何更好处理电源域隔离设计呢?

2019-02-25 09:08:09

电源域是什么?

2017-08-07 18:59:27

相同的IO域VDDPST和VDD的电压输入是一样的吗?RK3399中的IO域电压该怎样去选择呢?

2022-03-07 07:10:14

逻辑出身的农民工兄弟在面试时总难以避免“跨时钟域”的拷问,在诸多跨时钟域的方法里,握手是一种常见的方式,而Stream作为一种天然的握手信号,不妨看看它里面是如做跨时钟域的握手

2022-07-07 17:25:02

和发送数据,处理异步信号,以及为带门控时钟的低功耗ASIC进行原型验证。 这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步单元(触发器、同步RAM块以及流水乘法器等)都使用同一个网络

2022-10-14 15:43:00

型的问题,并且这些问题的解决方案也有所不同。本文讨论了不同类型的跨时钟域,以及每种类型中可能遇到的问题及其解决方案。在接下来的所有部分中,都直接使用了上图所示的信号名称。例如,C1和C2分别表示源时钟

2022-06-23 15:34:45

bq1_dat稳定在1,bq2_dat也输出稳定的1。最后,从特权同学的经验和实践的角度聊一下。跨时钟域的信号同步到底需要1级还是2级,完全取决于具体的应用。如果设计中这类跨时钟域信号特别多,增加1级

2020-08-20 11:32:06

] set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]设计中fifo前端时钟域是cmos_pclk在TimeQuest

2018-07-03 11:59:59

,以及为带门控时钟的低功耗ASIC进行原型验证。本章讨论一下在FPGA设计中多时钟域和异步信号处理有关的问题和解决方案,并提供实践指导。

这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步

2023-06-02 14:26:23

高速无线调试器HSWLDBG BURNER 3.3,5

2023-03-28 13:06:20

目标的运动速度、加速度,是估计目标后续空间位置必需的重要参数,对光电设备持续捕获目标具有重要现实意义。在分析经纬仪交汇跟踪目标原理的基础上,将目标的运动分解

2010-01-11 11:10:12 10

10 将空间飞行器分为目标和射弹两类,对二者撞击过程中的弹目交汇模型进行研究。在目标构型分析的基础上,基于基本几何形体建立目标等效模型,实现了典型目标的数学描述。考虑弹

2011-05-03 17:18:00 0

0 针对室内CCD交汇测量的试验环境,通过添加辅助光源照明,在基于CCD立靶测量原理的条件下,分析了室内立靶影响捕获率的原因,并建立了室内立靶的捕获率模型。该模型能够为室内立

2012-04-05 16:21:35 44

44 时钟芯片DS1302目前得到广泛的应用,但是DS1302的调试还是很有难度的。这篇文章就来说说DS1302时钟芯片的调试惊艳,奉上时钟芯片调试程序贴,是网上下的,我已经通过硬件测试,绝对没有问题。

2017-10-19 11:12:24 10225

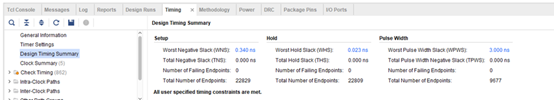

10225 博文介绍了如何调试设计中的时钟域交汇问题。 问题说明: 在此设计中,用户生成了比特流并将其用于器件编程,在硬件上进行测试时,用户发现少量时钟域上无法获得期望的功能。 用户对行为仿真和实现后仿真进行了测试,发现信号上可得到正确的结果。 同时,这些用

2021-08-20 09:32:21 5152

5152

本篇博文中的分析是根据真实客户问题撰写的,该客户发现在现场出现罕见的比特翻转, 本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。 最终发现,此问题是由于时钟域交汇 (CDC) 处理

2021-09-10 09:44:55 1172

1172 S32K14x系列MCU时钟调试笔记

2021-11-18 16:51:02 45

45 第二章 电机调试和时钟配置上一章我们移植好了单片机,于是在我们兴奋地看到自己点亮了LED之后,开始着手准备驱动的设置,那么这里面又会有什么问题呢?我把我遇到的困难和问题记录在此,同时也为你们答疑解惑。电机介绍can通信回顾时钟设置在线调试...

2021-12-04 18:06:05 7

7 SWD是STM32单片机常用的调试模式之一。它通过单一的调试引脚(SWDIO)和时钟引脚(SWCLK)来进行调试和编程操作。使用SWD调试模式,可以进行单步调试、断点调试、查看寄存器状态等操作。

2023-12-02 17:14:03 1322

1322

电子发烧友App

电子发烧友App

评论