1.PCIe 3.0 x16配置下,支持8路4K(3840x2160p)@60Hz的采集与显示2.PCIe 3.0 x8配置下,支持4路4K(3840x2160p)@60Hz的采集与显示3.PCIe

2024-03-13 13:59:45

电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0 ,基于描述符链表信息完成自己通道的数据传输,然后使用MSI中断发出描述符完成或错误的信令。内核也提供多达16个输出到Host的用户中断信号。主机可以通过以下2个接口访问用户逻辑:ØAXI4

2024-03-07 13:54:29

VS034 PCie X4 X16 环出HDMI 游戏直播4K电脑内置采集卡 .主机接口:PC1E2.0X420Gbps传输带宽 ·音频:直播设备/电脑音频

2024-02-23 13:55:47

;

8路用户LED;

4路拨码开关;

4路按键;

36个用户可扩展I/O(其中包括一路SPI硬核接口和一路I2C硬核接口)

支持的开发工具思德普开发的Web IDE以及Lattice官方提供

2024-01-31 21:01:32

如题,利用现有例程运行BF70X,计划读取LPDDR中的数据,但实际发现写进数据为0x100(或任意值)时,读取出来的数据为恒定值0x0000ffff;计划自己对LPDDR驱动进行调试,采用怎样的方法or 步骤进行调试或者修改bug,以实现正常的读写数据。

2024-01-12 07:10:04

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 464

464

)

DDR3内存条,240引脚(120针对每侧)

DDR4内存条,288引脚(144针对每侧)

DDR5内存条,288引脚(144针对每侧)

DDR芯片引脚功能如下图所示:

DDR数据线的分组

2023-12-25 14:02:58

)

DDR3内存条,240引脚(120针对每侧)

DDR4内存条,288引脚(144针对每侧)

DDR5内存条,288引脚(144针对每侧)

DDR芯片引脚功能如下图所示:

DDR数据线的分组

2023-12-25 13:58:55

,其中 FTC664 核主频可达 1.8GHz,FTC310 核主频可达 1.5GHz。

板载 64 位 DDR4 内存,有 2G 和 4G 两个版本,支持 SD 或者 eMMC 外部存储。主板板载

2023-12-10 21:27:03

3是目前使用最为广泛的计算机内存标准,它已经服务了计算机用户多年。但是,DDR4内存随着技术的进步,成为了更好的内存选择。本文将详细介绍DDR4和DDR3内存的各种区别。 1. 工作频率 DDR3内存的标准工作频率为1600MHz,而DDR4内存标准则为2133MHz。这意味着DDR4内存的传输速度

2023-10-30 09:22:00 3895

3895 。

关键特性

全志H618,四核ARM Cortex™-A53处理器

ARM Mali G31图形处理器

WIFI & 蓝牙

2G LPDDR4 RAM

8G eMMC闪存

1x

2023-10-08 15:25:13

数据和读写的测试数据一致,说明从0x1FFFF810开始往后的地址用户可以正常使用![]

总结:用户选择字存储区的前4个字(16个字节)存储区是有专门用途或格式要求的(每个字节有对应的反码),而后

2023-09-30 18:11:10

相对于DDR3, DDR4首先在外表上就有一些变化,比如DDR4将内存下部设计为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过渡,这样的设计可以保证金手指和内存插槽有足够的接触面

2023-09-19 14:49:44 1484

1484

已保留有6位SDR空间。最后,它占用的片上空间更少,单个封装最多可以包含12GB的DRAM。不利的一面是,LPDDR4X不能与LPDDR4向后兼容。即使设备与更快的LPDDR4内存兼容,它也可能不适用于LPDDR4X。

2023-09-19 11:09:36 8383

8383

CW32F003x3/x4是一款基于eFlash的单芯片微控制器,集成了ARM®Cortex®-M0+内核

具有高达48 MHz的主频率、高速嵌入式存储器(高达20 KB的FLASH和

至3K字节

2023-09-14 08:16:19

CW32F030x6/x8 是基于 eFlash 的单芯片微控制器,集成了主频高达 64MHz 的 ARM® Cortex®-M0+ 内核、高速嵌入式存储器(多至 64K 字节 FLASH 和多至

2023-09-14 07:19:09

CW32F030x6/x8是一款基于eFlash的单芯片微控制器,集成了ARM®Cortex®-M0+内核

主频率高达64MHz,高速嵌入式存储器(高达64K字节的FLASH和高达

8K字节

2023-09-14 07:03:34

STM32G431x6/x8/xB器件基于高性能ARM®Cortex®-M4 32位RISC内核。

它们的工作频率高达170兆赫。

Cortex-M4内核采用单精度浮点单元(FPU),支持所有ARM

2023-09-13 06:03:29

DDR4/LPDDR4/LPDDR4x接口

支持4x16bit DDR4

支持2x32bit LPDDR4/LPDDR4x

DDR4最高速率3200Mbps

LPDDR4/LPDDR4x最高

2023-09-12 10:23:38

)

•4种操作模式:

•独立模式:外部增益设置

•追随者模式

•PGA模式:内部增益设置(x2、x4、x8、x16)

•PGA模式:内部增益设置(x2、x4、x8、x16),反相输入用于滤波。

2023-09-12 08:09:23

将需要在现有项目中进行大量更改。

新的DFP基于意法半导体的STM32CubeFx固件包,不会对目录结构或单个文件进行任何更改。

此外,还有一个MDK文件夹,其中包含一组示例项目和模板文件,以及

2023-09-04 07:33:25

)处理

网络接口- 1 个千兆以太网接口

支持RGMII、RMII两种接口模式

支持TSO、UFO、COE等加速单元

外部存储器接口- DDR4/LPDDR4/LPDDR4x 接口

支持2 x 16

2023-08-23 10:04:44

LPDDR4X和LPDDR5(低功耗DDR4和DDR5)都是移动设备和嵌入式设备中最流行的内存技术。它们被广泛应用于智能手

2023-08-21 17:28:29 19710

19710 的内存速度和更低的功耗。 LPDDR4和LPDDR4X的主要区别在于功耗上的优化。 LPDDR4内存 LPDDR4内存是一种第四代低功耗DDR内存,是DDR4和DDR3的改进版本。该内存的最大优点是速度

2023-08-21 17:16:44 5961

5961

CPU管脚,对应的GND过孔数量,建议严格参考模板设计,不能删减GND过孔。8层通孔的PCB模板,CPU管脚GND过孔设计如下图所示,黄色为DDR管脚信号,地管脚为红色。

**Part.**2

信号换

2023-08-17 17:23:30

数量,建议严格参考模板设计,不能删减GND过孔。8层通孔的PCB模板,CPU管脚GND过孔设计如下图所示,黄色为DDR管脚信号,地管脚为红色。

2、信号换层前后,参考层都为GND平面时,在信号过孔

2023-08-16 15:15:53

PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

使用DDR4作为外接存储单元时,蜂鸟e203的访问地址为0x40000000,但是经过vivado的Block design后使用DDR4,在板子上跑测试DDR4读写程序,报store访问异常

2023-08-11 06:17:58

GB eMMC

TQ3568_COREB_V1.0核心板(工业级,2+16)

TMC3568CBV1X

RK3568J

2GB LPDDR4

16GB eMMc

TQ3568_COREB_V1.0核心板

2023-08-10 16:52:37

DDR5的主板不支持使用DDR4内存。DDR5(第五代双倍数据率)和DDR4(第四代双倍数据率)是两种不同规格的内存技术,它们在电气特性和引脚布局上存在明显差异。因此,DDR5内存模块无法插入DDR4主板插槽中,也不兼容DDR4内存控制器。

2023-08-09 15:36:25 12808

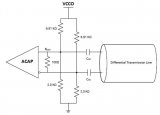

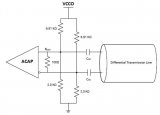

12808 本文旨在呈现使用 DDR4、LPDDR4 或 LPDDR4X 存储器控制器的 Versal ACAP 器件的外部参考时钟电路要求

2023-07-10 16:02:23 814

814

x8/x16/x32/x64

- 可以内部接ADC及比较器

内置8路COMP

-C0失调电压失调电压<±1mv ,其他失调电压<±4mv

-3路8BIT DAC及4

2023-06-26 09:23:42

如题降低lpddr4时钟频率为800M,使用lpddr4型号为MT53E1536M32D4DT-046

应用MX8M_Plus_LPDDR4_RPA_v8.xlsx配置lpddr4如下

应用工

2023-06-02 07:26:51

长度 =1)进行测试,结果如下:

多项式是 0x10211021(自定义)。起始 CRC 为零,无交换,无输出重整

测试字节值正确的结果CRCA 结果

00x000000000x00000000

1个

2023-06-01 08:39:41

解决方案,配置方式比较灵活,采用软核实现 DDR memory 的控制,有如下特点:

➢支持 DDR3

➢支持 x8、x16 Memory Device

➢最大位宽支持 32 bit

➢支持裁剪的 AXI4

2023-05-31 17:45:39

在我的设计中,使用了IMX8M Plus+PCA9450C+LPDDR4(参考NXP EVK)。

现在 ,我想降低SOC和LPDDR4的工作频率,

但是用cat命令看不到frequencis文件

2023-05-31 07:22:46

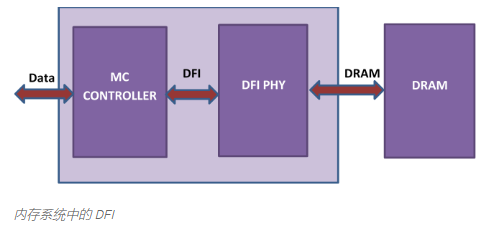

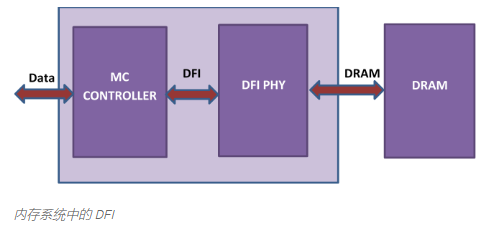

、时序和可编程参数。DFI 适用于所有 DRAM 协议,包括 DDR4、DDR3、DDR2、DDR、LPDDR4、LPDDR3、LPDDR2 和 LPDDR。

2023-05-26 15:27:31 4576

4576

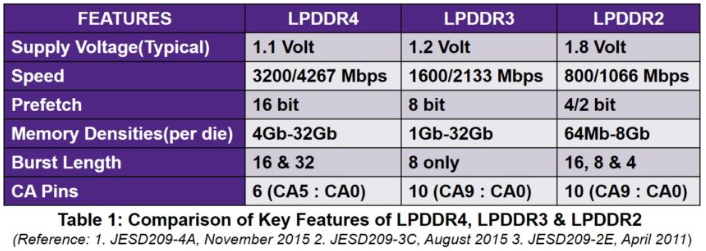

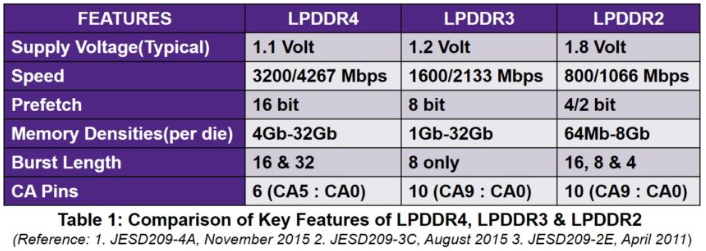

DRAM 存储器是任何计算设备的“心脏”,例如智能手机、笔记本电脑、服务器等。LPDDR4 主要用于提高智能手机、平板电脑和超薄笔记本电脑等移动计算设备的内存速度和效率。它支持高达 4267Mbps

2023-05-26 14:34:07 3497

3497

你好

我正在尝试使用带有 langdale (6.1.1) 的 Yocto imx8mm_evk 为 imx8mm_evk_lpddr4 构建完整图像。

创建根图像时,bitbake 失败并出

2023-05-25 08:08:33

如果是PCIe 4.0 x16插槽,那第二条PCIe插槽接入设备之后,第一条PCIe插槽也会降速到x8,如今RTX 4060系列的PCIe主动减少到x8,意味着使用主板第二条x8通道时不会对显卡有影响。

2023-05-23 10:06:07 11315

11315

我已经从 nxp 网站下载了 imx8mp - Android 13 代码的源代码。

但是当我开始为 imx8mp-evk 用户调试映像构建引导加载程序时,出现以下错误

2023-05-22 08:44:31

您的组织中进行此更改的人的意见。

接下来,我在我的脚本中为 1GB 模块添加了将 MAARCR 设置为 0x54420010,这也导致 DDR 压力测试运行良好。

您是否对某些问题有任何想法或反馈

2023-05-22 07:38:52

memory 控制器解决方案,配置方式比较灵活,采用软核实现 DDR memory 的控制,有如下特点:

➢支持 DDR3

➢支持 x8、x16 Memory Device

➢最大位宽支持 32 bit

2023-05-19 14:28:45

我有一块自制的imx8mp主板,使用DDR4的型号是:K4ABG165WA-MCWE,单片容量32Gb,主频3200Mhz,我的主板使用了两颗芯片,但是使用MX8M_Plus_DDR4_RPA_v9.xlsx无法完成配置

2023-05-17 06:12:25

是edge-aligned,符合Read Mode特征(这张图里还有其他线索,常分析DDR信号的同行可能已经发现,下面会讲到)

而且此测试专门设计了LPDDR4 Interposer,测点在

2023-05-16 15:43:05

有没有办法重置和重新初始化 DDR 控制器?DRAM 类型是 LPDDR4。

我们的目标:我们尝试为组装有不同大小 RAM 的电路板系列实施解决方案。

为了获得可重现的结果,我们寻求在尝试下一个配置

2023-05-16 09:03:04

1) 需要 11x11 IMX93 封装的 LPDDR4 线路(或全部)的传播延迟值。在项目中使用 Altium。在我们准备调整 LPDDR4 迹线时需要。在 IBIS 模型中没有看到这一点。

2

2023-05-09 10:36:32

IMX8MM_DDR4_EVK 作为起点。但这是我第一次使用 Yocto。

哪些文件以及我应该更改或/和添加到图层的位置?看来我应该更改 DDR4 的设备树和配置文件。

谁能给我一个提示?

2023-05-09 08:03:48

我需要帮助寻找用于 imx8m-plus 的替代可用 LPDDR4 6GB,因为用于开发板的 LPDDR4 不可用。

2023-05-09 07:33:34

请帮助检查MCIMX8DXL是否可以支持2GB LPDDR4解决方案?

2023-05-06 08:09:49

我们使用 LPDDR4-3200,3G Memory 应用于 I.MAX8MQ (MIMX8MQ6DVAJZAB)。

能否提供LPDDR4-3200 3G“Row 16bit”所有颗粒建议的最新搭配方案或列表?

2023-05-06 07:59:39

的事情。如果我更改任何设置,我会收到“不支持”错误。选择的 CPU 是 MIMX8ML4xxxKZ。据我所知,Pin 工具仍然可以正常工作。要重现,打开新配置,创建新配置,选择 MIMX8ML4xxxKZ。去在引脚工具和 DDR 工具之间来回几次和/或执行“更新代码”。

2023-05-05 06:45:36

我有一块使用基于 i.MX8QM MEK 板的 i.MX8QM 的板。我使用了 2 x MT53D512M32D2(总计 4GB DDR 内存)并且它可以正常工作。

现在我想把内存加倍到 8GB。我

2023-05-04 06:39:14

我们目前正在使用 LPDDR4 设计一个新的基于 iMX8M Plus 的定制板:Micron MT53D512M32D2,它有两个版本:MT53D512M32D2-053

2023-04-28 07:42:53

启动,但是,我们想要进行 DDR 校准并寻找 LPDDR4 校准二进制文件,这些二进制文件会生成/考虑来自外部振荡器的 CLK 源。

如果您能在DDR 校准工具的源代码中添加上述小改动(请参阅上面的补丁)并共享二进制文件,这将是一个很大的帮助。

2023-04-27 08:11:25

]==============================================

[i]DDR 配置

[i]DDR 类型是 LPDDR4

[i]数据宽度:16,bank num:8

[i]行大小:17,col 大小:10

[i]使用一个

2023-04-26 07:40:25

我有 LS1046AFRWY 板的克隆。高速公路板使用 MT40A512M16JY-083E:B(商业级DDR4)。我的克隆使用 MT40A512M16JY-083E IT:B(工业级 DDR4

2023-04-24 08:08:20

at offset 0x031e4b48.

Walking Ones: ok

Walking Zeroes: ok

8-bit Writes: ok

16-bit Writes : ok

Done

结果与上面的压力测试类似。

你能告诉我一些解决方案或我应该检查哪一点吗?

2023-04-23 14:32:31

i.mx8m 加支持 lpddr4 和 lpddr4x

2023-04-21 06:11:49

将 DDR4 内存添加到 imx8mp

2023-04-20 10:59:17

我目前正在使用 LPDDR4-3000 作为内存设计带有 i.MX8M Mini 的定制 PCB。在将 LPDDR4-3000 路由到 i.MX8M Mini 时,我有多个问题。我知道i.MX 8

2023-04-20 07:44:58

NXP IMX8M Mini DDR4 校准

2023-04-20 07:36:55

对 SCFW 的更改基本上是为 LPDDR4 调整 DCD 表(基于 MX8QXP_C0_B0_LPDDR4_RPA_1.2GHz_v16)。 我想为此自定义板设置构建系统以使用此文件而不是

2023-04-19 07:51:29

是速度等级和模具数量(从 2 个模具变为 1 个模具)。可能需要对软件进行哪些更改(如果有的话)以支持新部件(1 个芯片而不是 2 个芯片和更快的速度等级)?我们是否需要重新运行 DDR 工具以生成要在 LPDDR4 控制器中编程的新 bin 文件?

2023-04-19 06:56:55

........................... 62.3 DDR4 接口原理图.................72.4 兼容的 JEDEC DDR4 器件

2023-04-14 17:03:27

5-7. 使用 LP87334D 为支持 LPDDR4 存储器的 AM243x(ALV 封装)供电......................................... 10图 5-8

2023-04-14 16:40:42

给一个内核以简化软件任务分区• DDR 子系统 (DDRSS)– 支持 LPDDR4、DDR4 存储器类型– 具有内联 ECC 的 16 位数据总线– 支持高达 1600MT/s 的速度片上系统

2023-04-14 15:42:08

2 组 64bit 的DDR4 SDRAM,每组容量2GB,可稳定运行在2400MT/s。支持PCIE Gen3 x8模式及一路FMC HPC接口。同时可提供 Windows,Linux 上位机驱动

2023-04-13 15:56:21

组DDR4 SDRAM缓存单元,每组最大支持4GB容量,72bit(包含ECC,8bit),可实现进行复杂逻辑与算法时的数据缓存。PCIe总线最大支持Gen3、x8,具备超强的数据吞吐能力;前面板预留

2023-04-08 10:38:05

我们试图为imx8mm-lpddr4-evk构建图像。但我们面临问题。$ DISTRO=fsl-imx-wayland MACHINE=imx8mm-lpddr4-evk source

2023-04-04 06:53:00

你能告诉我在哪里可以获得 i.MX8M Plus 的详细 DDR4 布局跟踪路由指南吗?我在 i.MX8M Plus 硬件开发人员指南中找不到它。顺便问一下,NXP 有带 DDR4 的 i.MX8M Plus 评估板吗?

2023-03-31 07:52:02

所有步骤后我未能启动,很可能是因为其中一个命令仅指定为从 FlexSPI 启动:“放 [jtag::scan_io dr 64 0x0000010071FF001F]; // 用于 FlexSPI 启动

2023-03-30 09:00:41

:2022 年 10 月 25 日 18:55:21错误:BL2:加载图像失败(-2)身份验证失败我认为我们必须更改 atf\plat\nxp\soc-ls1046\ls1046ardb\ddr_init.c 中的配置,但我不知道它们是什么意思。是否有任何工具可以轻松生成配置或任何文档描述了参数的含义?

2023-03-24 08:50:43

通过故障参考“DDR_imx8+_8GB”参考“Mscale_ddr_tool _v3.30”通过测试请参阅“LPDDR4_2000MHz_8GB”以获取从 RPA excel for 8GB 内存生成

2023-03-24 06:54:09

电子发烧友App

电子发烧友App

评论