先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6406

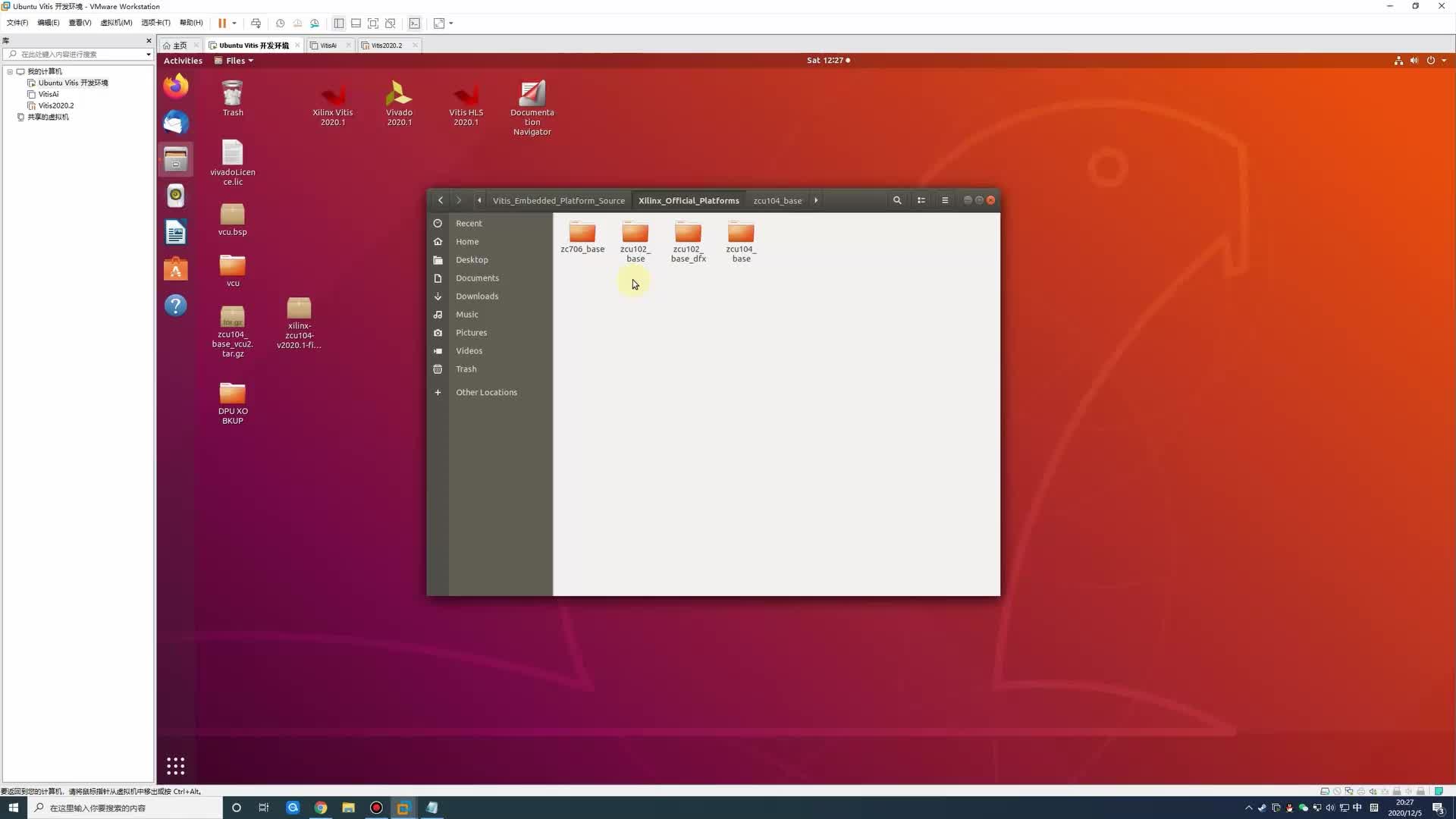

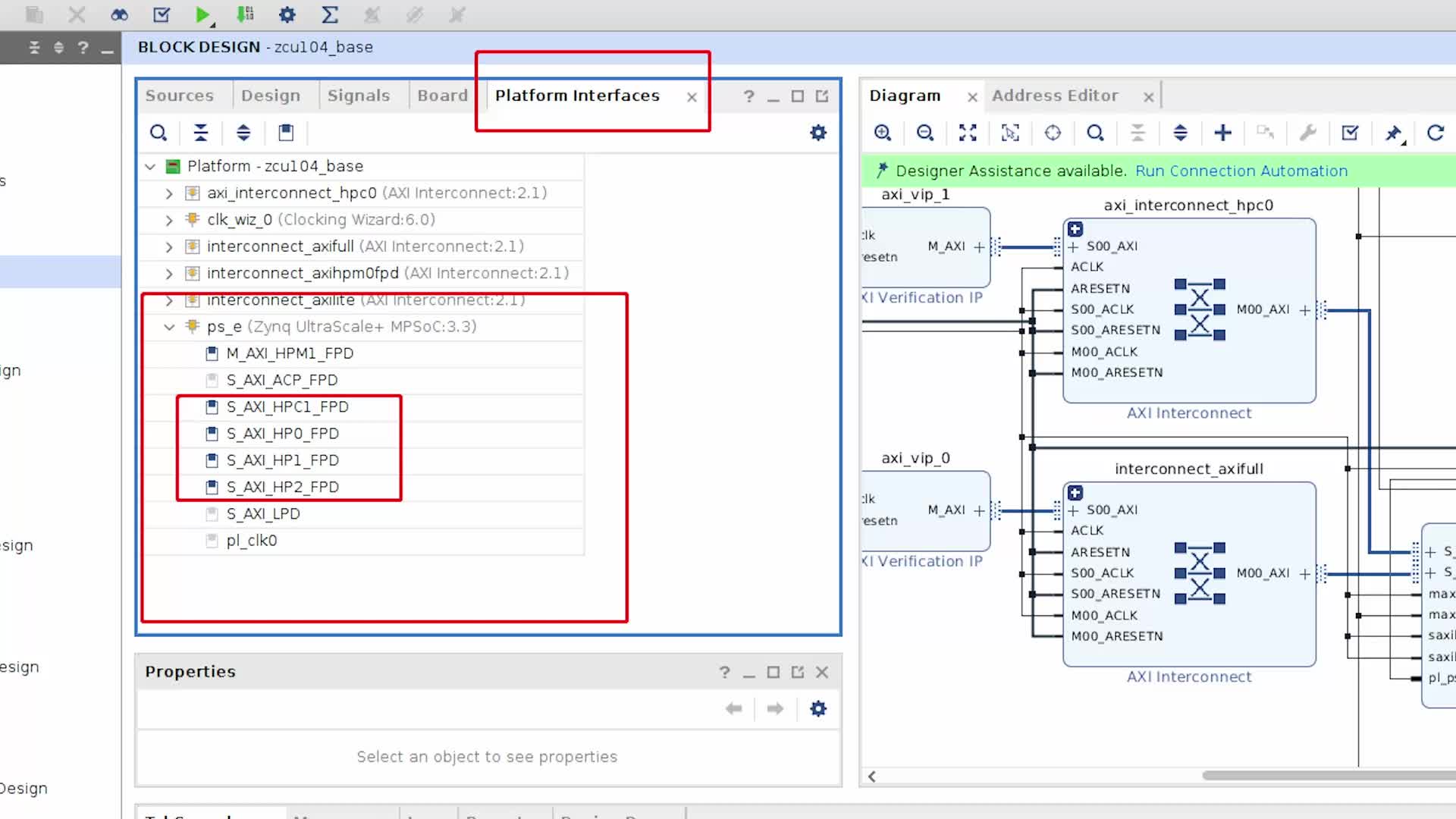

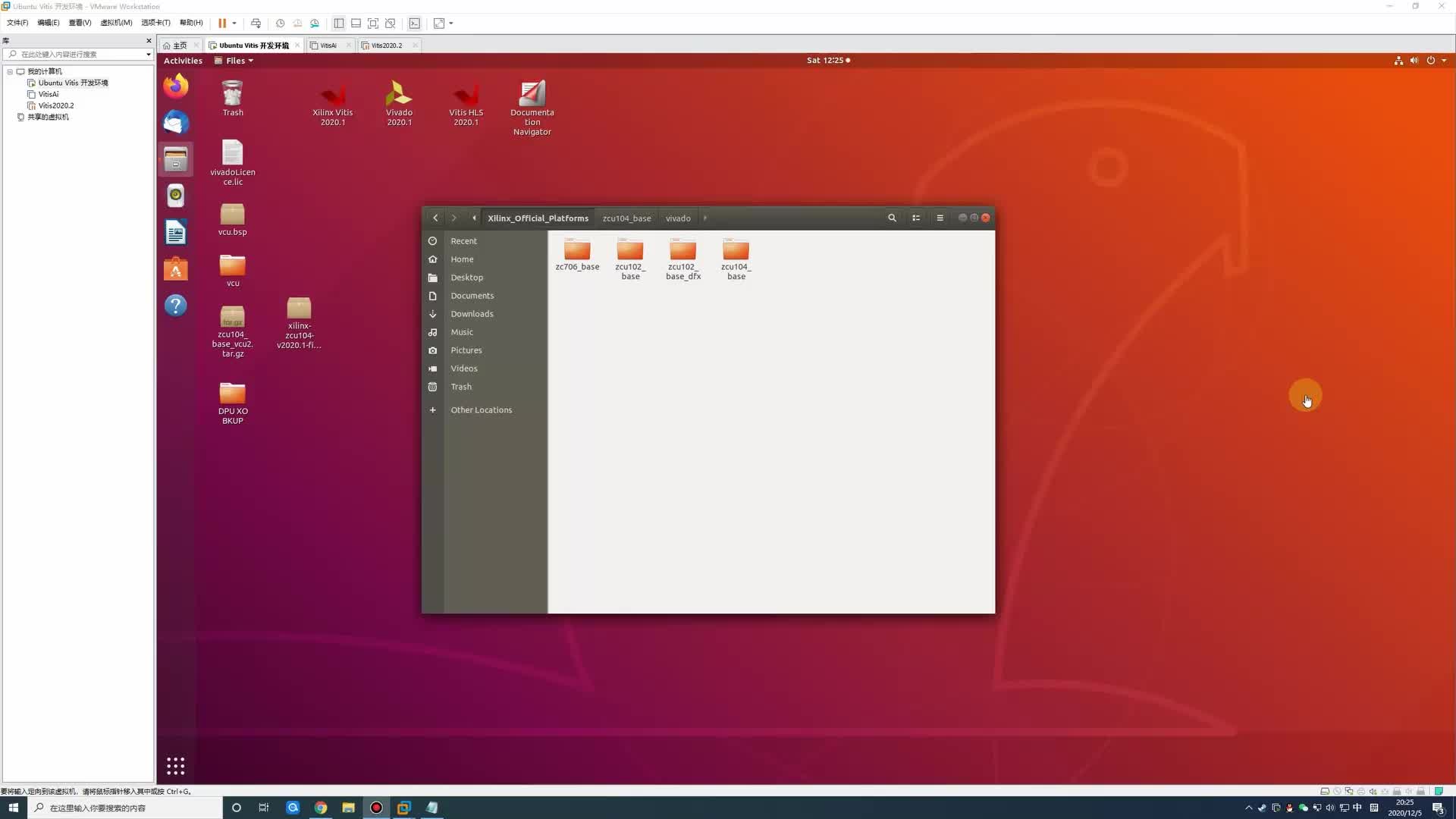

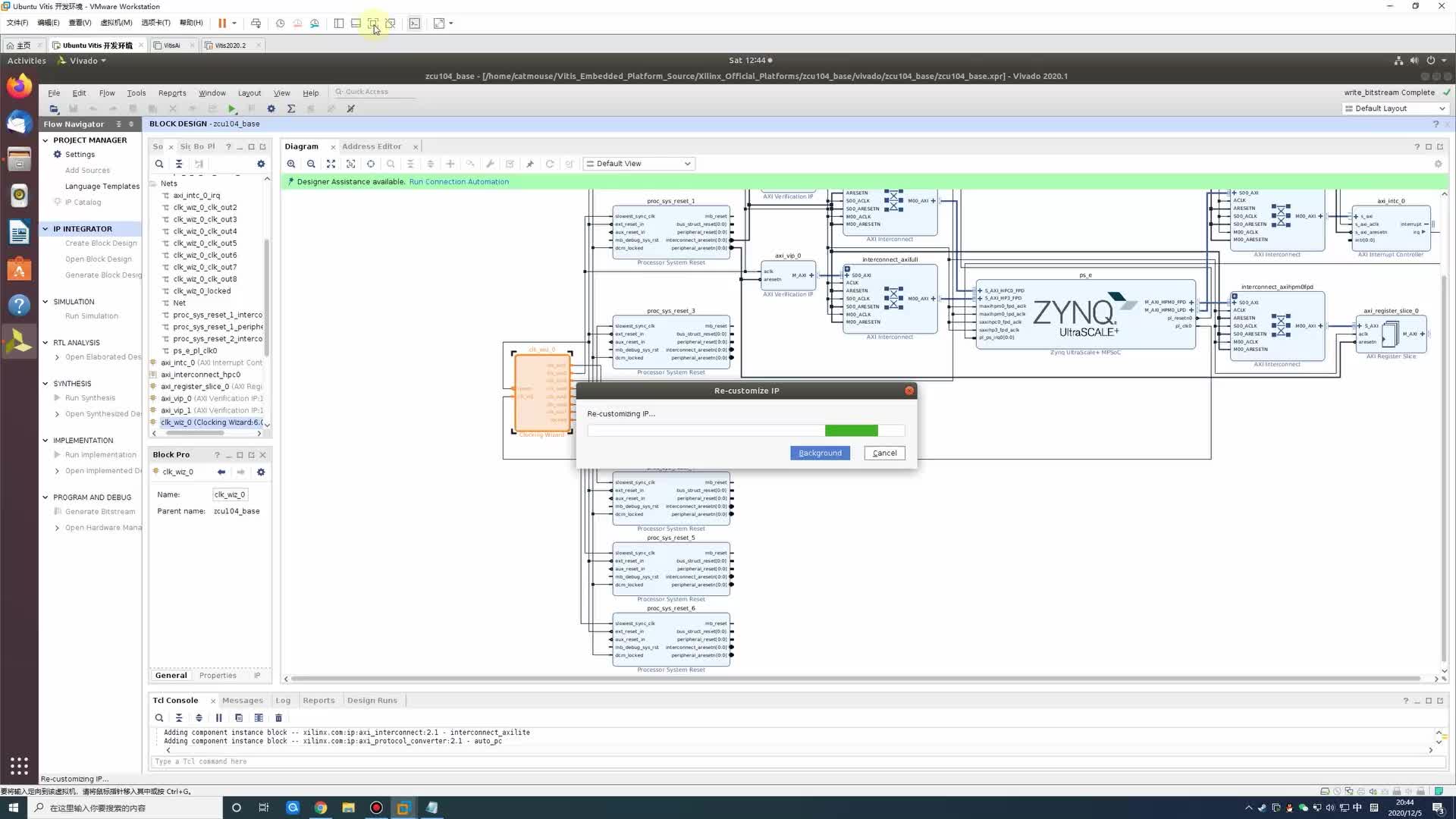

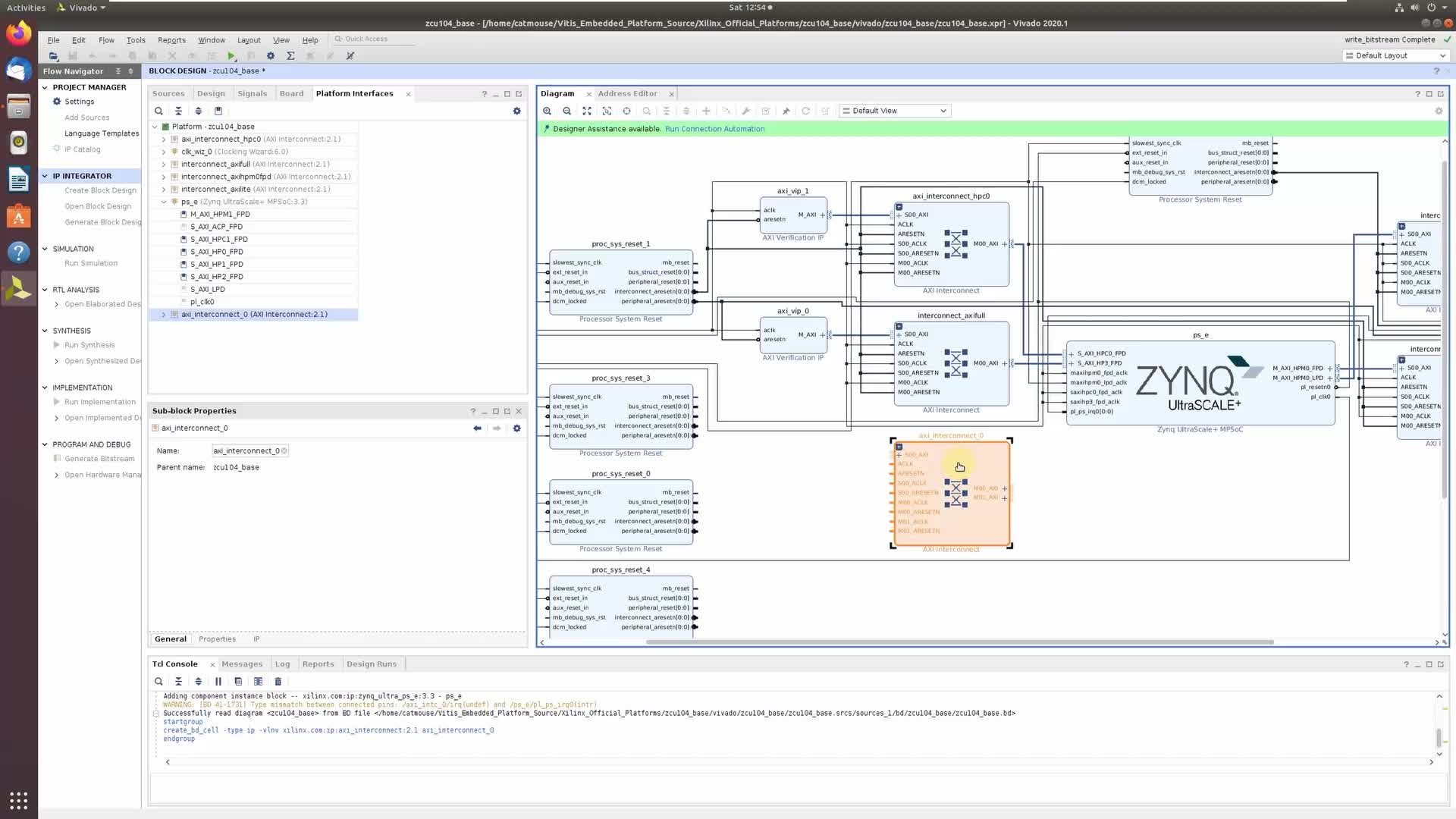

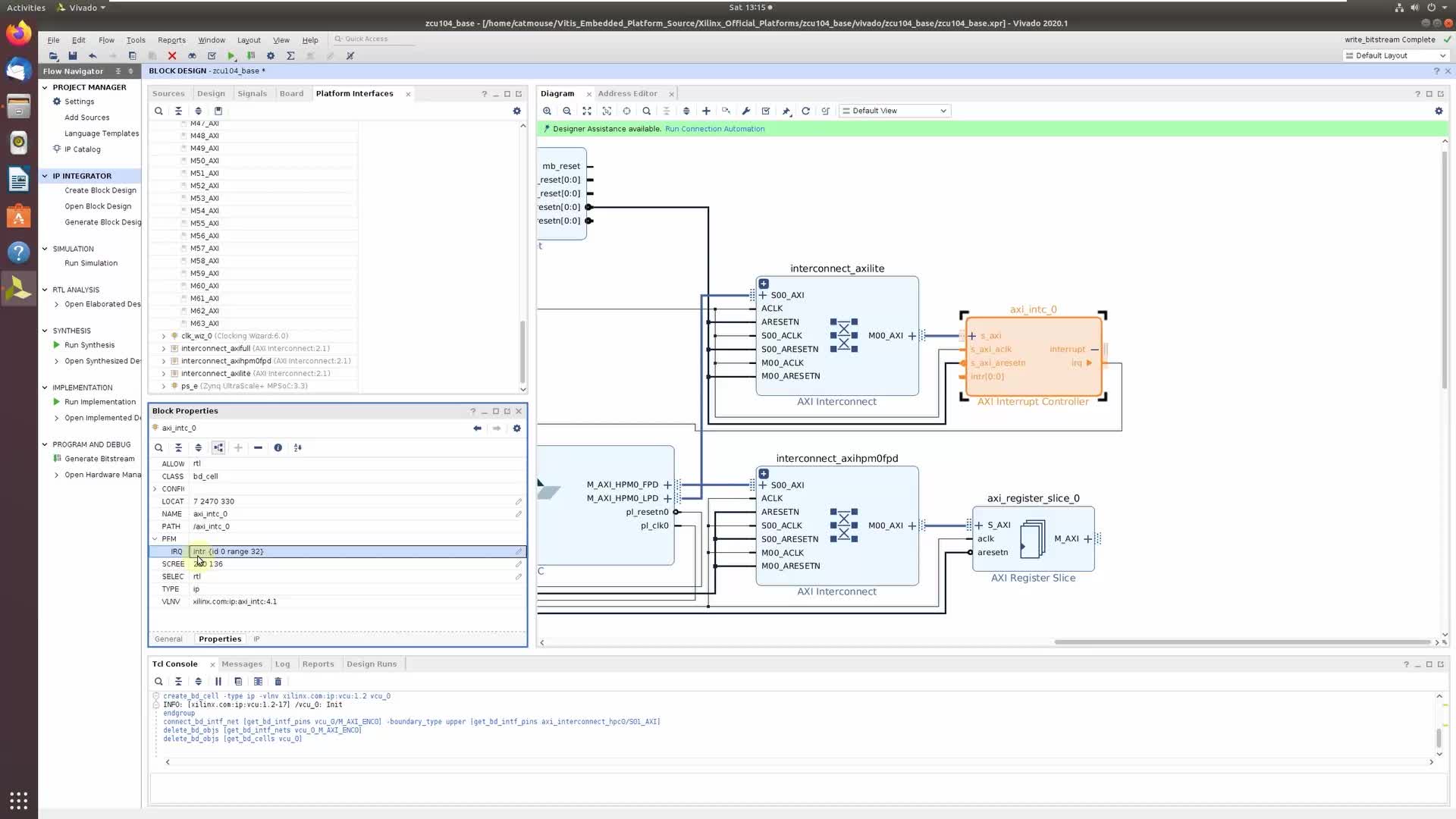

6406 装加速平台 ;第 4 部分: 在 Vitis 中测试定制加速平台 )。 在本文中,我们将讲解如何在 Vivado Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台。 您既可以采用已确认的成熟设计作为平台,这样只需稍作增强便可灵活运用于加速软件功能,或者也可以采用仅含加速所

2020-09-26 11:29:43 3451

3451

1). Windows 10 2). Vitis 2019.2 3). MicroZed 3. Vivado工程导出XSA文件 在 MicroZed 2019.1 BSP 下载MicroZed的Petalinux BSP。解压后,使用Vivado 2019

2020-11-04 12:03:25 5065

5065

从 2019.2 版开始,赛灵思 SDK 开发环境已统一整合到全功能一体化的 Vitis 统一软件平台 中。 马上开始将工程从赛灵思 SDK 移植到 Vitis 吧。 Vivado 工程升级 工程

2020-11-09 16:57:12 2279

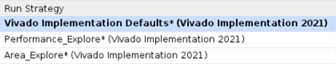

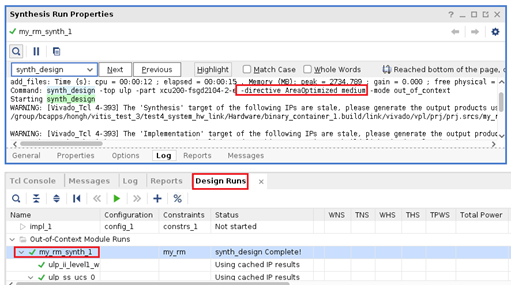

2279 在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分

2022-08-02 08:03:38 1016

1016

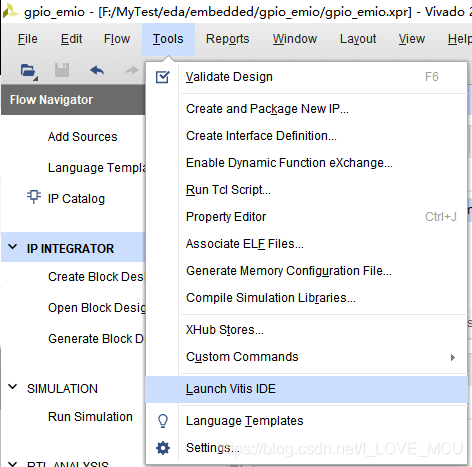

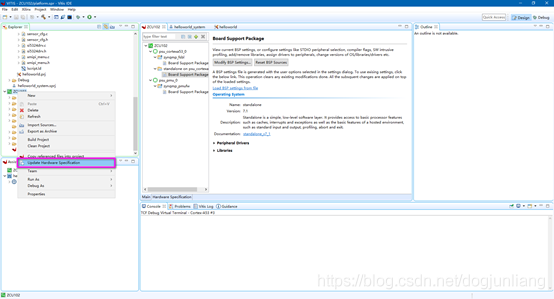

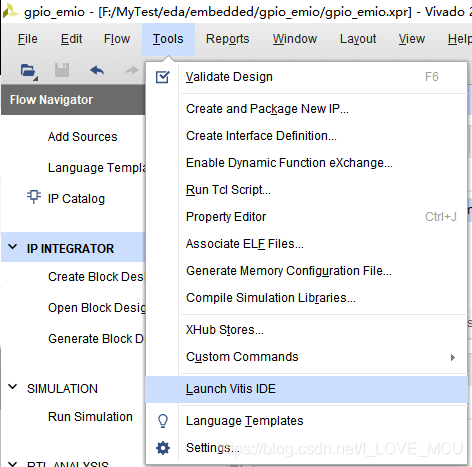

安装完成了,所以是灰色状态。创建platform工程vivado->tools->launch vitis ide选择工作路径先创建一个 platform project,填写工程名选择

2020-12-23 17:10:37

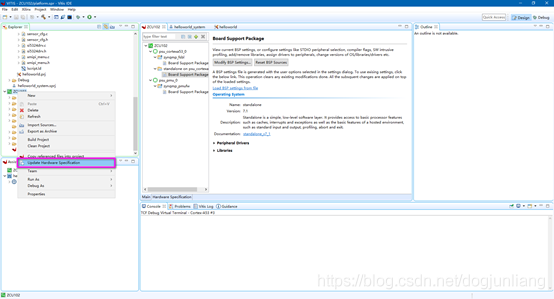

在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2021-02-04 07:09:50

在ISE中可以设置状态机安全模式 safe impementation模式,但是在Vivado中有没有类似的设置?我现在一段代码中可以跑到else,但是 偶尔会跑不到ifs_state_4这个状态机。。有大佬知道是为什么么?

2020-11-09 15:25:41

…。(不同Vivado版本可能Write Tcl菜单位置会有不同,但是都在File菜单中)弹出的WriteProject to Tcl文件夹,在Output File中设置当前工程路径,并输入.tcl为后缀

2020-08-17 08:41:25

源文件,之后Clean,再之后Build(Ctrl + B)。 注:中间会弹出来一个错误的提示,不用理会,等待工程编译完成,错误提示就不存在了。 更改目录后vitis工程需要重新加载平台 在建

2021-01-15 16:46:02

vitis和vivado有什么区别和联系呢

2023-10-16 07:55:35

电源线顶层过孔到底层,,,顶层的可以,,但到底层了就不可以了,,底层的哪里设置规则了吗???求解。。

2012-11-29 11:36:50

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

大家好,我在利用ni vision assistant生成的模板匹配界面时,想要将每一个匹配物体的位置信息导出到word或者Excel,但是他这个匹配个数不确定,怎么样把匹配到的所有物体信息导出呀?利用哪些编程?谢谢大家了

2024-03-11 20:22:18

STM32F103配置信息的怎样的?

2021-11-29 06:19:20

TESTSTAND自带的报表中有 UUT Result这一项(见下图),现在需要在自制的excel报表里用到 UUT Result,想知道它的底层参数是什么,怎么传递的

2015-11-08 20:06:20

【KV260视觉入门套件试用体验】+02.开发环境安装Vitis/Vivado(zmj)

本篇主要介绍在CentOS-7.9安装Vitis2022.2(包括Vivado2022.2)的安装。

注意

2023-08-27 21:22:34

FFT运算(Vivado)

四、硬件加速之—使用PL加速矩阵乘法运算(Vitis HLS)

五、Vitis AI 构建开发环境,并使用inspector检查模型

六、Vitis AI 进行模型校准和来

2023-10-14 15:34:26

本文将介绍如何使用Vitis-AI加速YOLOX模型实现视频中的目标检测,并对相关源码进行解读。由于演示的示例程序源码是Vitis-AI开源项目提供的,本文演示之前会介绍所需要的准备工作。演示之后

2023-10-06 23:32:47

都已编译到预构建的 Vitis AI 开发板镜像中。您可直接运行示例。如有新程序,请在主机侧对其进行编译并将可执行程序复制到目标。

1. 使用 scp 命令将

2023-09-26 16:22:43

sample_platedetect.jpg

“Plate Detection”(车牌检测)库使用 DenseBox 神经网络来检测车牌。输入是由 SSD 检测到的车辆图片,输出是包含车牌位置信息的结构

2023-09-26 16:28:10

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis

2022-09-09 16:45:27

。3.Vitsi 开始调试在 Vivado 2019.2 中启动 Vitis 的方式 与我现在用的 vivado 2017.4 有些不一样,当然这一点也不清楚是在 2019.2 版本中做的改变还是在2018版本

2020-03-06 22:59:12

在我们的设计中,Vivado实现结果因运行而异。我们想要从“最佳”实现中锁定两个模块的放置信息。然后将其保存以备将来运行。我们知道这可能与pblock和分层设计有关。但是,分层设计文档并不十分

2018-10-18 14:36:14

我要设计一个四层的PCB板子,底层用于焊接面(全部做成BGA焊盘),也就是底层用作元件的BGA焊盘,焊盘上不想有孔。我暂时考虑用盲孔,然后用铜填孔$ L& P0 k. m" T8 SI4 m" q, b' @9 E请教大家有什么更好的办法把顶层或内层走线引到底层,谢谢。

2014-10-28 16:27:36

请问在vivado中修改了DTCM的大小后,如何在nuclei studio 中对应地修改内存的大小?

2023-08-16 06:54:10

在PCB中怎样快捷地将器件从顶层移到底层,我想移很多元件,目前只会右键点元件,然后在选择bottomlayer,这种方法只适合单个元件,我想移很多元件,有没有更好的方法?

2014-11-19 10:31:02

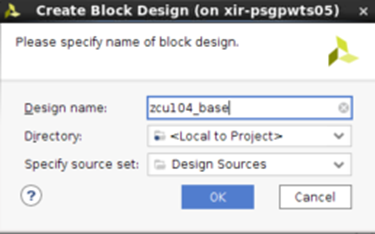

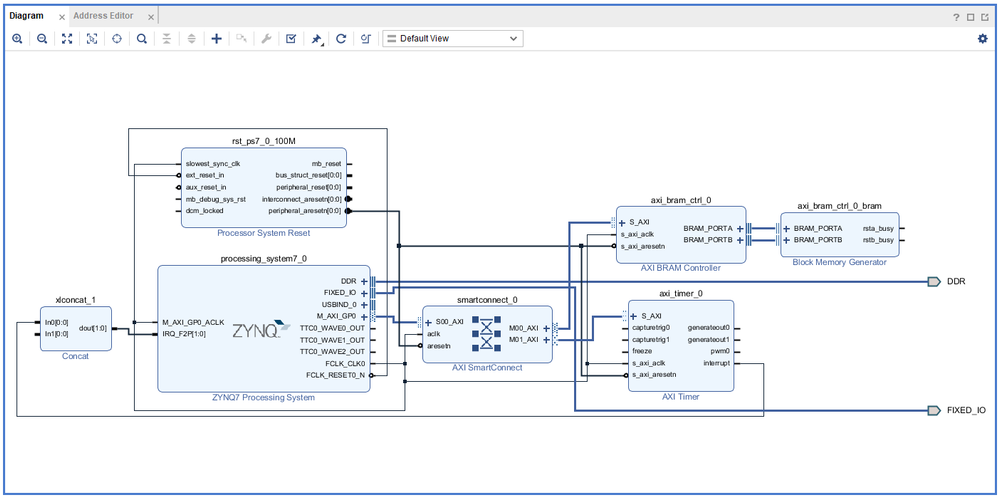

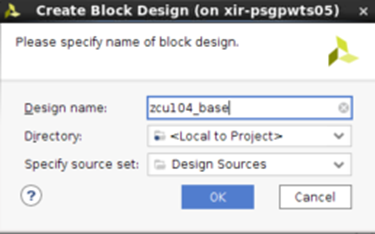

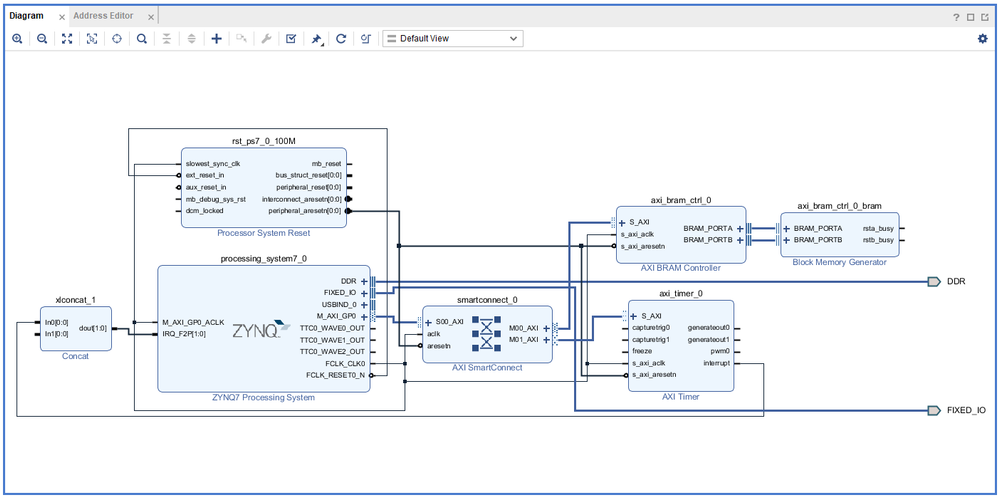

本文介绍如何在 vivado 开发教程,创建新工程 的基础上, 使用IP集成器, 创建块设计。

2021-02-23 07:02:27

如何在AudioService中把音量设置到最小呢?

2022-03-03 06:25:28

当我试图在Ubuntu的Synplify中调用xilinx for P& R时,它说XILINX变量尚未设置。我把它分配到vivado中的bin文件夹,但似乎是错误的。看起来Synplify

2018-12-19 11:04:40

如何在VMware中安装ubuntu 16.04如何安装Vitis AI几个常见的docker指令

2021-02-24 06:24:00

)IOStandard类型 - I / O端口clk是单端但具有LVDS的IOS标准,只能支持差分信息:[Vivado 12-3199] DRC完成了1个错误谁能让我了解如何在Virtex 7板上正确设置用户时钟

2020-03-30 09:51:26

如何在多个页面之间传递数组收录日期 : 2000-08-21 可以把数组转化成字符串,作为一个参数来传递: - file1.php <

2009-01-11 09:25:19

大家好,我试图在verilog文件中将命令传递给系统。 (在最初的开始循环中)我尝试使用$ system命令行。它现在处于verilog标准,但它似乎不适用于vivado。谁知道怎么做?这是我想要

2020-05-22 15:23:42

你好,我正在使用vivado 2013.3我试图在zedboard上进行VITA传递,但是当我生成一个比特流时,我已经在这条消息的末尾列出了问题(我有一个视频评估许可证)和图像处理)错误信息:信息

2020-05-20 12:50:42

,和/libcpu/arm/zynqmp-r5,/src源码,/include头文件,以及/components中的必要组件。我正确的设置了各头文件的工程路径,但在Vitis2019.2工程中Build时报错大量错误,大多都是头文件找不到,变量重复定义等。

2022-09-15 14:11:28

在cadence17.2中,如何将顶层丝印放置到底层丝印中,器件已经放置到底层,但是丝印还是在顶层。

2020-09-28 11:51:57

在布局PCB的时候 底层需要放置元件 怎样才能把元件放置到底层

2019-09-29 10:05:21

我想读取鼠标位置信息,求大神赐教

2016-06-28 23:30:47

本帖最后由 lsergao 于 2013-3-29 07:53 编辑

我把一个贴片元件双击选择放到底层,怎么打印底层没有焊盘啊,请高手指点,我是一个新手

2013-03-28 16:39:24

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

传递方式 它的信息传送方式:用户手机安装APP后,扫描共享单车二维码识别后,蓝牙芯片通过共享手机的GPS定位,获得共享单车的位置信息,并把信息传输给云端平台。后台管理系统向用户手机中安装的app发送

2020-08-14 08:00:35

/xlnx/board/crawl_message?board.id=OTHER&message.id=9394)。我想要做的是在Vivado GUI中更改默认位置和文

2020-05-12 09:23:20

PROTEL顶层到底层镜像

图文解析

2010-09-12 16:34:37 0

0 本期视频主要介绍了隔离的意义、绝缘的等级及介质、以及如何在两个隔离系统间传递信息等信息,并总结了Maxim在数字隔离方面的技术。

2018-10-08 03:27:00 4018

4018 了解如何在Vivado中执行工程变更单(ECO)。

本视频将向您介绍ECO的常见用例,我们推荐的完成ECO的流程,优势和局限性,并将演示功能设计的ECO。

2018-11-21 06:40:00 4645

4645

此视频概述了Vivado Design Suite中的IP加密。

它涵盖了IP加密工具流程,如何准备加密IP以及如何在Vivado中运行加密工具。

2018-11-20 06:34:00 5948

5948 了解Vivado 2015.1中引入的新仪表板改进,如何在Vivado Logic Analyzer中使用它们以及使用它们的好处。

2018-11-26 07:07:00 2777

2777 物理优化是Vivado实现流程中更快时序收敛的重要组成部分。

了解如何在Vivado中应用此功能以交换运行时以获得更好的设计性能。

2018-11-23 06:06:00 3726

3726 了解如何使用2014.1中引入的新激活许可为Vivado工具生成许可证。

另外,了解Vivado 2014.1中的许可更改如何影响您,以及如何在激活客户端中使用新的Vivado License Manager

2018-11-22 07:10:00 2614

2614 Vitis 2019.2 使用 gcc 编译 C 语言源代码,使用 Vivado HLS 编译与 SDAccel 流匹配的加速内核。此外,Vitis 也使用与 SDAccel 相同的目标平台

2020-06-28 10:05:51 2011

2011

在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。

2020-09-13 10:04:19 5961

5961

在Vitis HLS下,一个Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下图所示。前者最终导出来

2020-11-05 17:43:16 37060

37060 Linux嵌入式设计中最基本的任务之一是创建用户应用程序。 在本篇博文中,我们将探讨如何在 Vitis 中使用 UIO 驱动框架创建简单的 Linux 用户应用。 1 硬件设计 本次

2020-11-20 14:05:34 3840

3840 这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis 中将所有这些工程封装在一起。 在 Vitis 中加速软件

2020-12-26 10:20:54 2465

2465

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-01-22 05:51:23 1065

1065

本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

2022-02-08 10:47:39 2089

2089

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3057

3057

在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2022-07-25 18:03:30 3090

3090

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-01-28 09:28:18 12

12 本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2021-01-31 08:12:02 8

8 在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2021-02-21 06:48:51 17

17 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。 本篇博文将分为 3 个部分: 1. 从 Vitis HLS 导出 IP。 2.

2021-04-26 17:32:26 3506

3506

Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-90度。 设置输出时钟

2021-06-09 17:28:01 3888

3888

首先我们看一下如何在Vivado下设置BITSTREAM配置信息。这可以在综合之后进行。借助如下操作: 打开综合后的设计 依次点击Tools-》 Edit Device Properties 会弹

2021-06-15 14:26:18 5395

5395

首先我们看一下如何在Vivado下设置BITSTREAM配置信息。这可以在综合之后进行。借助如下操作: 打开综合后的设计 依次点击Tools-》 Edit Device Properties 在这

2021-06-18 10:24:51 1738

1738

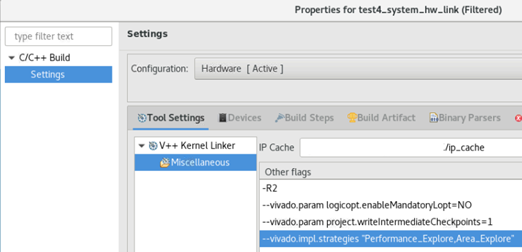

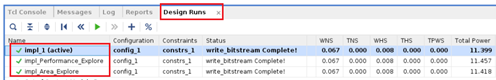

XCLBIN 在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要

2021-07-28 10:12:47 1758

1758

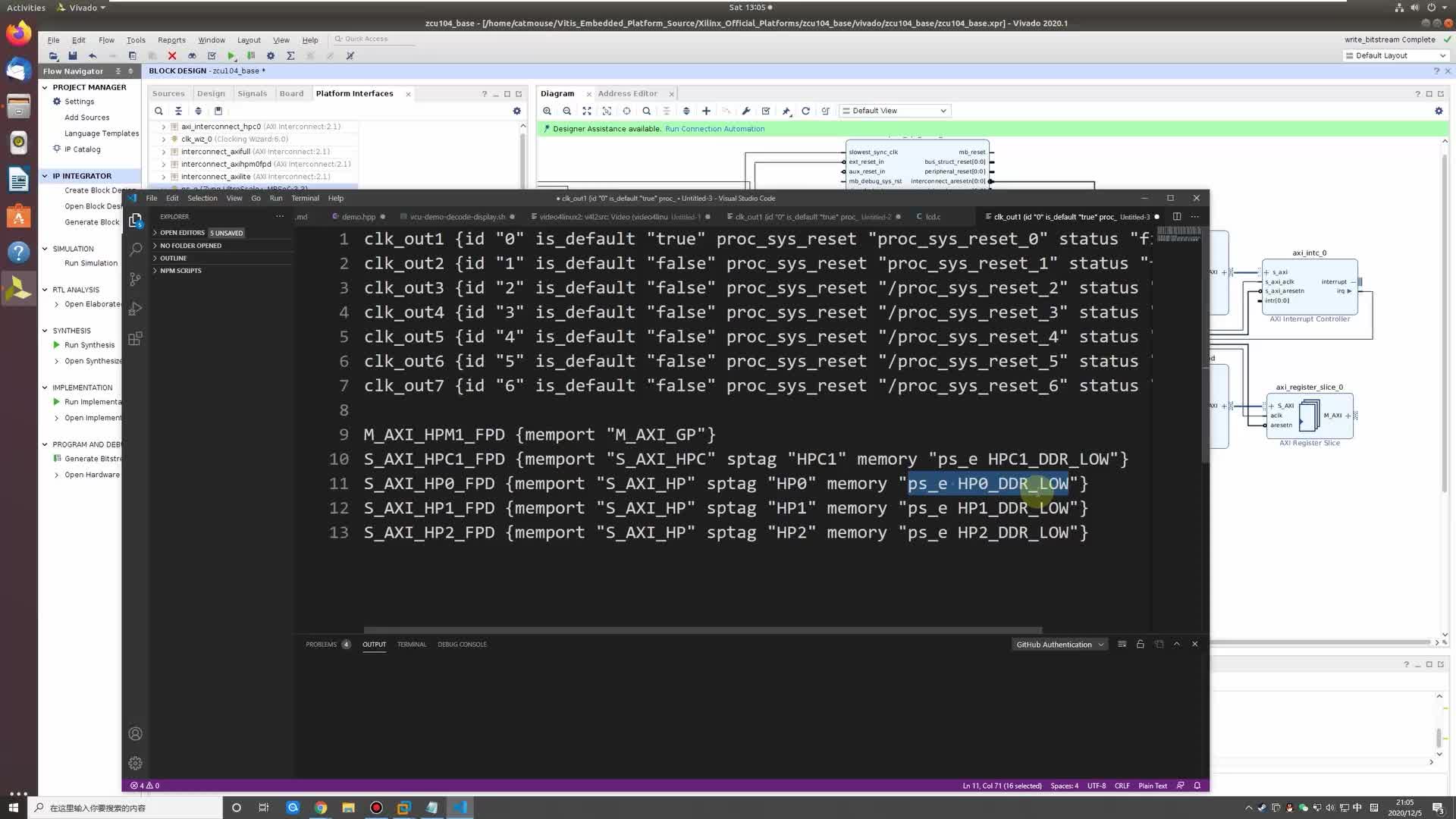

本篇文章来自赛灵思高级工具产品应用工程师 Hong Han. 本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado. 对于Vivado实现阶段策略的指定

2021-08-13 14:35:56 3900

3900 使用Vivado / Vitis工具提供预安装的OpenCV版本。尽管Vitis_hls编译Vision库不需要OpenCV,但是用户测试验证使用时OpenCV。

2022-02-16 16:21:38 2015

2015

Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 在Kernel Estimate报告中,可以看到,Target Clock已经按要求设置成200Mhz. 说明 Vitis_HLS是按照200Mhz的要求来综合Kernel的代码的.

2022-07-01 09:52:53 36129

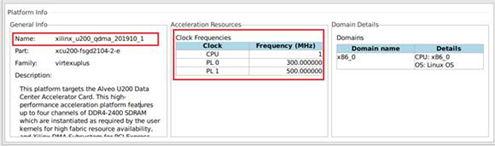

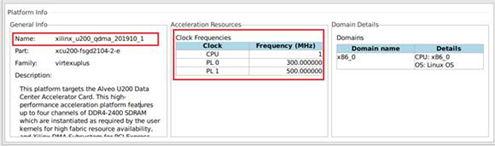

36129 在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率。以 xilinx_u200_qdma_201910_1 平台为例,在Vitis中选择平台时可以看到默认的时钟频率是300Mhz和500Mhz。

2022-08-02 10:30:45 514

514

以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

2022-08-02 09:43:05 579

579

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2856

2856 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 652

652

在本快速入门演示中,将探讨如何在 Vitis 中使用 Git 集成以及如何使用团队操作来共享 Vitis 工程。

2023-05-12 15:01:00 566

566

本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2956

2956

如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado的综合参数设置。

2023-05-16 16:45:50 1856

1856

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

2023-08-16 10:26:16 546

546

AMD Vitis 软件平台是一款开发环境,主要用于开发包括 FPGA 架构、Arm 处理器子系统和 AI 引擎在内的设计。Vitis 工具与 AMD Vivado ML 设计套件相结合,可为

2023-12-20 10:00:02 154

154

Vitis2023.2之前就安装过了,vivado 2023.2相比于2023.1区别不明显,但嵌入式平台vitis2023.2的变化很大,有种vscode的既视感,更符合软件开发人员的习惯。

2024-01-05 09:42:45 379

379

电子发烧友App

电子发烧友App

评论