本文来自 XILINX BY BenM. Fell

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量。

时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分析。应首先从系统角度来分析设计,以判定是否有任何因素会对设计中较大区域产生影响,而不只是判定有哪些因素会影响存在最严重违例的个别路径。

如需获取有关此过程的实用指南,请参阅《UltraFast 设计方法时序收敛快捷参考指南》(UG1292)。

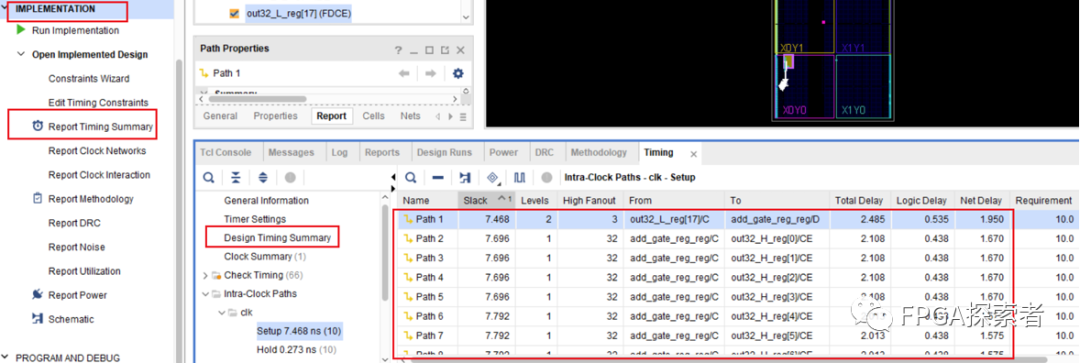

本篇博文旨在描述此文档中所述的时序基线检查流程,尤其是当 WNS

为了解决这些时序收敛失败问题,用户可以采用时序路径分析方法来对布局步骤、phys_opt 步骤和布线实现步骤之后发生的时序收敛失败问题进行优先级排序。

第一步是使用下列命令生成一组报告。

在 Vivado 非工程模式下,可将这些命令添加到用于运行此流程的 Tcl 脚本中。在 Vivado 工程模式下,则可将这些命令添加到 Tcl 挂钩脚本中(请参阅 (UG894) 的 “定义 Tcl 挂钩脚本” 部分)。

report_design_analysis -timing -routes -logic_level_distribution -of_timing_paths [get_timing_paths -routable_nets -max_paths 10000 -slack_lesser_than 0] -file timing_vios.rpt report_timing -of [get_timing_paths -routable_nets -max_paths 1000 -slack_lesser_than 0] -file timing_paths.rpt -rpx timing_paths.rpx

这些命令会生成文本报告 timing_vios.rpt 和 timing_paths.rpt,这些报告可通过任意文本编辑器来查看。这些命令还可生成交互报告 timing_paths.rpx,此报告可用于在 Vivado GUI 中进行交叉探测。这些报告可显示有关设计中时序收敛失败的主要路径的信息。通过将这些报告结合在一起,即可快速达成时序收敛。

timing_vios.rpt

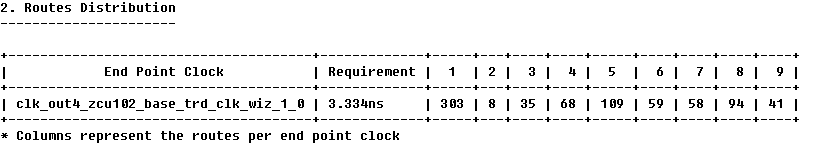

此报告可显示时序收敛失败的主要路径的属性(根据 Tcl 参数设置,最多可报告 10,000 条路径)。报告底部显示的直方图可显示每个端点时钟对应的时序失败的路径数量,按逻辑级别分组。此直方图作为非常实用的高级视图,可帮助缩小造成最严重的时序收敛失败的时钟域的范围。

用户应首先从造成最严重违例的时钟域开始分析这些失败问题。在多 SLR 器件中,许多违例所含的逻辑级数为 0,这表示导致时序违例的根本原因可能是没有足够的流水打拍,或者 SLR 分区效果不良。

这些都只是时序失败的线索,而并非真正原因。重要的是首先缩小问题最严重的区域的范围,然后再寻找解决方案。了解最差负时序裕量时序违例的本质有助于用户确定应执行的补救步骤的优先顺序。以下显示了一个简单的直方图示例(仅有 1 个时钟存在时序收敛失败路径)。

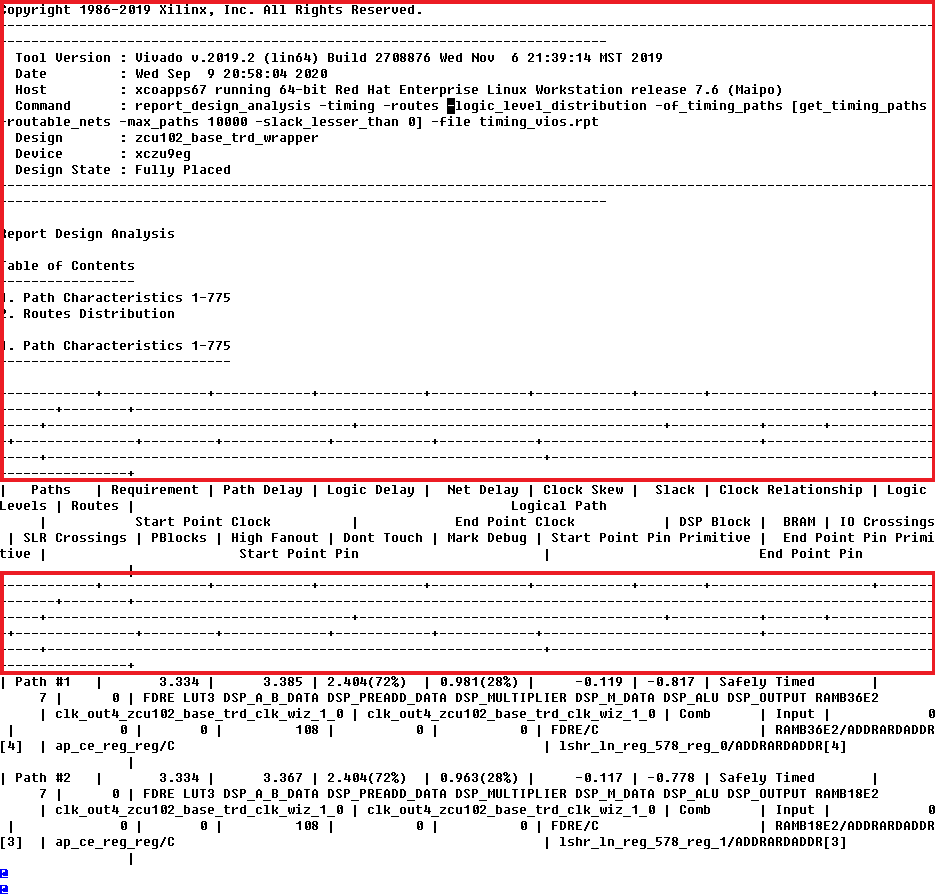

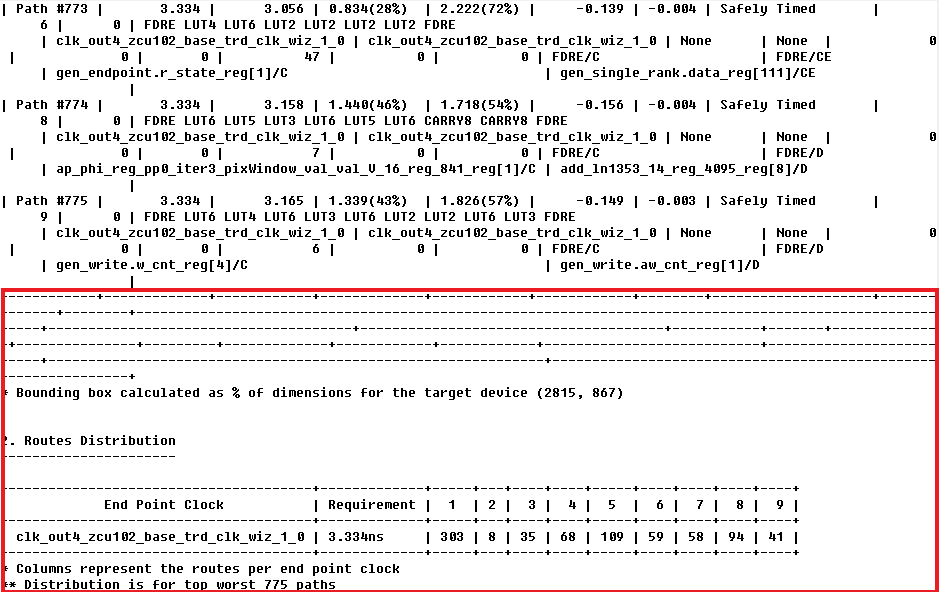

报告其余部分可通过文本编辑器来读取,但由于换行,可能导致难以阅读。更简单的数据分析方法是将其导入 Microsoft Excel。 以下过程用于将文本编辑器报告转换为逗号分隔式报告。

1. 创建 timing_vios.rpt 的副本,并将其重命名为 timing_vios.csv。

2. 使用文本编辑器,移除报告中的页眉、页眉分隔符行和页脚(如下红框所示):

3. 如果已将 -show_all 选项与 report_design_analysis Tcl 命令配合使用,请将文件中的逗号 (,) 替换为冒号 (:)。

4. 将所有管道字符 (|) 都替换为逗号 (,),然后保存此文件。

5. 关闭文件。

timing_vios.rpt 顶部

timing_vios.rpt 底部

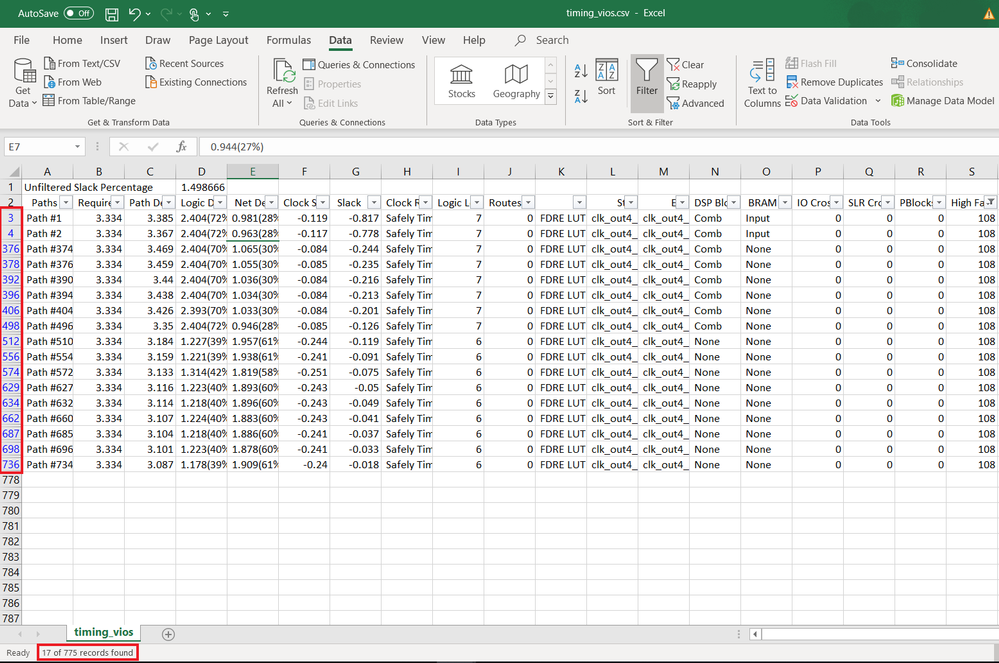

6. 在 Microsoft Excel 中打开此 csv 文件。

7. 移除 A 列,因为此列为空。

8. 在顶部插入空白行。

9. 添加以下等式,以在报告中生成未经筛选的裕量百分比。此百分比将有助于指导完成分析操作。此百分比值越大,则失败特征对时序的影响越大。

=SUBTOTAL(109,G:G)/SUM(G:G)*100

10. 高亮 excel 文档的第 2 行,该行应为各列的标题行,然后选择“数据 (Data) -> 筛选 (Filter)”。

对此报告使用筛选,以查找对设计影响最大的失败类型。

此报告通常本身无法提供时序失败的准确原因,但可帮助指导用户发现需进一步调查的路径,并使用交互时序报告(timing_paths.rpx;稍后将提供此报告的实用技巧)进行调查。

通过筛选,用户即可看到具有相似属性(逻辑级数、起点管脚等)的相似失败路径(例如,同一条总线的路径)。用户可以使用未筛选的裕量百分比来指导他们。并且,用户还可通过筛选来使用发现的记录行(如下所示),并留意筛选后显示的行号(电子表格中行号越小,表示显示的时序收敛失败的路径越差)。

以下是一些有关筛选的实用技巧。

“文本筛选器 (Text Filters) -> 包含 (Contains)”对于筛选“起点管脚 (Start Point Pin)”、“终点管脚 (End Point Pin)”和“逻辑路径 (Logical Path)”很有用。在 timing_vios.csv 中包含以下列(定义源自 (UG835) v2020.1 第 1324-1325 页)。

首次生成电子表格时,可根据以下入门指南来尝试执行下列检查。这些检查主要聚焦于讲解设计后的时序收敛失败原因和修复方法。设计师还可以选择更改硬件描述语言 (HDL) 以缩短路径长度或者降低时钟速率,以及运用下文未列出的其它修复方法:

1. 在时钟关系 (CLOCK RELATIONSHIP) 列中,是否所有时序收敛失败的路径都已安全完成时序约束?如果没有,那么时序约束对于其它路径是否合适?

2. 是否有任何时序收敛失败的路径的时钟偏差 > .5ns?如果存在此类路径,请参阅 (UG1292) v2020.1 第 8 页,以获取相关偏差建议。

3. 对于 SSI 器件,跨 SLR 的路径的未筛选的裕量百分比为多少?如果此比值过高,请参阅(UG1292) v2020.1 第 7 页。

4. 有多少时序收敛失败的路径具有与之关联 Pblock?如果此比值较高,请参阅 (UG1292) v2020.1 第 7 页。

5. 是否有大量时序收敛失败的路径的扇出都偏高 (>=512)?在 (UG1292) v2020.1 第 6 页中,如果工具存在较大的信号线延迟,则建议对具有 512 个端点的高扇出信号线进行最优化。

6. 是否有任何时序收敛失败的路径具有 DONT_TOUCH 或 MARK_DEBUG?包含这些时序路径的逻辑是否属于非第三方逻辑或非赛灵思 IP?

这些属性会阻碍工具执行有助于改善时序的最优化操作。

7. 有多少比例的路径所含的起点管脚原语或端点管脚原语不属于寄存器类型(非 FDPE、FDCE、FDRE 或 FDSE)?是否存在类似的失败特征?

8. 对于布线后操作,包含非零保持时间绕行 (HOLD FIX DETOUR) 的时序路径所占比例为多少?

timing_paths.rpt

这是基于文本的时序分析报告,包含对应设计中的主要时序收敛失败路径(根据 Tcl 命令参数,最多可包含 1000 条路径)的时序分析。它可通过使用简单的 Linux grep 来帮助生成前 1000 条路径的失败源和目标列表。 例如,用户可以按如下方式来识别排名前 100 的时序起点和端点。

grep -m 10 "Source:" place_paths.rpt > top_100_startpoints.rpt grep -m 10 “Destination:” place_paths.rpt > top_100_endpoints.rpt

timing_paths.rpx

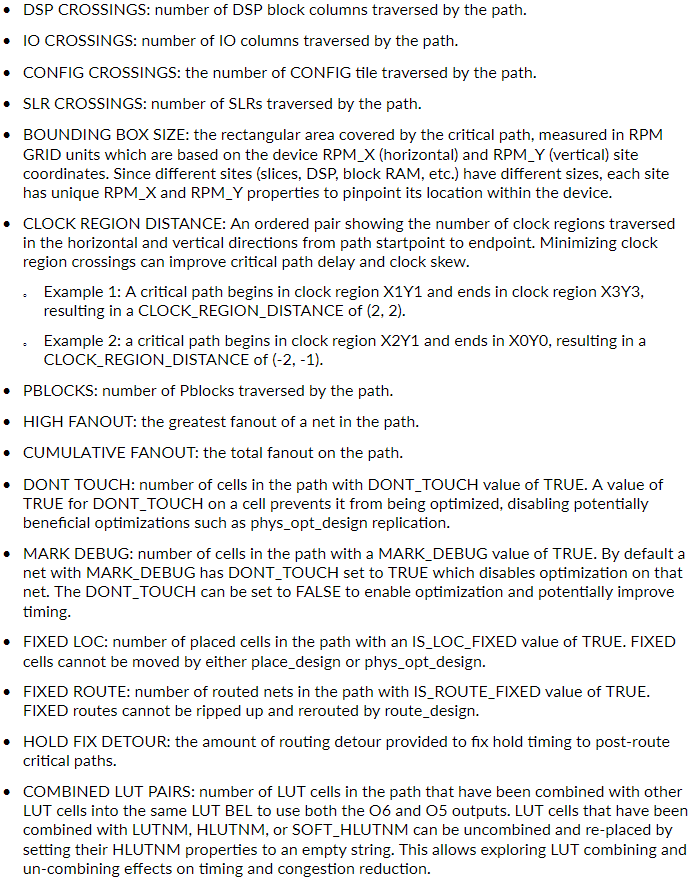

这是 timing_paths.rpt 的交互式报告版本。最实用的 3 个窗口分别是“器件 (Device)”窗口、“层级 (Hierarchy)”窗口和“原理图 (schematic)”窗口。

一旦确定某个失败特征对于设计的时序影响较大,即可使用 timing_paths.rpx 报告来对其进行深入挖掘。用户通过在 Vivado 中使用 timing_paths.rpx 报告即可借助具有失败特征的主要失败路径来判定出现时序收敛失败特征的原因。

要查看 timing_path.rpt 中包含的每条路径的信息,请在 Vivado 交互式报告中双击相应的时序路径。这样即可显示路径报告汇总信息窗口,其中包含时钟和数据路径等路径信息。查看原理图中的路径是很有用的。通过使用原理图,即可查看有哪些时钟被用作为数据路径中的时序元件的时钟源。在原理图中还能同时展开此时序收敛失败路径的前后级路径,这些信息有助于更准确了解数据路径。

此外,还可查看原理图中的单元属性、信号线属性和管脚属性,因为原理图可显示时序收敛失败的路径附近的固定布局单元(例如,收发器)或受限布局单元(例如,块存储器)。

用户还可高亮时序报告中的路径,这样即可在“Hierarchy”窗口中高亮相应的模块。如果用户选择前 10、100 或 1000 条路径,则可查看收敛失败的时序路径是否集中于层级内某一部分。已知路径在层级中所在位置有助于将时序收敛工作重心集中于明确设计的某一区域内包含较多违例的原因。

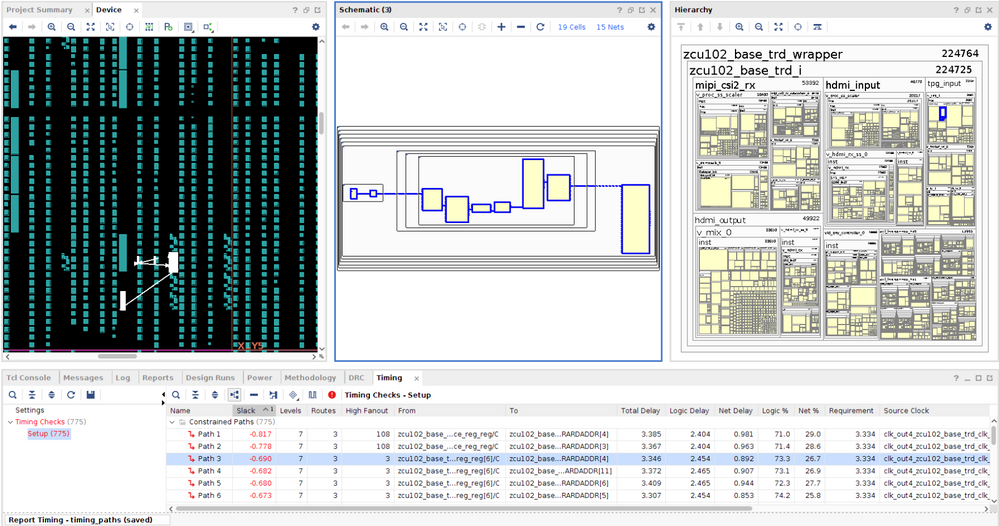

最后,用户可以在时序报告中将路径高亮,这些路径也会显示在“Device”窗口中,以显示物理器件中逻辑的布局位置(如下所示)。

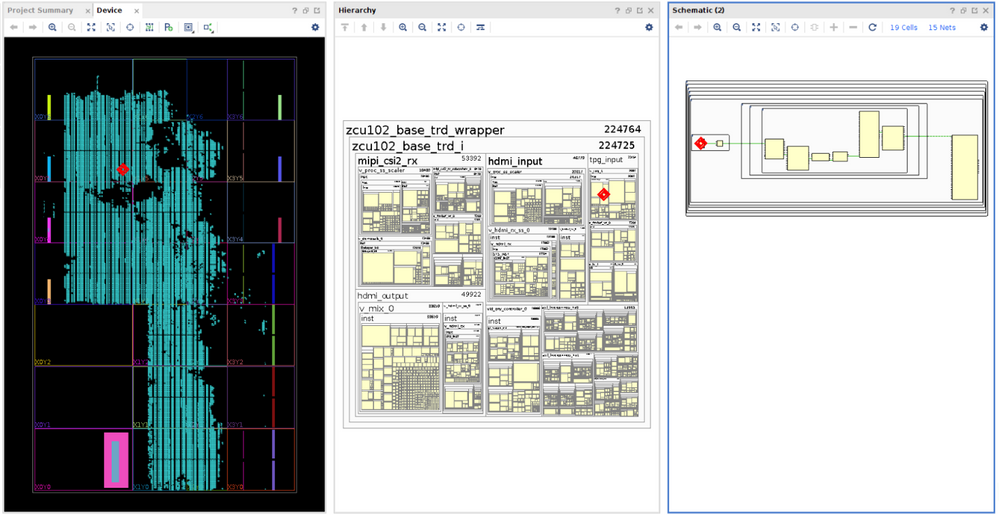

通过使用“Schematic”窗口,即可在时序路径内标记单元以帮助用户在“Schematic”窗口、“Hierarchy” 窗口和 “Device”窗口之间进行浏览(如下所示)。

将构建模块放置在一起

本篇博文提供了一种时序路径分析优先排序方法,此方法可在 (UG1292) 的时序基线检查流程中使用。

本篇博文中涵盖了下列话题:

1. 如何为此时序分析生成重要报告(timing_vios.rpt 和 timing_paths.rpx)。

2. timing_vios.rpt 的分析过程包括将其转换为便于分析的 Excel 格式 (timing_vios.csv)。

3. 使用timing_paths.rpx 来帮助确定时序收敛失败的原因。

在发生时序收敛失败的大型设计中,用户将在 2 份报告之间进行迭代(timing_vios.csv 和 timing_paths.rpx)。timing_vios.csv 报告提供了失败的高级别视图(例如,森林级视图)。timing_paths.rpx 报告包含 “Schematic” 窗口、“Device” 窗口和路径报告,可提供各条路径的具体信息(例如,单独的树视图)。

您可反复切换回 timing_vios.csv 以查看共有的失败特征。即使大侦探面对千头万绪也可能一筹莫展,负裕量最高的路径也可能无法轻易解释其时序收敛失败原因。如果发生这种情况,那么应分析负裕量仅次于它的另一组时序路径,查看其失败原因。

这样做的目的是通过明确最常见的时序收敛失败的原因来尽可能快速使工作取得进展。希望能够藉此加快达成时序收敛,少受殚精竭虑之苦。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论