当然,(近乎)完美的电气开关已经存在很长时间了,但我们在这里不是在谈论机械。现代电源转换依赖于理想情况下没有电阻的半导体开关,当打开时没有电阻,关闭时具有无限电阻和耐压,并且能够通过简单的驱动在两种状态之间切换,任意快速,并且没有瞬时功耗。

在我们注重能源和成本的世界中,这些功能有助于在电源、逆变器、电池充电器、电机驱动器等领域实现高功率转换效率。随之而来的好处是减少了设备尺寸、重量和故障率,同时降低了采购成本和生命周期成本。有时,会超出一个简单的效率阈值,从而打开整个应用领域。例如,如果电机驱动器损耗过大并因此又大又重,则电动汽车几乎不可行,而这又需要更多的电池功率,同时又会导致重量和续航里程的进一步损失。从近 75 年前的 Shockley、Bardeen 和 Brattain 时代开始,工程师们因此一直致力于改进半导体开关,以更接近理想状态。

迈向理想开关

机械开关确实用于第一个电源转换应用——机械“振动器”最初是用于隔离 DC/DC 转换或 DC 电压升压的电动发电机组的唯一替代品。然而,在晶体管发明大约 10 年后,出现了第一个开关模式电源 (SMPS) 设计,从那时起,设计人员不得不使用可用的半导体技术。尽管场效应晶体管 (FET) 的原理已于 1930 年由 Julius Edgar Lilienfeld 提出并获得专利1,但它们实际上无法制造,而且最初使用锗的双极晶体管主导了早期的 SMPS 电路。

双极晶体管起初具有有限的额定电压、高关断状态泄漏以及缓慢且有损的开关,并且它们需要复杂的基极驱动。时至今日,双极晶体管的增益很低,可能需要数安培的基极电流。基极中存储的电荷是一个大问题,限制了关断时间和效率,因此使用技术来精确定制基极驱动并使用 Baker 钳位等技术来限制电荷,该技术以一些传导损耗换取较低的动态损耗。

硅金属氧化物栅极 FET (MOSFET) 在 70 年代和 80 年代具有垂直传导路径和平面栅极结构,随后在 90 年代采用“沟槽”布置,因此在高功率方面变得可行。然而,在更高功率下的使用受到电压额定值和可实现的导通电阻的限制。一个主要的发展是 70 年代后期的绝缘栅双极晶体管 (IGBT),它结合了类似 MOSFET 的栅极驱动和类似双极的传导路径,具有易于驱动和固定饱和电压的优点,因此功耗名义上与电流成正比,而不是与 MOSFET 中的电流平方成正比。然而,IGBT 并非没有自己的问题,有闭锁的趋势,会带来灾难性的后果。关断时的“尾电流”也使动态损耗相对较高,从而限制了工作频率。现代 IGBT 中的闩锁问题现已解决,尾电流最小化,而电流和电压额定值已显着增加,这使得这些部件在非常高的功率转换中很常见。但是,由于动态损耗,开关频率仍被限制在最大几十千赫兹。

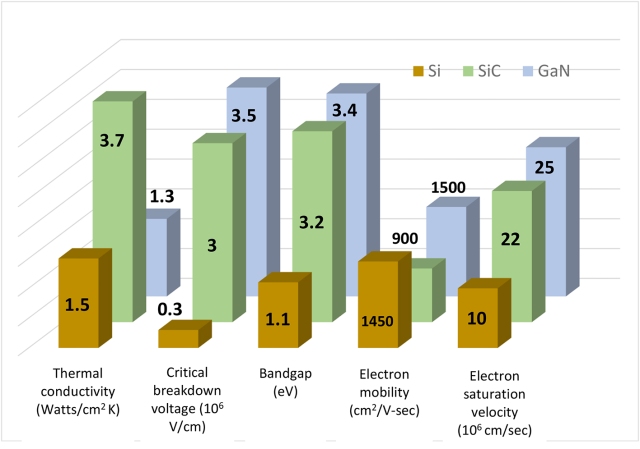

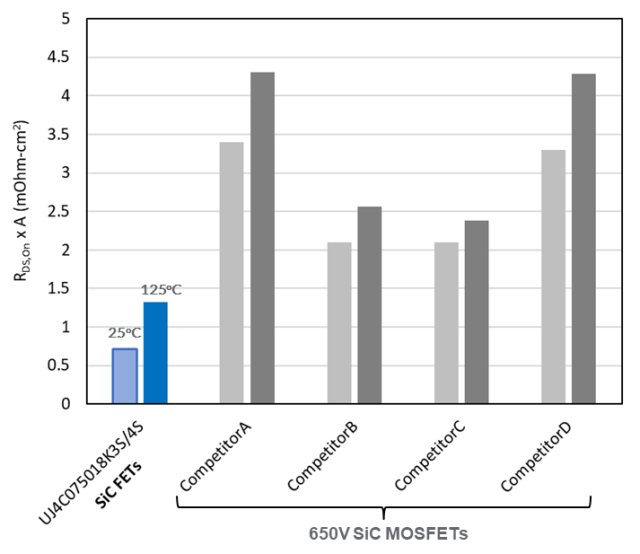

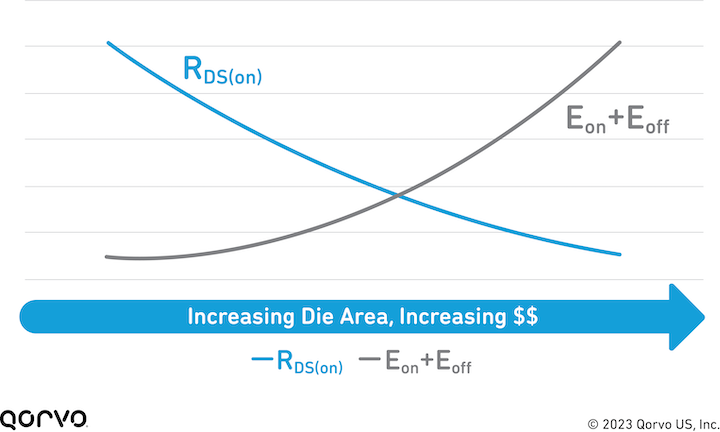

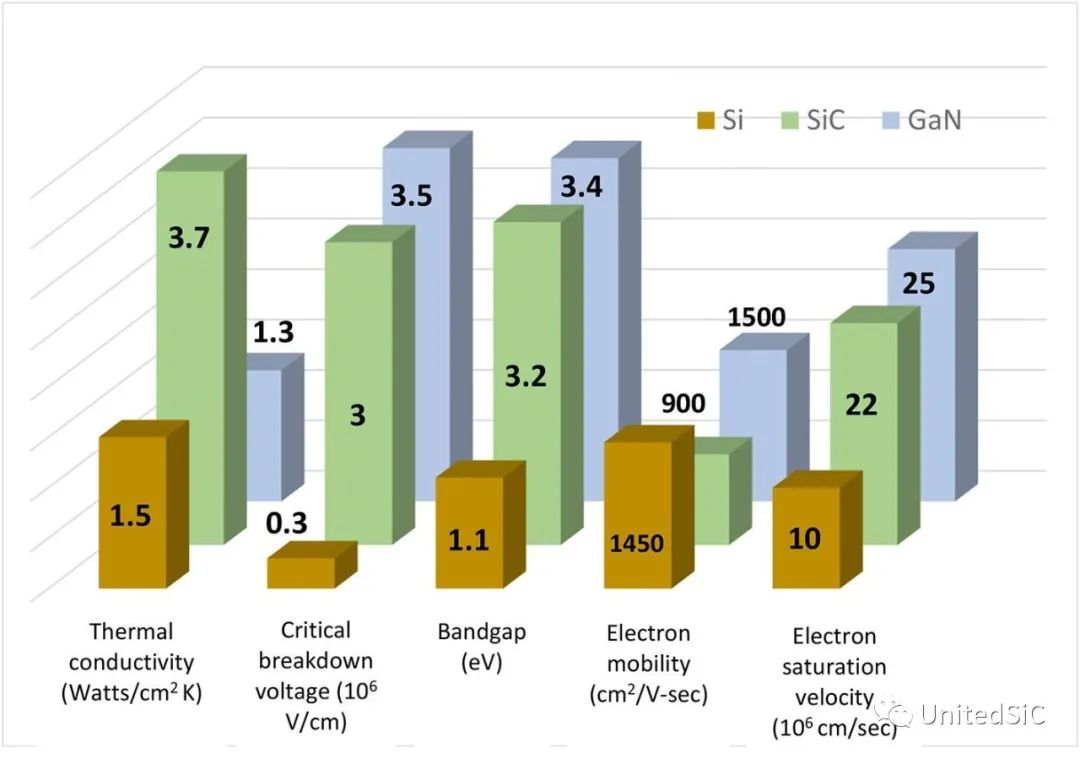

高开关频率是更小的磁性元件和具有更高性能控制回路的整体更小、更轻的功率转换产品的关键,因此随着 MOSFET 导通电阻和额定电压的提高,它们被越来越多地使用,频率被推高到数百千赫兹,“超级结”类型是最先进的。然而,一个限制因素是硅的击穿电压,对于给定的工作电压和因此高的导通电阻 (R DS )值迫使体材料的最小厚度。许多单元可以并联以减少这种情况,但总芯片面积 (A) 会增加。该效应通过每单位面积的导通电阻 (R DSA) 品质因数,并促使人们对碳化硅和氮化镓等宽带隙材料的兴趣激增。与硅相比,WBG 材料具有更高的本征击穿电压和其他有利特性,例如更高的电子迁移率和饱和速度、耐高温能力以及对于 SiC 而言更好的导热性。图 1显示了硅、SiC 和 GaN 材料主要特性的比较。

图 1:Si、SiC 和 GaN 材料特性

图 1:Si、SiC 和 GaN 材料特性早期 SiC 器件开发

SiC器件的开发比GaN 早 10 年,预期最初更广泛地适用于更高的电压和额定功率。SiC 开关的一个自然起点是考虑开发增强型、常关型 MOSFET,以便与现有的 Si MOSFET 设计和制造技术兼容。与任何新技术一样,也存在初期问题——有些是可以预测的,有些则不是,这导致了零件商业化的延迟。

与硅相比,碳化硅的一个固有特性过去是,现在仍然是,晶格缺陷的数量更多。这些缺陷导致栅极氧化层与 SiC 沟道的界面处电子迁移率低,导致导通电阻相对较高。为了成本效益,碳化硅晶圆尺寸必须最大化,并且很难在 6 英寸行业标准下保持低缺陷率和晶圆平整度。SiC MOSFET 还表现出具有显着滞后的栅极阈值不稳定性,使得栅极驱动难以设计以实现最佳效率和可靠性。尽管最新的 SiC MOSFET 更好,理论上可以使用单极 0 至 15V 驱动,但实际上,–5V 的负栅极电压通常用于可靠运行。此外,15 V 不会提供最低的导通电阻,

2010 年左右,碳化硅 MOSFET 遇到了一个无法预料的困难,即“基面位错”——晶格中的体缺陷——实际上在工作应力期间生长和迁移。随着体二极管从源极到漏极的导电,产生电子空穴载流子,当它们复合时,有足够的能量移动并扩大缺陷。这是 SiC 更高带隙能量值的结果,其结果可能是性能下降——更高的漏电流和导通电阻——进而导致更高的损耗和故障。随着制造方法的进步和缺陷筛选,如今的 SiC MOSFET 有了很大的改进,但仍在努力提高芯片的产量和成本效益以及封装的性能,以实现低电感和热阻。

SiC FET:另一种方法

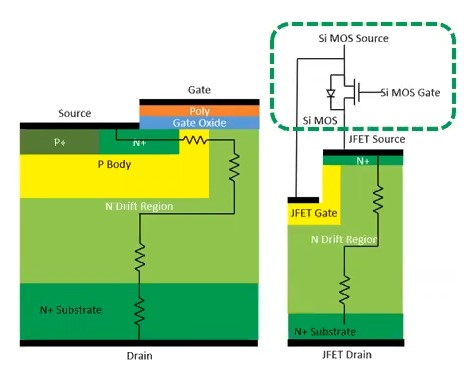

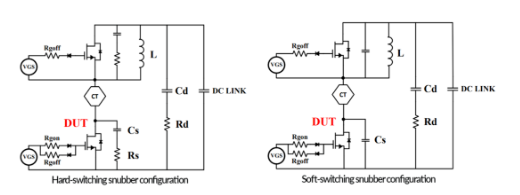

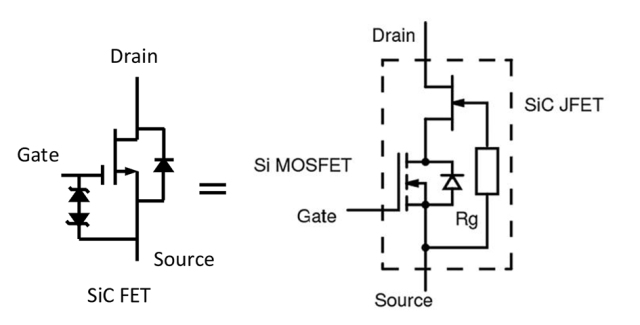

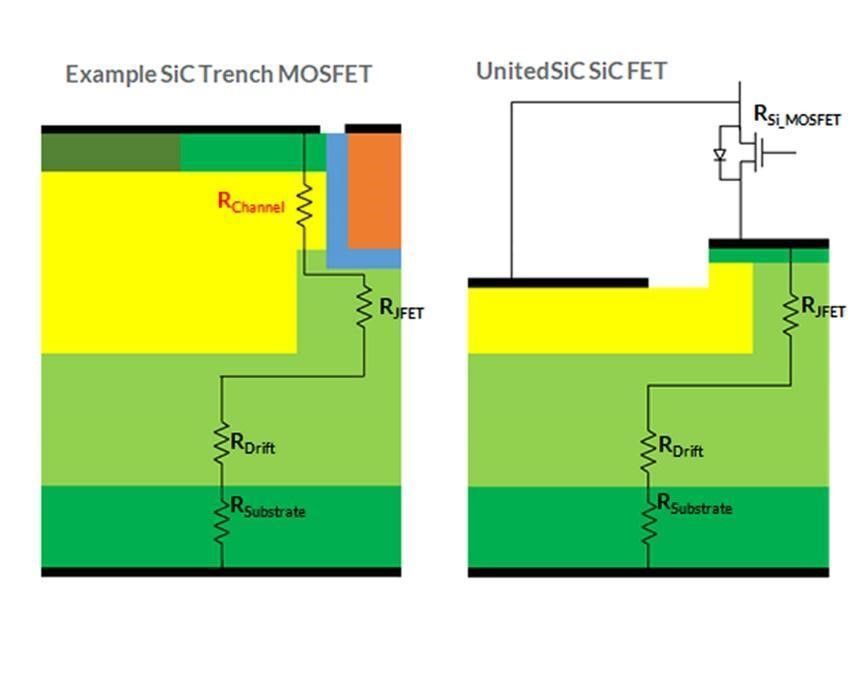

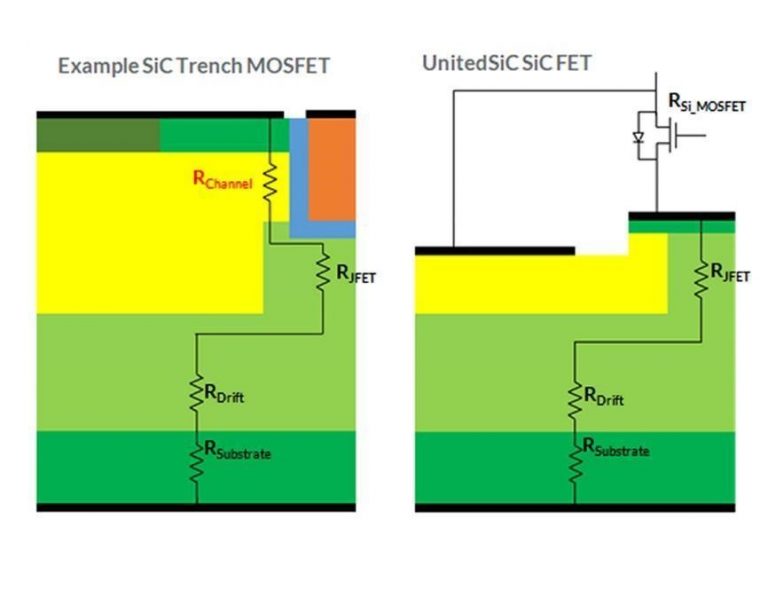

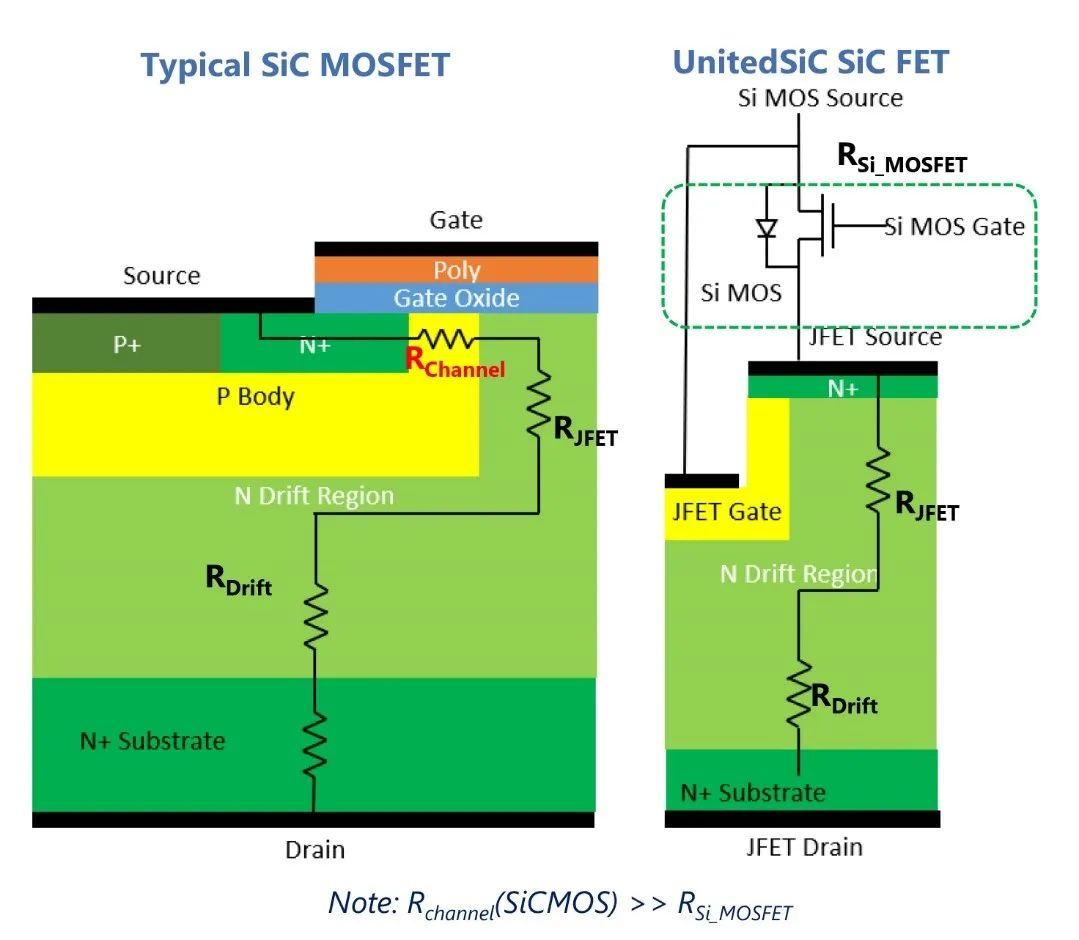

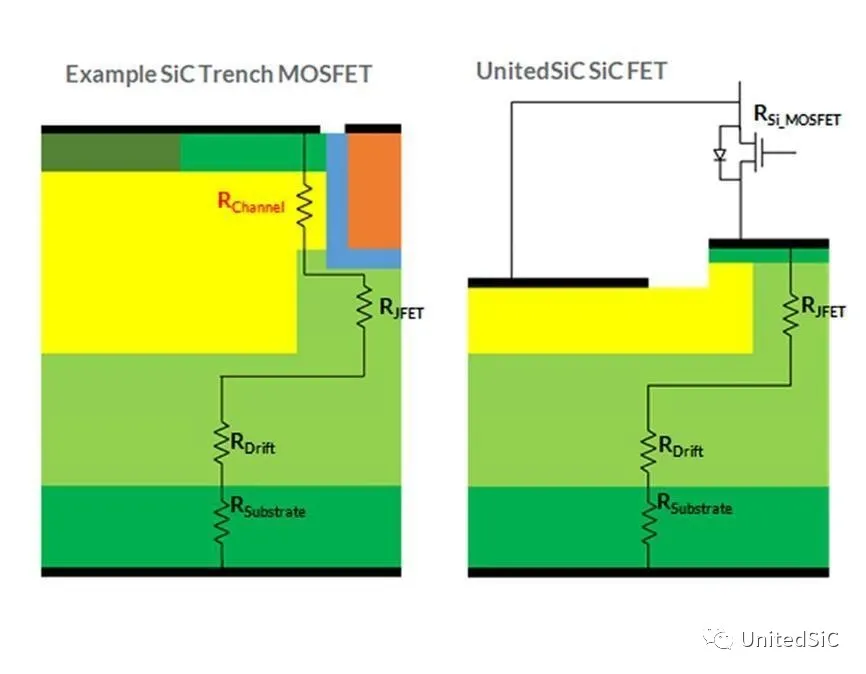

With the arrival of wide-bandgap technology, while many semiconductor manufacturers took the route of development of SiC MOSFETs using existing fabrication lines, others started with a blank sheet and considered other options. The simplest switch implemented with SiC is the JFET structure, which has no gate oxide and is a unipolar conduction device, so it does not show some of the limitations of MOSFETs. The device has a major drawback, though: It is normally on with gate drive at 0 V and requires a negative drive to turn off. At best, this is inconvenient; at worst, it risks application failure, especially under transient conditions such as system turn-on/turn-off. A device was proposed in the ’90s and developed around 2010 that solved the problem: the SiC FET, a combination of a SiC JFET and a silicon MOSFET that is normally off but maintains the advantages of a JFET over a MOSFET. 图 2显示了 SiC FET 布置(右)与通用 SiC MOSFET 原理图(左)的比较。

图 2:SiC MOSFET(左)和 SiC FET 结构(右)

图 2:SiC MOSFET(左)和 SiC FET 结构(右)SiC FET 的排列是共源共栅,可能对更成熟的工程师来说熟悉,他们甚至可能看到它以原始形式实现为真空管的组合,旨在降低音频放大器中的噪声。多年来,共源共栅或“发射极开关”以不同的形式出现,包括双极晶体管或 BJT 和 MOSFET 的组合;一般属性是低压开关控制高压开关,在高额定电压和易于驱动之间取得了很好的折衷。然而,由于需要大量的基极驱动电流和缓慢的开关速度,带有 BJT 的电路在高功率下并不流行。SiC 共源共栅或 SiC FET 解决了这些问题。

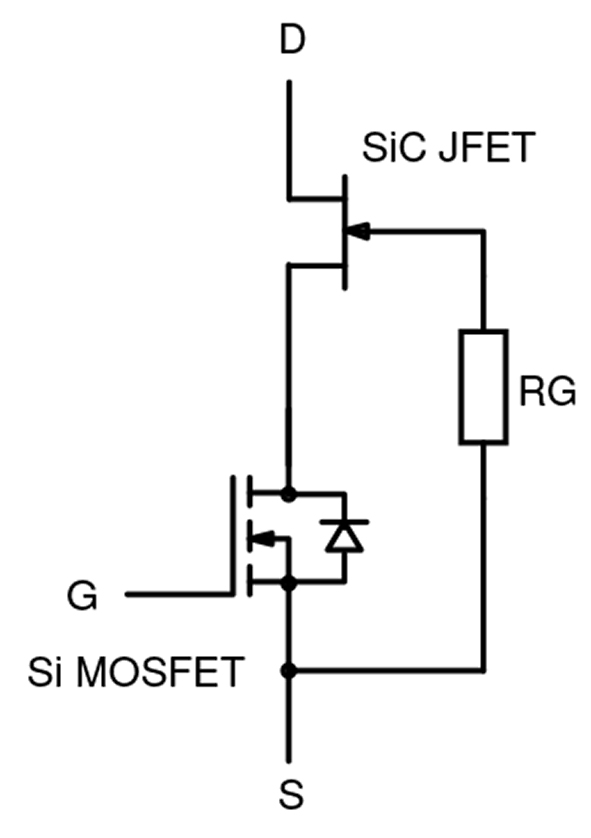

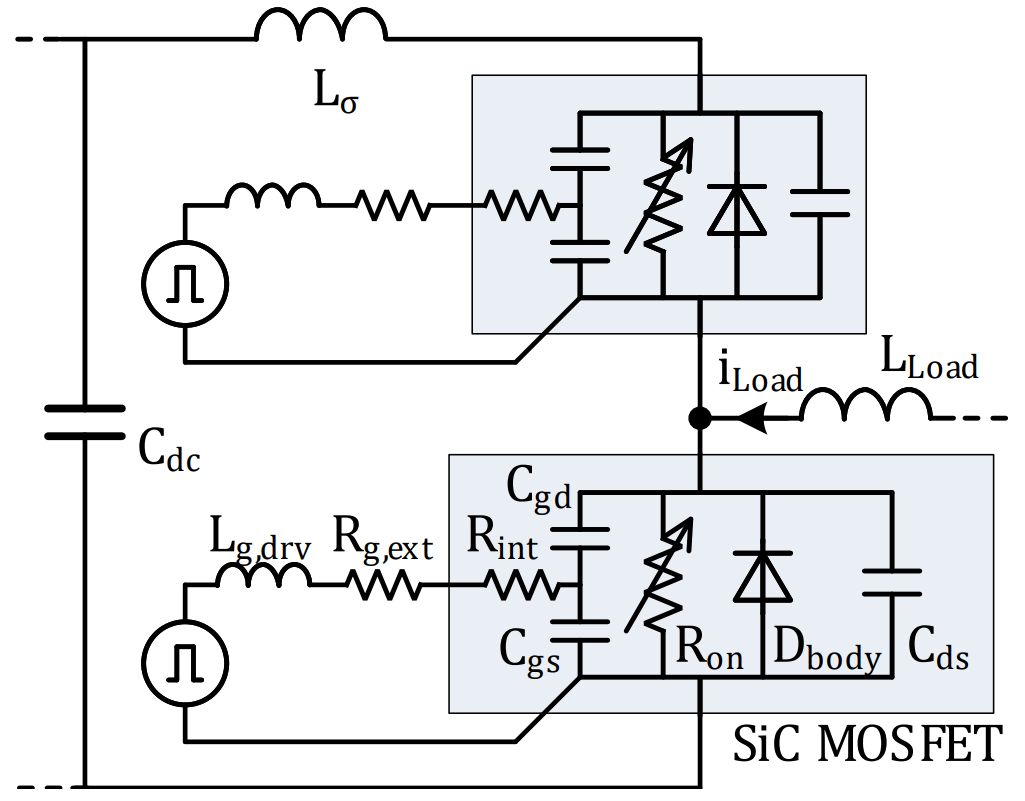

参考图 3所示的 SiC FET 原理图,当 Si MOSFET 通过其栅极导通时,JFET 源极和栅极有效短路且 JFET 导通。电流现在可以通过 JFET 和 MOSFET 漏源通道,传导损耗由 JFET 固定,因为与高压 SiC JFET 相比,低压 Si MOSFET 导通电阻可以非常低。当 Si MOSFET 关闭时,JFET 源极电压上升到超过其负几伏的栅源阈值并且 JFET 关闭的点。由于器件电容的比率,Si MOSFET 两端的电压动态保持较低。

图 3:SiC FET 原理图

图 3:SiC FET 原理图SiC FET 与 SiC MOSFET 相比,无论是在电气性能还是在实际使用中,都具有许多优势。作为开关,导通电阻是一个主要因素,与 SiC MOSFET 相比,SiC JFET 固有地在通道中具有更好的电子迁移率。通道密度也更高,这种组合意味着对于给定的裸片面积,SiC FET 导通电阻低 2 到 4 倍,或者相反,每个晶圆可以获得高达 4 倍的裸片数量。 SiC MOSFET 具有相同的导通电阻。与硅超级结 MOSFET 相比,增加的裸片数量可高达 13 倍。考虑到 SiC 作为一种材料可能总是比硅更昂贵,因此每片晶圆上总管芯的增加对于 SiC FET 技术的成功至关重要。如前所述,衡量芯片生存能力的指标是品质因数 R动态搜索广告。

另一个品质因数是R DS × E oss,即导通电阻和器件输出开关能量之间的权衡,源自输出电容。这是一种有用的措施,因为可以通过简单地在芯片中并联更多单元来减少导通电阻和传导损耗;但是,除了增加面积外,这还会直接增加电容,从而增加 E oss,从而导致与频率相关的开关损耗增加。因此,R DS × E oss 的低值是有利的。

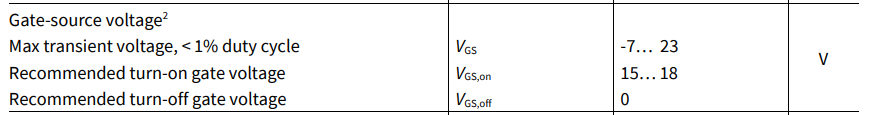

SiC FET 的栅极只是级联 Si MOSFET 的栅极。它具有大约 5 V 的稳定的、基本上无滞后的阈值,因此很容易用 12 V 或 15 V 驱动以实现完全增强和低 R DS(on),与典型的 25 V 的绝对最大值相比有很大的余量。简单的 SiC FET 栅极驱动在名义上与硅 MOSFET 甚至 IGBT 级兼容,为现有产品设计升级提供潜在的向后兼容性。SiC MOSFET 和 GaN HEMT 单元在实践中需要定制驱动装置,以实现最佳效率和足够的栅极过压保护。

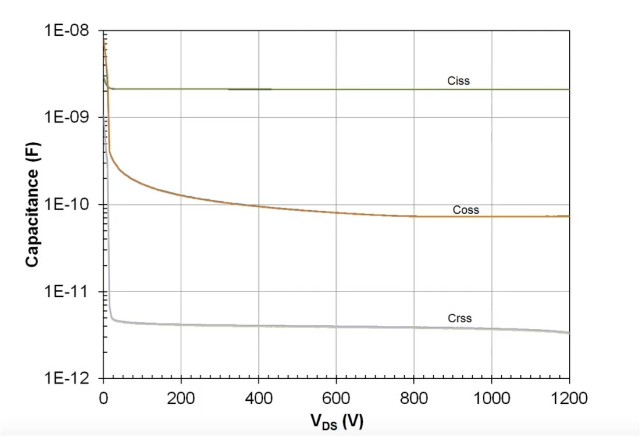

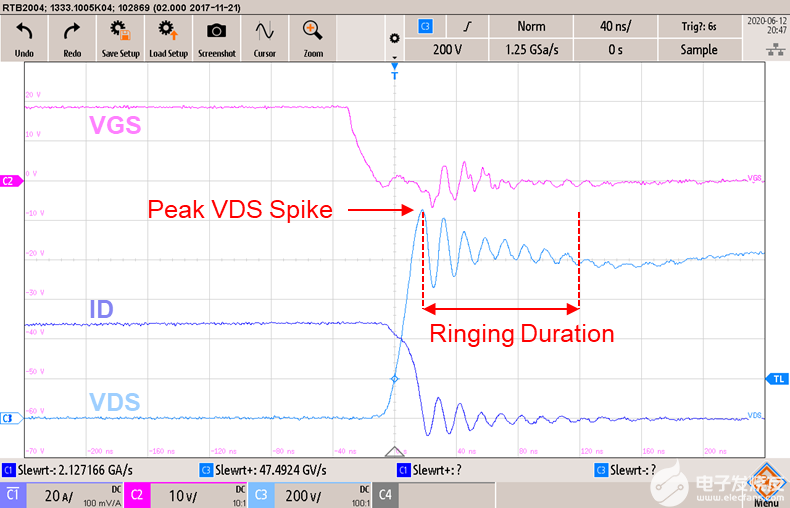

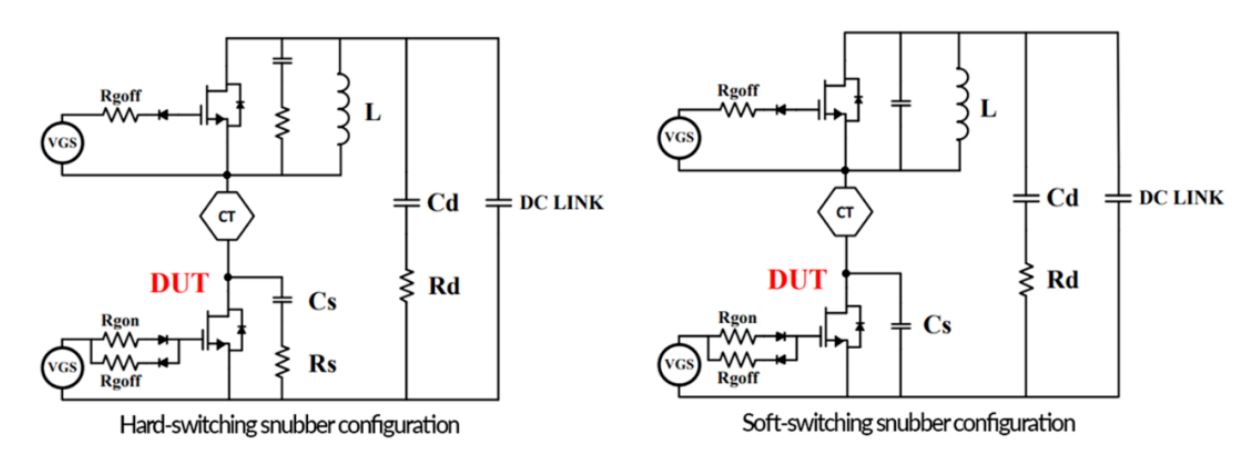

SiC FET 几乎没有栅漏电容或米勒电容 (C rss ),因为器件尺寸小,而且共源共栅排列中的 Si MOSFET 具有隔离效应,可实现超快速开关。输出电容 (C oss ) 以及相关的开关能量 (E oss ) 很低,这也导致以最小的损耗实现快速开关。边缘速率如此之快,以至于在实际电路中,必须减慢 SiC FET 以限制电压过冲和 EMI。这可以通过添加栅极电阻器来实现,但这种方法会导致高开关频率下无法接受的控制延迟,因此简单的 RC 缓冲器通常是更好的解决方案。电容器通常设置为大约 3 × C oss,串联电阻的耗散最小。图 4显示了典型的 SiC FET 器件电容及其在阻塞状态下随漏电压的变化。

C iss = C GS + C GD , (C DS短路), C rss = C GD , C oss = C DS + C GD

图 4:SiC FET 器件电容

图 4:SiC FET 器件电容SiC FET“体二极管”

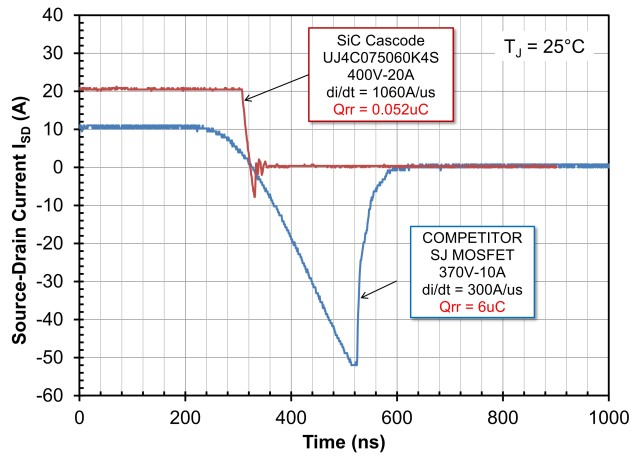

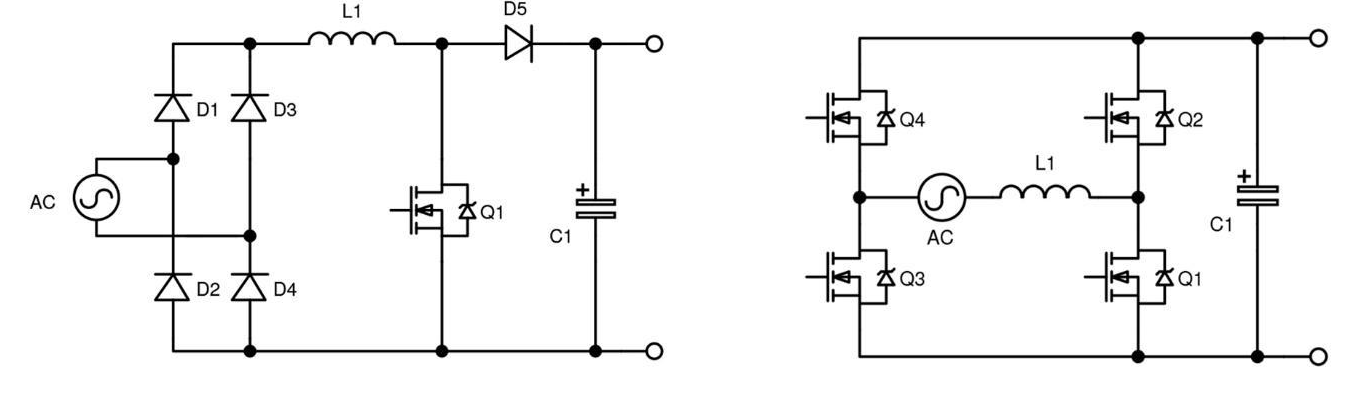

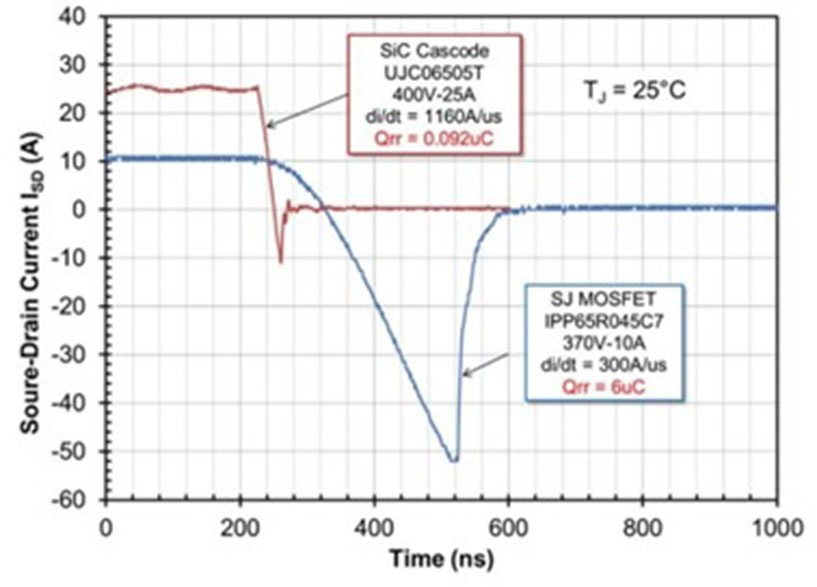

在电源转换器中,完美的开关应该以低损耗双向传导。这实际上在交流电机驱动器和带有感性负载的转换器等电路中是必需的——即所谓的三象限操作。IGBT 无法做到这一点,需要一个并联二极管,但硅和 SiC 中的 MOSFET 和 JFET 可以在栅极的控制下通过其沟道在任一方向导电。MOSFET 还具有 JFET 中不存在的固有体二极管,并且该体二极管通过在具有感性负载的硬开关转换器中在器件通道通过栅极导通之前的“死区时间”中通过“换向”自动导通,以允许反向电流。这种传导存储电荷 (Q rr),当体二极管随后反向偏置时恢复,此操作会耗散大量峰值功率,随着频率的增加,峰值功率平均会逐渐升高,从而降低效率。对于硅 MOSFET,其影响可能非常严重,以至于实际上它们不能用于某些电路,例如流行的图腾柱 PFC 级,在连续导通模式下工作。SiC MOSFET 的 Q rr值可能比硅好 10 倍,但 SiC FET 仍然更好,因为器件的输出电容较低,并且低压 MOSFET 中存储的电荷最少。比较确实取决于器件的电压等级,但图 5显示了 SiC FET 和其他类似硅超级结 MOSFET 的典型反向恢复图。

图 5:碳化硅 FET 共源共栅的反向恢复电荷比硅超级结 MOSFET 小 100 倍。

图 5:碳化硅 FET 共源共栅的反向恢复电荷比硅超级结 MOSFET 小 100 倍。虽然 SiC MOSFET 和 GaN 器件可能具有足够低的反向恢复损耗或没有反向恢复损耗,但反向传导时的压降却是另一回事。这会在电源转换器的死区时间内产生显着的损耗。Si 超结 MOSFET 的二极管压降通常约为 1 V,而 SiC MOSFET 的情况要差得多,其体二极管可以轻松压降 4 V。三象限操作中的 GaN HEMT 单元降低的电压 (V sd ) 是所述的总和我× [R通道的电压和栅阈值电压小于栅极-源极电压,或:

V sd = ( V th – V gs ) + ( I sd × R on )

GaN 的栅极阈值通常为 1.5 V,因此在高电流下,总压降可能很高。如果栅极被驱动为负以关闭(这很常见),则此电压 (V gs ) 会增加源极-漏极压降,导致 V sd为几伏,这可能比其他技术要差得多。SiC FET 导通源极至漏极时,与 GaN 器件类似,沟道电阻有I × R压降,但这仅因低压级联 Si MOSFET 的体二极管两端的电压而增加,相对而言低的。产生的正向压降通常约为 1.5 V,优于 SiC MOSFET 或 GaN 性能。

证明 SiC FET 的可靠性

宽带隙开关是稳健的,尤其是因为它们固有的高温和高击穿电压能力,而且 SiC FET 的一个特殊优势是没有 SiC 栅极氧化物,如 SiC MOSFET 中存在的,以及它们的退化问题来自高电场。共源共栅中的 Si MOSFET 是一种稳健的低电压类型,具有高阈值电压和厚栅极氧化层,此外还受到内置齐纳钳位的保护。在实践中,碳化硅 FET 已证明其非常可靠,其部件现在通常能达到汽车 AEC-Q 等级。

另一个重要的考虑因素是过压和短路等意外应力事件期间的可靠性。SiC FET 具有强大的雪崩能力,可通过 JFET 漏栅击穿激活。通过图 3 中的RG 产生的电流会降低电压,从而开启 JFET 并钳位过压。Si MOSFET 现在以高度可控的方式发生雪崩,因为雪崩保护二极管包含在每个单元的制造中,并且耗散的功率很小。SiC MOSFET 也具有雪崩额定值,但 GaN HEMT 单元没有,这迫使制造商在较低的电压下对部件进行额定值,以在工作和破坏性击穿电压之间获得足够的裕度。

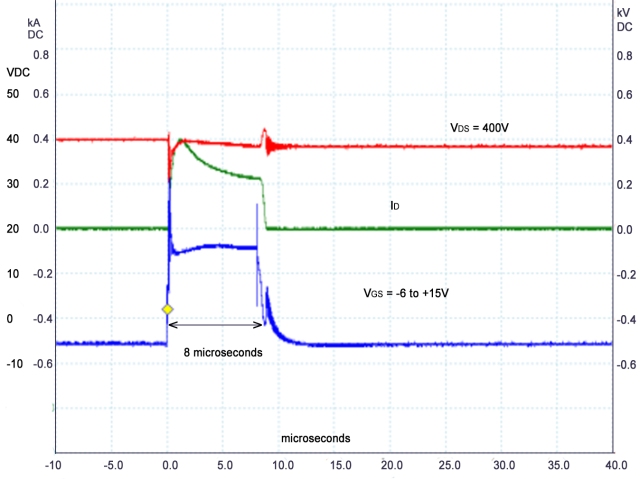

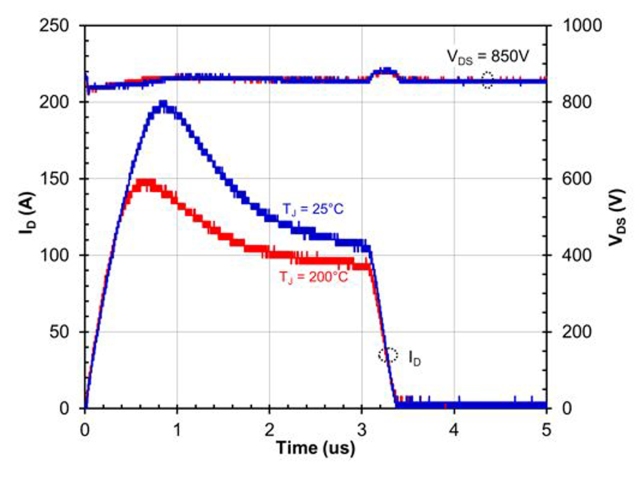

SiC FET 还具有良好的短路电流特性:在高电流下,沟道两端的电压降梯度会导致自然的“夹断”效应来限制电流。与 MOSFET 和 IGBT 不同,短路电流与栅极电压无关,而且 SiC FET 通道的导通电阻正温度系数也有助于降低限制电流并将应力分散到芯片中的各个单元上。效果如此一致,以至于 SiC FET 可用作线性电路中的精确限流器件。汽车应用中的一项典型测试是使器件能够承受至少 5 µs 的短路,图 6显示了一个 750-V SiC FET 能够承受 8 µs 的应力而没有退化。图 7 显示导通电阻随温度增加的影响,使用额定值为 1,200V 的 SiC FET 将短路电流降低到很大程度上独立于初始结温的最终值。

图 6:SiC FET 可承受来自 400V 总线的 8µs 短路应力。

图 6:SiC FET 可承受来自 400V 总线的 8µs 短路应力。 图 7:SiC FET 短路电流与初始结温无关。

图 7:SiC FET 短路电流与初始结温无关。为了保持可靠性,封装的 SiC FET 中的温升和梯度应该最小化,并且 SiC 的热导率是硅或 GaN 的 3 倍以上,在这里是一个优势。最新的器件还使用银烧结而不是焊接进行芯片连接,这使界面的热导率提高了 6 倍,从而保持较低的结温上升和较高的可靠性。

其他 SiC FET 应用

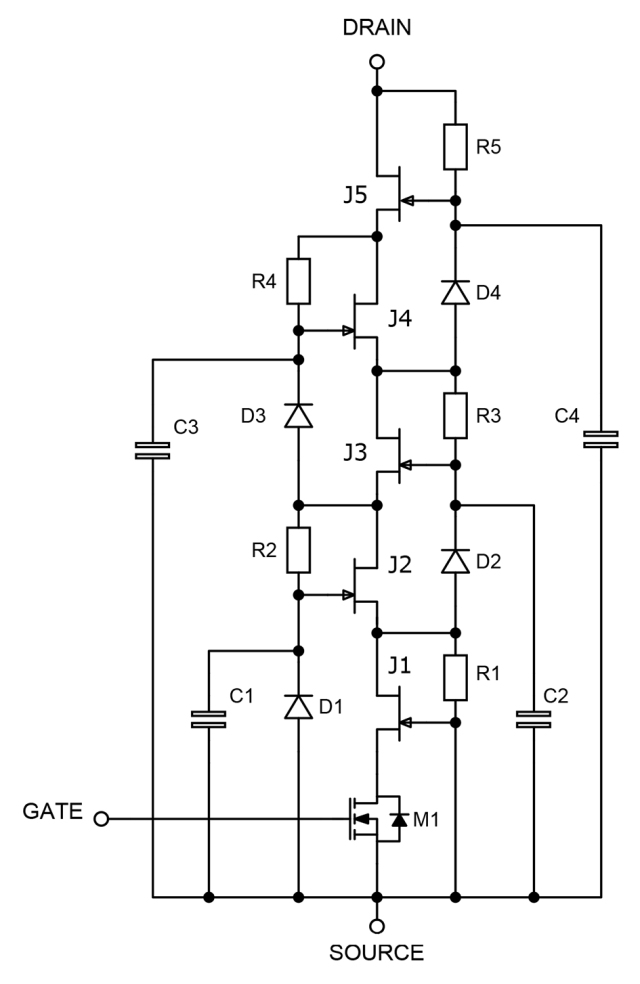

碳化硅场效应晶体管在高效功率转换器中找到了自然的归宿,可提供高达 1,700V 的额定电压,适用于典型的工业三相应用。然而,通过在控制硅 MOSFET 上“堆叠”碳化硅 JFET,可以轻松扩展共源共栅原理(图 8)。已开发出具有 40 kV 额定值的演示该原理的模块。3

图 8:堆叠共源共栅原理可用于额定电压为数十千伏的高电压。

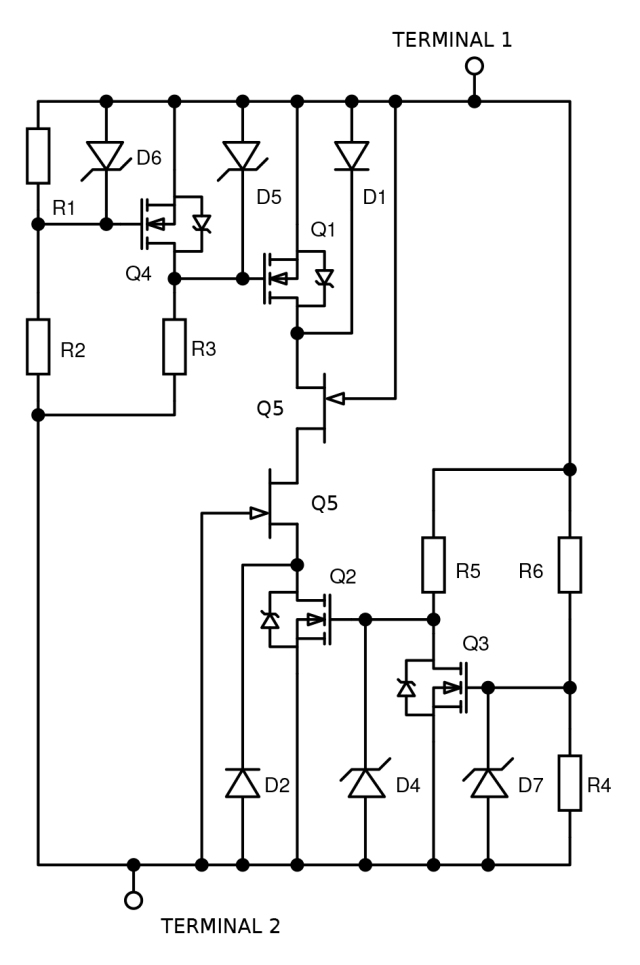

图 8:堆叠共源共栅原理可用于额定电压为数十千伏的高电压。如前所述,碳化硅 JFET 具有接近恒定的饱和电流特性,具有栅极-源极和漏极电压,这可用于电流限制器或断路器等电路保护应用。图 9显示了使用 SiC FET 共源共栅的自偏置断路器概念,它是真正的“两端”,没有外部辅助电源轨或内部 DC/DC 转换器。

图 9:两端自偏置断路器概念

图 9:两端自偏置断路器概念在提高性能和价值方面取得进展

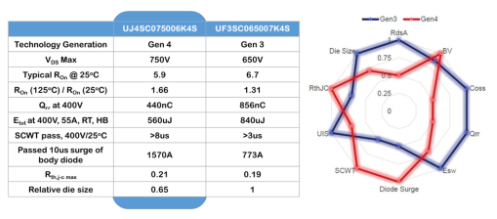

SiC FET 经历了几代技术的进步。最新的 GEN4 带来了一系列改进,包括可用的电压范围、更好的导通电阻的单元密度,以及提高热性能的烧结芯片连接。现在使用基板减薄技术,因为通道电阻非常低,通过基板本身的传导损耗成为一个限制因素。在动态方面,部件也得到了改进,特别是输出电容 (C oss)。这降低了硬开关拓扑(例如连续传导模式下的图腾柱 PFC)的损耗,并在软开关谐振电路(例如 LLC 或 PSFB)中实现更高频率的操作。开关边缘速率现在如此之快,以致于为设备提供了超快和有意减慢的“快速”额定值,以适应边缘速率对性能并不重要并且可能导致 EMI 和故障问题的应用,例如在电机驱动中。

封装也从第一个 SiC FET 发展而来,由 Si MOSFET 和 SiC FET 裸片并排排列形成,并带有互连线键合。例如,这可实现 TO-247 封装的灵活性,但为了降低成本和提高性能,“堆叠”芯片布置现在普遍用于大电流的大芯片,尤其是在紧凑模块中并联部件时。为了获得更好的热性能,焊片贴装已让位于银烧结,而 DFN 8 × 8 封装可实现用于兆赫兹开关的低电感、高频布局。TO-220、TO-247 和 D2PAK 封装仍然很受欢迎,因为它们可以将 SiC FET 改造为旧设计,甚至是使用 IGBT 的设计。

除此之外,使用碳化硅场效应晶体管从其电气性能中增加的价值得到了成本降低计划的补充,该计划通过持续改进生产良率和向 8 英寸晶圆发展。

SiC FET 是一种引人注目的解决方案

现在,最新一代 SiC FET 更接近理想的开关。传导和动态损耗是有史以来最低的,使高频功率转换级具有 99% 以上的效率,并相应地节省了能源、尺寸和重量。设计师对“理想”有更广泛的定义;他们还希望该部件在一个方便的封装中易于驱动,具有稳定的特性,在广泛的操作和故障条件下。与此同时,设备最终用户需要可靠的最终产品,其总生命周期成本优于旧技术实施。UnitedSiC 的 SiC FET 可通过一系列额定电压为 650 V 至 1,700 V 且导通电阻低至 7 mΩ 的部件实现这一点。

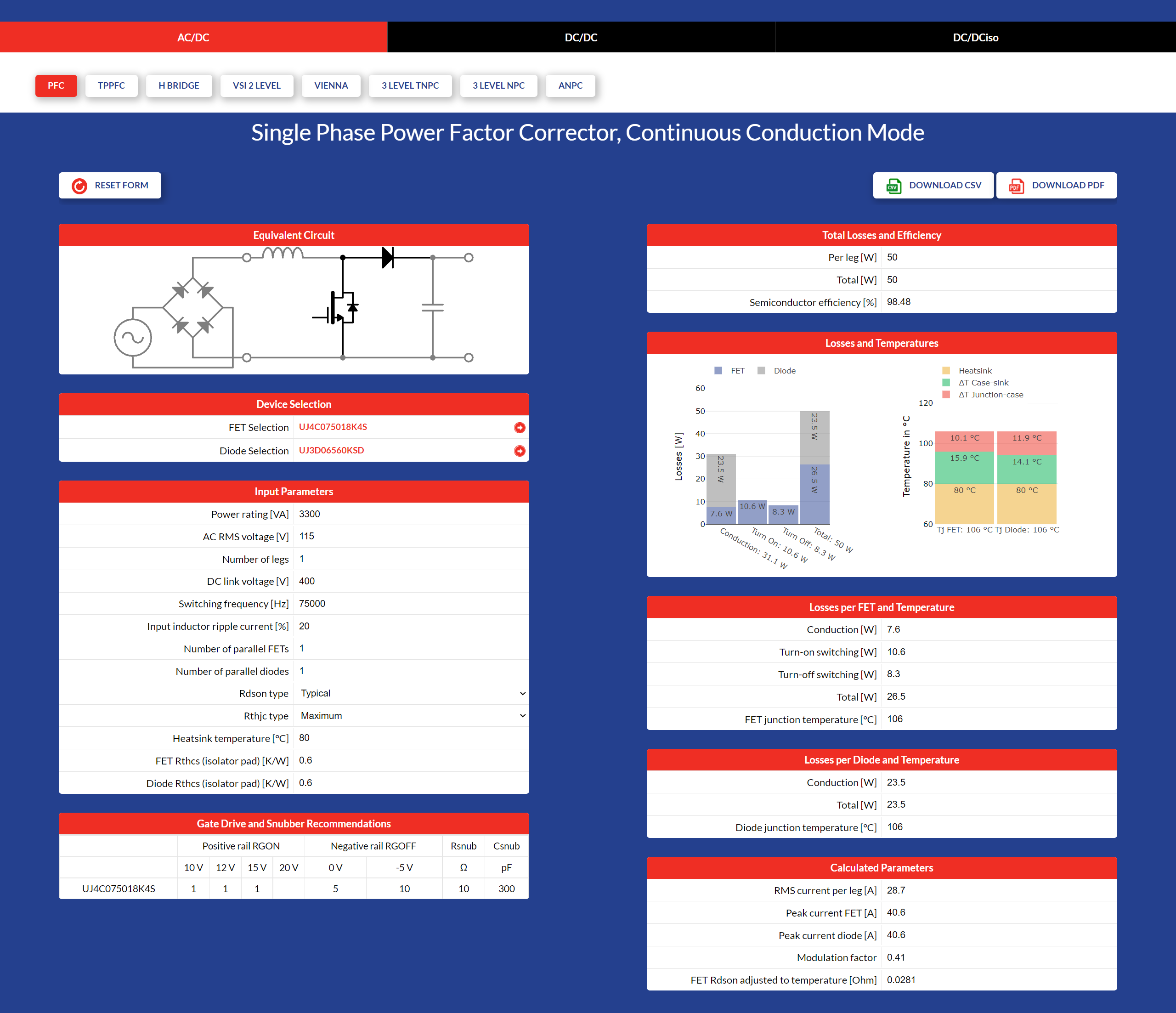

作为设计辅助工具,UnitedSiC 的“FET JET”计算器4允许在选择的功率转换拓扑结构中对其任何器件进行快速选择和性能预测,包括 PFC 级和隔离/非隔离 DC/DC 转换器。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论