需要读卡距离35cm以上,目前条件下只能做20cm左右,如何增加具体的放大电路来增加发射功率呢?

2024-03-21 06:50:27

STM32F4的裸机源码可以移植到linux ARM开发板上运行吗?

具体需要怎么实现呢?

2024-03-20 07:00:05

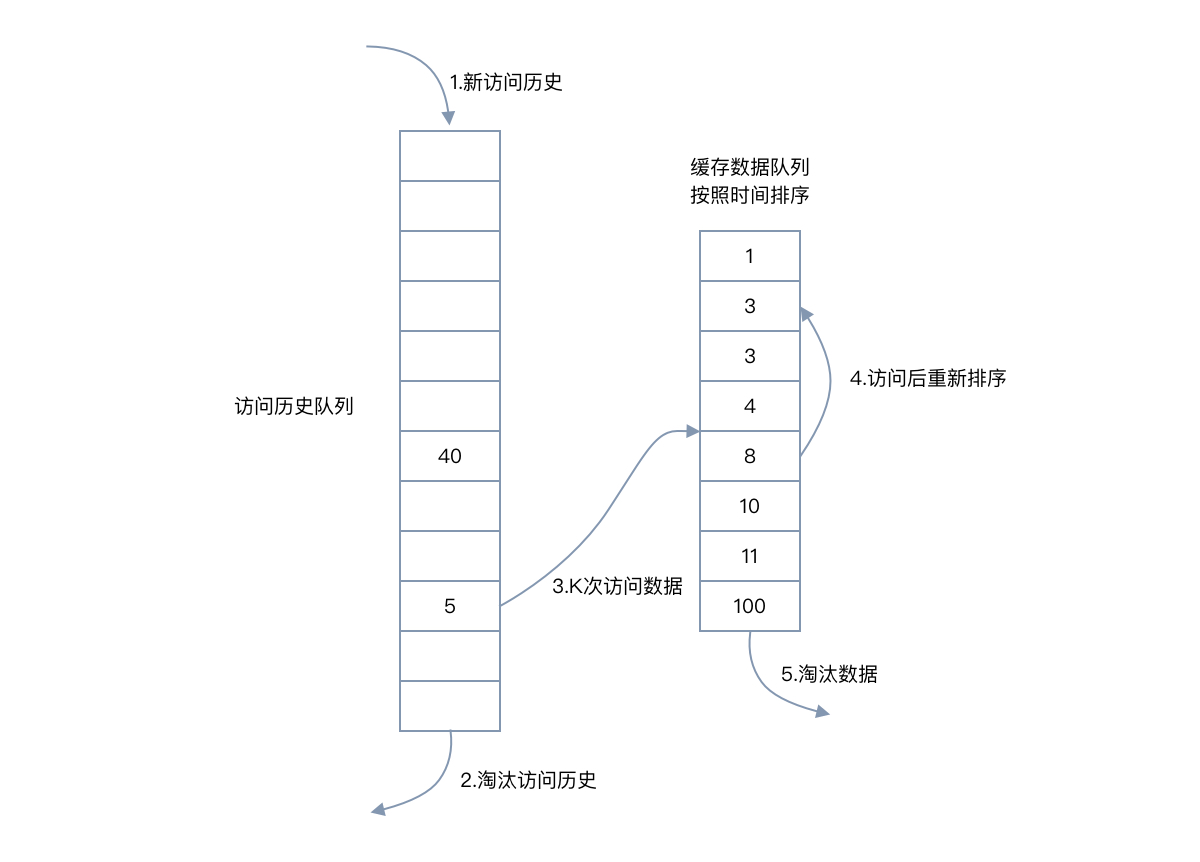

交换机是数据中心不可缺少的网络设备,在数据中心里发挥着重要作用。在平时使用和采购时,大多数都关注交换机的背板带宽、端口密度、单端口速度、协议特性等方面的性能指标,很少有人去关注缓存指标,这是一个常常

2024-03-15 17:39:55 126

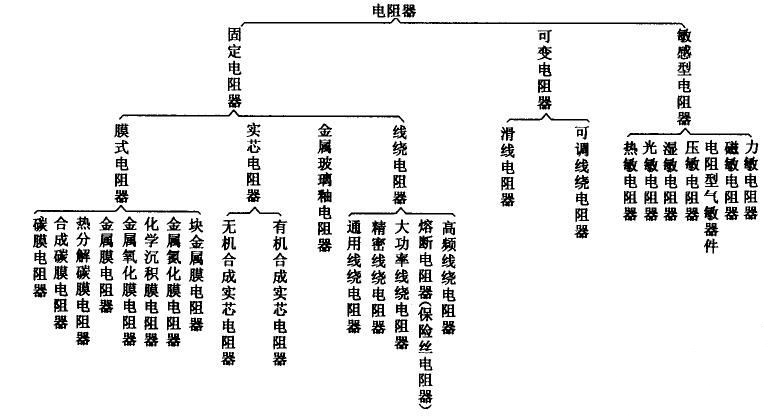

126 变阻器 电路保护 - 分类套件 分类

2024-03-14 21:19:04

现在一般的汽车ECU处理器是32位的吗,具体的RAM和Flash有多大呢?现在汽车的ECU处理器位数发展到多少了?相应配备的RAM和Flash有多大?

2024-02-02 06:08:04

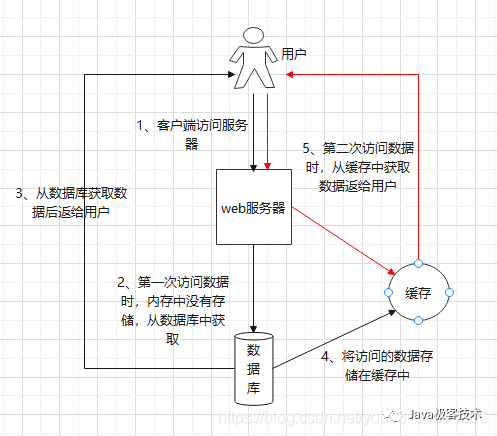

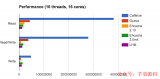

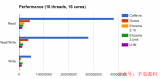

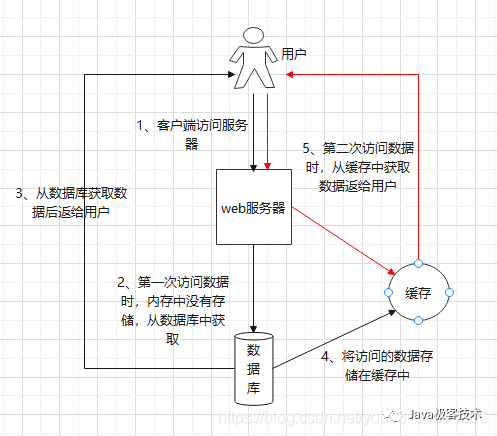

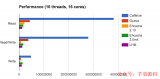

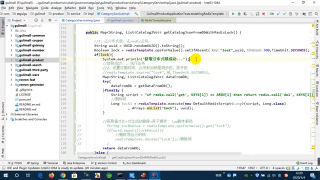

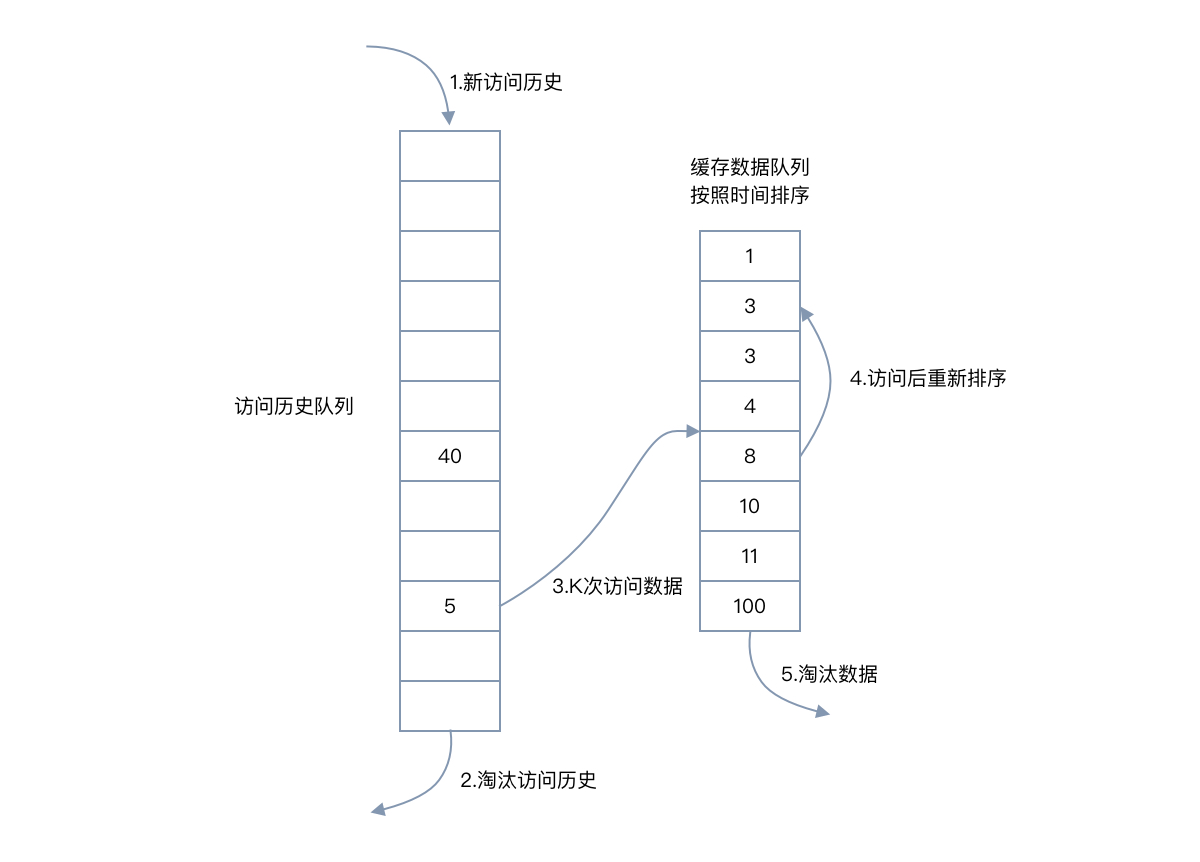

小编最近在使用系统的时候,发现尽管应用已经使用了 redis 缓存提高查询效率,但是仍然有进一步优化的空间,于是想到了比分布式缓存性能更好的本地缓存,因此对领域内常用的本地缓存进行了一番调研,有早期

2024-01-18 11:19:07 478

478

LabVIEW 是一款功能强大的图形化编程软件,常用于控制、监测和数据采集等应用。当我们使用串口进行数据通信时,有时会遇到串口缓存的数据无法及时清除或清除不彻底的情况。解决这个问题的方法有多种,下面

2024-01-08 11:30:09 670

670 请问Linear Lab Tool具体是做什么的呢?

2024-01-05 12:52:00

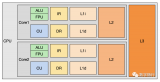

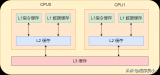

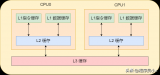

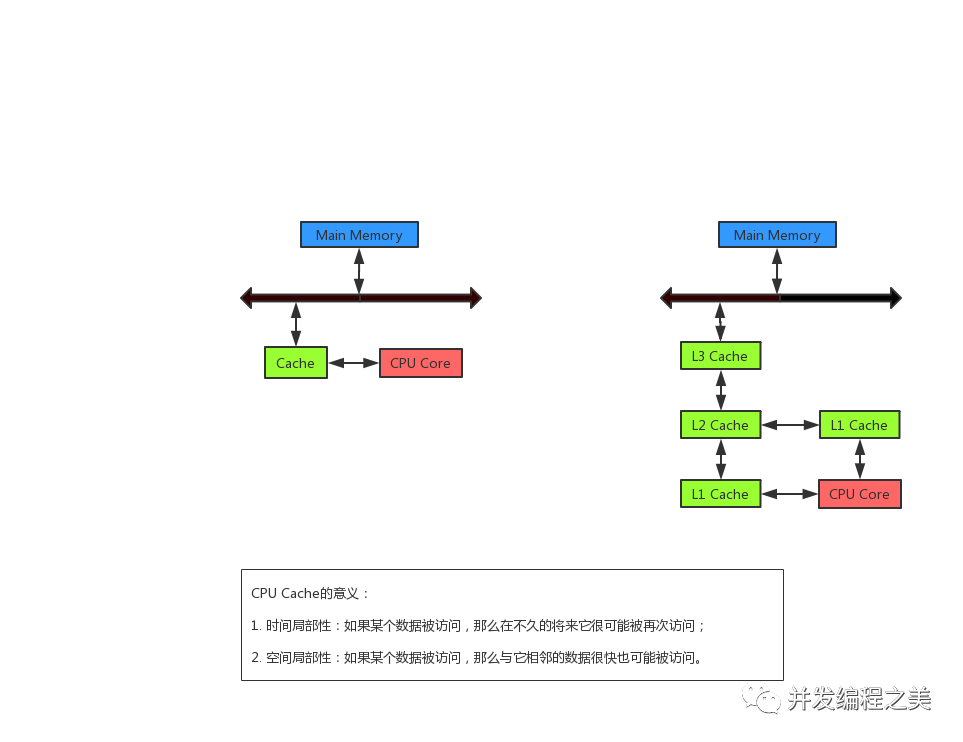

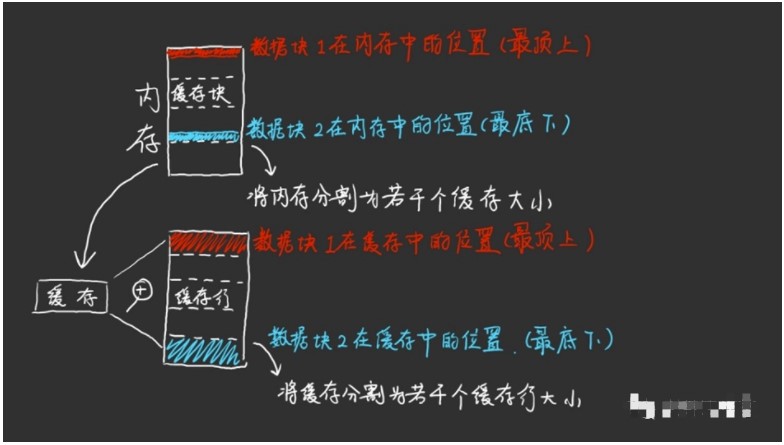

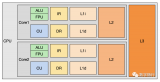

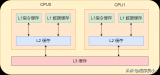

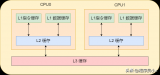

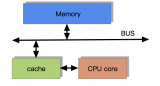

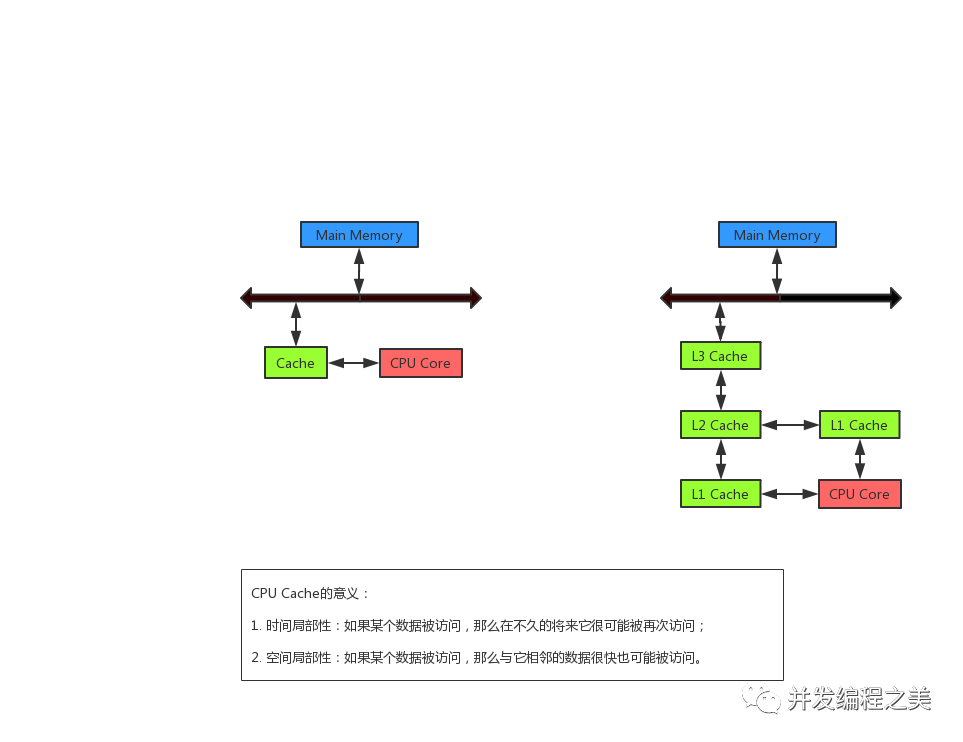

CPU的核心功能包括数据运算和指令控制。CPU运算的数据和执行的指令全部存储在CPU的寄存器中,这些数据和指令又都来自于CPU高速缓存。

2024-01-02 16:01:48 663

663

缓存预热就是系统上线后,提前将相关的缓存数据直接加载到缓存系统。

2023-12-25 09:41:02 250

250

温控开关可以根据不同的分类标准进行分类,以下是几种常见的分类方式

2023-12-13 14:46:27 463

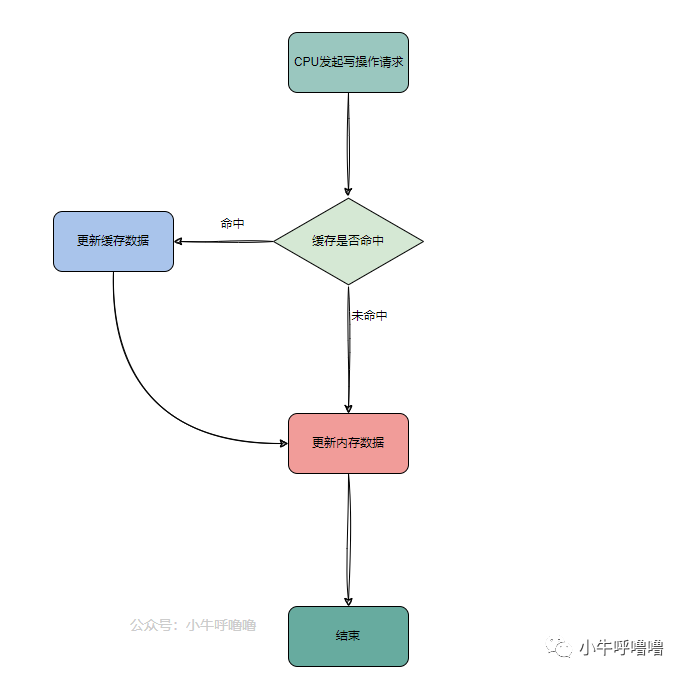

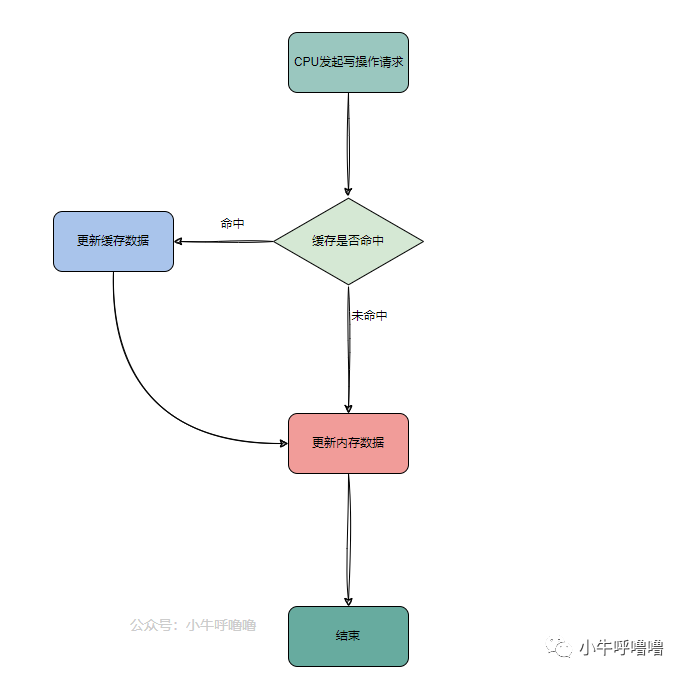

463 我们介绍`CPU Cache`的组织架构及其进行**读操作**时的寻址方式,但是缓存不仅仅只有读操作,还有 **写操作** ,这会带来一个新的问题

2023-12-04 15:05:32 459

459

MyBatis是一种轻量级的持久化框架,它提供了一级缓存和二级缓存的机制来优化数据库操作性能。一级缓存是默认开启的,而二级缓存需要手动配置启用。 一、一级缓存 1.1 缓存生命周期 一级缓存存在于

2023-12-03 11:55:11 438

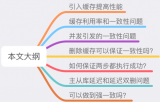

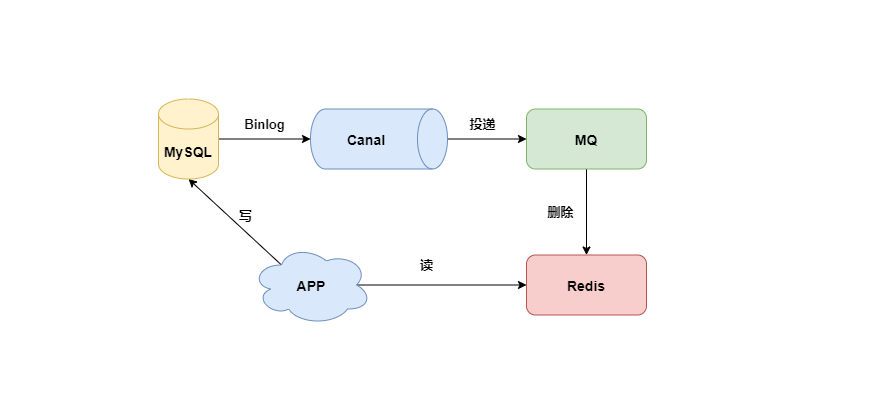

438 基本流程就是客户端A请求,先去删除缓存,然后将数据写入数据库,此时客户端B查询先去查询缓存,缓存没有返回,去查数据库,此时还没有完成主从同步,拿到是从库的旧数据,然后将旧数据进行缓存,在客户端A完成主从同步后,再次删除缓存,这时数据才是一致的,但是重点就是在休眠的几秒钟,会造成数据的不一致性;

2023-12-02 14:23:53 601

601

PLC光分路器的分类和具体用法 PLC(Planar Lightwave Circuit,平面光波导电路)光分路器是一种集成光学器件,用于在光通信、光网络、传感器和光学测试等领域中实现光信号的分配

2023-11-28 15:50:56 463

463 作者最近在开发公司项目时使用到 Redis 缓存,并在翻看前人代码时,看到了一种关于 @Cacheable 注解的自定义缓存有效期的解决方案,感觉比较实用,因此作者自己拓展完善了一番后分享给各位。

2023-11-28 10:44:14 261

261

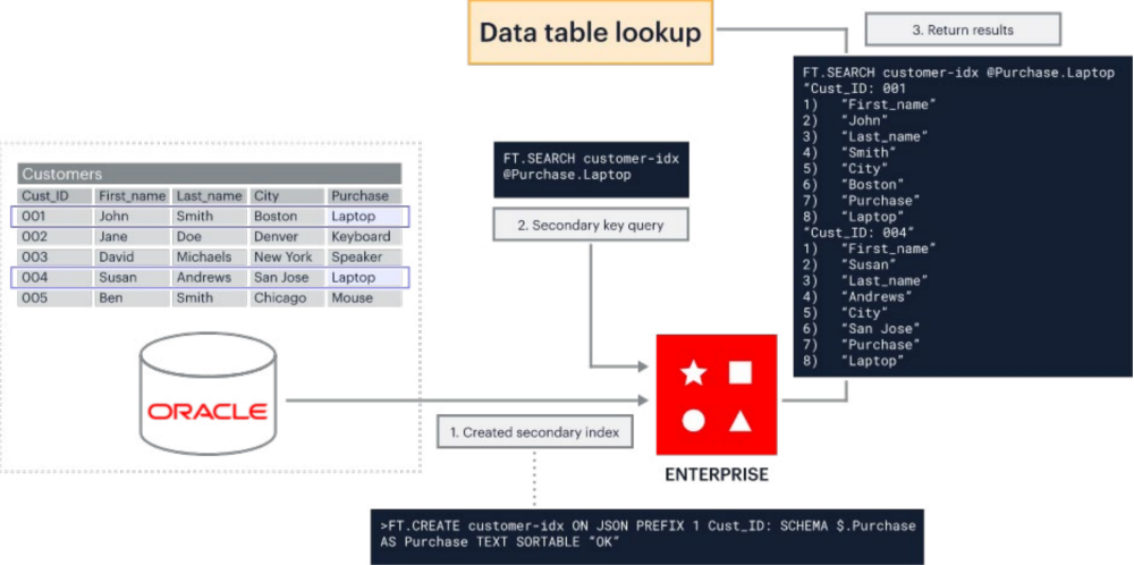

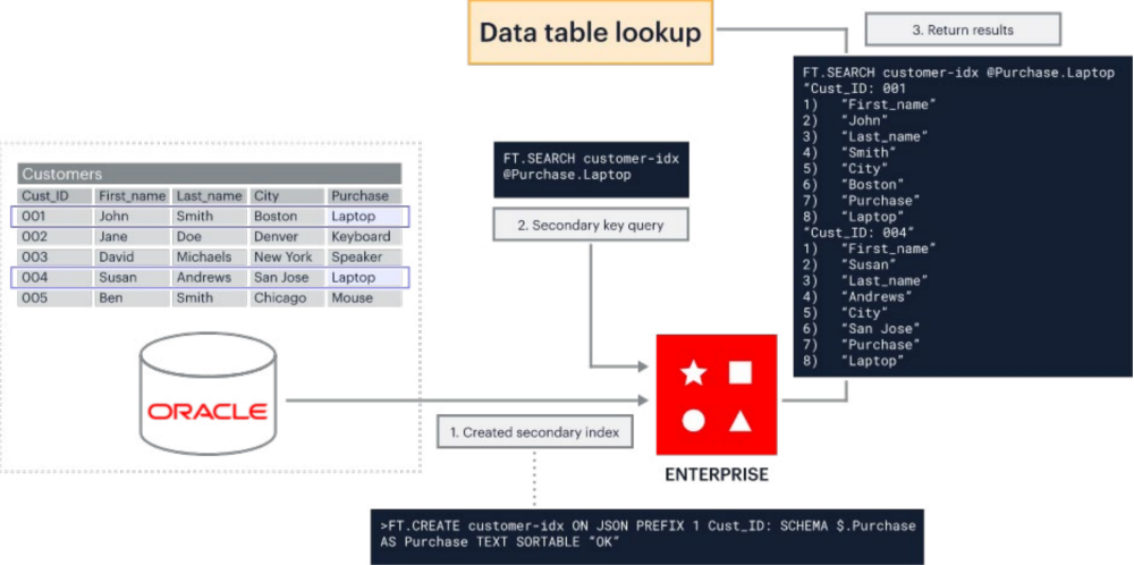

单独使用Oracle作为企业缓存数据库时,会出现哪些问题呢?使用RedisEnterprise与Oracle共同用作企业级缓存或副本数据库,会出现哪些喜人的提升呢?Orcle配合

2023-11-26 08:04:33 126

126

钳子套装 钳子 分类 分类

2023-11-24 15:26:39

钳子套装 钳子 分类 分类

2023-11-24 15:26:20

一个是锐龙7 5700X3D,可以视为锐龙7 5800X3D的降频版,主频从3.4-4.5GHz来到了3.0-4.1GHz,同时依然有8核心16线程、4MB二级缓存、96MB三级缓存(包括64MB 3D缓存),合计达100MB。

2023-11-22 17:07:32 555

555

单独使用Oracle作为企业缓存数据库时,会出现哪些问题呢?使用Redis Enterprise与Oracle共同用作企业级缓存或副本数据库,会出现哪些喜人的提升呢?Orcle配合使用Redis Enterprise,为什么能够打造更快、更高效、更具成本效益的现代企业数据库呢?

2023-11-22 10:00:03 258

258

HashMap 是很多程序员接触的第一种缓存 , 因为现实业务场景里,我们可能需要给缓存添加缓存统计、过期失效、淘汰策略等功能,HashMap 的功能就显得孱弱 ,所以 HashMap 在业务系统中使用得并不算多。

2023-11-14 18:02:23 232

232

一直以来我们都知道socket的缓存会对tcp性能产生影响,也有无数文章告诉我们应该调大socke缓存。但是究竟调多大?什么时候调?有哪些手段调?具体影响究竟如何?这些问题似乎也没有人真正说明

2023-11-09 10:13:28 246

246 请问论坛的大佬们,

①逆变器并联系统的环流产生机制到底是什么呢?看了很多论文都说法不一。有的说共交直流系统的并联才会产生环流;

②那么环流是如何具体体现的呢?有的说法是逆变器三相电流之和,也有说法

2023-10-30 20:12:19

时间序列数据分析在工业,能源,医疗,交通,金融,零售等多个领域都有广泛应用。其中时间序列数据分类是分析时序数据的常见任务之一。本文将通过一个具体的案例,介绍 Intel 团队

2023-10-27 11:08:29 303

303

开辟20kb左右的缓存空间,如果直接用全局变量数组,在不需要用到DMA时,那这20k的内存就一直不能释放,好浪费。若使用malloc来开辟动态内存,应该是放在堆区吧?堆区不是默认只有512字节?还要修改启动文件的堆大小?

2023-10-23 06:53:54

“ 本文的参考文章是2022年HOT 34上Intel Rob Blakenship关于CXL缓存一致性的一篇介绍。”

2023-10-19 17:42:27 447

447

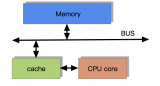

缓存是将频繁访问的数据或资源存储在临时存储位置(例如内存或磁盘)的过程,以提高检索速度并减少重复处理的需要。

2023-10-17 10:48:06 453

453

电子元器件按照A/B/C分类法可以根据其功能、特性和用途进行分类。这种分类方法是根据国际电工委员会(IEC)制定的标准,用于对电子元器件进行统一的分类和命名。

2023-10-13 09:31:23 792

792 缓存技术被认为是减轻服务器负载、降低网络拥塞、增强Web可扩展性的有效途径之一,其基本思想是利用客户访问的时间局部性(Temproral Locality)原理, 将客户访问过的内容在Cache

2023-10-08 14:07:17 300

300 提高指令缓存命中率 前面说的是数据缓存,现在看看指令缓存命中率该如何提高。 有一个数组 array ,数组元素内容为 0-255 之间的随机数: int array

2023-10-04 15:45:00 256

256 LRU(Least Recently Used)是一种缓存替换算法,它的核心思想是当缓存满时,替换最近最少使用的数据。在实际应用中,LRU算法被广泛应用于缓存、页面置换等领域。Rust语言提供

2023-09-30 16:47:00 493

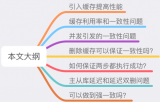

493 一、摘要 说到缓存,面试官基本上会绕不开以下几个话题! 项目中哪些地方用到了缓存?为什么要使用缓存?怎么使用它的?引入缓存后会带来哪些问题? 这些问题,基本上是互联网公司面试时必问的一些问题,如果

2023-09-30 15:29:00 338

338

缓存一致性 每次逢年过节的时候抢票非常艰难,放票的时候那么多人同时去抢票,如果所有人查询、购票等都去访问数据库,那数据库的压力得有多大,这时候很多都会引入缓存, 把车票信息放入缓存,这样可以减少

2023-09-25 15:25:31 606

606

电子发烧友网站提供《管理基于Cortex-M7的MCU的高速缓存一致性.pdf》资料免费下载

2023-09-25 10:11:48 0

0 stm32的双缓存dma怎么使用,一般用在哪里

2023-09-21 08:23:59

电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7 MCU上在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-20 11:40:24 0

0 电子发烧友网站提供《使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-19 16:28:10 0

0 从AMD给出的图片来看,Genoa-X的采用的是混合键合的方式实现了CPU核心和SRAM核心的连接。AMD可以为每个CCD增加64MB SRAM L3缓存,是原生CCD中包含的32MB的2倍。由于

2023-09-13 15:41:09 578

578

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作。当wr被插入时,输入的数据被写入缓存,此时读操作被忽视。FIFO缓存的head一般

2023-09-11 10:12:39 376

376

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作

2023-09-11 09:12:23 257

257

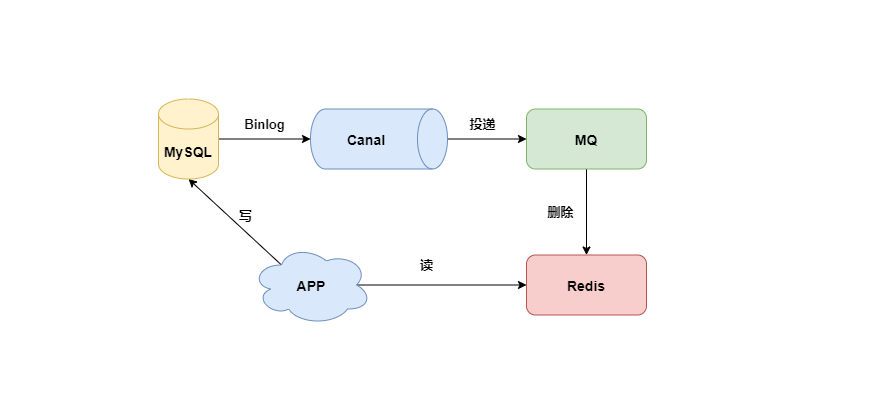

CPU Cache 在读取内存数据时,每次不会只读一个字或一个字节,而是一块块地读取,这每一小块数据也叫CPU 缓存行(CPU Cache Line)。这也是对局部性原理的运用,当一个指令或数据

2023-09-10 10:57:28 341

341

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作。

2023-09-08 09:06:18 237

237

在实际应用中,并不是单一的使用本地缓存或者redis,更多是组合使用来满足不同的业务场景,于是如何优雅的组合本地缓存和远程缓存就成了我们要研究的问题,而这一点,阿里开源的jetcache组件帮我们实现了

2023-09-07 10:36:51 470

470

什么是高速缓存?• 高速存储器块,包含地址信息(通常称作TAG)和相关联的数据。• 目的是提高对存储器的平均访问速度• 高速缓存的应用基于下面两个程序的局部性 :• 空间局部性:如果一个存储器的位置

2023-09-07 08:22:51

本应用笔记描述了意法半导体开发的首款指令缓存(ICACHE)和数据缓存(DCACHE)。在 Arm® Cortex®-M33 处理器的 AHB 总线中引入的 ICACHE 和 DCACHE 嵌入到

2023-09-07 07:51:27

2级缓存控制器(AC131)本文件描述了按严重程度分类的勘误表。每种描述都包括:•缺陷的当前状态•实施偏离规范的地方以及错误行为发生的条件•勘误表对典型应用程序的影响•可能的情况下“变通办法”的应用和限制

2023-09-04 07:22:44

许多web服务需要对数十亿个小对象实现快速访问,而每个小对象只有几百个字节。为了实现这一点同时考虑实际生产效益,缓存系统必须做到同时低成本,大容量与高性能。

2023-08-29 09:01:27 395

395

根据不同的分类方法对可视化安冬暗按拉灯呼叫Andon安灯系统进行的分类,每种类型的Andon安灯系统都有其独特的特点和应用场景。在实际应用中,需要根据具体需求选择合适的类型,以达到最佳的使用效果。

2023-08-28 16:42:53 426

426

这份白皮书着眼于ARM实施的敏感性,此前包括谷歌和麻省理工学院在内的安全研究人员对利用处理器推测的新的潜在缓存计时旁路进行了研究。

本白皮书还概述了可用于设计在现有ARM处理器上运行的软件的可能缓解措施

2023-08-25 08:23:45

电子发烧友网站提供《LSIiBBU和CFVM01缓存备份产品用户指南.pdf》资料免费下载

2023-08-23 15:10:58 0

0 电子发烧友网站提供《MegaRAID CacheCade Pro 2.0读/写缓存软件.pdf》资料免费下载

2023-08-22 10:59:29 0

0 CPU高速缓存集成于CPU的内部,其是CPU可以高效运行的成分之一,本文围绕下面三个话题来讲解CPU缓存的作用

2023-08-21 12:17:35 797

797

当处理器产生大量内存流量时,添加片上二级缓存(也称为二级或二级缓存)是提高基于ARM的系统性能的公认方法。根据定义,二级缓存假定存在与处理器紧密耦合或内部的一级缓存或主缓存。缓存控制器的功能

2023-08-02 15:09:49

当中央处理器(CPU)产生大量内存流量时,添加片上二级缓存(也称为二级缓存,L2CC)是提高计算机系统性能的公认方法。根据定义,二级缓存假定存在与CPU紧密耦合或内部的一级缓存或主缓存。

2023-08-02 13:11:45

您应该熟悉用于描述AHB缓存及其操作的术语。

本文件使用Arm®AMBA®5 AHB协议规范B.B版中定义的术语来描述AHB传输:

•可缓冲•可修改•查找•分配下表描述了AHB Cach使用的复杂传输属性

2023-08-02 11:05:17

电子发烧友网站提供《STM32F7技术--高速缓存.pdf》资料免费下载

2023-08-01 15:18:55 0

0 电子发烧友网站提供《使用STM32缓存来优化性能与功率效率应用笔记.pdf》资料免费下载

2023-08-01 10:02:53 0

0 但凡牵涉到SmartNIC,都免不了牵涉到MAC IP。在网络设计里,MAC IP Rx端一般都是不接受反压的,随着报文类型对应的处理能力的不一样,在MAC收包处不可避免的存在报文缓存和丢包。

2023-07-30 10:08:49 320

320

就Java而言,其常用的缓存解决方案有很多,例如数据库缓存框架EhCache,分布式缓存Memcached等,这些缓存方案实际上都是为了提升吞吐效率,避免持久层压力过大。

2023-07-29 11:21:07 1150

1150

网络服务几乎在系统架构的每一层都依赖于缓存。大型网络服务依靠缓存系统来实现高性能和高效率。例如,在Facebook,CDN缓存为70%的网络请求提供服务,将延迟降低了一个或多个数量级。

2023-07-27 09:02:03 596

596

好久没有写一些微观方面的文章了,今天写一篇关于CPU Cache相关的文章,这篇文章比较长,主要分成这么几个部分:基础知识、缓存的命中、缓存的一致性和延伸阅读。其中会讲述一些多核 CPU 的系统架构

2023-07-17 12:26:24 739

739

不同分类方式可能会相互重叠或衔接,而且厂商和行业可能会有自己的特定分类。因此,在选择高压连接器时,需要根据具体应用需求和标准要求来选择合适的连接器类型。

2023-07-14 11:46:21 868

868

CPU运行效率高不高,一定程度取决于缓存,这里就给大家分享一下CPU缓存相关的内容。

2023-07-12 10:07:51 406

406

缓存服务器是什么?缓存服务器是专用网络服务器或充当在本地保存网页或其他互联网内容的服务器的服务。通过将以前请求的信息放入临时存储(或高速缓存)中,高速缓存服务器既可以加快数据访问速度,又可以减少

2023-07-07 17:48:59 353

353 对于存储来说,性能是绕不开的话题。当提到性能,可靠、高效的缓存策略是极其重要的。

2023-06-29 15:05:10 536

536

刷新本地 DNS 缓存可以解决 HTTP 错误并保护您免受 DNS 欺骗。以下是在 Linux 上执行此操作的方法。 当您使用域名访问网站时,您的系统会向 DNS 服务器发送请求以获取

2023-06-26 10:52:54 2281

2281

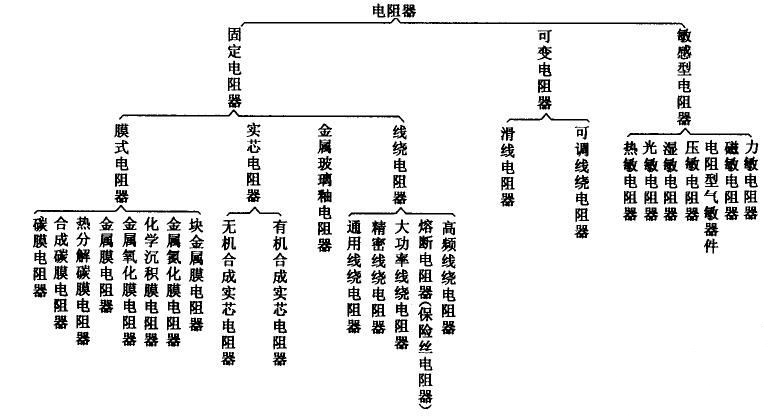

电阻器在日常生活中一般直接称为电阻,是组成电路的基本元件之一,也是应用最广泛的电子元器件,大约占所有电子元器件的35%。电阻器的分类也是多种多样的,电阻器按照其结构和性能的不同,可分为固定电阻器、可变电阻器和敏感型电阻器三大类,具体分类如下。

2023-06-21 15:36:34 2486

2486

如何使用 UART printf 印出不同页的缓存器值?

2023-06-16 06:41:15

缓存是计算机科学中的一个重要概念。设想某个组件需要访问外部资源,它向外部源请求资源,接收并使用资源,这些步骤都需要花费时间。

2023-06-12 09:50:59 369

369

本地缓存 :应用中的缓存组件,缓存组件和应用在同一进程中,缓存的读写非常快,没有网络开销。但各应用或集群的各节点都需要维护自己的单独缓存,无法共享缓存。

2023-06-11 15:12:21 556

556

之前介绍了java并发包的cas原理和java内存模型,这篇我们介绍下cpu缓存一致性原理,可以帮助我们更好的理解cas的底层原理。

2023-06-09 16:01:17 2572

2572

电子发烧友网站提供《用于PCChips M919的3.3V 1MB缓存棒设计.zip》资料免费下载

2023-06-08 10:52:29 0

0 对于一个百万、千万级别的接口调用,若是没有缓存的设计,直接打到数据持久层,那将是毁灭性的灾难。

2023-05-23 14:20:08 181

181

首先来了解几个概念: 缓存穿透:大量请求根本不存在的key 缓存雪崩:redis中大量key集体过期 缓存击穿:redis中一个热点key过期(大量用户访问该热点key,但是热点key过期) 穿透

2023-05-23 09:54:00 375

375

缓存(Cache)在代码世界中无处不在。从底层的CPU多级缓存,到客户端的页面缓存,处处都存在着缓存的身影。缓存从本质上来说,是一种空间换时间的手段,通过对数据进行一定的空间安排,使得下次进行数据访问时起到加速的效果。

2023-05-22 11:01:14 637

637

当下优秀的缓存中间件,当属 Redis 莫属,它不仅性能非常高,还提供了很多友好的数据类型,可以很好地满足我们的业务需求。

2023-05-15 14:30:19 248

248

根据不同的分类标准,HTMD连接器可以有不同的分类方式。

2023-05-15 11:04:03 360

360

在学习Spring Cache之前,笔者经常会硬编码的方式使用缓存。

2023-05-11 17:40:23 350

350

工业通信协议如modbus如何具体使用呢?是否依赖一定的硬件,还是根据协议直接编程实现数据读写?

2023-05-05 15:47:22

今天给大家介绍一下如何在SpringBoot中解决Redis的缓存穿透、缓存击穿、缓存雪崩的问题。

2023-04-28 11:35:19 495

495 ,所以我们将此页面重新映射到可缓存内存:

void* Image = memremap(pyhsmem.start, physmem.size, MEMREMAP_WB);

这极大地提高了性能。

不幸

2023-04-27 08:30:48

我正在使用 S32k358 uC,我想禁用内存区域的数据缓存。在框图中,我看到树形 SRAM 块 SRAM0、SRAM1、SRAM2。是否可以禁用 SRAM2 的数据缓存并保留 SRAM 0 和 SRAM1 的数据缓存?

2023-04-23 08:01:09

我有一个带有 RT1064 和 HyperRAM(与 EVK 相同的芯片)的系统。这非常有效,我已经运行了数周又数周的 RAM 测试,一切都很好。但是,如果我将不可缓存的区域放在 HyperRAM

2023-04-17 07:04:11

请问一下PCB抄板的具体步骤包括哪些呢?

2023-04-14 14:31:41

一、功能简介智能垃圾分类箱通过手机APP扫码、人脸识别、IC卡、GPS定位技术,建立一户一码实名制,实现垃圾投放的有源可溯。居民将不同的垃圾投放至不同的箱体内,垃圾箱则根据居民投放的垃圾,自动进行

2023-04-03 17:23:18

最近不是正好在研究 canal 嘛,刚巧前两天看了一篇关于解决缓存与数据库一致性问题的文章,里边提到了一种解决方案是结合 canal 来操作的,所以阿Q就想趁热打铁,手动来实现一下。

2023-03-24 14:34:35 412

412

我在 EDMA 中使用 lpuart 和 lpspi 驱动程序。要应用 EDMA,缓冲区必须位于 RAM 的不可缓存区域,并带有 AT_NONCACHEABLE_SECTION_INIT宏。但在

2023-03-23 09:10:04

电子发烧友App

电子发烧友App

评论