行业背景 随着工业技术的不断发展,物联网作为新兴生产力正在改变许多行业的工作方式。在半导体芯片行业,自动蚀刻机的物联网应用正在助力企业达到监控设备更加便利、故障运维更加高效、数据分析更加精准等等

2024-03-20 17:52:39 823

823

根据已公开的研究报告,东京电子的新式蚀刻机具备在极低温环境下进行高速蚀刻的能力。据悉,该机器可在33分钟内完成10微米的蚀刻工作。此外,设备使用了新开发的激光气体,搭配氩气和氟化碳气体以提升工艺水平。

2024-02-18 15:00:22 109

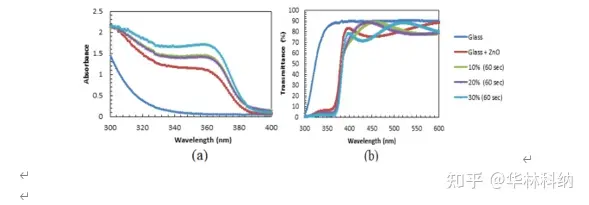

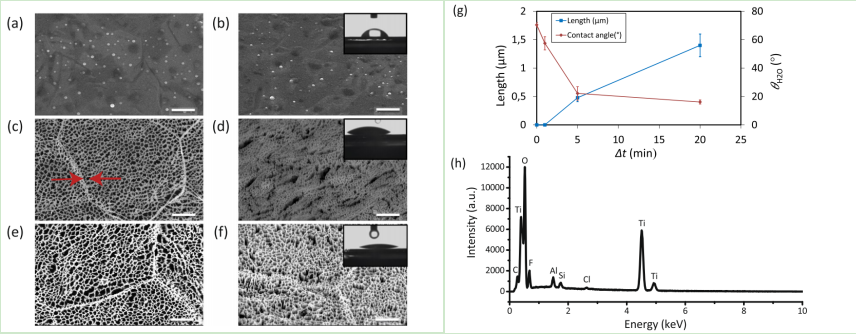

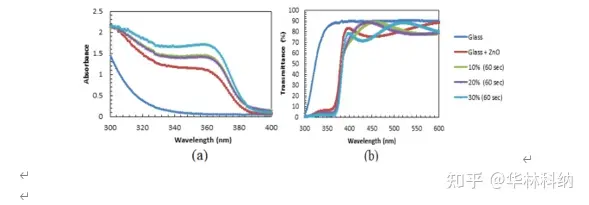

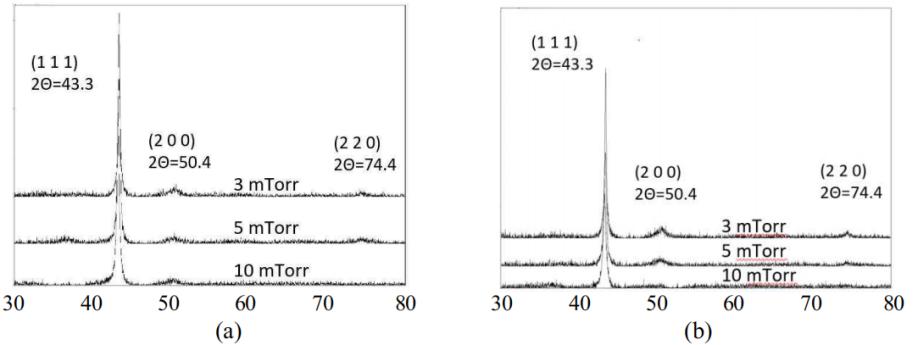

109 蚀刻时间和过氧化氢浓度对ZnO玻璃基板的影响 本研究的目的是确定蚀刻ZnO薄膜的最佳技术。使用射频溅射设备在玻璃基板上沉积ZnO。为了蚀刻ZnO薄膜,使用10%、20%和30%的过氧化氢(H2O2

2024-02-02 17:56:45 306

306

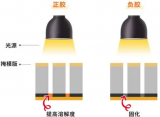

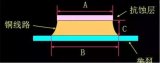

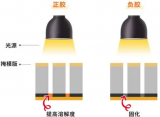

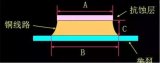

通常正片工艺是以碱性蚀刻工艺为基础的。底片上面,所需的路径或铜表面是黑色的,而不需要的部分是完全透明的。同样,在路线工艺曝光后,完全透明的部分被暴露在紫外线下的干膜阻滞剂的化学作用硬化,随后的显影过程将在下一工序中冲走无硬衬底的干膜

2024-01-17 15:33:35 163

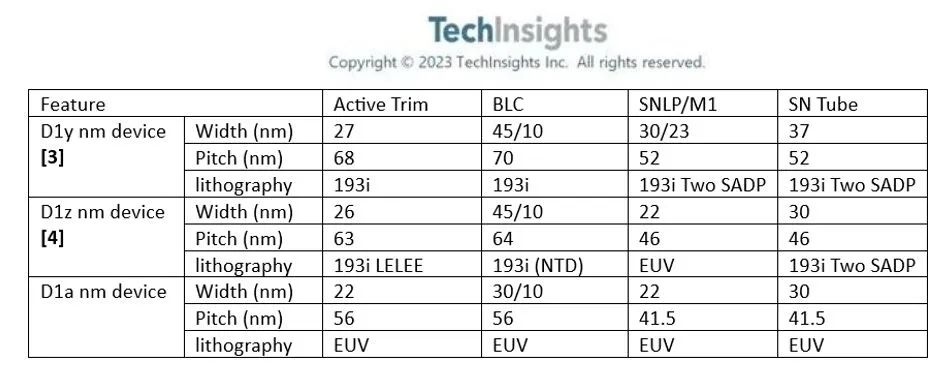

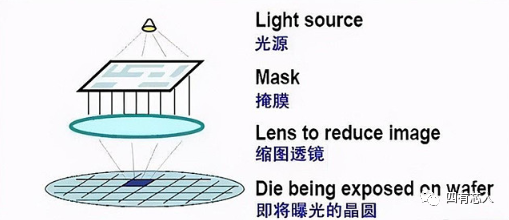

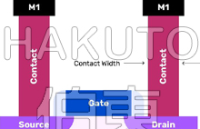

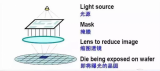

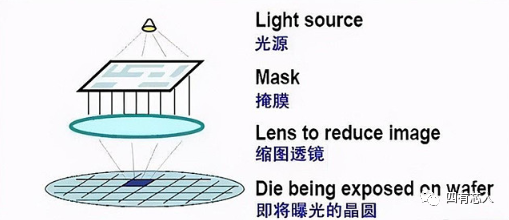

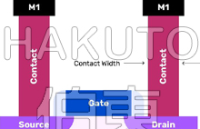

163 光罩限制(光穿过芯片掩模以在硅晶圆上蚀刻晶体管的孔径大小)不仅定义了小芯片的设计方式,而且还限制了离散计算和内存块的大小单个晶圆。

2024-01-05 16:23:11 1976

1976

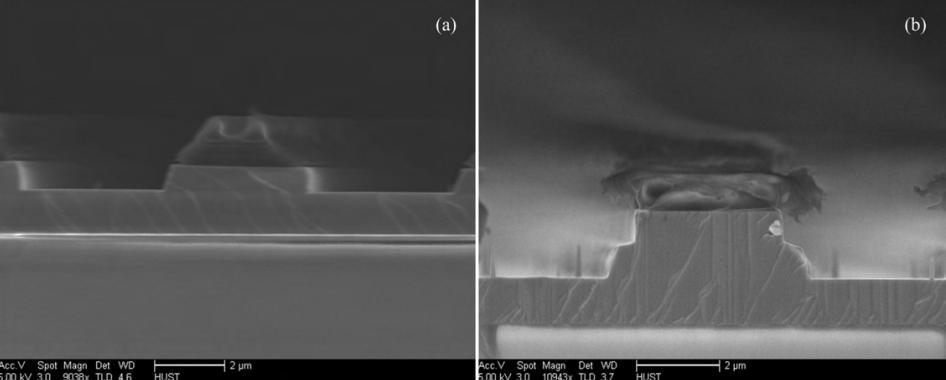

铜箔蚀刻过度,市场上使用的电解铜箔一般为单面镀锌(俗称灰化箔)及单面镀铜(俗称红化箔),常见的甩铜一般为70um以上的镀锌铜箔,红化箔及18um以下灰化箔基本都未出现过批量性的甩铜。

2023-12-28 16:30:47 86

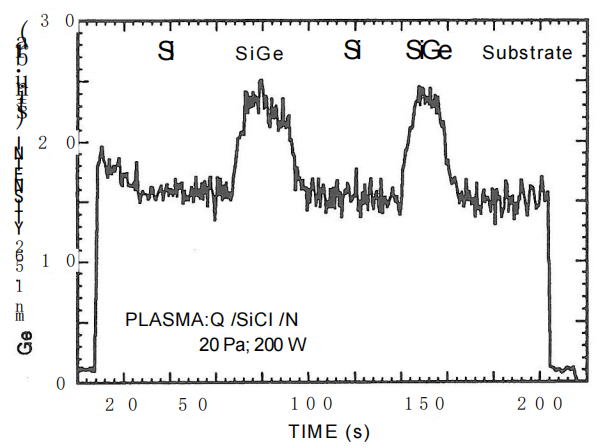

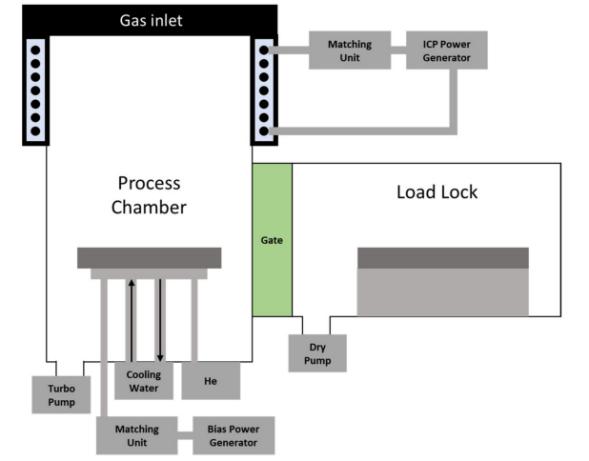

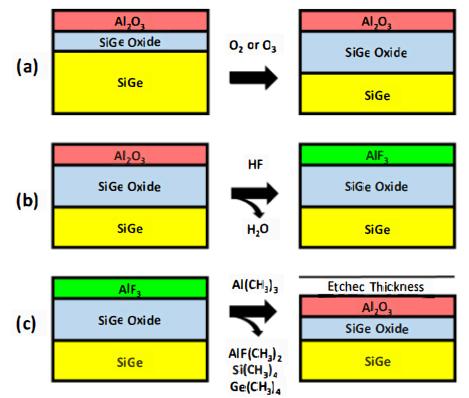

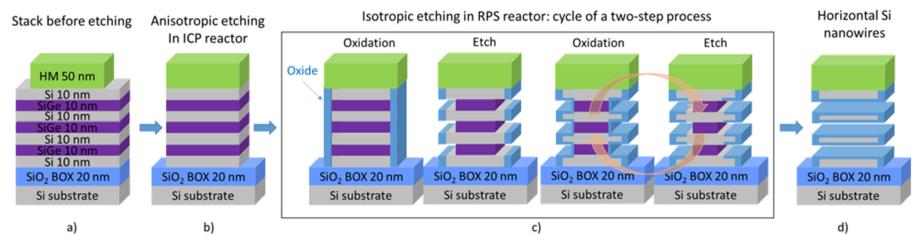

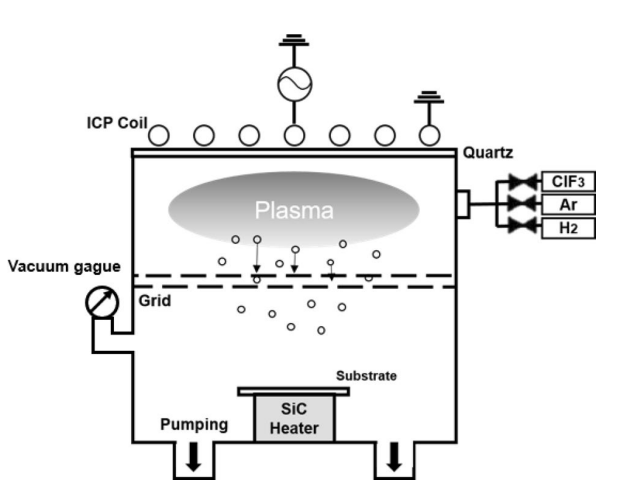

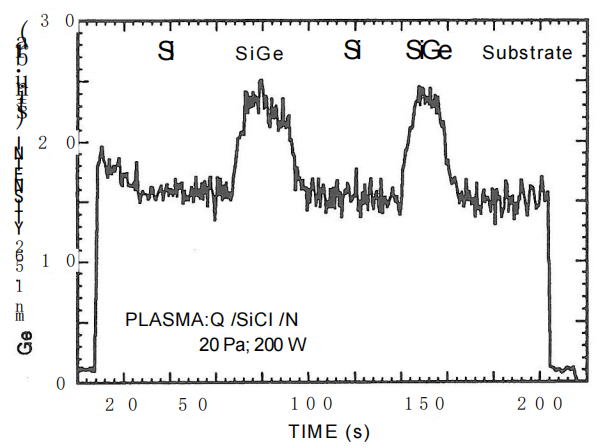

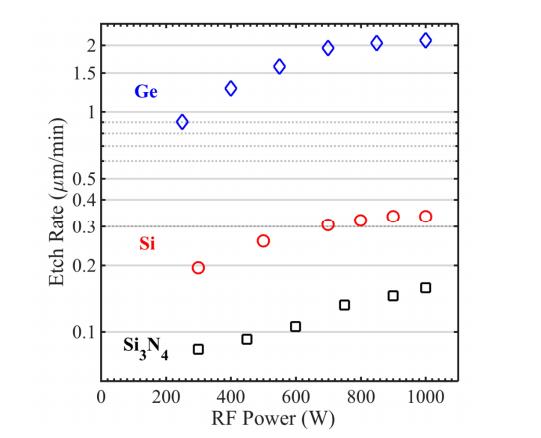

86 中起着重要的作用。这种制造过程通常需要与埋着的SiGe薄膜接触。与这些埋地区域接触需要蚀刻硅并在薄薄的SiGe层中停止。 因此,为了实现精确的图案转移,我们需要一种可控蚀刻的方法。不幸的是,针对SiGe选择性的RIE技术尚未被发现。幸运的是

2023-12-28 10:39:51 131

131

还有一种情况就是PCB蚀刻参数没有问题,但蚀刻后水洗及烘干不良,造成铜线也处于PCB便面残留的蚀刻液包围中,长时间未处理,也会产生铜线侧蚀过度而甩铜。

2023-12-27 16:24:54 114

114 客户线路设计好过蚀刻线的时候,若铜箔规格变更后而蚀刻参数未变,造成铜箔在蚀刻液中的停留时间过长。因锌本来就是活泼金属类,当LED广告屏PCB上的铜线长时间在蚀刻液中浸泡时,必将导致线路侧蚀过度,造成某些细线路背衬锌层被完全反应掉而与基材脱离,即铜线脱落。

2023-12-26 16:28:43 119

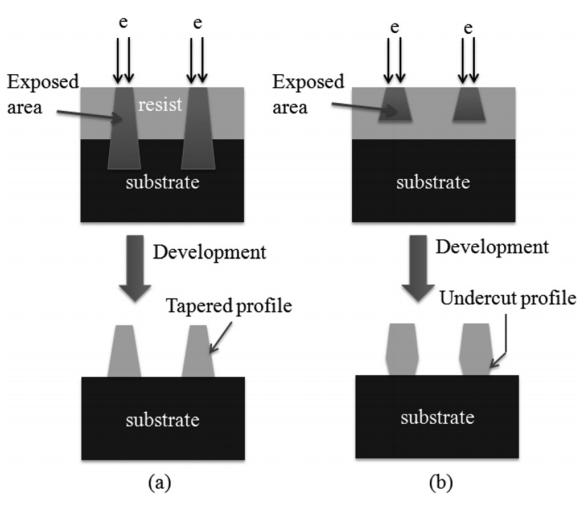

119 光照条件的设置、掩模版设计以及光刻胶工艺等因素对分辨率的影响都反映在k₁因子中,k₁因子也常被用于评估光刻工艺的难度,ASML认为其物理极限在0.25,k₁体现了各家晶圆厂运用光刻技术的水平。

2023-12-18 10:53:05 326

326

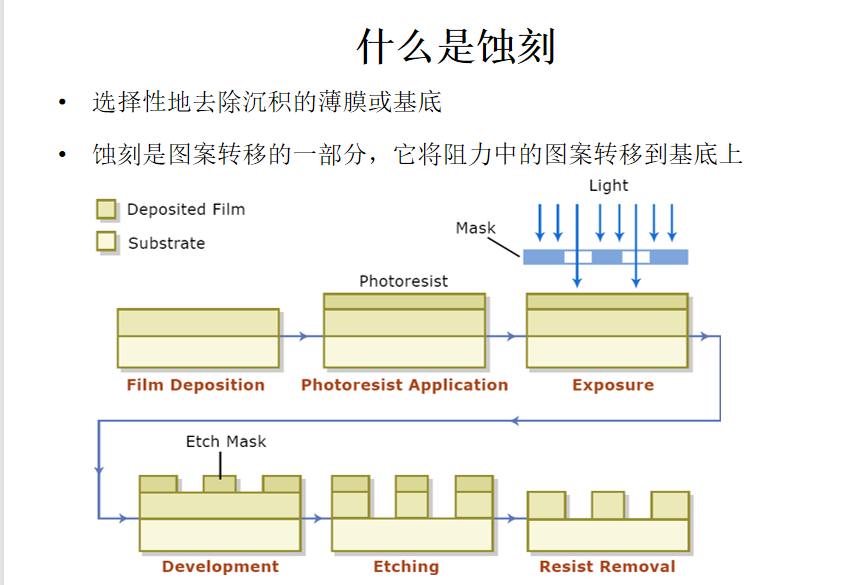

在微电子制造领域,光刻机和蚀刻机是两种不可或缺的重要设备。它们在制造半导体芯片、集成电路等微小器件的过程中发挥着关键作用。然而,尽管它们在功能上有所相似,但在技术原理、应用场景等方面却存在着明显的区别。本文将对光刻机和蚀刻机的差异进行深入探讨。

2023-12-16 11:00:09 371

371

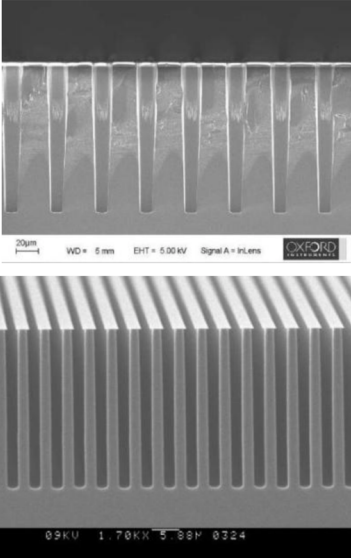

技术提供了典型应用。蚀刻工艺对器件特性有着较大的影响,尤其是在精确控制蚀刻深度和较小化等离子体损伤的情况下影响较大。

2023-12-13 09:51:24 294

294

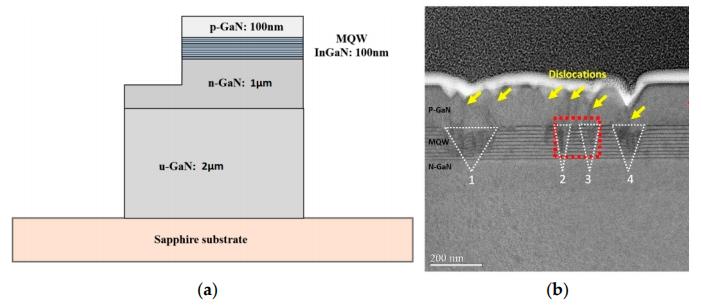

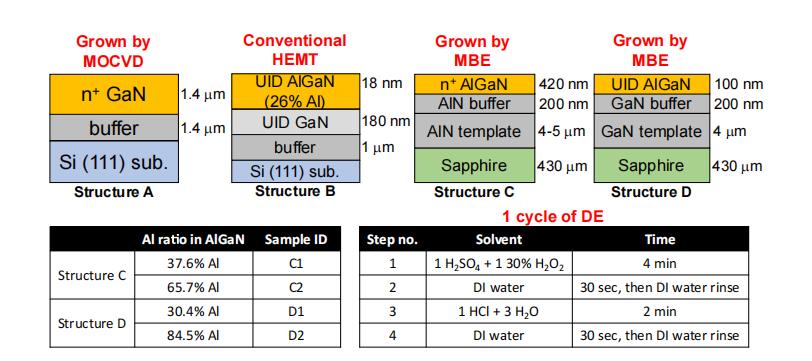

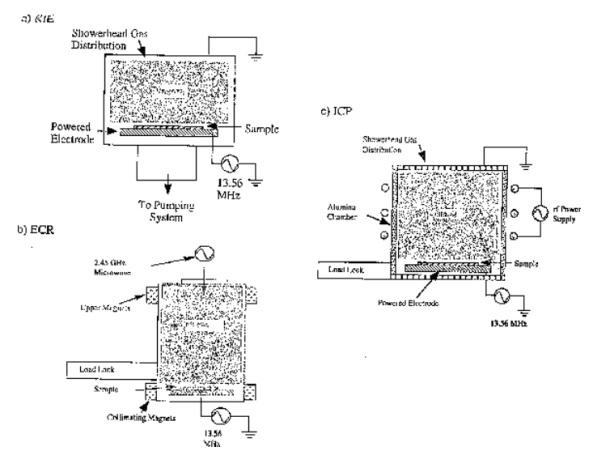

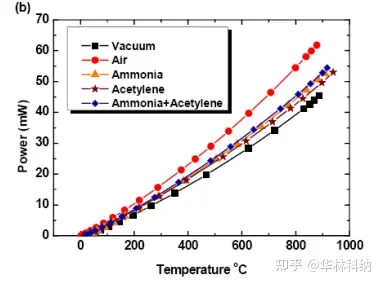

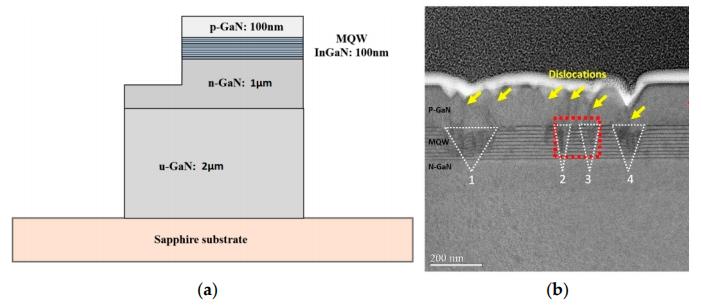

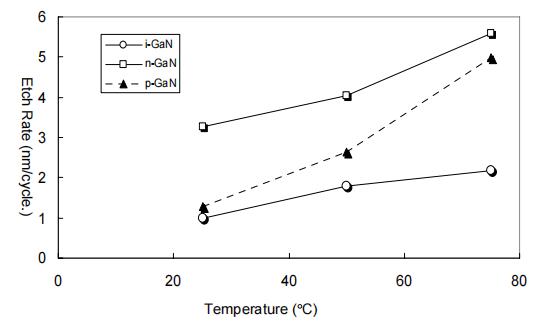

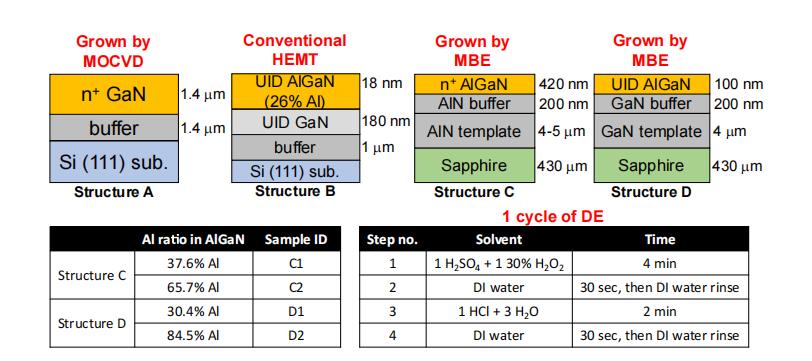

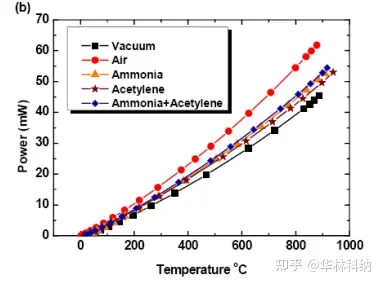

GaN和相关合金由于其优异的特性以及大的带隙、高的击穿电场和高的电子饱和速度而成为有吸引力的材料之一,与优化工艺过程相关的成熟材料是有源/无源射频光电子器件近期发展的关键问题。专用于三元结构的干法蚀刻工艺特别重要,因为这种器件通常包括异质结构。因此,GaN基光电器件的制造部分或全部依赖于干法刻蚀。

2023-12-11 15:04:20 188

188

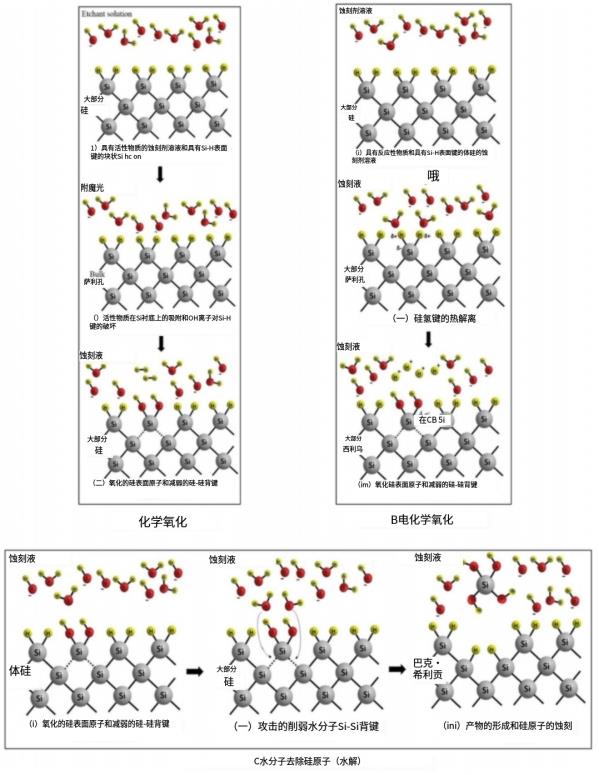

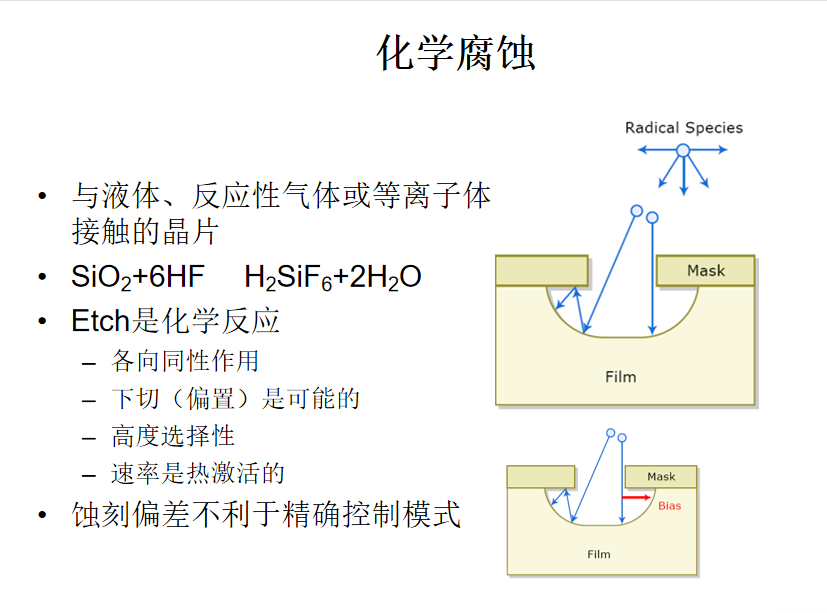

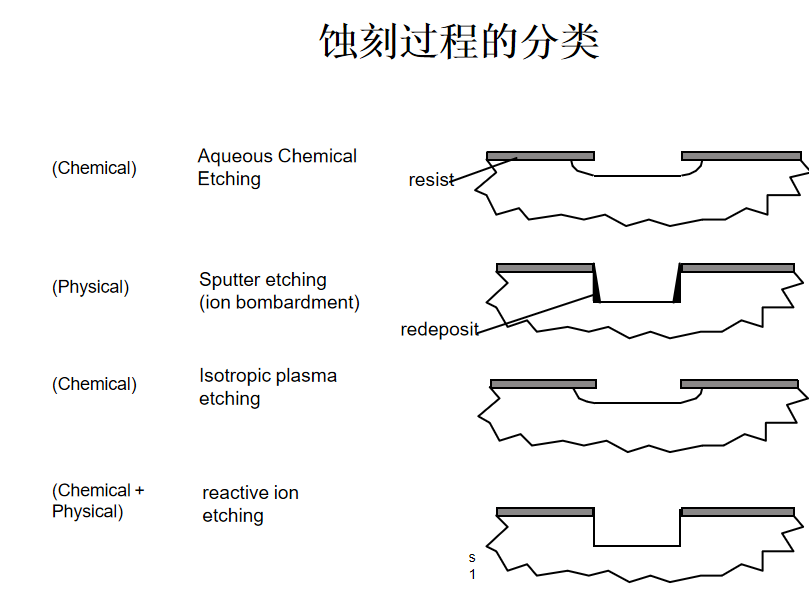

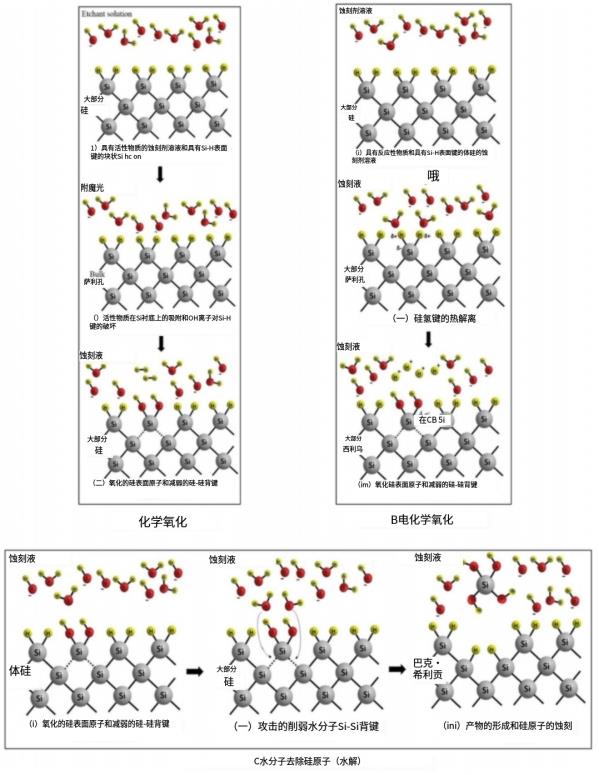

刻蚀的机制,按发生顺序可概分为「反应物接近表面」、「表面氧化」、「表面反应」、「生成物离开表面」等过程。所以整个刻蚀,包含反应物接近、生成物离开的扩散效应,以及化学反应两部分。

2023-12-11 10:24:18 250

250

另外一种工艺方法是整个板子上都镀铜,感光膜以外的部分仅仅是锡或铅锡抗蚀层。这种工艺称为“全板镀铜工艺“。与图形电镀相比,全板镀铜的缺点是板面各处都要镀两次铜而且蚀刻时还必须都把它们腐蚀掉。

2023-12-06 15:03:45 263

263 按工艺要求排放出部分比重高的溶液经分析后补加氯化铵和氨的水溶液,使蚀刻液的比重调整到工艺充许的范围。

2023-12-06 15:01:46 286

286 光刻工艺就是把芯片制作所需要的线路与功能做出来。利用光刻机发出的光通过具有图形的光罩对涂有光刻胶的薄片曝光,光刻胶见光后会发生性质变化,从而使光罩上得图形复印到薄片上,从而使薄片具有电子线路图的作用

2023-12-04 09:17:24 1335

1335

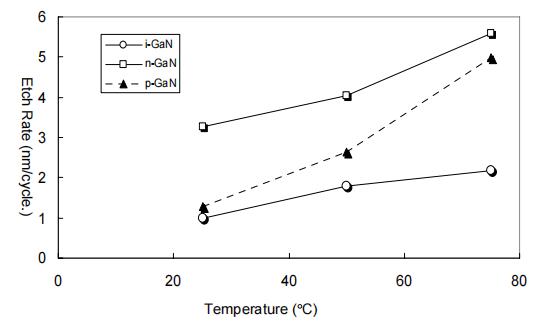

GaN作为宽禁带III-V族化合物半导体最近被深入研究。为了实现GaN基器件的良好性能,GaN的处理技术至关重要。目前英思特已经尝试了许多GaN蚀刻方法,大部分GaN刻蚀是通过等离子体刻蚀来完成

2023-12-01 17:02:39 259

259

三星电子和sk海力士用于tsv蚀刻的设备都是Syndion。synthion是典型的深硅蚀刻设备,深度蚀刻到晶片内部,用于tsv和沟槽等的高度和宽度比的形成。泛林集团 sabre 3d将用于用铜填充蚀刻的晶圆孔来制作线路的tsv线路。

2023-11-30 10:15:57 331

331 由于其独特的材料特性,III族氮化物半导体广泛应用于电力、高频电子和固态照明等领域。加热的四甲基氢氧化铵(TMAH)和KOH3处理的取向相关蚀刻已经被用于去除III族氮化物材料中干法蚀刻引起的损伤,并缩小垂直结构。

2023-11-30 09:01:58 166

166

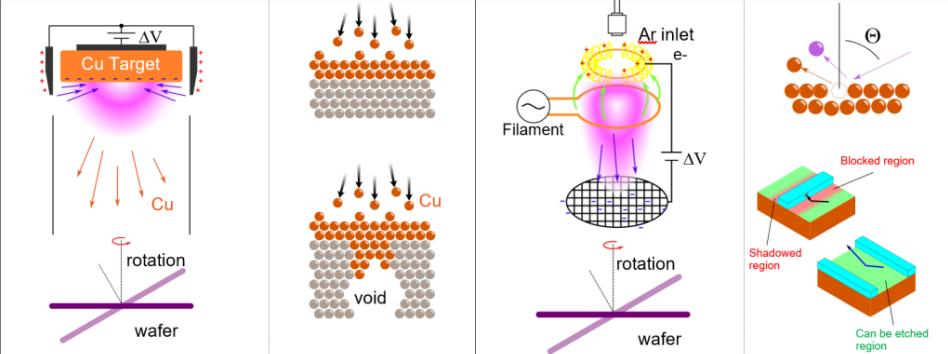

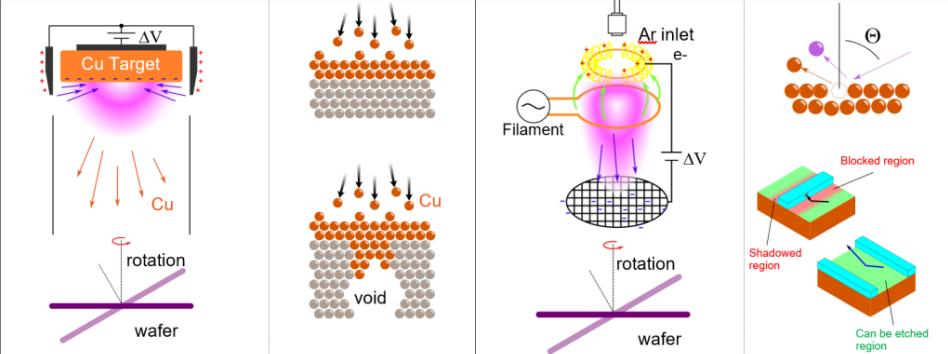

在半导体芯片等器件工艺中,后道制程中的金属连接是经过金属薄膜沉积,图形化和蚀刻工艺,最后在器件元件之间得到导电连接。

2023-11-29 09:15:31 434

434

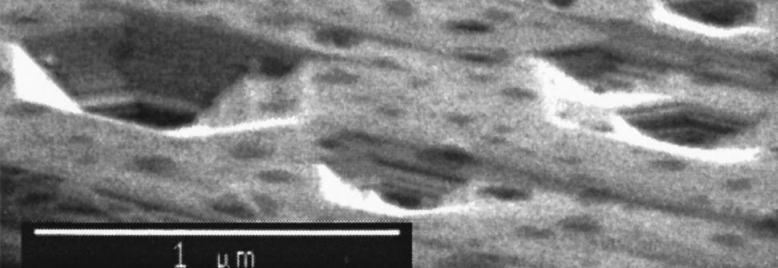

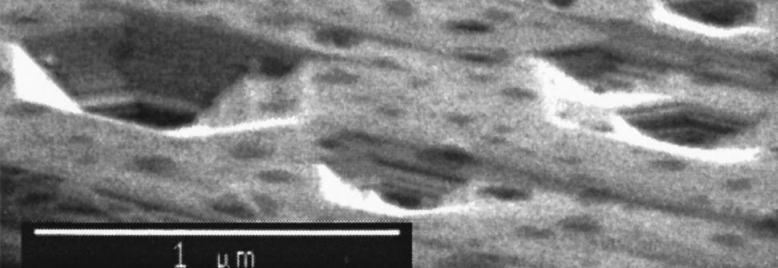

目前,大多数III族氮化物的加工都是通过干法等离子体蚀刻完成的。干法蚀刻有几个缺点,包括产生离子诱导损伤和难以获得激光器所需的光滑蚀刻侧壁。干法蚀刻产生的侧壁典型均方根(rms)粗糙度约为50纳米

2023-11-24 14:10:30 241

241

三星D1a nm LPDDR5X器件的EUV光刻工艺

2023-11-23 18:13:02 579

579

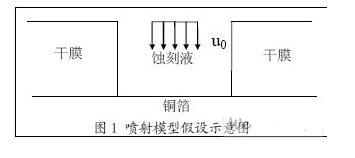

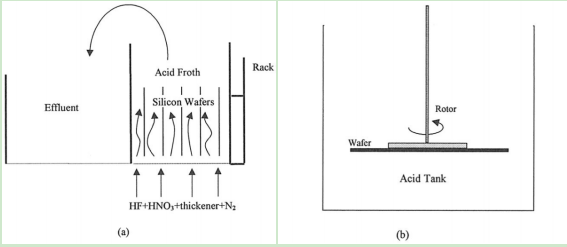

蚀刻设备的结构及不同成分的蚀刻液都会对蚀刻因子或侧蚀度产生影响,或者用乐观的话来说,可以对其进行控制。采用某些添加剂可以降低侧蚀度。这些添加剂的化学成分一般属于商业秘密,各自的研制者是不向外界透露的。至于蚀刻设备的结构问题,后面的章节将专门讨论。

2023-11-14 15:23:10 217

217 自动蚀刻机是利用电解作用或化学反应对金属板进行处理,以获得所需图纹、花纹、几何形状的自动化设备,广泛应用于芯片、数码、航空、机械、标牌等领域中。现有一家蚀刻机设备制造商,要求对全国各地的蚀刻机设

2023-11-08 13:59:52 146

146

近年来,铜(Cu)作为互连材料越来越受欢迎,因为它具有低电阻率、不会形成小丘以及对电迁移(EM)故障的高抵抗力。传统上,化学机械抛光(CMP)方法用于制备铜细线。除了复杂的工艺步骤之外,该方法的一个显著缺点是需要许多对环境不友好的化学品,例如表面活性剂和强氧化剂。

2023-11-08 09:46:21 188

188

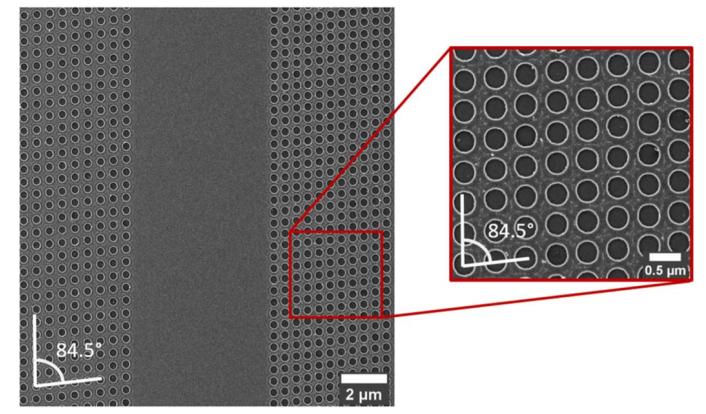

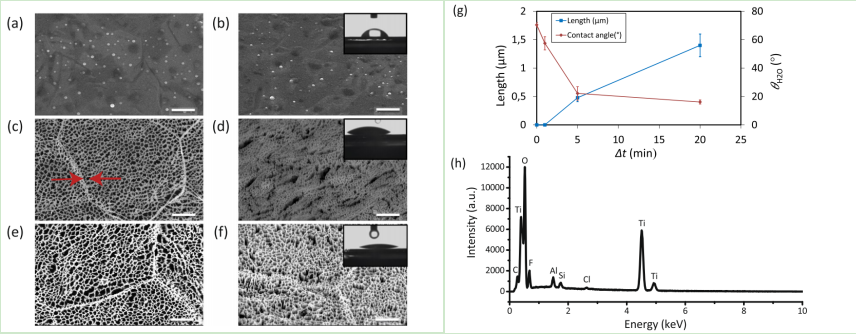

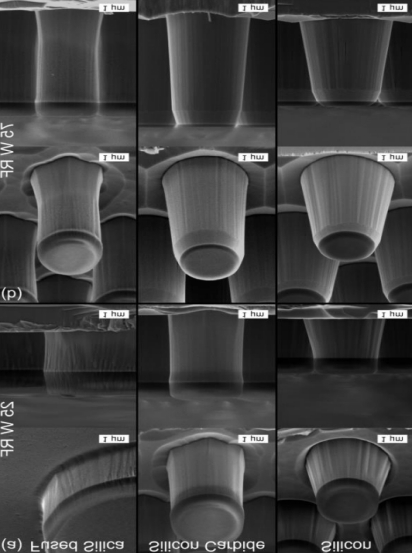

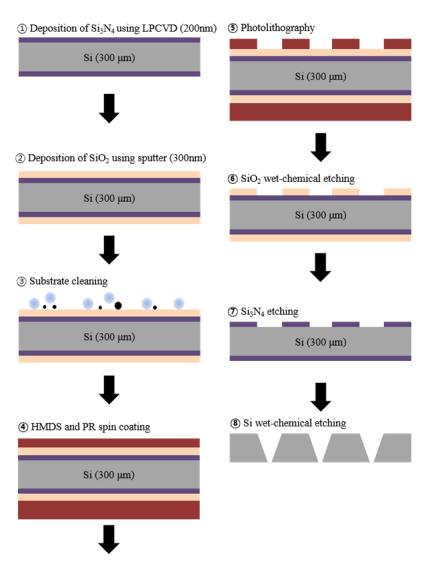

众所周知,微尺度和纳米尺度的地形结构对真核细胞和原核细胞的行为都有显著的影响。例如,具有特殊尺寸的纳米线、纳米柱、纳米管已被证明具有抗菌性能。开发这种结构提供了一种无药物的方法来对抗感染,这被认为是一种替代释放抗菌剂的常见抗菌表面的替代品。

2023-10-23 09:43:16 136

136

干法蚀刻(dry etch)工艺通常由四个基本状态构成:蚀刻前(before etch),部分蚀刻(partial etch),蚀刻到位(just etch),过度蚀刻(over etch),主要表征有蚀刻速率,选择比,关键尺寸,均匀性,终点探测。

2023-10-18 09:53:19 788

788

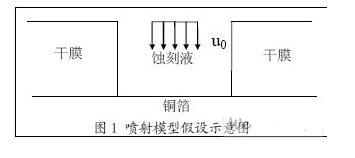

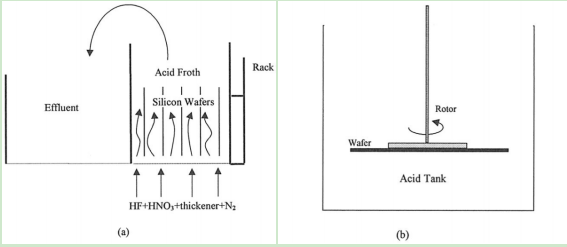

在精细印制电路制作过程中,喷淋蚀刻是影响产品质量合格率重要的工序之一。现有很多的文章对精细线路的蚀刻做了大量的研究,但是大多数都只停留在表象的研究中,并没有从本质上认识喷淋蚀刻中出现的问题。

2023-10-17 15:15:35 164

164

蚀刻液的化学成分的组成:蚀刻液的化学组分不同,其蚀刻速率就不相同,蚀刻系数也不同。如普遍使用的酸性氯化铜蚀刻液的蚀刻系数通常是&;碱性氯化铜蚀刻液系数可达3.5-4。而正处在开发阶段的以硝酸为主的蚀刻液可以达到几乎没有侧蚀问题,蚀刻后的导线侧壁接近垂直。

2023-10-16 15:04:35 553

553 据悉,东京电子新技术的目标是能够长时间储存数据的3d nand闪存。该公司开发了一种新的通道孔蚀刻方法,该方法是将垂直孔快速深插入存储单元。3D nand的存储器容量可以通过将存储器单元层垂直堆积来增加,如果层数增加,就需要性能更高的装置。

2023-10-16 14:39:49 368

368 氮化镓(GaN)具有六方纤锌矿结构,直接带隙约为3.4eV,目前已成为实现蓝光发光二极管(led)的主导材料。由于GaN的高化学稳定性,在室温下用湿法化学蚀刻来蚀刻或图案化GaN是非常困难的。与湿法

2023-10-12 14:11:32 244

244

GaN及相关合金可用于制造蓝色/绿色/紫外线发射器以及高温、高功率电子器件。由于 III 族氮化物的湿法化学蚀刻结果有限,因此人们投入了大量精力来开发干法蚀刻工艺。干法蚀刻开发一开始集中于台面结构,其中需要高蚀刻速率、各向异性轮廓、光滑侧壁和不同材料的同等蚀刻。

2023-10-07 15:43:56 319

319

铜的电阻率取决于其晶体结构、空隙体积、晶界和材料界面失配,这在较小的尺度上变得更加重要。传统上,铜(Cu)线的形成是通过使用沟槽蚀刻工艺在低k二氧化硅中蚀刻沟槽图案,然后通过镶嵌流用Cu填充沟槽来完成的。

2023-09-22 09:57:23 281

281

4层蓝牙产品PCB设计素材

2023-09-20 07:43:16

一站式PCBA智造厂家今天为大家讲讲pcb打样蚀刻工艺注意事项有哪些?PCB打样蚀刻工艺注意事项。PCB打样中,在铜箔部分预镀一层铅锡防腐层,保留在板外层,即电路的图形部分,然后是其余的铜箔被化学方法腐蚀,称为蚀刻。

2023-09-18 11:06:30 670

670 随着技术的发展,与ic制造相关的排放量也增加了,特别是光刻和蚀刻能耗较大,例如n3工程中光刻工序产生的二氧化碳排放量约占45%。imec的工程师们半导体制造过程中产生的尾气可以建模软件平台开发,可持续半导体技术及系统计划(ssts)的使用率

2023-09-13 10:56:53 290

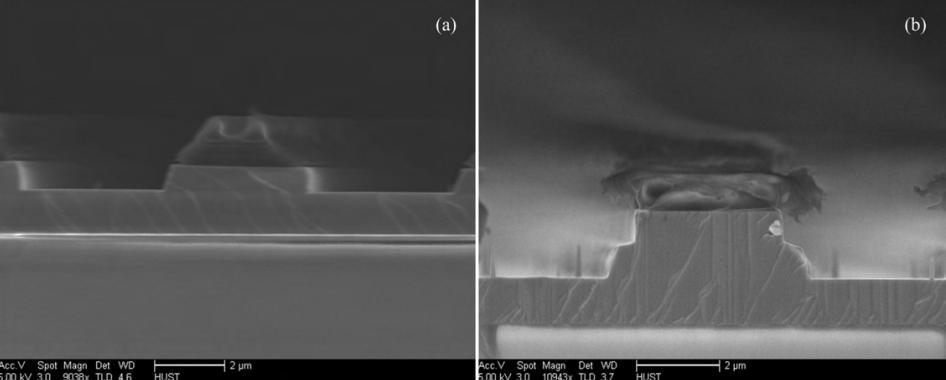

290 要注意的是,蚀刻时的板子上面有两层铜。在外层蚀刻工艺中仅仅有一层铜是必须被全部蚀刻掉的,其余的将形成最终所需要的电路。这种类型的图形电镀,其特点是镀铜层仅存在于铅锡抗蚀层的下面。

2023-09-07 14:41:12 474

474

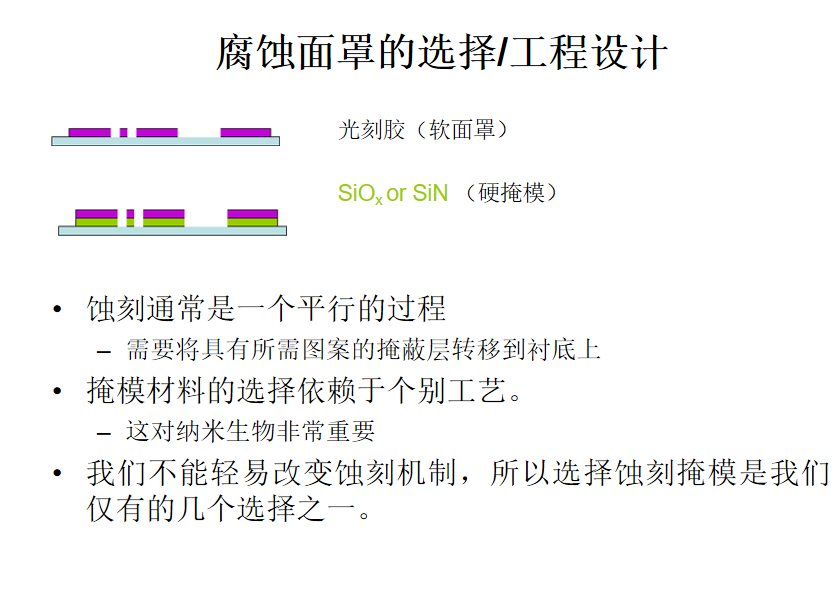

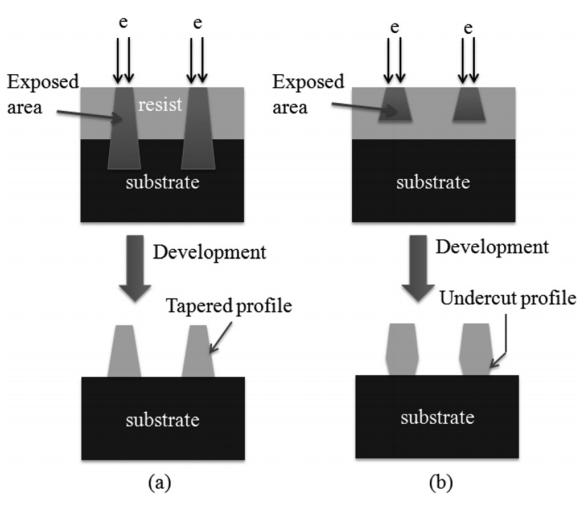

直接蚀刻和剥离是两种比较流行的图案转移工艺。在直接蚀刻工艺中,首先使用光刻技术对聚合物抗蚀剂进行构图,然后通过干法蚀刻技术用抗蚀剂作为掩模将图案转移到衬底或子层上。

2023-09-07 09:57:14 292

292

在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺中的蚀刻。

2023-09-06 09:36:57 811

811

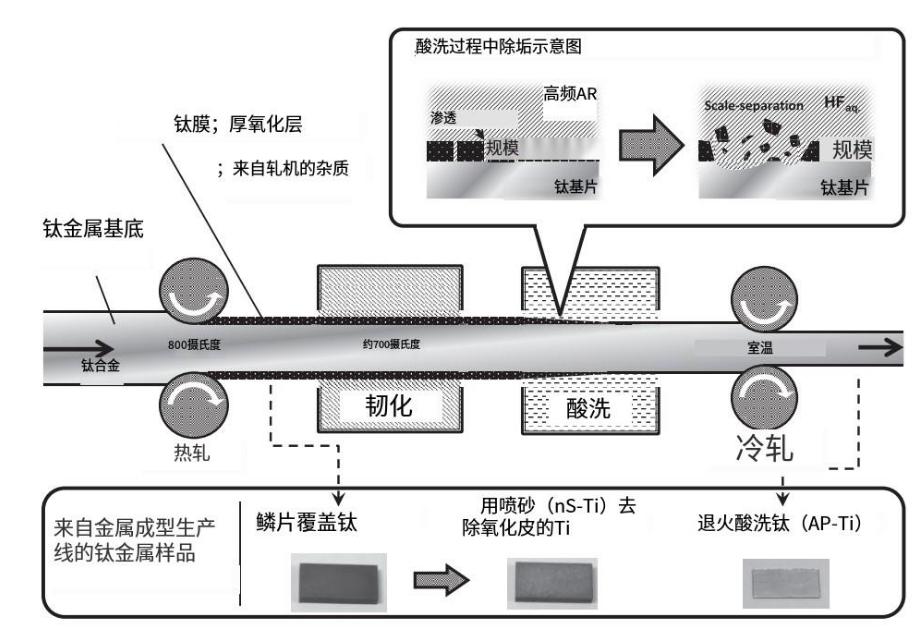

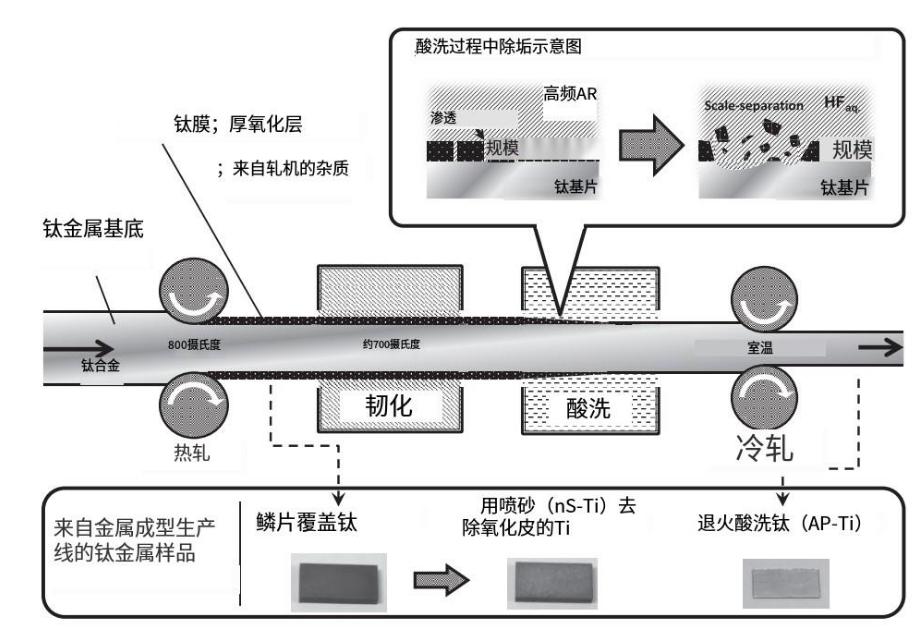

钛金属具有较高的比强度和生物相容性,并且由于在金属表面自发形成的钝化膜而具有优异的抗蚀刻性。这种薄氧化膜在空气中容易形成,保护内部活性钛金属免受侵蚀性介质的影响。二氧化钛具有很宽的带隙,因此钛经常被用于各种应用,包括光催化剂、化学传感器和医疗植入物。

2023-09-01 10:18:07 187

187

集成电路按照实现工艺分类可以分为哪些? 集成电路 (Integrated Circuit,简称IC) 是一种半导体器件,通过将许多电子元器件集成在单一的芯片上,实现了高度的集成度和电路的升级

2023-08-29 16:28:55 1707

1707 半导体制造工艺之光刻工艺详解

2023-08-24 10:38:54 1221

1221

光刻是半导体芯片生产流程中最复杂、最关键的工艺步骤,耗时长、成本高。半导体芯片生产的难点和关键点在于将电路图从掩模上转移至硅片上,这一过程通过光刻来实现, 光刻的工艺水平直接决定芯片的制程水平和性能水平。

2023-08-23 10:47:53 1586

1586

我们华林科纳通过光学反射光谱半实时地原位监测用有机碱性溶液的湿法蚀刻,以实现用于线波导的氢化非晶硅(a-Si:H)膜的高分辨率厚度控制。由a-Si:H的本征各向同性结构产生的各向同性蚀刻导致表面

2023-08-22 16:06:56 239

239

下料磨边→钻孔→沉铜加厚→外层图形→镀锡、蚀刻退锡→二次钻孔→检验→丝印阻焊→镀金插头→热风整平→丝印字符→外形加工→测试→检验

2023-08-18 14:25:02 345

345 ,内层线路加工是把需要的图形用干膜或湿膜保护起来,将不需要留下来的铜箔用酸性药水蚀刻掉。

现有线路板上线路的线宽/间距一般都是一次性曝光-蚀刻形成的,由于化学蚀刻过程中的水池效应,致使金属线路产生侧蚀

2023-08-18 10:08:02

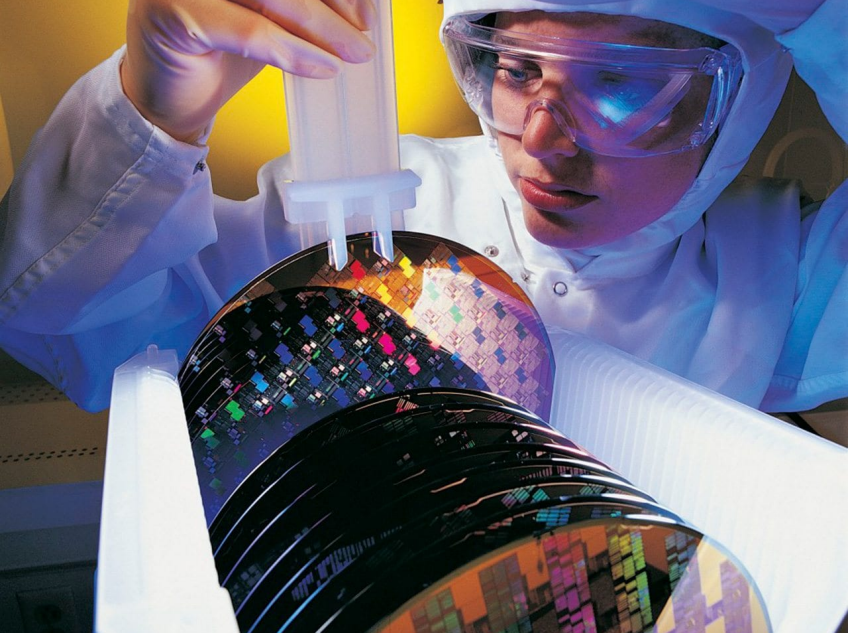

半导体蚀刻设备是半导体製造过程中使用的设备。 化学溶液通过将晶片浸入化学溶液(蚀刻剂)中来选择性地去除半导体晶片的特定层或区域,化学溶液溶解并去除晶片表面所需的材料。

2023-08-15 15:51:58 319

319 PCB蚀刻工艺中的“水池效应”现象,通常发生在顶部,这种现象会导致大尺寸PCB整个板面具有不同的蚀刻质量。

2023-08-10 18:25:43 1013

1013 刻蚀和蚀刻实质上是同一过程的不同称呼,常常用来描述在材料表面上进行化学或物理腐蚀以去除或改变材料的特定部分的过程。在半导体制造中,这个过程常常用于雕刻芯片上的细微结构。

2023-07-28 15:16:59 4140

4140 来源:半导体芯科技编译 干法等离子蚀刻工艺中的污染最小。 Greene Tweed推出了全氟弹性体Chemraz G57,由Greene Tweed材料科学家和应用工程师专门研发,用来满足侵蚀性干法

2023-07-19 16:32:11 222

222 电解提铜过程中,阳极区的氢离子会透过阳离子膜迁移到阳极区中,使药水酸度增加,正好可以补充蚀刻过程中药水酸度的损耗,使蚀刻液可以不断循环使用。

2023-07-18 15:01:43 383

383 蚀刻是一种从材料上去除的过程。基片表面上的一种薄膜基片。当掩码层用于保护特定区域时在晶片表面,蚀刻的目的是“精确”移除未覆盖的材料戴着面具。

2023-07-14 11:13:32 183

183

蚀刻是一种从材料上去除的过程。基片表面上的一种薄膜基片。当掩码层用于保护特定区域时在晶片表面,蚀刻的目的是“精确”移除未覆盖的材料戴着面具。

2023-07-12 09:26:03 190

190

在之前的文章里,我们介绍了晶圆制造、氧化过程和集成电路的部分发展史。现在,让我们继续了解光刻工艺,通过该过程将电子电路图形转移到晶圆上。光刻过程与使用胶片相机拍照非常相似。但是具体是怎么实现的呢?

2023-06-28 10:07:47 2427

2427

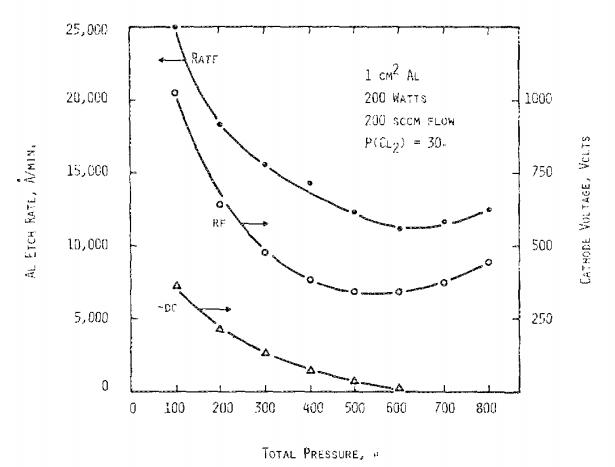

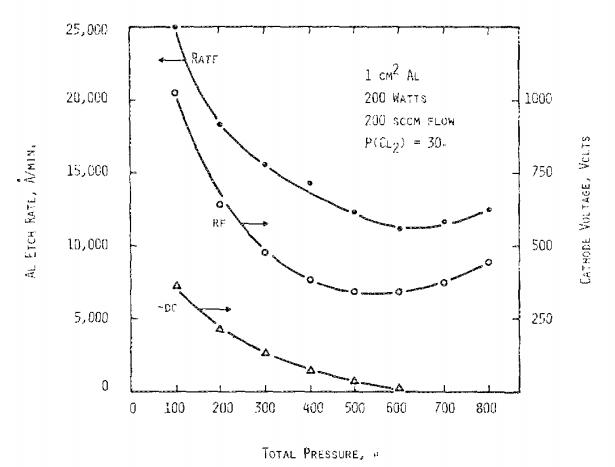

随着集成电路互连线的宽度和间距接近3pm,铝和铝合金的等离子体蚀刻变得更有必要。为了防止蚀刻掩模下的横向蚀刻,我们需要一个侧壁钝化机制。尽管AlCl和AlBr都具有可观的蒸气压,但大多数铝蚀刻的研究

2023-06-27 13:24:11 318

318

在介绍日本电子公司研发的全新蚀刻技术之前,我们需要了解蚀刻技术的历史。蚀刻技术是芯片制造基础工艺之一,它是指对光刻技术制作的图案进行蚀刻,得到具有一定几何形状和结构的微细孔洞和凹坑的工艺。

2023-06-26 15:58:18 897

897

CMOS和MEMS制造技术,允许相对于其他薄膜选择性地去除薄膜,在器件集成中一直具有很高的实用性。这种化学性质非常有用,但是当存在其他材料并且也已知在HF中蚀刻时,这就成了问题。由于器件的静摩擦、缓慢的蚀刻速率以及横向或分层膜的蚀刻速率降低,湿法化学也会有问题。

2023-06-26 13:32:44 1053

1053

,我们可以看到,本质上阻抗偏差与材料及加工过程有关。板材来料本身偏差、线路蚀刻偏差、层压带来的流胶率偏差,以及铜箔表面粗糙度、PP玻纤效应、介质的DF频变效应等都会对阻抗公差有影响。

一、覆铜板的来料

2023-06-25 10:25:55

,我们可以看到,本质上阻抗偏差与材料及加工过程有关。板材来料本身偏差、线路蚀刻偏差、层压带来的流胶率偏差,以及铜箔表面粗糙度、PP玻纤效应、介质的DF频变效应等都会对阻抗公差有影响。

一、覆铜板的来料

2023-06-25 09:57:07

上海伯东日本 Atonarp Aston™ Impact 和 Aston™ Plasma 是超紧凑型质谱仪, 适用于先进半导体工艺(如沉积和蚀刻)所需的定量气体分析.

2023-06-21 10:21:08 197

197

3D NAND 工艺通过堆叠存储单元, 提供更高的比特密度, 上海伯东日本 Atonarp Aston™ 质谱分析仪适用于先进半导体工艺(如沉积和蚀刻)所需的定量气体分析. 沉积应用中: 实时过程

2023-06-21 10:09:13 197

197

上海伯东日本 Aston™ 质谱仪能够进行准确且可操作的端点检测, OA% 是传统 OES 计量解决方案的一个数量级(1/10). Aston™ 质谱仪解决方案适用于具有高蚀刻吞吐量和大量重复相同

2023-06-20 17:28:31 258

258

上海伯东代理日本 Atonarp 过程控制质谱仪 Aston™ 为半导体生产而设计, 作为一个强大的平台, Aston™ 可以取代多种传统工具, 提供半导体制程中 ALD, CVD, 蚀刻, ALE

2023-06-20 17:18:12 231

231

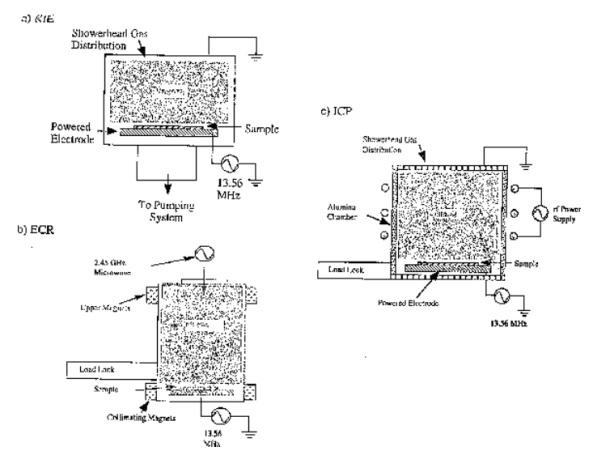

在干法蚀刻中,气体受高频(主要为 13.56 MHz 或 2.45 GHz)激发。在 1 到 100 Pa 的压力下,其平均自由程为几毫米到几厘米。

2023-06-20 09:49:16 3689

3689

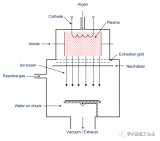

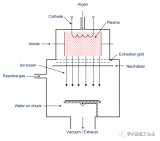

离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对

2023-06-20 09:48:56 3989

3989

均匀性(1 σ)达到 离子束刻蚀属于干法刻蚀, 其核心部件为离子源. 作为蚀刻机的核心部件, KRi 射频离子源提供大尺寸, 高能量, 低浓度的宽束离子束, 接受客户定制, 单次工艺时间更长, 满足

2023-06-15 14:58:47 665

665

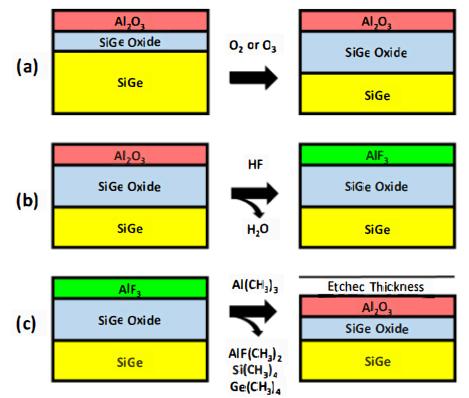

器件尺寸的不断缩小促使半导体工业开发先进的工艺技术。近年来,原子层沉积(ALD)和原子层蚀刻(ALE)已经成为小型化的重要加工技术。ALD是一种沉积技术,它基于连续的、自限性的表面反应。ALE是一种蚀刻技术,允许以逐层的方式从表面去除材料。ALE可以基于利用表面改性和去除步骤的等离子体或热连续反应。

2023-06-15 11:05:05 526

526

为了提供更优良的静电完整性,三维(3D)设计(如全围栅(GAA)场电子晶体管(FET ))预计将在互补金属氧化物半导体技术中被采用。3D MOS架构为蚀刻应用带来了一系列挑战。虽然平面设备更多地依赖于各向异性蚀刻,但是3D设备在不同材料之间具有高选择性,需要更多的各向异性蚀刻能力。

2023-06-14 11:03:53 1779

1779

凸块制造过程一般是基于定制的光掩模,通过真空溅镀、黄光、电镀、蚀刻等环节而成,该技术是晶圆制造环节的延伸,也是实施倒装(FC)封装工艺的基础及前提。

2023-06-12 09:35:42 771

771

:线路电镀和全板镀铜,现叙述如下。 1、线路电镀 该工艺中只在设计有电路图形和通孔的地方接受铜层的生成和蚀刻阻剂金属电镀。在线路电镀过程中,线路和焊垫每一侧增加的宽度与电镀表面增加的厚度大体相当,因此

2023-06-09 14:19:07

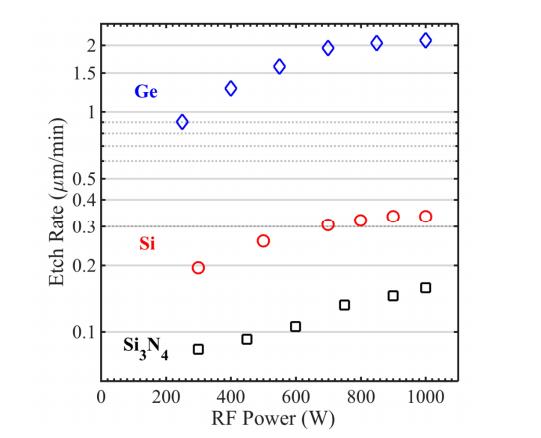

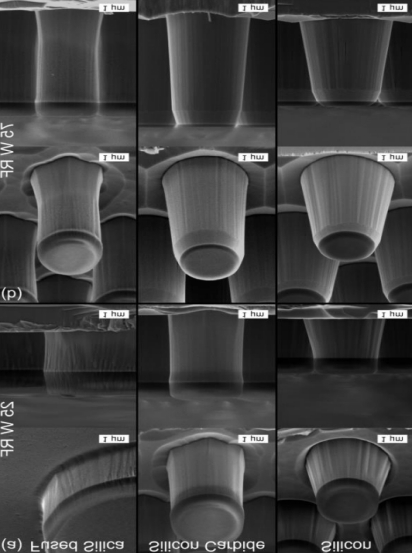

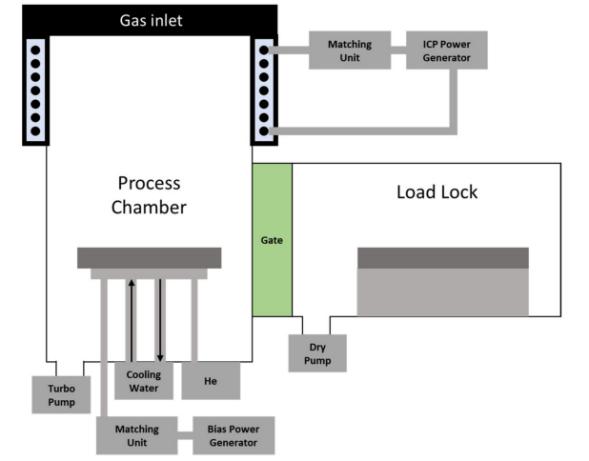

等离子体蚀刻是氮化镓器件制造的一个必要步骤,然而,载体材料的选择可能会实质上改变蚀刻特性。在小型单个芯片上制造氮化镓(GaN)设备,通常会导致晶圆的成本上升。在本研究中,英思特通过铝基和硅基载流子来研究蚀刻过程中蚀刻速率、选择性、形貌和表面钝化的影响。

2023-05-30 15:19:54 452

452

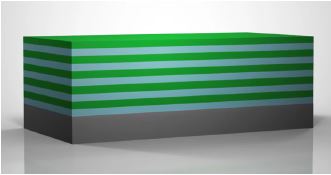

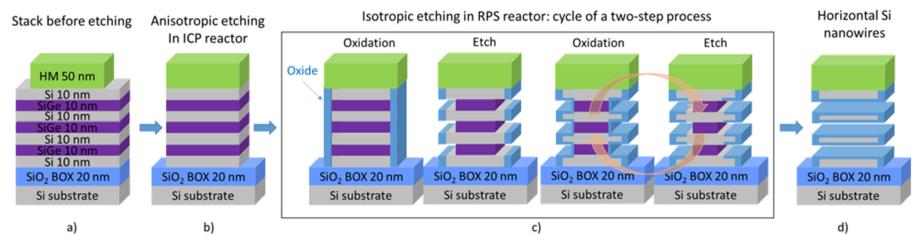

纳米片工艺流程中最关键的蚀刻步骤包括虚拟栅极蚀刻、各向异性柱蚀刻、各向同性间隔蚀刻和通道释放步骤。通过硅和 SiGe 交替层的剖面蚀刻是各向异性的,并使用氟化化学。优化内部间隔蚀刻(压痕)和通道释放步骤,以极低的硅损失去除 SiGe。

2023-05-30 15:14:11 1071

1071

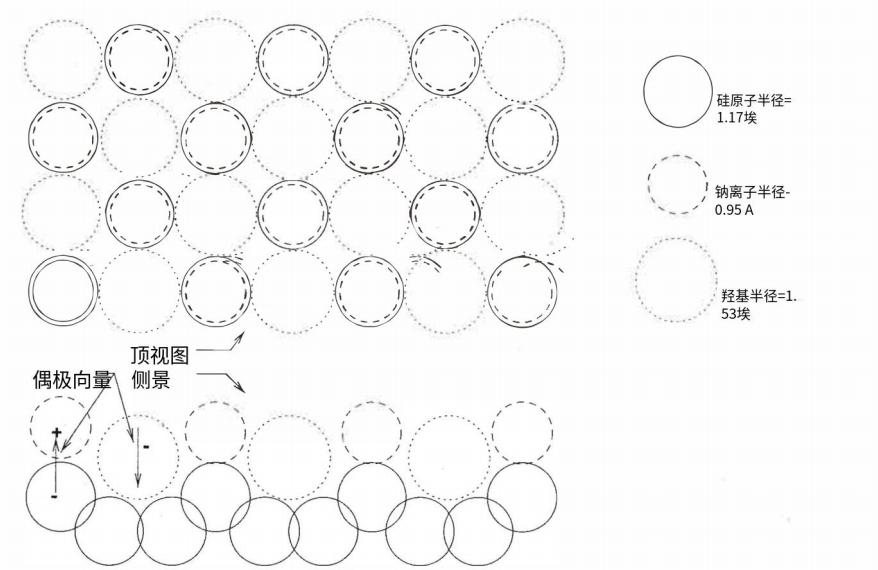

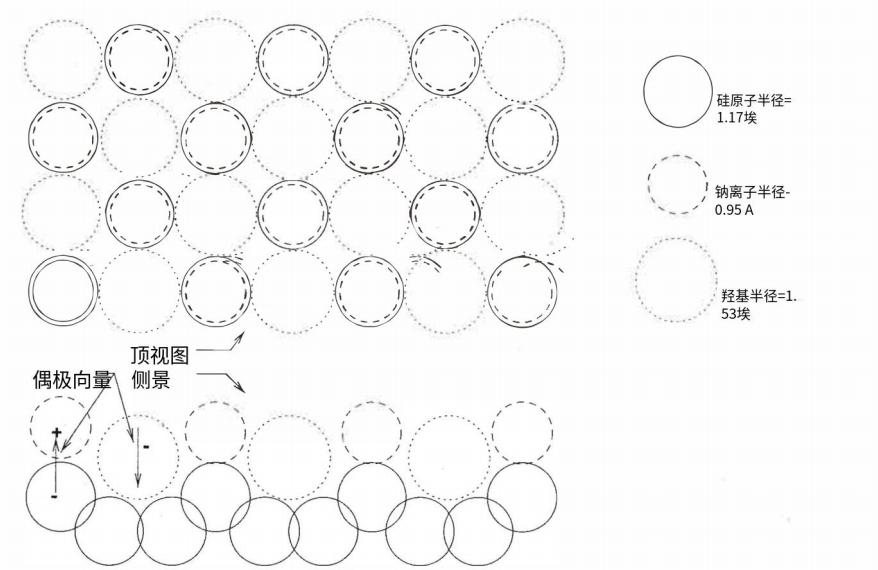

过去利用碱氢氧化物水溶液研究了硅的取向依赖蚀刻,这是制造硅中微结构的一种非常有用的技术。以10M氢氧化钾(KOH)为蚀刻剂,研究了单晶硅球和晶片的各向异性蚀刻过程,测量了沿多个矢量方向的蚀刻速率,用单晶球发现了最慢的蚀刻面。英思特利用这些数据,提出了一种预测不同方向表面的倾角的方法

2023-05-29 09:42:40 618

618

微孔利用光和物质的相互作用来获得独特的性质,特别是,当用紫外光、可见光或近红外光在其表面等离子体极化频率附近照射时,金属微孔结构表现出强烈的共振。然而,用于制造微孔的技术是耗时的,并且需要昂贵的设备和专业人员。因此,英思特开发了一种通过湿化学蚀刻硅衬底来制造微孔的方法。

2023-05-25 13:47:51 846

846

蚀刻可能是湿制程阶段最复杂的工艺,因为有很多因素会影响蚀刻速率。如果不保持这些因素的稳定,蚀刻率就会变化,因而影响产品质量。如果希望利用一种自动化方法来维护蚀刻化学,以下是你需要理解的基本概念。

2023-05-19 10:27:31 575

575

微电子机械系统(MEMS)是将机械元件和电子电路集成在一个共同的基板上,通过使用微量制造技术来实现尺寸从小于一微米到几微米的高性能器件。由于现有的表面加工技术,目前大多数的MEMS器件都是基于硅的。

2023-05-19 10:19:26 352

352 一般适用于多层印制板的外层电路图形的制作或微波印制板阴板法直接蚀刻图形的制作抗蚀刻 图形电镀之金属抗蚀层如镀覆金、镍、锡铅合金

2023-05-18 16:23:48 4918

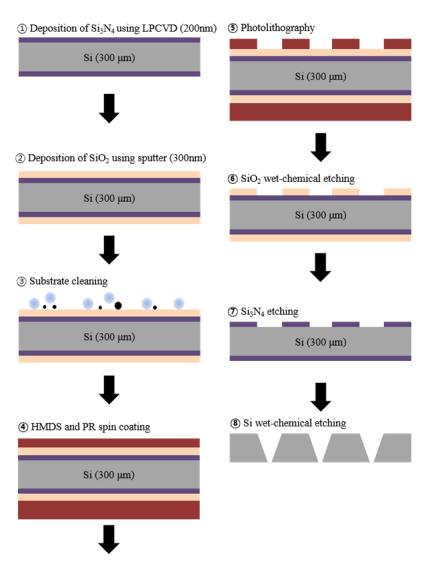

4918 蚀刻是微结构制造中采用的主要工艺之一。它分为两类:湿法蚀刻和干法蚀刻,湿法蚀刻进一步细分为两部分,即各向异性和各向同性蚀刻。硅湿法各向异性蚀刻广泛用于制造微机电系统(MEMS)的硅体微加工和太阳能电池应用的表面纹理化。

2023-05-18 09:13:12 700

700

抛光硅晶片是通过各种机械和化学工艺制备的。首先,硅单晶锭被切成圆盘(晶片),然后是一个称为拍打的扁平过程,包括使用磨料清洗晶片。通过蚀刻消除了以往成形过程中引起的机械损伤,蚀刻之后是各种单元操作,如抛光和清洗之前,它已经准备好为设备制造。

2023-05-16 10:03:00 584

584

减薄晶片有四种主要方法,(1)机械研磨,(2)化学机械平面化,(3)湿法蚀刻(4)等离子体干法化学蚀刻(ADP DCE)。四种晶片减薄技术由两组组成:研磨和蚀刻。为了研磨晶片,将砂轮和水或化学浆液结合起来与晶片反应并使之变薄,而蚀刻则使用化学物质来使基板变薄。

2023-05-09 10:20:06 979

979 其实不同颜色的PCB,它们的制造的材料、制造工序都是一样的,包括敷铜层的位置也是一样的,经过蚀刻工艺后就在PCB上留下了最终的布线,例如下图这块刚经过蚀刻工艺的PCB,敷铜走线就是原本的铜色,而PCB基板略显微黄色。

2023-05-09 10:02:43 1699

1699

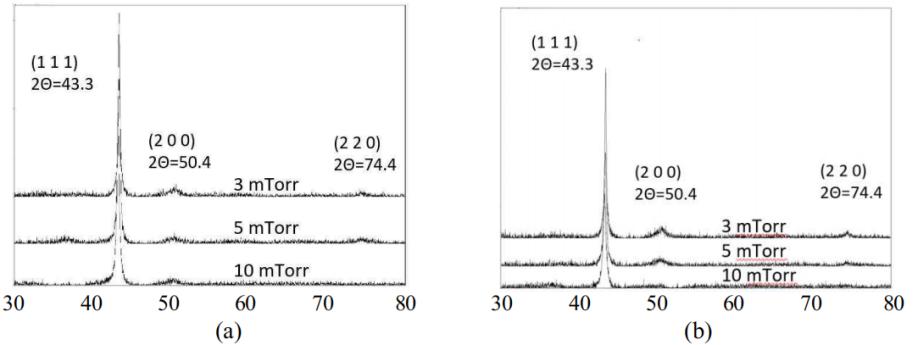

书籍:《炬丰科技-半导体工艺》 文章:单晶的湿法蚀刻和红外吸收 编号:JFKJ-21-206 作者:炬丰科技 摘要 采用湿法腐蚀、x射线衍射和红外吸收等方法研究了物理气相色谱法生长AlN单晶的缺陷

2023-04-23 11:15:00 118

118 PCB对准图。 为了实现所有胶片的完美对准,应在所有胶片上打上定位孔。孔的精确度可通过调节胶片所在的工作台来实现。当工作台的微小校准导致最佳匹配时,就打孔。这些孔将在成像过程的下一步中装入定位销

2023-04-21 15:55:18

的保护膜,使用贴膜机把感光胶膜贴在覆铜板上。 (4)蚀刻 蚀刻也称烂板。是生产过程的一个重要环节,它的成败关系到印制电路板的后续工序。它是利用化学方法除去板上不需要的铜箔,留下组成图形的焊盘、印制

2023-04-20 15:25:28

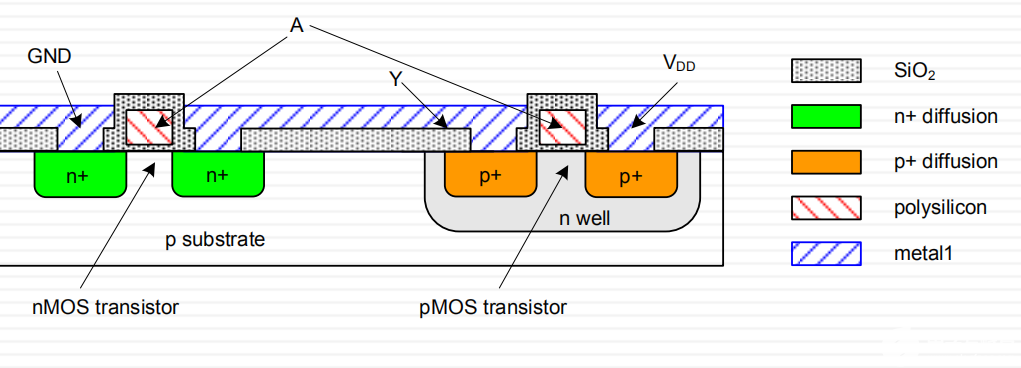

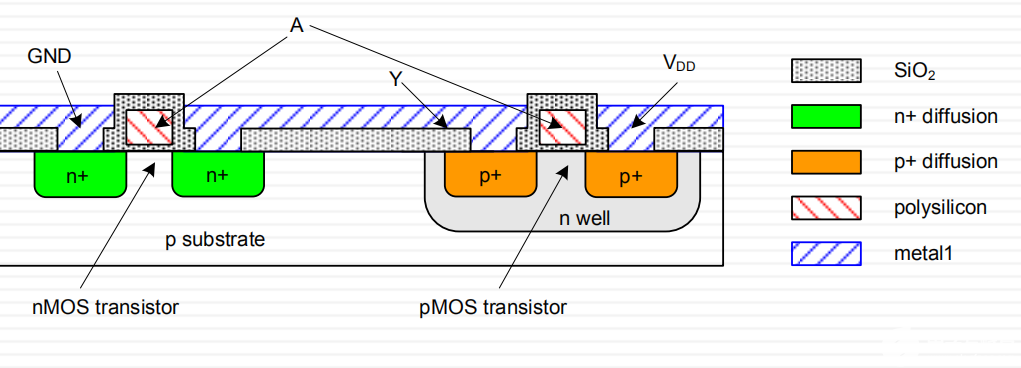

半导体工艺 1.CMOS晶体管是在硅片上制造的 2.平版印刷的过程类似于印刷机 3.每一步,不同的材料被存放或蚀刻 4.通过查看顶部和顶部最容易理解文章全部详情:壹叁叁伍捌零陆肆叁叁叁简化制造中的晶圆截面的过程 逆变器截面 要求pMOS晶体管的机身 逆变器掩模组 晶体管

2023-04-20 11:16:00 247

247

反应离子蚀刻 (RIE)是一种干法蚀刻工艺,与半导体工业中使用的互补金属氧化物半导体(CMOS)方法兼容。

2023-04-14 14:26:16 1253

1253

新的High NA EUV 光刻胶不能在封闭的研究环境中开发,必须通过精心设计的底层、新型硬掩模和高选择性蚀刻工艺进行优化以获得最佳性能。为了迎接这一挑战,imec 最近开发了一个新的工具箱来匹配光刻胶和底层的属性。

2023-04-13 11:52:12 1164

1164 干法蚀刻与湿法蚀刻之间的争论是微电子制造商在项目开始时必须解决的首要问题之一。必须考虑许多因素来决定应在晶圆上使用哪种类型的蚀刻剂来制作电子芯片,是液体(湿法蚀刻)还是气体(干法蚀刻)

2023-04-12 14:54:33 1004

1004 湿法蚀刻工艺的原理是使用化学溶液将固体材料转化为液体化合物。选择性非常高

2023-04-10 17:26:10 453

453

半导体行业的许多工艺步骤都会排放有害废气。对于使用非常活泼的气体的化学气相沉积或干法蚀刻,所谓的靠近源头的废气使用点处理是常见的做法。相比之下,对于湿法化学工艺,使用中央湿式洗涤器处理废气是一种公认

2023-04-06 09:26:48 408

408

了革命性的变化,这种布局完全不同于90nm节点。从45nm节点后,双重图形化技术已经应用在栅图形化工艺中。随着技术节点的继续缩小,MOSFET栅极关键尺寸CD继续缩小遇到了困难,IC设计人员开始减少栅极之间的间距。

2023-04-03 09:39:40 2452

2452 经过多年的研发,随着该行业在内存和逻辑方面面临新的挑战,一种称为低温蚀刻的技术正在重新出现,成为一种可能的生产选择。

2023-03-29 10:14:41 392

392

印刷线路板从光板到显出线路图形的过程是一个比较复杂的物理和化学反应的过程,本文就对其最后的一步--蚀刻进行解析。目前,印刷电路板(PCB)加工的典型工艺采用"图形电镀法"。即先在

2023-03-29 10:04:07 886

886 研究表明,半导体的物理特性会根据其结构而变化,因此半导体晶圆在组装成芯片之前被蚀刻成可调整其电气和光学特性以及连接性的结构。

2023-03-28 09:58:34 251

251

6-16um之间,最终加上二次电镀的铜厚,外层成品铜厚大概在26-36um之间。外层铜越厚,线路蚀刻时向下蚀刻时间长,对线路左右的侧蚀量大,导致线路变细或断掉开路。外层线路加工流程:外层线路蚀刻的过程及效果图

2023-03-27 14:33:01

在湿蚀刻的情况下,随着SiNx/SiOy层的厚度减小,剩余的SiOy层由于表面张力而坍塌,蚀刻溶液对孔的渗透变得更具挑战性。

2023-03-27 10:17:49 402

402

(Packaging)二. 多层板工艺流程:内层覆铜板(CCL)铜箔(Copper Foil)下料(Cut)→内层图形制作(Inner-layer Pattern)→内层蚀刻(Inner-layer Etch

2023-03-24 11:24:22

在过去的几年中,随着器件尺寸的不断减小,蚀刻表面的粗糙度开始发挥越来越重要的作用。

2023-03-24 10:11:13 251

251

电子发烧友App

电子发烧友App

硬声App

硬声App

823

823

109

109 306

306

163

163 1976

1976

86

86 131

131

114

114 119

119 326

326

371

371

294

294

188

188

250

250

263

263 1335

1335

259

259

331

331 166

166

434

434

241

241

217

217 146

146

188

188

136

136

788

788

164

164

553

553 368

368 244

244

319

319

281

281

670

670 290

290 474

474

292

292

811

811

187

187

1707

1707 1586

1586

239

239

345

345 319

319 1013

1013 4140

4140 222

222 383

383 183

183

190

190

2427

2427

318

318

897

897

1053

1053

197

197

197

197

258

258

231

231

3689

3689

3989

3989

665

665

526

526

1779

1779

771

771

452

452

1071

1071

618

618

846

846

575

575

352

352 700

700

584

584

979

979 1699

1699

118

118 247

247

1164

1164 1004

1004 408

408 2452

2452 886

886 402

402

评论