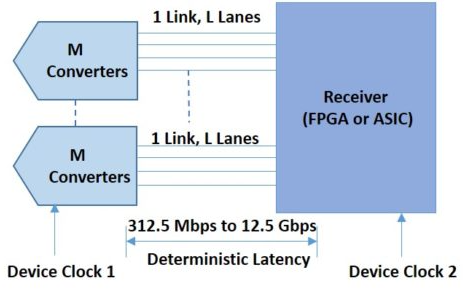

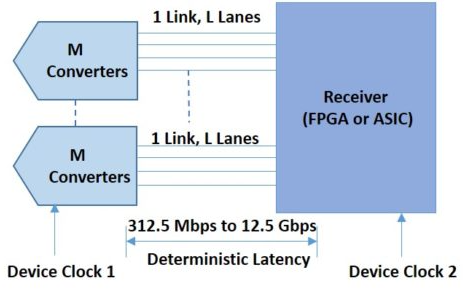

JESD204B标准提供一种将一个或多个数据转换器与数字信号处理器件接口的方法(通常是ADC或DAC与FPGA接口),相比于通常的并行数据传输,这是一种更高速度的串行接口。

2024-03-20 11:33:34 34

34

在STM32F103芯片中,利用I2C读写EEPROM时,单字节写入,读回的数据和写入的一致;但是当利用页写入时,读回的数据和写入的数据不一致,这是什么原因导致的?

2024-03-20 07:01:40

在微电子封装领域,铜线键合技术以其低成本、高效率和良好的电气性能等优势,逐渐成为芯片与基板连接的主流方式。然而,铜线键合过程中的焊接一致性问题是制约其进一步发展和应用的关键难题。焊接一致性不仅

2024-03-13 10:10:08 674

674

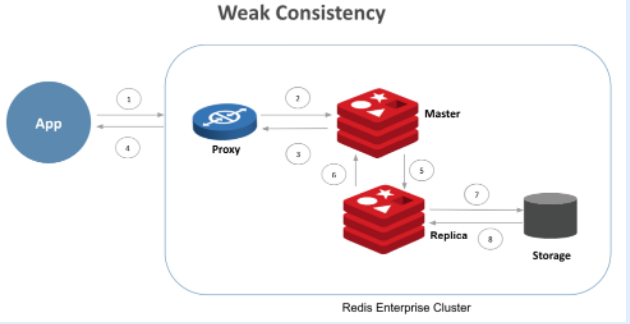

在数字化时代,数据备份成为了企业信息安全的核心环节。但在备份过程中,两个关键概念——应用一致性和崩溃一致性,常常被误解或混淆。本文旨在阐明这两个概念的差异,并分析它们在数据备份中的重要性,以便读者

2024-03-11 14:05:57 58

58

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别 在数字化时代,数据备份成为了企业信息安全的核心环节。但在备份过程中,两个关键概念——应用一致性和崩溃一致性,常常被误解或混淆。本文旨在阐明

2024-03-11 11:29:40 127

127

{bd295b7e-798c-41d4-9ea5-6f2de3e6e6f9}"

产品"ScanDrive28K8"

有没有解决或修复这个错误的方法?

我希望有一种一致的方法来获取 USB 设备的 USB 位置

2024-03-04 06:19:29

信号的应用。该套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 数据接收器 (JRx) 端口、片内时钟乘法器和数

2024-02-16 17:16:40

DDR一致性测试的操作步骤 DDR(双数据率)一致性测试是对DDR内存模块进行测试以确保其性能和可靠性。在进行DDR一致性测试时,需要遵循一系列的操作步骤,以保证测试的准确性和完整性。下面将详细

2024-02-01 16:24:52 210

210 )通过引出一个JTAG插座,同时兼容JTAG和DAP两种协议。由于上面提到的不一致性,只能通过调整线缆线序来满足这种需求,即当使用DAP协议时,需要将设备(TC397)侧JTAG插座的TMS(DAP1

2024-02-01 06:47:09

个串行通道的高速 JESD204C 输出接口,支持高达 17.16Gbps 的线路速率。通过 JESD204C 子类 1 支持确定性延迟和多器件同步。JESD204C 接口可进行配置,对线路速率和通道

2024-01-31 15:22:55

的应用。该套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 数据接收器 (JRx) 端口、片内时钟乘法器和数字

2024-01-04 20:01:43

× 235 MHz] ∕ 2

通道速率 = 4700 Mbps或4.7 Gbps

问:什么是应用层,它能做什么?

答:应用层是JESD204B提供的一种方法,允许样本数据映射到普通规格之外。这对于某些

2024-01-03 06:35:04

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-23 09:24:37

我使用的AD9974数据转换芯片,但是因为传感器的非一致性,两路数据进入9974之后需要调节9974的增益和偏置使得整幅图像保持一致性。请问有什么途径自动调节增益和偏置?主要是“方法”,谢谢

2023-12-19 07:37:23

目前,我在设计中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D转换器AD9683转换完成后的数据。但是JESD204 IP核的端口很多,我不知道应该如何将AD9683

2023-12-15 07:14:52

使用AD9680时遇到一个问题,AD9680采样率为1Gsps,JESD204B IP核的GTX参考时钟为250MHz,参数L=4,F=2,K=32,线速率为10Gbps,使用的为SYSREF

2023-12-12 08:03:49

我使用的是KC705板卡,调用了里面JESD204B的IP核,使用模式为interpolation值为4,4条链路,DAC频率为2.5GHZ,通道速度为6.25GHZ,出现的问题是:

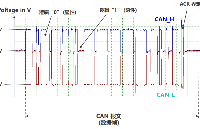

帧同步过程

2023-12-12 07:28:25

用单片AD9690采集数据给FPGA,不要求确定延迟,因此想要把AD9690配置在JESD204B sublcass 0 模式下。但是这种模式下,对于AD9690的SYSREF±的输入管脚怎么处理?以及AD9690工作在subclass 0 模式下还有没有其他要注意的地方?

2023-12-12 06:16:08

最近在使用AD9144芯片,调试JESD204B接口出现了一些问题,暂时没有头绪,期盼能得到各位的指点。

AD9144的主要配置如下:8条JESD204B链路,subclass1,速率为

2023-12-08 06:00:25

] axi-jesd204-rx 84aa0000.axi-jesd204-rx: Lane 1 desynced, restarting link

然后IIO软件没有波形出来,显示一条横线。

我的Boot.bin

2023-12-07 07:09:20

你好,因为项目需要,要做一块数据采集和发生板,接口支持JESD204B,时钟我选用了AD9523-1,电路我参考FMC-DAQ2开发板,舍弃了PLL1,直接在OSC_IN接入125M时钟作参考,输出

2023-12-06 07:48:32

的AD9162-FMX-EBZ板子,看到的现象是SYSREF信号一直为高,CGS测试信号不完全拉高,每次重新配置时拉高的lane通道数还不一样。其界面设置如下图所示。FPGA的使用是条用的xilinx的JESD204 IP核。

FPGA抓到的SYNC信号与SYSREF信号如下图所示:

2023-12-05 08:23:30

使用内部PLL,输入参考频率为100MHz。在采样率时钟设置为1GHz时,DAC的JESD204B链路能建立,但是当频率改为1.5GHz时,SYNC一直为低。其他相关寄存器都已经修改,serdes

2023-12-05 08:17:30

9680测试评估中遇到问题:

按照数据手册中的配置步骤,关断链路,通过0x570和0X56E寄存器快速配置JESD204B,链路上电后,电路锁相环无法锁定,204B无法正常输出数据。

2023-12-05 08:04:26

Jesd 无法连接到的问题已经配置了 AD9173 。模式为 8, 主要的内插是 x12, 通道内插是 x1. DAC PLL 锁定在 12GHz, 双链接, L=4. 。 Reg0X281 中

2023-12-05 08:04:04

我在使用AD9163的时候遇到JESD204B的SYNC信号周期性拉低。通过读寄存器值如图,发现REG470和REG471都为0xFF,而REG472始终为0.不知有谁知道是什么原因?该如何解

2023-12-04 07:30:17

AD9164 JESD204B接口的传输层是如何对I/Q数据进行映射的

2023-12-04 07:27:34

大佬好,小弟最近在调试AD9136芯片,遇到一个问题,如下:

1.我使用的是9136模式11,单链路模式,使用一个JESD204+一个JESD204 PHY,我将JESD204的tx_charisk

2023-12-04 07:14:58

在AD9680和AD9690数据手册上,写着它们[size=200%]支持的最小通道线率是3125Mbps,但是在JESD204B标准手册写着最小通道线率是312.5Mbps。

我疑惑这是数据手册的错误,还是AD9680和AD9690这两款芯片支持的最低通道线率确实时3125Mbps

2023-12-01 07:57:58

我这边做了一批包含AD9826芯片的板卡,实测本底暗信号幅度都是一样的,对应到AD9826应该是3000的DN值。但是AD9826采集出来不一致,变化从1500~4800。板卡更换AD9826芯片,暗信号DN值立马跟着改变。请问AD9826的本底偏置一致性这么差吗,还是其他什么原因造成的?

2023-12-01 06:33:55

作者:Ian Beavers,ADI公司应用工程师 JESD204B串行数据链路接口针对支持更高速转换器不断增长的带宽需求而开发。作为第三代标准,它提供更高的通道速率最大值(每通道高达12.5

2023-11-28 14:24:47 0

0 电子发烧友网站提供《JESD204B规范的传输层介绍.pdf》资料免费下载

2023-11-28 10:43:31 0

0 前言TSW14J57EVM数据采集/图形发生器:具有 16 个 JESD204B 通道 (1.6-15Gbps) 的数据转换器 EVM提示:以下是本篇文章正文内容,下面案例可供参考一

2023-11-21 15:05:23

我想把ADL5205用于IQ两路放大,想咨询两个问题

1、datasheet上没有给出两个通道的增益和相位一致性,有没有相关数据?

2、datasheet上只给出了10MHz以上的非线性指标,有没有DC~10MHz的非线性指标?

2023-11-20 06:11:48

我使用OP2177进行32倍放大,两个通道都同时进行32倍放大操作。进行两个通道的相位差测试时发现,在超过4KHz频点以后,两个通道的相位差就已经超过0.4度。8Hz的低频部分,相位一致性也不太好

2023-11-17 07:01:18

是德科技验证了首个采用 NB-IoT 技术的非地面网络 3GPP Rel-17 标准的协议一致性测试用例。 是德科技公司针对采用窄带物联网(NB-IoT)技术的非地面网络,针对第三代合作伙伴计划

2023-11-14 16:01:10 295

295 ADA4960 工作在单端输入-差分输出模式下,其输出P、N之间的相位一致性该怎么测试呢?

我使用矢量网络分析仪进行测试,未用到的端口接50Ω负载,接线方式如下图

原理图如下:增益电阻RG=100

2023-11-14 06:53:05

电子发烧友网站提供《铁轨铝磁环电感性能一致性差的原因.docx》资料免费下载

2023-11-13 16:22:45 0

0 MM32F0140 FlexCAN一致性测试 (2)

2023-11-10 18:23:15 333

333

MM32F0140 FlexCAN一致性测试 (1)

2023-11-10 17:50:47 237

237

什么是锂离子电池不一致性?锂离子电池不稳定的原因?如何提高锂离子电池的一致性? 锂离子电池不一致性是指同一批次或不同批次的锂离子电池在性能上出现不一致的现象。这种不一致性可能表现为电压和容量的差异

2023-11-10 14:49:43 516

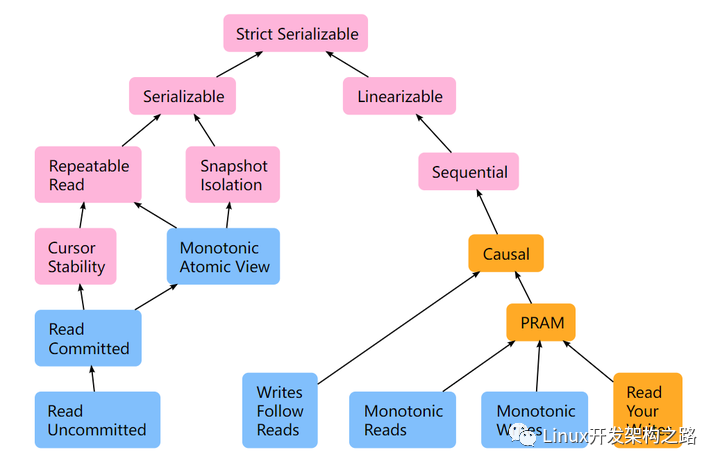

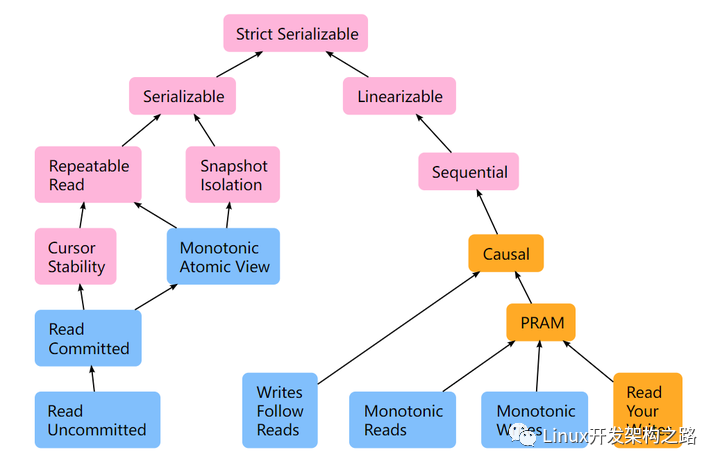

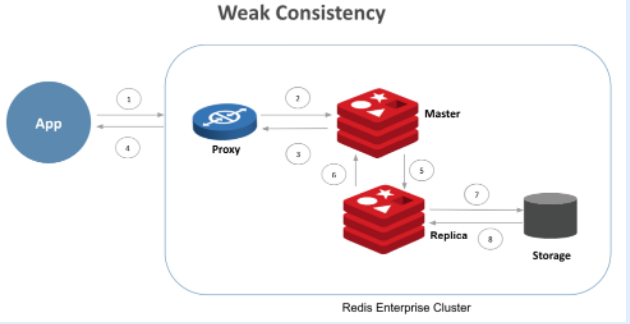

516 什么是一致性模型? 在分布式系统中,C(一致性) 和 A(可用性)始终存在矛盾。若想保证可用性,就必须通过复制、分片等方式冗余存储。而一旦进行复制,又来带多副本数据一致性的问题——一个副本的数据更新

2023-11-10 11:33:48 241

241

什么是电芯的不一致性?电芯不一致会造成什么后果? 电芯是电池组成部分之一,由正负极、电解质和隔膜组成。在电动车和移动设备中广泛使用的锂离子电池,通常由数十个甚至数百个电芯组成。电芯的不一致性指的是

2023-11-06 10:56:45 1381

1381 相对于传统金线键合,铜线键合设备焊接过程工艺窗口更小,对焊接的一致性要求更高。通过对铜线键合工艺窗口的影响因素进行分析,探索了设备焊接过程的影响和提升办法,为铜线键合技术的推广应用提供技术指导。

2023-10-31 14:10:16 324

324

“ 本文的参考文章是2022年HOT 34上Intel Rob Blakenship关于CXL缓存一致性的一篇介绍。”

2023-10-19 17:42:27 447

447

电子发烧友网为你提供ADI(ADI)AD9094: 8-Bit, 1 GSPS, JESD204B, Quad Analog-to-Digital Converter Data Sheet相关产品

2023-10-17 19:13:59

电子发烧友网为你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相关产品参数、数据手册,更有AD9207

2023-10-16 19:02:55

LogiCORE IP JESD204内核实现了一个JESD204B接口,使用GTX、GTH、GTP或GTY(仅限UltraScale和UltraScale+)收发器在1至8个通道上支持1至12.5

2023-10-16 10:57:17 358

358

在制药领域,注射剂的一致性密封质量对于产品的安全性和质量至关重要。为确保注射剂的密封性能符合预期,采用专业的注射剂一致性密封验证仪器进行检测是必不可少的。注射剂一致性密封验证仪器主要通过模拟实际使用

2023-10-13 13:41:44

电子发烧友网为你提供ADI(ADI)AD9694-EP: 14比特、500 MSPS、JESD204B、“四向数字转换器”强化产品数据表相关产品参数、数据手册,更有AD9694-EP: 14比特

2023-10-09 19:12:15

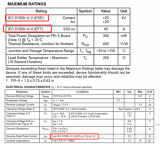

ESD和浪涌问题往往是基带工程师最头疼的问题,因为测试标准严苛,问题神出鬼没。特别是ESD问题,没有解决问题的标准路径,只能靠反复地构思方案并验证。

想要尽量避免以上问题,就必须选择合适的防护器件,设计上做足防护措施。本文告诉你ESD和浪涌的测试标准,测试方法,以及如何选择TVS器件。

2023-10-09 12:18:28 2394

2394

电子发烧友网为你提供ADI(ADI)AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次对数字转换器数据表相关产品参数、数据手册,更有AD9694S: 14-Bit

2023-10-08 16:48:36

缓存一致性 每次逢年过节的时候抢票非常艰难,放票的时候那么多人同时去抢票,如果所有人查询、购票等都去访问数据库,那数据库的压力得有多大,这时候很多都会引入缓存, 把车票信息放入缓存,这样可以减少

2023-09-25 15:25:31 606

606

电子发烧友网站提供《管理基于Cortex-M7的MCU的高速缓存一致性.pdf》资料免费下载

2023-09-25 10:11:48 0

0 电子发烧友网站提供《一种基于JESD204B的射频信号高速采集系统.pdf》资料免费下载

2023-09-14 11:14:07 1

1 AD9144是一款支持jesd204b协议高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的评估板(Evaluation Board),它是主要由AD9144,AD9516,与PIC16F单片机组成的系统。

2023-09-13 09:20:22 997

997

的IT标准,可以集成到现场总线系统中• PROFINET被IEC规范IEC 61158和IEC 61784标准化拥有低资源消耗、可用和不用操作系统、高度可移植性• 提供最好的条件用于PNO一致性测试• 提供嵌入式μIP UDP/IP栈• 支持几乎所有TCP/IP栈,通过通用和原生UDP socket连接

2023-09-07 07:10:15

74HCT165:TTL电平

•符合JEDEC标准:

•JESD8C(2.7伏至3.6伏)

•JESD7A(2.0 V至6.0 V)

•ESD保护:

•HBM JESD22-A114F超过2000 V

2023-08-04 17:39:53

CCN-502是基于AMBA 5 CHI架构的可扩展相干互连。它设计用于高端网络和企业计算系统。

CCN-502将互连和一致性功能组合到单个模块中。它提供以下外部接口:

•四个完全一致的CHI端口

2023-08-02 10:38:59

数据库一致性(database consistency)由一组值定义,数据库系统中的所有数据点都必须与这些值保持一致,才能正确读取和接受数据。如果任何不符合先决条件值的数据进入数据库,将导致数据

2023-07-13 13:56:06 356

356

本文旨在提供发生 JESD204B 链路中断情况下的调试技巧简介

2023-07-10 16:32:03 802

802

今天我们简单聊一聊,如何进行千兆以太网的Tx一致性测试。

2023-07-07 09:32:33 585

585

该芯片是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和 SYSREF 时钟时,PLL2 的 14 个时钟输出可配置去驱动 7 个JESD204B 转换器或其他逻辑设备。

2023-06-25 10:13:46 848

848 SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。

2023-06-21 15:11:14 508

508

SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。SYSREF可以使用直流和交流耦合来提供。不仅限于JESD204B应用,14个输出均可单独配置为传统高性能时钟系统输出。

2023-06-21 15:10:58 608

608

本文主要讲解了一致性哈希算法的原理以及其存在的数据倾斜的问题,然后引出解决数据倾斜问题的方法,最后分析一致性哈希算法在Dubbo中的使用。通过这篇文章,可以了解到一致性哈希算法的原理以及这种算法存在的问题和解决方案。

2023-06-16 15:30:23 279

279

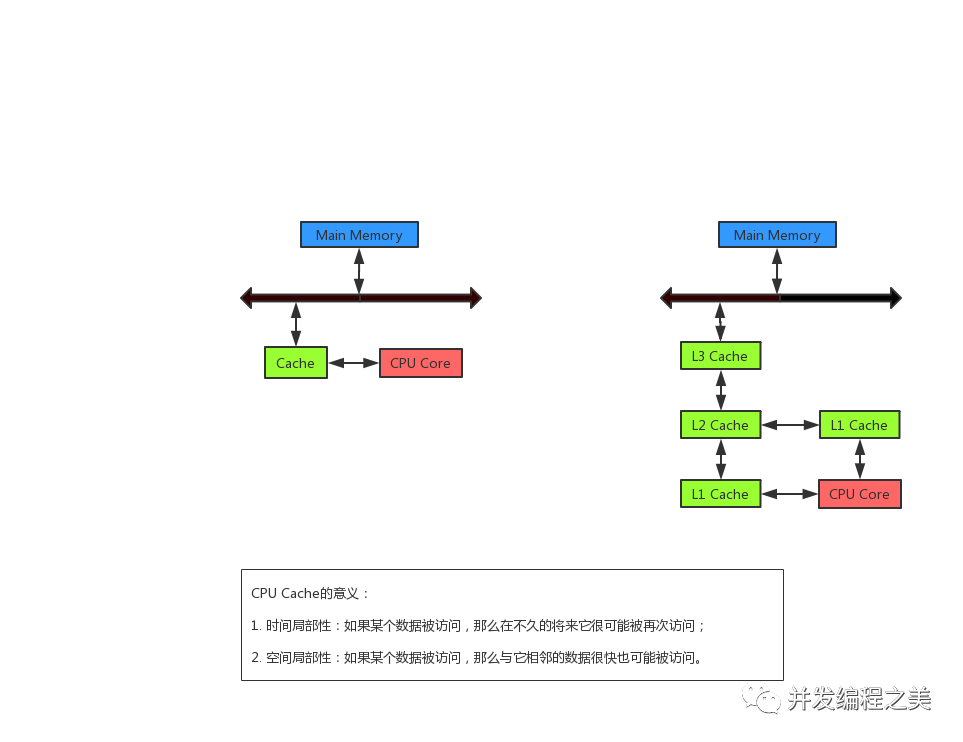

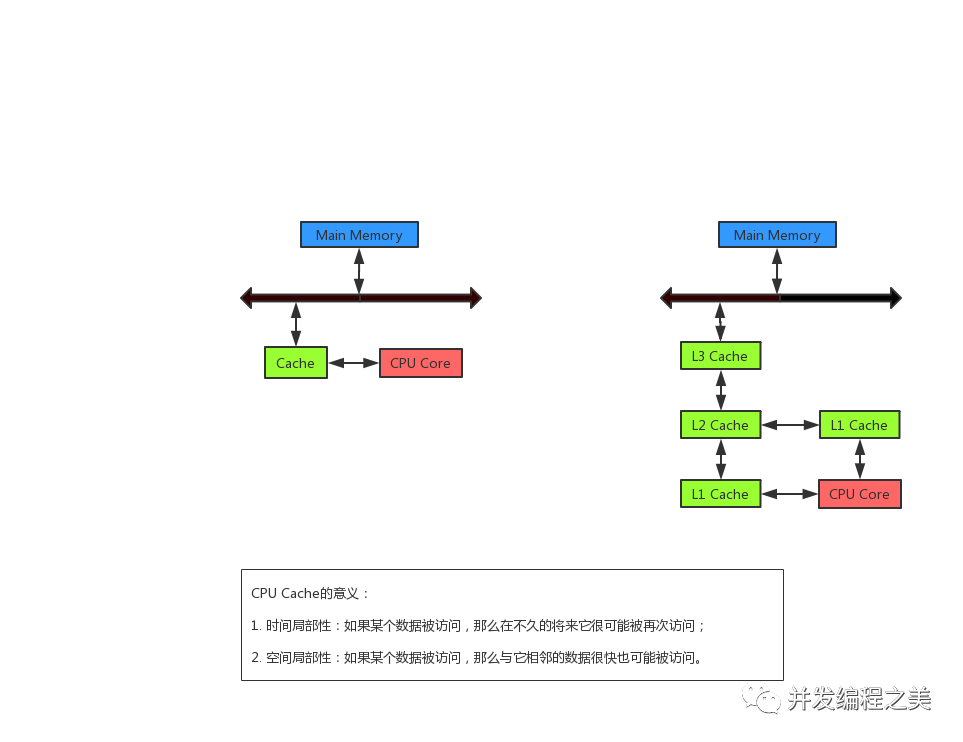

之前介绍了java并发包的cas原理和java内存模型,这篇我们介绍下cpu缓存一致性原理,可以帮助我们更好的理解cas的底层原理。

2023-06-09 16:01:17 2572

2572

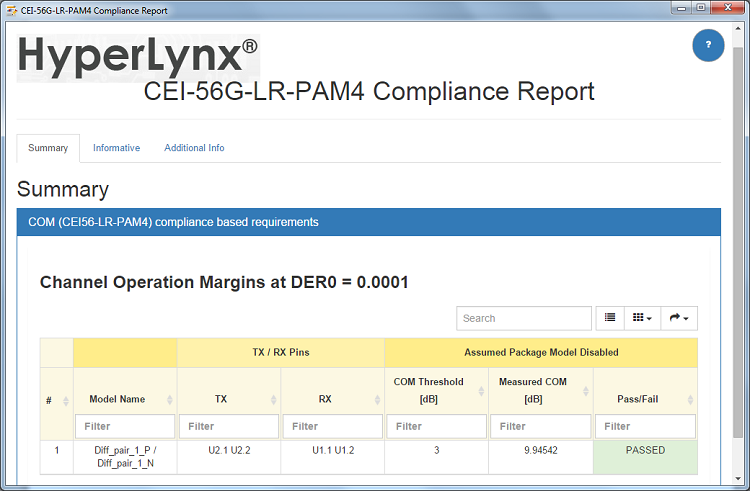

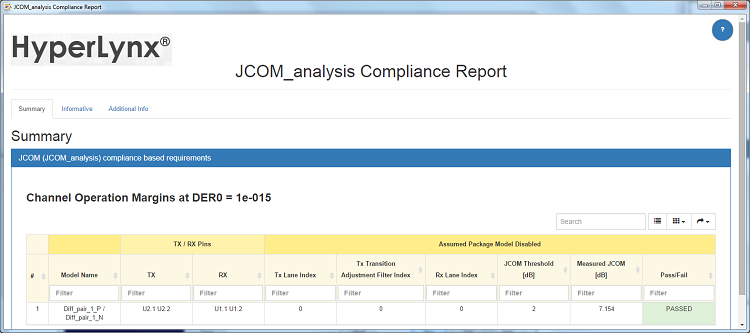

您的PCB可以处理高达12.5Gbps的速度吗,感到惊讶,对吗?JESD204B标准为串行接口提供高达12.5Gbps的比特率。这种升级允许设计人员在FPGA/ASIC上使用更少的收发器,从而减少

2023-05-26 14:50:57 608

608

JESD204B规范是JEDEC标准发布的较新版本,适用于数据转换器和逻辑器件。如果您正在使用FPGA进行高速数据采集设计,您会听到新的流行词“JESD204B”。与LVDS和CMOS接口相比,这一较新的版本具有显著的优势,因为它包括更简单的布局和更少的引脚数。

2023-05-26 14:49:31 361

361

多路热电偶测温容易遇到通道精度的一致性问题,主要原因是冷端的温度不一致性。本文分析该问题,并推荐相应的电路解决方案。热电偶冷端的实际位置热电偶是一种温差元件,如下图1,它的输出信号是两个线端之间

2023-05-18 09:54:59 419

419

多路热电偶测温容易遇到通道精度的一致性问题,主要原因是冷端的温度不一致性。本文分析该问题,并推荐相应的电路解决方案。

2023-05-16 14:04:14 490

490

大部分的ADC和DAC都支持子类1,JESD204B标准协议中子类1包括:传输层,链路层,物理层。在少部分资料中也会介绍含有应用层,应用层是对JESD204B进行配置的接口,在标准协议中是不含此层,只是为了便于理解,添加的一个层。

2023-05-10 15:52:55 1376

1376

大家好,

我正在使用 Vector CANoe 进行 LIN 一致性(合规性)测试,我正面临这个问题,那么它的原因应该是什么,解决方案是什么?

在测试用例 PT-CT88,89,90,93 中。

IUT 未响应诊断请求

2023-05-09 09:31:36

的是,我们现在在较小的传输中遇到缓存问题。有时,当缓冲区被复制到用户空间时,64 字节的数据没有被正确的数据 buf 填充为 0xff。我们在一次传输中传输了大约 1.1 MBytes,有时一些缓存行会得到不正确的数据。

可以调用哪些刷新/无效缓存函数来保证缓存一致性?

2023-04-27 08:30:48

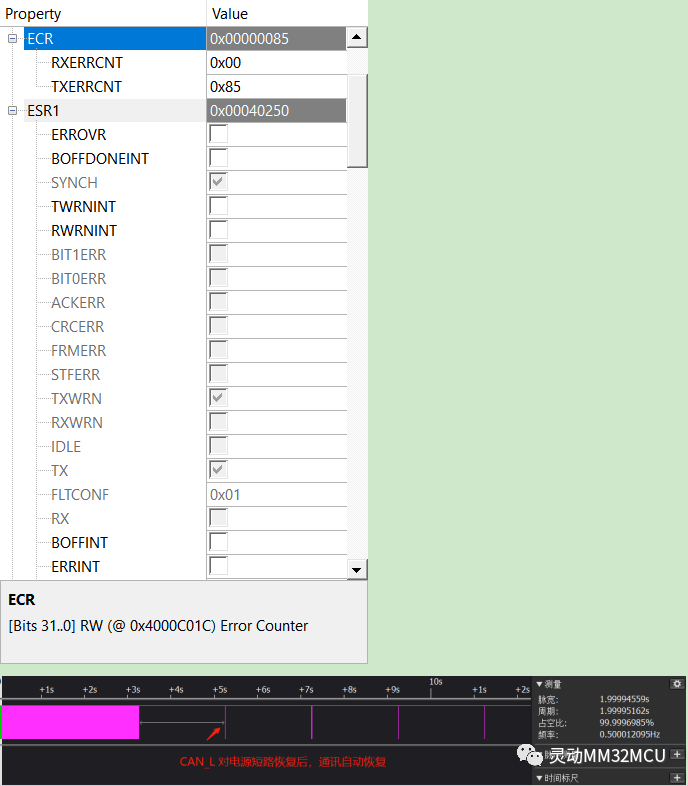

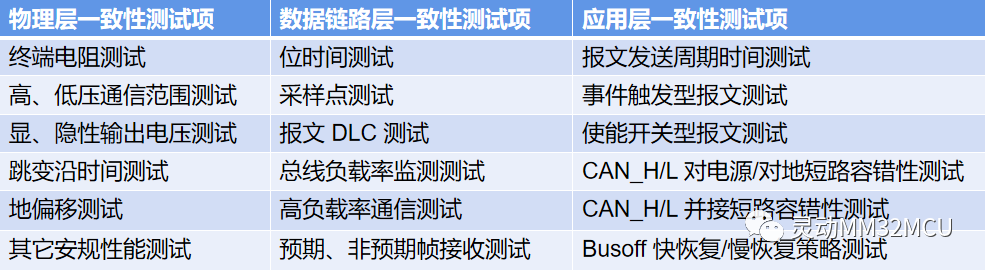

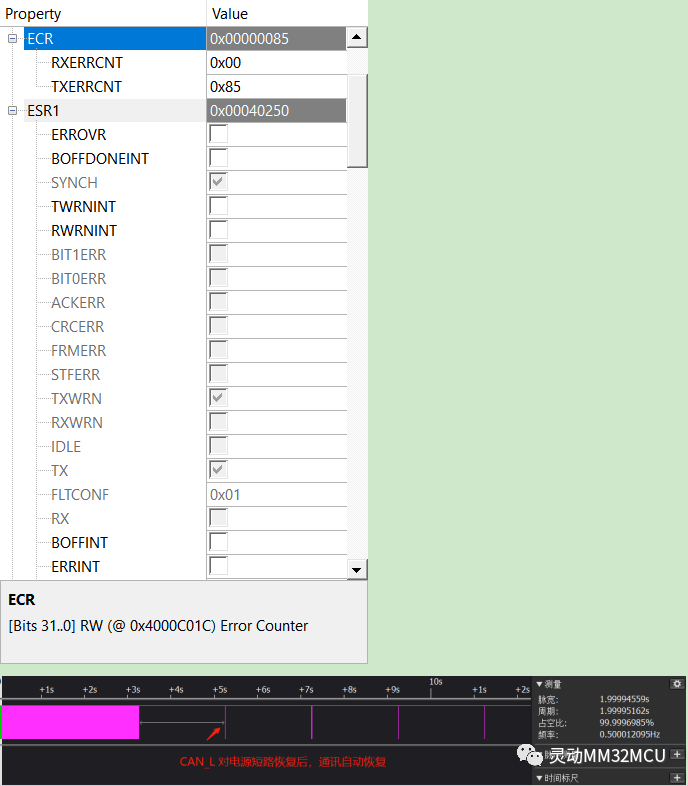

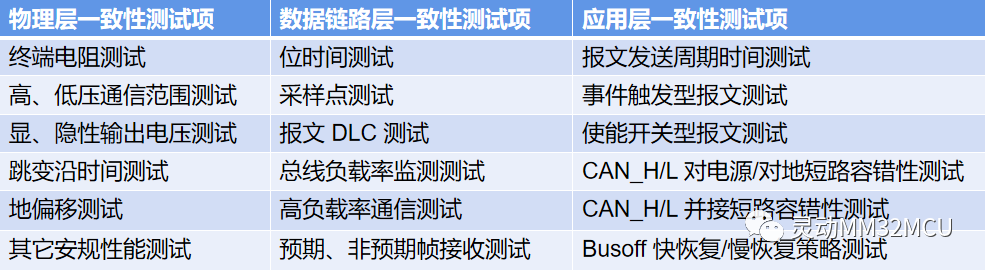

在汽车领域CAN/CANFD网络通信中,各节点(控制器)的质量不一致可能会引发错误、网络故障或网络瘫痪等问题,所以,为保证CAN/CANFD网络的正常安全运行,必须要执行CAN/CANFD一致性测试。

2023-04-24 09:28:18 1983

1983

LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们是高性能的双环路抖动清除器,可在具有器件和SYSREF时钟的子类1时钟方案里驱动多达七个JESD204B转换器或逻辑器件。图1是典型JESD204B系统(以LMK04821系列器件作为时钟解决方案)的高级方框图。

2023-04-18 09:25:30 918

918

JESD207 FOR LATTICEECP3

2023-03-30 12:02:10

JESD207 FOR LATTICEECP3

2023-03-30 12:01:20

电子发烧友App

电子发烧友App

评论