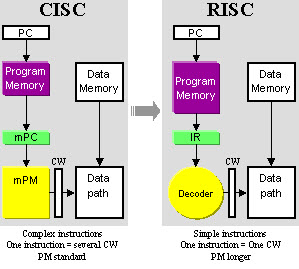

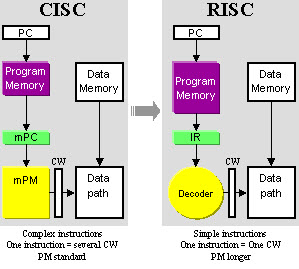

精简指令集计算(RISC)架构的目标之一即是保持指令简单化,以便让指令运行得足够快。这与复杂指令集计算(CISC)架构正好相反,后者一般不会同样快地执行指令,但每个指令可完成更多处理任务。

2024-03-22 11:08:27 22

22

超低功耗 高性能的无线射频收发器

2024-03-18 13:55:17 81

81

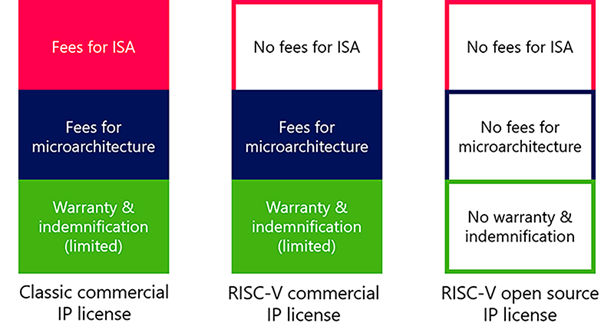

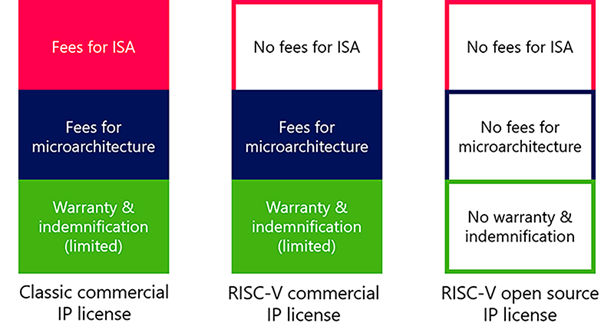

它应该是稳定的,基础的指令集架构不应该改变。更重要的是,它不能像以前的专有指令集架构一样被弃用,例如AMD Am29000、Digital Alpha、Digital VAX、Hewlett

2024-03-13 09:41:06 136

136

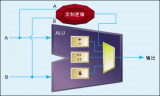

,精简指令架构的CPU,都会提供大量的寄存器。

RISC-V 的规范定义了32个通用寄存器以及一个PC寄存器,这对于RV32I、RV64I、RV128I 指令集都是一样的,只是寄存器的位宽不一样。

如果要

2024-03-12 10:25:21

本人没有芯片设计,或者指令集方面较深的基础知识,不过认真看这本书也令我学到了不少。

书中一开始便提到RISC-V的目标是称为一款通用的指令集架构:需要适合设计各种规模的处理器,能兼容各种流行的软件栈

2024-03-05 22:01:02

这本书确实不是简单的书,两位作者都曾参与RISC-V的研发设计,而几位译者及审校者则都与中科院计算技术研究所相关,可见这本书的质量肯定不低!

看到书中说,最好是了解过至少一款指令集,否则建议先阅读

2024-03-05 20:54:55

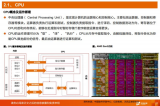

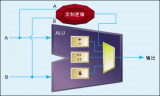

CPU 支持的所有指令和指令的字节级编码就是这个 CPU 的指令集架构(Instruction Set Architecture,ISA),指令集在计算机软件和硬件之间搭起了一座桥梁。

2024-03-05 10:31:03 169

169

简介

https://github.com/nihui/ruapu

ruapu单个文件探测CPU指令集信息

ruapu通过执行特定扩展指令,捕获CPU非法指令异常,判断当前CPU是否支持某扩展指令集

2024-02-25 21:36:55

的目标文件。

扩展指令集

RISC-V除了基本指令集外,还支持多种扩展指令集,例如RV32M(乘法和除法指令),RV32F和RV32D(单精度和双精度浮点数),RV32A(原子指令),RV32C(压缩指令),RV32V(向量),RV64(64位地址指令),RV32/64特权架构;未来还有多种可选的扩展。

2024-02-03 13:29:19

第2章 RV32I:RISC-V基础整数指令集

本章重点讲解构成RISC-V基础整数指令集的基本指令和指令格式。主要包含寄存器间操作的R型,用于短立即数和取数操作的I型,用于存数操作的S型,用于条件

2024-01-31 21:10:52

RISC-V开放架构设计之道, 是一本全面介绍RISC-V指令集架构设计、优化和实现的书籍。 书中详细介绍了RISC-V指令集体系结构,包括指令集、寄存器体系、存储体系和中断体系。 还介绍了

2024-01-29 10:09:47

指令,通常讲授指令一条一条地讲过去,往往让人觉得枯燥,特别是现在用汇编语言开发程序的场合很少。该书没有陷入俗套,而是从体系设计的角度对指令进行了全面的分类和介绍。对于每类指令,都讲RISC-V和其他指令集

2024-01-28 16:58:24

。

图1:RV32I指令集

在讲RISC-V各个阶段,横向比较ARM架构,体现出RISC-V的优越性。

●RV32I寄存器

RISC-V基础指令集RV32I,只有6种基本指令格式:用于寄存器之间操作

2024-01-28 11:41:22

(Andrew Waterman),SiFive 的总工程师和联合创始人。SiFive 由RISC-V 架构的发明者们创办,旨在提供基于RISC-V 的低成本定制芯片。

和其他介绍指令集架构书籍相比,该书

2024-01-23 20:08:24

中出现的RISC-V拓展。

这本书的开篇讲的是,为什么我们需要RISC-V指令集?

从过去的ISA的特点进行引入,先以目前主流的x86指令集架构为例列出了增量式指令集架构中普遍含有的的一个缺点,并从指令集设计导论中

2024-01-22 16:24:25

想问问具体要怎么实现标准指令集的扩展呢?需要修改哪些硬件啊?

每一种指令集扩展是相似的吗?还是需要不一样的步骤呢(比如V扩展、K扩展)?

2024-01-21 22:19:21

,RISC-V的64位地址版本。

●第10章:介绍系统指令

●第11章:简要介绍RISC-V国际基金会目前正在考虑添加的其他扩展。

○附录A:按字母表顺序排列的指令集汇总

○附录B:展示了一些常见的汇编语言操作

2024-01-21 17:03:21

该章节适合理论结合实践学习,直接在开发板上使用gdb调试参考。

RV32I指令集示意图以下图片很好的解释了RISC-V的指令表示,列出了缩写对应的完整单词有助于记忆,且表示了指令的组合,这样看到指令

2024-01-20 23:12:40

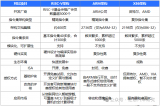

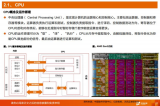

RISC-V(Reduced Instruction Set Computing - Five),中文名为第五代精简指令集。它是一种基于精简指令集原则的开源指令集架构(ISA),可用于设计和实现处理器芯片和计算机体系结构。它是全球共识的第三大架构,与X86和ARM并列。

2024-01-19 15:45:12 232

232

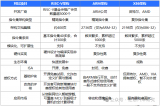

)和RISC(精简指令集)两大类,CISC型CPU目前主要是x86架构,RISC型CPU主要包括ARM、RISC-V、MIPS、POWER、Alpha架构等。

2024-01-16 10:59:01 155

155

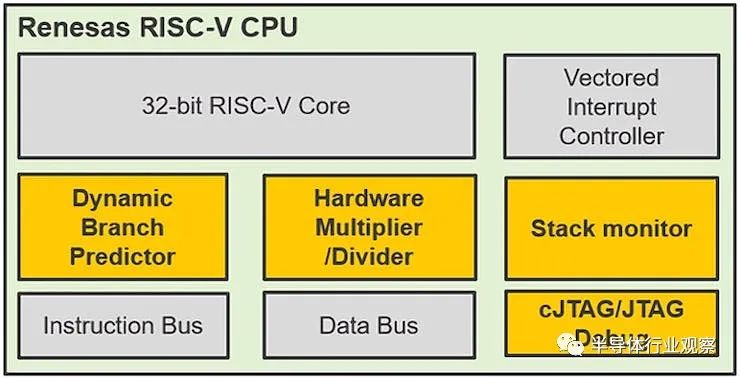

RISC-V内核的指令集只有47条指令。x86指令的实际数量难以计算,可能将近1000个。尽管Arm的指令集很小,但仍然比RISC-V的指令集大很多。

2024-01-04 10:46:03 221

221

面向未来产品商业化,这家新型公司成立的主要目标在于加快基于 RISC-V(一种基于精简指令集 RISC 原则的开源指令集架构,常用于芯片设计)架构的实现。作为一个单一来源,他们计划打造基于 RISC-V 的兼容产品,以提供参考架构,协助建立业界广泛采用的解决方案。

2023-12-26 14:59:03 272

272 ,

本书值得每一位对RISC-V感兴趣的读者精读,并可作为从业者随时翻阅的案头参考书。

RISC-V 的基本概念和设计原则

深入分析RISC-V 的指令集、寄存器、内存管理、异常处理等

丰富的图表

2023-12-13 17:25:41

现代处理器的主要指令集架构(ISA)包括:x86指令集架构、RISC指令集架构。

2023-12-11 09:55:10 757

757

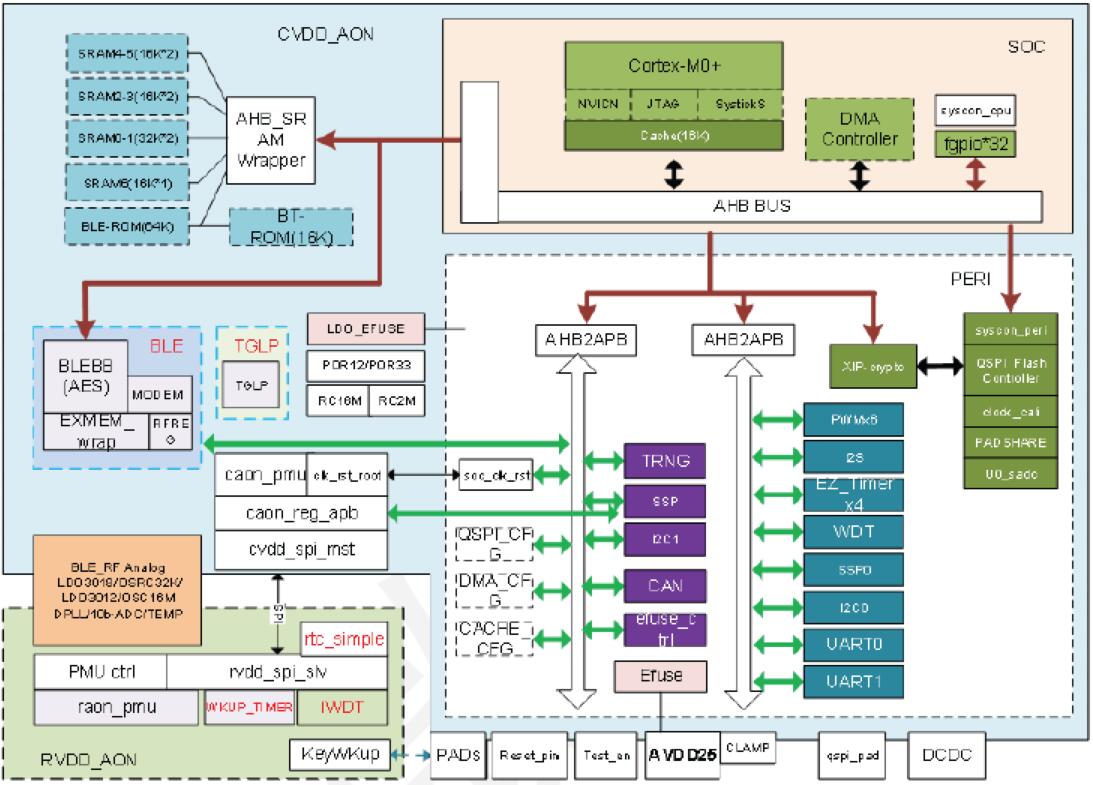

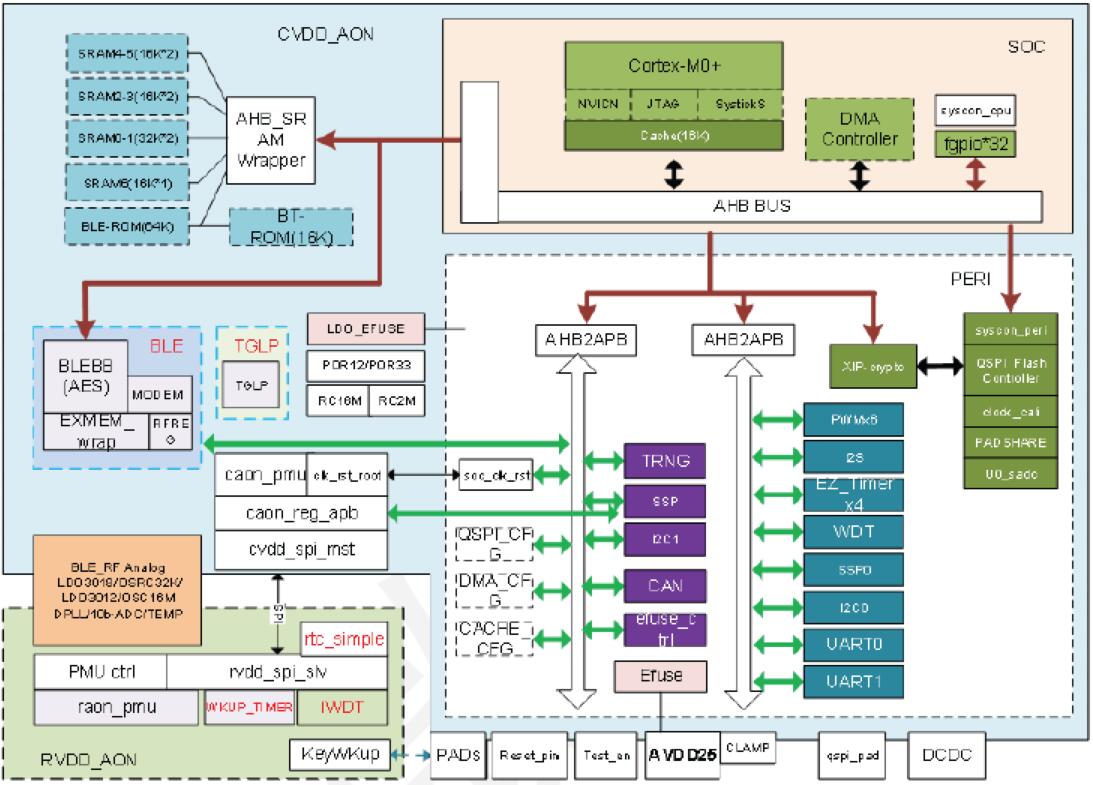

Si24R03是一款高度集成的低功耗SOC芯片,其集成了基于RISC-V核的低功耗MCU和工作在2.4GHz ISM频段的无线收发器模块。

MCU模块具有低功耗、Low Pin Count、宽电压

2023-12-10 00:46:03

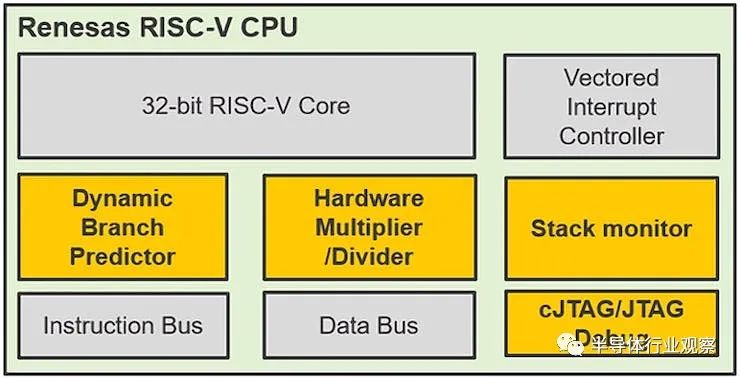

嵌入式硬件专家瑞萨电子宣布推出首款基于免费开放的 RISC-V 指令集架构 (ISA) 的完全自主研发的处理器内核。

2023-12-01 17:28:18 827

827

无线收发器特性: n 工作在 2.4GHz ISM 频段。 n 调制方式:GFSK/FSK。 n 数据速率:2Mbps/1Mbps/250Kbps 。 n 兼容 BLE4.2 PHY&MAC

2023-11-06 15:34:58 176

176

RISC-V(Reduced Instruction Set Computing-five)是一个基于精简指令集(Reduced Instruction Set Computing,RISC)原则的开源指令集架构(ISA)。

2023-10-30 15:54:54 251

251

简介

青稞处理器是沁恒微电子自研的32位微处理器,遵循和兼容开源的RISC-V指令集架构规范,并提供可选的功能扩展。支持IMAFC指令集和自定义压缩指令,并提供硬件压栈(HPE)、免表中断(VTF

2023-10-11 10:42:49

产品概述

CH32V、CH32X系列MCU采用自研的青稞RISC-V内核,基于蓬勃发展的RISC-V开源指令集架构,针对低功耗和高速响应等应用优化扩展,免费配套IDE等开发工具软件,免除第三方

2023-10-11 09:56:08

DLX指令集RISC_CPU_verilog源码

2023-09-26 07:01:26

学习如何构建由多个NR24L01收发器模块组成的Arduino无线网络。包含相关代码+线路图+详细说明下

2023-09-25 07:40:50

指令系统是生态底层逻辑,可分为复杂指令集和精简指令集。指令系统(ISA)属于计算机中硬件与软件的接口,可实现高级程序语言、汇编语言和机器语言的连接,最终编译为 CPU 可执行的简单指令

2023-09-22 16:09:20 813

813

处理器可以基于复杂指令集计算(CISC)或精简指令集计算(RISC)。CISC一般有约80条指令,而RISC大约有30条指令,同时也有更多的寻址模式,约为12-24条,而RISC只有3-5条寻址模式

2023-09-05 15:47:30

Hot Chips 2023大会上,Intel首次公布了一款RISC指令集处理器,拥有独特的8核心528线程规格。

2023-09-01 15:02:49 365

365

-V是基于精简指令集计算(RISC)原理建立的开放指令集架构,它是由加州大学伯克利分校图灵奖得主David Patterson教授及其课题组历经30多年研发的第五代基于RISC的CPU(中央处理器)指令集架构

2023-08-30 23:06:43

ASR6505是一种通用的LoRa无线通信芯片组,集成了LoRa无线电收发器、LoRa调制解调器和一个8位CISC MCUASR6505是基于STM 8位MCU与SX1262 的SiP芯片,相对于

2023-08-30 15:34:19

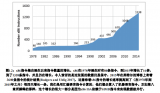

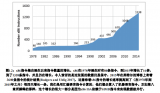

历程及特征,可大致分为三个阶段,在RISC-V发展早期,大家把RISC-V处理器多应用于专用芯片,如RF通信、电源管理芯片等;随着RISC-V指令集的逐渐完善,越来越多的IoT(物联网)、MCU(微控制

2023-08-30 13:53:47

-V是基于精简指令集计算(RISC)原理建立的开放指令集架构,它是由加州大学伯克利分校图灵奖得主David Patterson教授及其课题组历经30多年研发的第五代基于RISC的CPU(中央处理器)指令集架构

2023-08-30 10:40:43

系列兼容的软件。

ARM720T是一个完全静态的部件,旨在将功耗需求降至最低。

这使得它非常适合便携应用程序,因为这两个功能都是必不可少的。

ARM720T的体系结构基于精简指令集计算机(RISC

2023-08-24 07:16:02

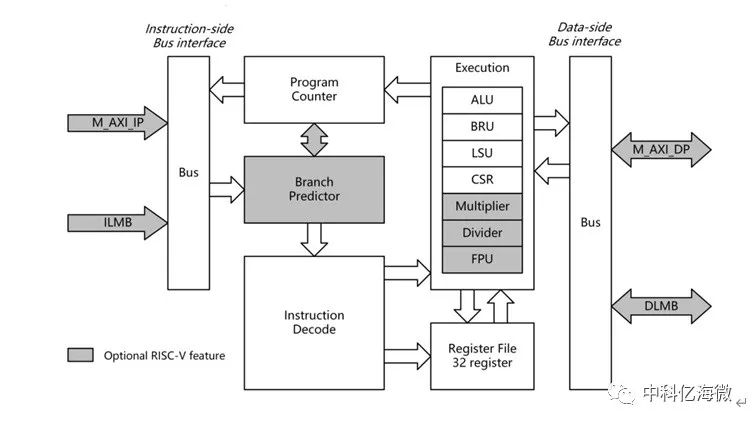

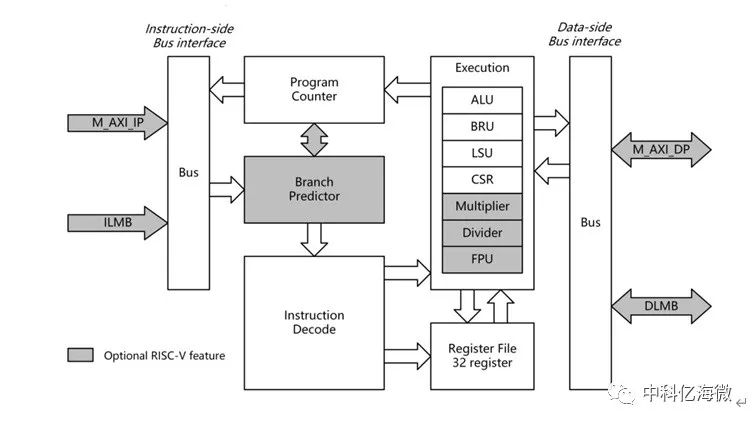

MicroBlade 处理器软核 IP是实现基于 RISC-V(Reduced Instruction Set Computer,精简指令集计算机)指令集架构的 32 位处理器软核,支持 RV32IM 指令集,支持 AXI4-Lite 接口,用于简化 FPGA 中复杂的控制逻辑。

2023-08-18 09:27:00 232

232

MicroBlade处理器软核IP是实现基于RISC-V(ReducedInstructionSetComputer,精简指令集计算机)指令集架构的32位处理器软核,支持RV32IM指令集,支持

2023-08-18 08:14:05 369

369

RVDK由一套工具以及支持文档和示例组成,使您能够为ARM系列精简指令集计算(RISC)处理器编写应用程序。

您可以使用RVDK构建C、C++和ARM汇编语言程序

2023-08-16 07:44:37

我看了一下说明书,好像nice接口的opcode是固定的,不能与f指令集的互通,需要改什么rtl代码吗?

2023-08-11 13:01:37

RISC-V4C内核

支持RV32IMAC指令集和自扩展指令

26KB SRAM,512KB Flash,支持ICP、ISP和IAP,支持OTA无线升级

内置2.4GHz RF收发器和基带及链路控制,支持

2023-08-09 11:27:27

应用的MCU新产品。不同厂家的MCU产品其指令集各不相同,特别是指令集系统架构的不同,如市场上广泛应用的MCS51系列和PIC系列微控制器则分别采用CISC指令系统和RISC指令系统。

2023-08-02 15:11:01 253

253 的方式执行它。

本指南介绍了在64位Armv8-A体系结构中使用的A64指令集AArch64。

我们不会在本指南中涵盖每一个指令。所有的说明都在臂中详细说明架构参考手册。相反,我们将介绍指令的格式

2023-08-02 06:33:42

于RISC-V发展“主流CPU”。 确实,在x86架构统治高性能运算,ARM架构主导移动计算之后,RISC-V成为第三种主流架构的趋势愈发明显,其中国内业者是主要的推动力量。RISC-V是一种基于精简指令集原则的开源指令集架构,相较于x86架构和ARM架构,RISC-V在灵活

2023-07-22 01:05:00 1832

1832 应用博览会”(ICDIA 2023) 在无锡太湖国际博览中心召开。中移芯昇科技RISC-V芯片精彩亮相ICDIA滴水湖论坛国产芯片展区。 RISC-V是基于精简指令集原则的开源指令集架构(ISA)。在万物互联时代,RISC-V因其开源开放的特性表现出了较强优势,为国产芯

2023-07-14 17:40:03 684

684 RISC-V是一种开源精简指令处理器,起源于美国加州大学伯克利分校的一项研究项目。相比受到授权限制的x86和ARM架构,RISC-V具有精简、开源、中立和响应速度快等特点,能够用于开发适应特定需求的定制芯片。

2023-07-11 16:45:55 1002

1002 中央处理单元架构具有从“指令集架构”到其设计工作的能力。CPU的架构设计是RISC(精简指令集计算)和CISC(复杂指令集计算)。CISC能够在一个指令集中执行寻址模式或多步操作。这是CPU的设计,其中一条指令执行许多底层操作。例如,内存存储、算术运算和从内存加载。

2023-07-10 10:30:24 5253

5253

RISC-V指令集是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),RISC-V则是在指令集不断发展和成熟的基础上建立的全新指令。RISC-V指令集完全开源,设计简单,拥有模块化

2023-07-10 09:23:44

RISC-V、ARM 和x86微处理器之间的许多差异都很细微,并且与内存寻址方式、分支执行方式、异常处理方式等有关。本文将考虑更高层次的差异,并将简要比较精简指令集计算(RISC)和复杂指令集计算

2023-07-06 11:32:56 3302

3302

RISC-V指令集是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),RISC-V则是在指令集不断发展和成熟的基础上建立的全新指令。RISC-V指令集完全开源,设计简单,拥有模块化

2023-06-30 10:00:39 325

325

直播简介 RISC-V已然成为后摩尔时代DSA芯片的基础指令集,基于RISC-V的AI芯片,GPGPU,高性能服务器CPU,嵌入式CPU如雨后春笋;如何支持各种RISC-V扩展,支持基于RISC

2023-06-28 09:05:04 764

764

制程并同时提供客户低成本、高性能、及高性价比等显著优势。 XL2401C 核心建立在 RISC 精简指令集架构可以很容易地做编辑和控制,共有 55 条指令。 除了少数指令需要 2 个时序,大多数指令

2023-06-25 15:14:00

一、RISC-V 和 ARM 的相似之处

RISC-V 和 ARM 基本上都是 RISC(精简指令集计算机)。RISC-V 和 ARM 都使用加载-存储架构。意思是数据从内存中加载,在CPU中处理

2023-06-21 20:31:32

概述CH583是集成BLE无线通讯的32位RISC微控制器。片上集成2Mbps低功耗蓝牙BLE 通讯模块、2个全速USB主机和设备控制器及收发器、2个SPI、4个串口、ADC、触摸按键检测模块

2023-06-20 15:59:05

RISC-V处理器采用精简指令集(RISC)原则的开源指令集架构(ISA),与传统的x86和Arm平台相比,其决定性优势在于ISA的开源特性,企业可在RISC-V架构下自由修改并优化(IC架构)。

2023-06-13 17:21:05 587

587 MS1636是一款高性能,低成本,超低功耗的无线通信MCU芯片。该芯片不仅集成一个可以工作到高达64MHz的32位的精简指令集的(RISC)的高效处理器,还集成一个功能丰富的蓝牙5.1通信收发模块。

2023-06-12 17:15:51 577

577

RISC-V处理器在移动通信、数据中心、边缘计算及自动驾驶等领域的市场化落地。全球RISC-V软件生态计划“RISE”启动灵活开放的精简指令集RISC-V,是当下发展最快的处理器新架构。RISC

2023-06-02 15:29:02

ASR6505是基于STM 8位MCU的无线通信芯片组

ASR6505是一种通用的LoRa无线通信芯片组,集成了LoRa无线电收发器、LoRa调制解调器和一个8位CISC MCU

ASR6505

2023-05-31 10:04:08

都不能完全满足它们的需求。

因此,RISC-V进入数据中心市场似乎将成为必然的结果。再加上大量初创公司和行业巨头在高性能处理器内核和制造领域的努力,RISC-V指令集架构的开源化与中立化的过程,显然会

2023-05-30 14:11:59

精简指令集计算机体系结构(RISC)是一种指令集体系结构(ISA),它意味着硬件和软件之间的基本桥梁。RISC通过定义一组简单的指令来实现汇编语言程序员和处理器之间的通信,这些指令组合在一起以执行各种复杂的指令。

2023-05-25 15:39:12 890

890

产品概述:KF8A100 为哈佛结构的精简指令 CPU。在这种结构中,程序和数据总线是相互独立的。指令字节长度为 16 位,大多数指令能在一个机器周期内执行完成。一共有 73 条指令,效率高,容易

2023-05-23 17:00:55

厦门感芯科技多线程处理器MC3172开发板 ,64线程同步并行运行,各个线程速度可按需配置,硬件级实时响应,无需中断服务程序,无需实时操作系统。RISC-V RV32IMC 指令集,100%单周期

2023-05-23 11:44:03

RISC-V等精简指令集架构 (ISA) 比复杂指令集架构更高效,并且占用资源更少。工业物联网 (IIoT) 应用通常不仅需要模块之间具有高度连接性和协作水平,还需要保持较低成本以及降低

2023-05-18 10:32:13 458

458 RISC-V是一个基于精简指令集的开源指令集架构。与主流的主流的架构为x86与ARM架构不同,其特点就是完全开源。今天我们聊一聊具有国产RISC-V内核的单片机。

1、 CH32Vxxx系列:南京沁

2023-05-14 09:18:55

RISC-V是基于精简指令集计算(RISC)原理建立的开放指令集架构,是一种与X86,ARM并列的一种计算指令集架构。RISC是一个开放的芯片架构,可以免费授权。客户可以添加自己的扩展,并为包括

2023-05-14 09:05:11

适配优化,结合RISC-V精简指令集特性,裁剪了冗余功能,实现了既保证用户应用安全隔离,同时降低资源消耗并提升响应速度,适用于可信云原生、Serverless、函数计算等新型弹性云计算业务场景。

作为

2023-05-11 14:08:09

CISC与RISC的不同 CISC是复杂指令集CPU,指令较多,因此使得CPU电路设计复杂,功耗大,但是对应编译器的设计简单。 RISC的精简指令集CPU,指令较少,功耗比较小,但编译器设计很复杂,它的关键在与流水线操作能在一个时钟周期完成多条指令。

2023-05-06 12:52:52 13442

13442

-V 精简指令集特性,裁剪冗余功能,实现了应用安全隔离,同时降低资源消耗并提升响应速度,适用于可信云原生、Serverless、函数计算等新型弹性云计算业务场景。”

赛昉科技表示,已交付支持虚拟化指令扩展

2023-05-05 09:46:26

MIPS指令集与OpenHarmony 在带屏设备上的商业化应用演讲PPT资料免费下载,有需要的朋友自取~

2023-04-21 17:06:36

ESP32 AT指令集.pdf

2023-04-17 09:33:15 18

18 RISC-V(“RISC five”)的目标是成为一个通用的指令集架构(ISA):

⚫ 它要能适应包括从最袖珍的嵌入式控制器,到最快的高性能计算机等各种规模的

处理器。

⚫ 它应该能兼容各种

2023-04-17 09:21:17 0

0 的复杂性和相关知识产权的限制,伯克利大学决定发明一种全新的、简单且开放免费的指令集架构。RISC的英文全称为“Reduced InstrucTIon Set Computer”,即“精简指令集

2023-04-14 22:10:56

请教各位前辈,最近貌似RISC-V比较热门,那么RISC-V是什么时候出现的?应该不会很久吧?RISC-V的指令集有多少条呢?

2023-04-14 21:46:30

。RISC-V指令集有RV32I、RV32E、RV64I、RV64E、RV64I等等,RV代表RISC-V,32/64代表32位或64位,I和E都是基本指令集,在I和E的基础上,可以添加D(双精度浮点扩展

2023-04-14 10:18:23

本帖最后由 余一yui 于 2023-4-26 10:44 编辑

《玄铁RISC-V处理器入门与实战》是一本介绍开源ISA(指令集架构)RISC-V的电子书。RISC-V是由加州大学伯克利分校

2023-04-12 11:16:58

采用Arm架构会存在得天独厚的优势,短时间来看还是难以撼动的。Arm是一个32位精简指令集(RISC)处理器架构,其应用领域十分广泛,目前主要有手机、PC、服务器、汽车、物联网、人工智能解决方案等。在

2023-04-05 12:16:42

占据市场主流,且未来32位产品占比预计仍将不断提高。 6. 按照指令集:可分为CISC(复杂指令集架构)和RISC(精简指令集架构)两类。 MCU的产生与发展和微处理器的产生与发展大体同步,自

2023-04-03 15:32:56

RISC-V架构 RISC-V(发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA)。 与大多数指令集相比,RISC-V指令集可以自由地用于任何目的

2023-04-03 15:29:09

本书详细地介绍了RISC-V的基本原理、指令集、编程工具和环境、体系结构和扩展以及应用案例和实践等方面的内容,覆盖了RISC-V体系结构的各个方面,使读者能够全面深入地了解RISC-V的体系结构

2023-04-03 15:15:20

RISC(精简指令集计算机)是一种执行较少类型计算机指令的微处理器,起源于80年代的MIPS主机(即RISC机),RISC机中采用的微处理器统称RISC处理器。

它能够以更快的速度执行操作

2023-04-03 14:22:38 1170

1170 RISC-V3A处理器为核心的32位通用微控制器,该处理器是基于RISC-V开源指令集设计。片上集成了时钟安全机制、多级电源管理、通用DMA控制器。此系列具有1路USB2.0主机/设备接口、多通道12位

2023-04-03 13:56:47

x86架构的指令集相对于RISC(精简指令集计算机)架构而言更为复杂。这意味着x86架构CPU可以执行更多的操作,但同时也会带来一些性能上的损失。

2023-04-03 10:21:09 9626

9626 1、产品概述Ci24R1 是一颗工作在 2.4GHz ISM 频段,专为低成本无线场合设计,集成嵌入式 ARQ 基带协议引擎的无线收发器芯片。工作频率范围为 2400MHz-2525MHz,共有

2023-03-31 10:03:20

MCU解决方案,集成丰富的MCU资源、更小尺寸,来满足设计中的各种内存、功率、尺寸要求,充分缩短2.4GHz无线产品设计周期并优化产品成本。Ci2451 是一款集成无线收发器和8位RISC(精简指令集

2023-03-31 09:56:59

MCF52259 是 ColdFire® 精简指令集计算 (RISC) 微处理器系列的成员。本文档概述了 32 位 MCF52259 微控制器,重点介绍了其高度集成和多样化的功能集。这款 32 位

2023-03-31 08:49:25

RISCMachine),又称“高级RISC机器”,是一个32位精简指令集(RISC)处理器架构。RISC-V是一种新的开放且免费的指令集架构。二者架构都源自1980年代的精简指令集计算机RISC,正是

2023-03-30 16:43:36

基于“精简指令集(RISC)”原则的开源指令集架构。 指令集:存储在CPU内部,引导CPU进行运算,并帮助CPU更高效运行,介于软件和底层硬件之间的一套程序指令合集。 RISC-V的历史 RISC-V的作者

2023-03-30 16:40:41

five RISC(Reduced Instruction Set Computer,精简指令集计算机),是和CISC(Complex InstructionSetComputer,复杂指令集

2023-03-30 16:34:57

Ci2451 是一款集成无线收发器和 8 位 RISC(精简指令集)MCU 的 SOC 芯片。 优点:超低睡眠功耗,极少外围器件,降低系统应用成本,拥有精简指令集架构,可以很容易做编程和控制。 主要

2023-03-30 10:56:23 591

591 快兼容性好PC服务器精简指令集RISCARM生态成熟非离散需授权移动设备嵌入式设备RISC-V开源模块化简洁可拓展物联网人工智能边缘计算ISA是底层硬件电路面向上层软件程序提供的一层 接口规范 ,即

2023-03-28 16:57:06

Ci24R1 是一颗工作在2.4GHz ISM频段,专为低成本无线场合设计,集成嵌入式ARQ基带协议引擎的无线收发器芯片。工作频率范围为2400MHz-2525MHz,共有126个1MHz带宽的信道

2023-03-27 17:17:10

正在加载...

电子发烧友App

电子发烧友App

评论