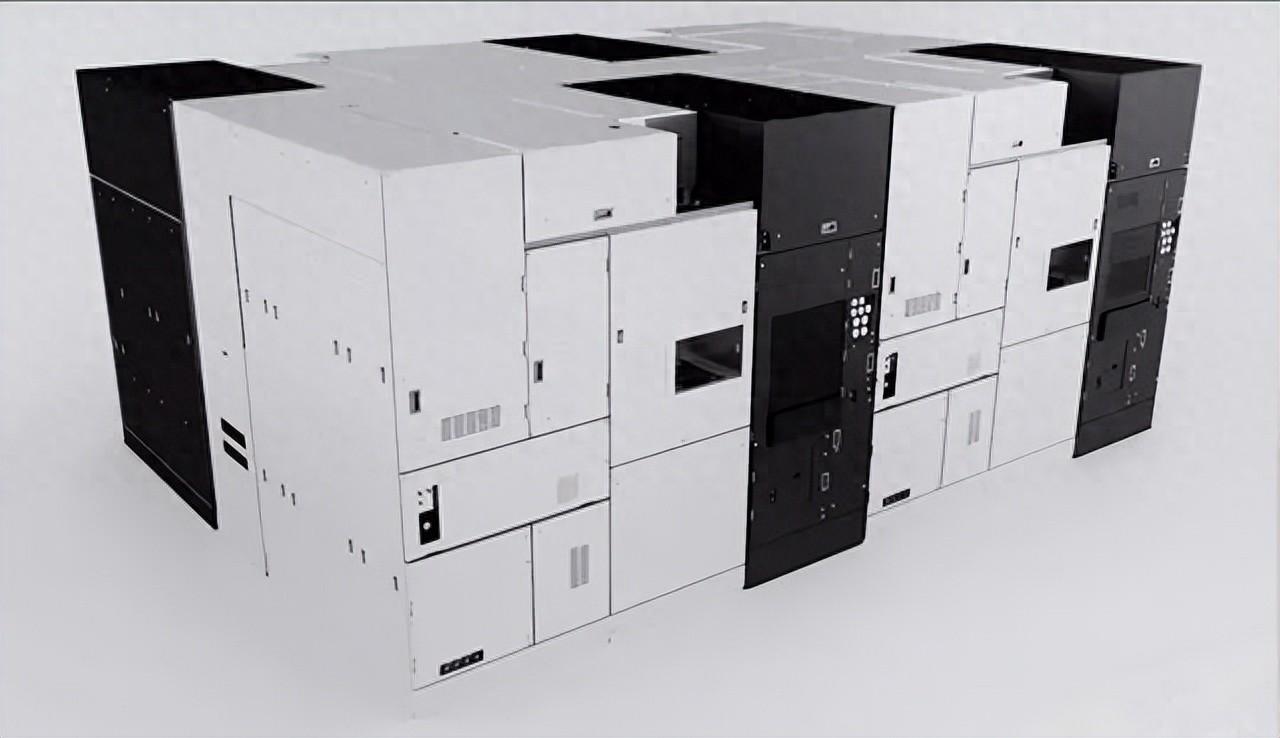

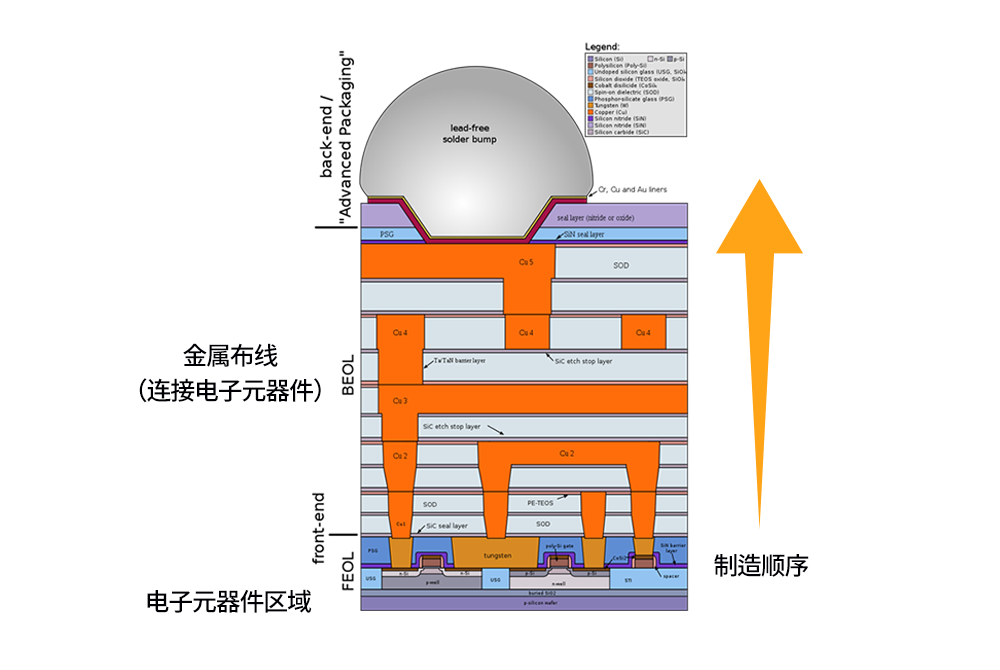

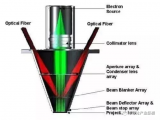

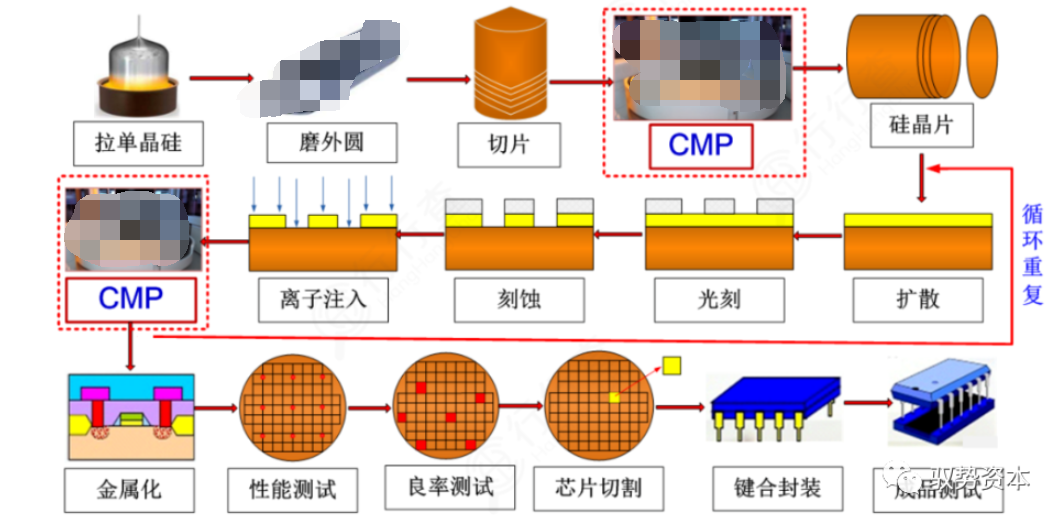

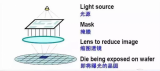

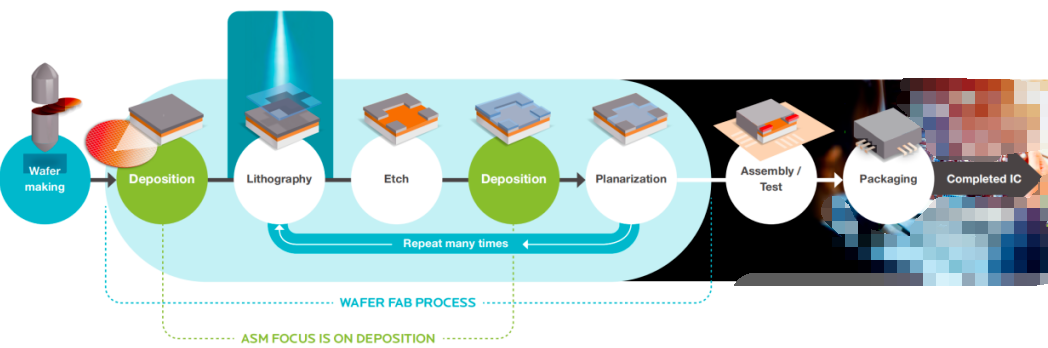

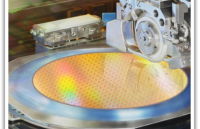

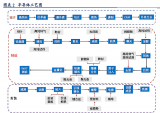

集成电路在制作过程中需要经历材料制备、掩膜、光刻、刻蚀、清洗、掺杂、机械研磨等多个工序,其中以光刻工序最为关键,因为它是整个集成电路产业制造工艺先进程度的重要指标。而光刻工序用到的设备--***则是集成电路制造中最精密复杂、难度最高、价格最昂贵的设备,用于在芯片制造过程中的掩膜图形到硅衬底图形之间的转移。

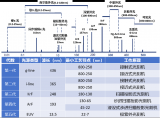

***的发展经过了一个漫长的过程,1960年代的接触式***、接近式***,到1970年代的投影式***,1980年代的步进式***,到步进式扫描***,到浸入式***和现在的EUV***,设备性能不断提高,推动集成电路按照摩尔定律往前发展。

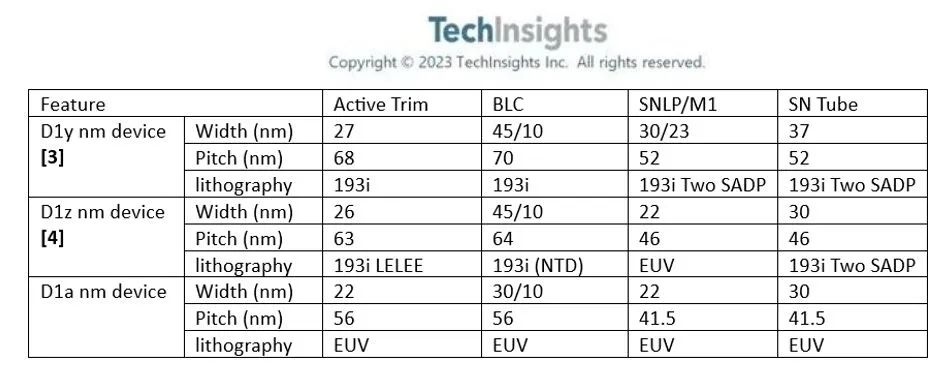

EUV作为下一代技术的代表,不需要多重曝光,一次就能曝出想要的精细图形,没有超纯水和晶圆接触,在产品生产周期、OPC的复杂程度、工艺控制、良率等方面的优势明显。但是也需要继续优化。特别是EUV的曝光方式,降低EUV掩膜版的缺陷,以及晶圆产率方面还有很大发大空间。EUV***对7nm及以下的工艺节点非常重要,台积电、三星两大代工巨头均已在最新产品中引入7纳米EUV技术。

EUV***垄断者ASML

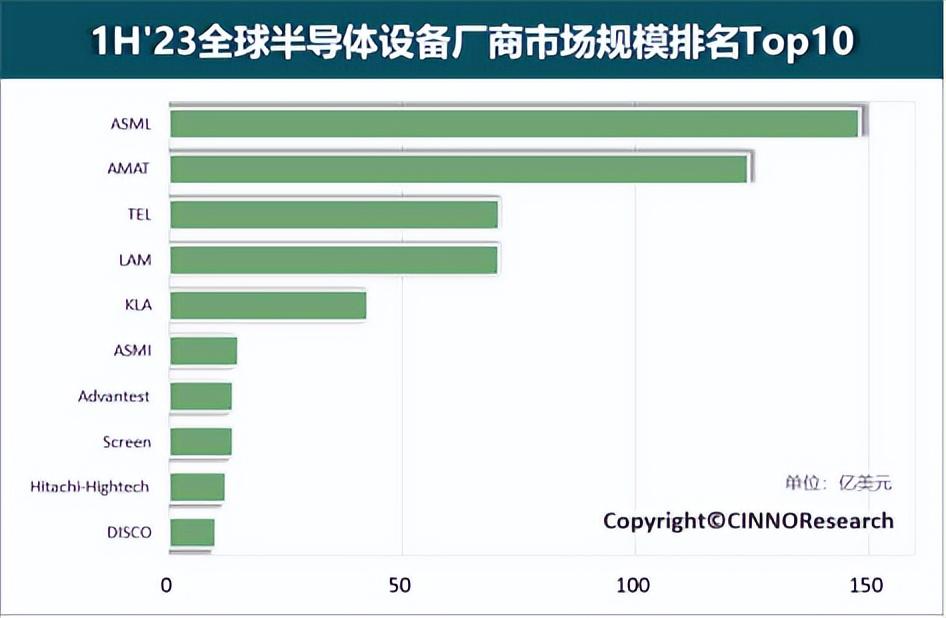

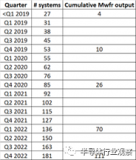

目前,***领域的龙头老大是荷兰ASML,并已经占据了高达80%的市场份额,垄断了高端***市场。ASML公司日前发布2018年Q3季度财报,当季营收27.8亿欧元,净利润6.8亿欧元,出货了5台EUV***,全年预计出货18台,明年将增长到30台,而且明年下半年会推出新一代的NXE:3400C型***,生产能力从现在的每小时125晶圆提升到155片晶圆以上,意味着产能提升24%。

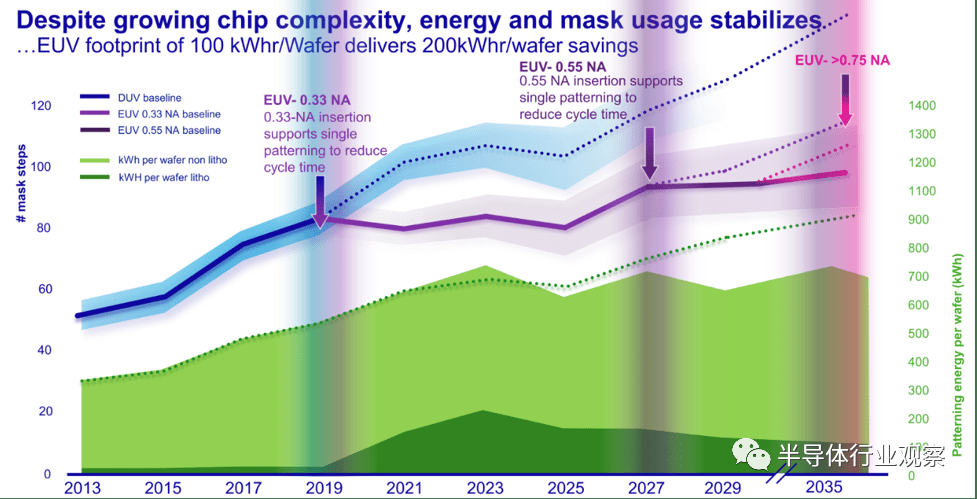

在现有的EUV之外,ASML与IMEC比利时微电子中心还达成了新的合作协议,双方将共同研发新一代EUV***,NA数值孔径从现有的0.33提高到0.5,可以进一步提升光刻工艺的微缩水平,制造出更小的晶体管。

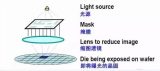

NA数值孔径对***有什么意义?,决定***分辨率的公式如下:

***分辨率=k1*λ/NA

其中k1是常数,不同的***k1不同,λ指的是光源波长,NA是物镜的数值孔径,所以***的分辨率就取决于光源波长及物镜的数值孔径,波长越短越好,NA越大越好,这样***分辨率就越高,制程工艺越先进。

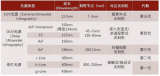

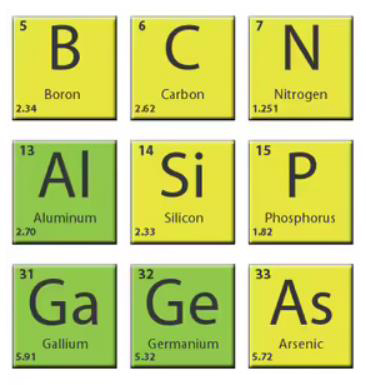

现在的EUV***使用的是波长13.5nm的极紫外光,而普通的DUV***使用的是193nm的深紫外光,所以升级到EUV***可以大幅提升半导体工艺水平,实现7nm及以下工艺。

但是改变波长之后再进一步提升EUV***的分辨率就要从NA指标上下手了,目前的***使用的还是NA=0.33的物镜系统,下一代的目标就是NA=0.5及以上的光学系统了。

如今ASML与IMEC合作的就是高NA的EUV工艺了,双方将成立一个联合实验室,在EXE:5000型***上使用NA=0.55的光学系统,更高的NA有助于将EVU光源投射到更广阔的晶圆上从而提高半导体工艺分辨率,减少晶体管尺寸。

如今这项研究才刚刚开始,所以新一代EUV光刻工艺问世时间还早,此前ASML投资20亿美元入股蔡司公司,目标就是合作研发NA=0.5的物镜系统,之前公布的量产时间是2024年,这个时间点上半导体公司的制程工艺应该可以到3nm节点了。

国内2019年迎首台EUV***

***是中国在半导体设备制造上最大的短板,处于技术领先的上海微电子装备有限公司已量产的***中,性能最好的是能用来加工90nm芯片的***,与国外的技术差距说是鸿沟都不为过。正是因此,国内晶圆厂所需的高端***完全依赖进口。

在国内,一直流传着一种声音,即受西方《瓦森纳协议》的限制,中国只能买到 ASML 的中低端产品,出价再高,也无法购得 ASML 的高端设备。这一说法受到ASML 中国区总裁金泳璇的否认。金泳璇在接手媒体采访时澄清:ASML 对大陆晶圆厂与国际客户一视同仁,只要客户下单, EUV 要进口到中国完全没有任何问题。在交期方面,所有客户也都完全一致,从下单到正式交货,均为21个月。

而这一说法在中芯国际向ASML订购的一台最新型EUV极紫外线***之后,貌似经过了证实。这一中国大陆首台 EUV ***,将在2019年交付。

电子发烧友App

电子发烧友App

评论